Research on the Mechanical Failure Risk Points of Ti/Cu/Ti/Au Metallization Layer

Abstract

:1. Introduction

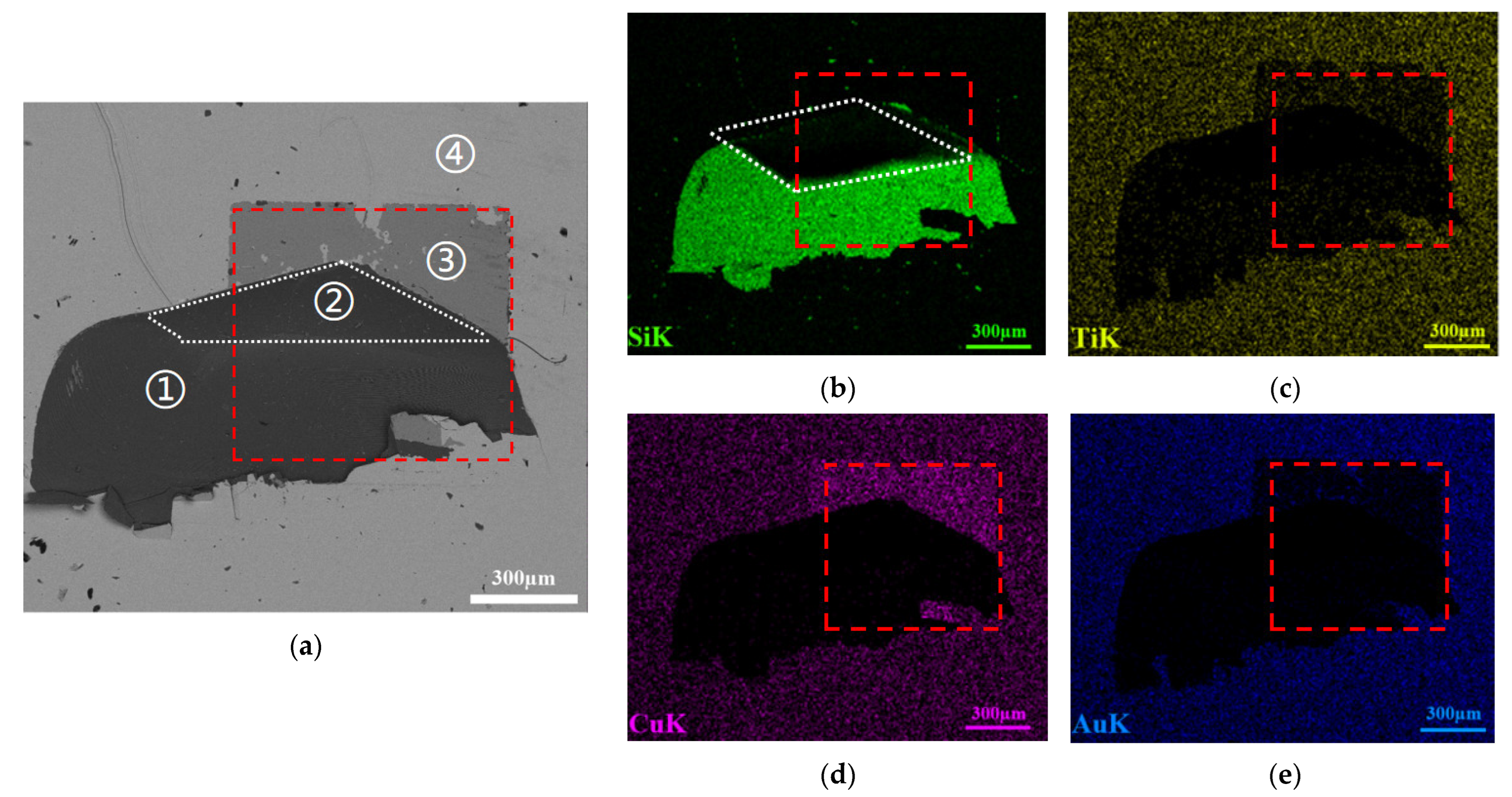

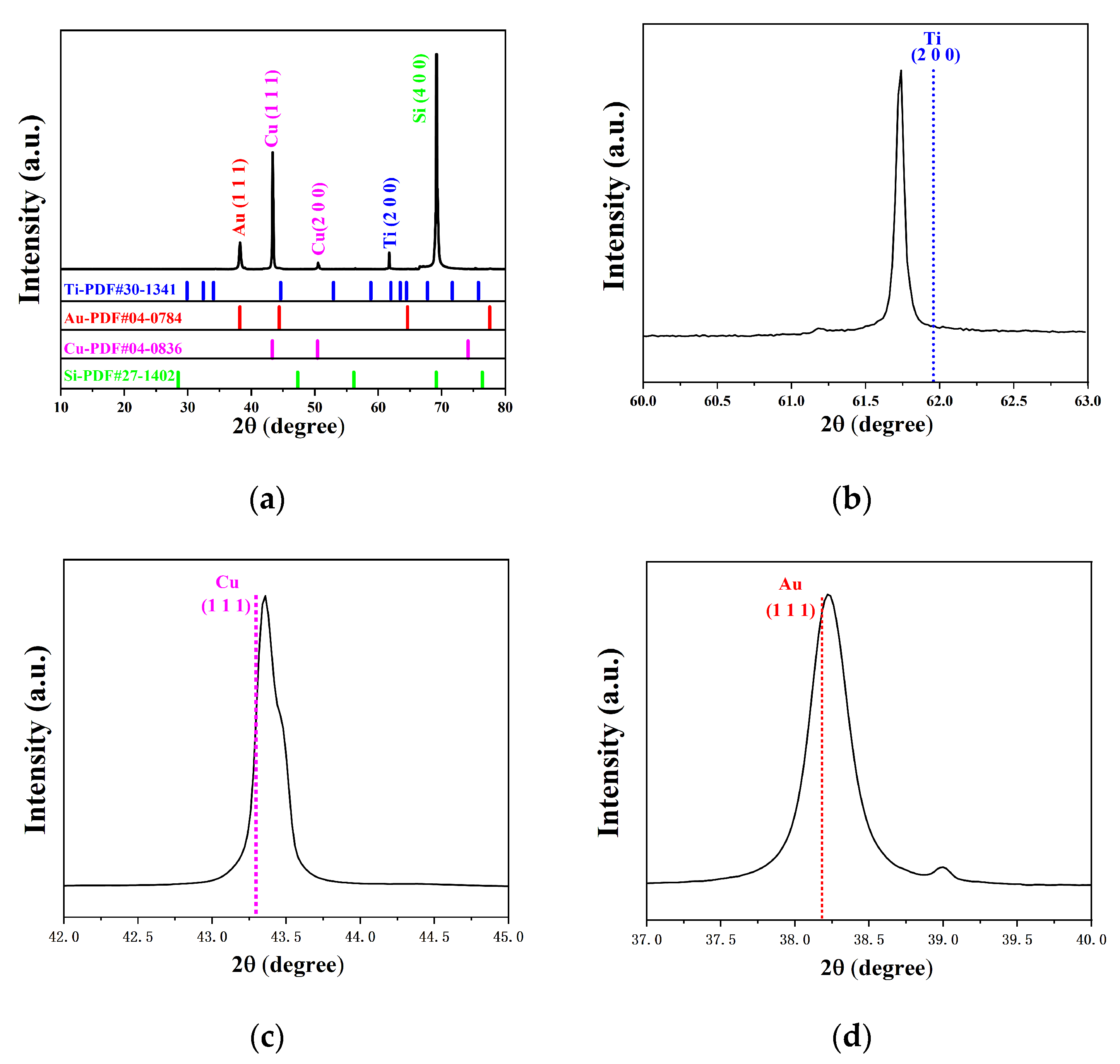

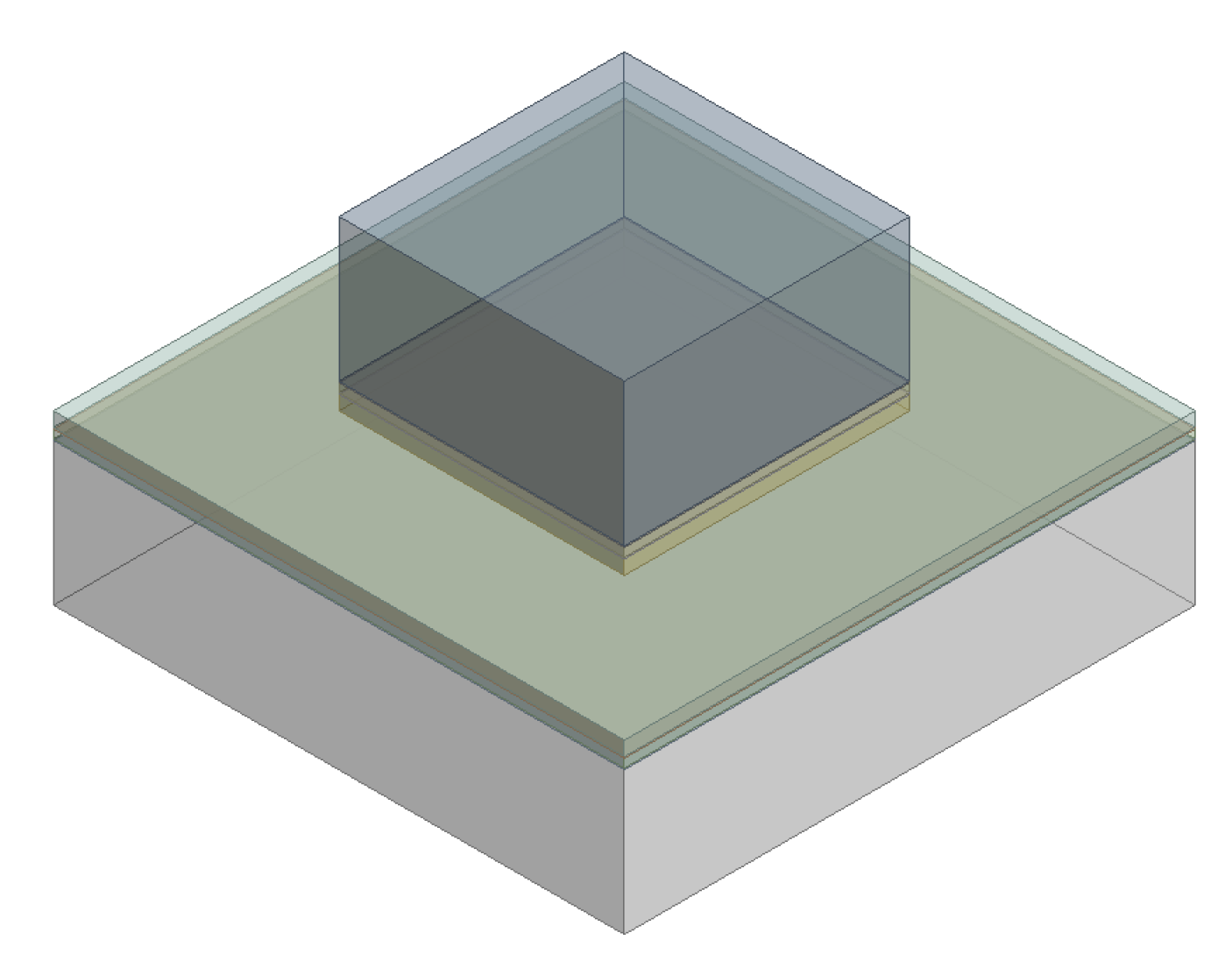

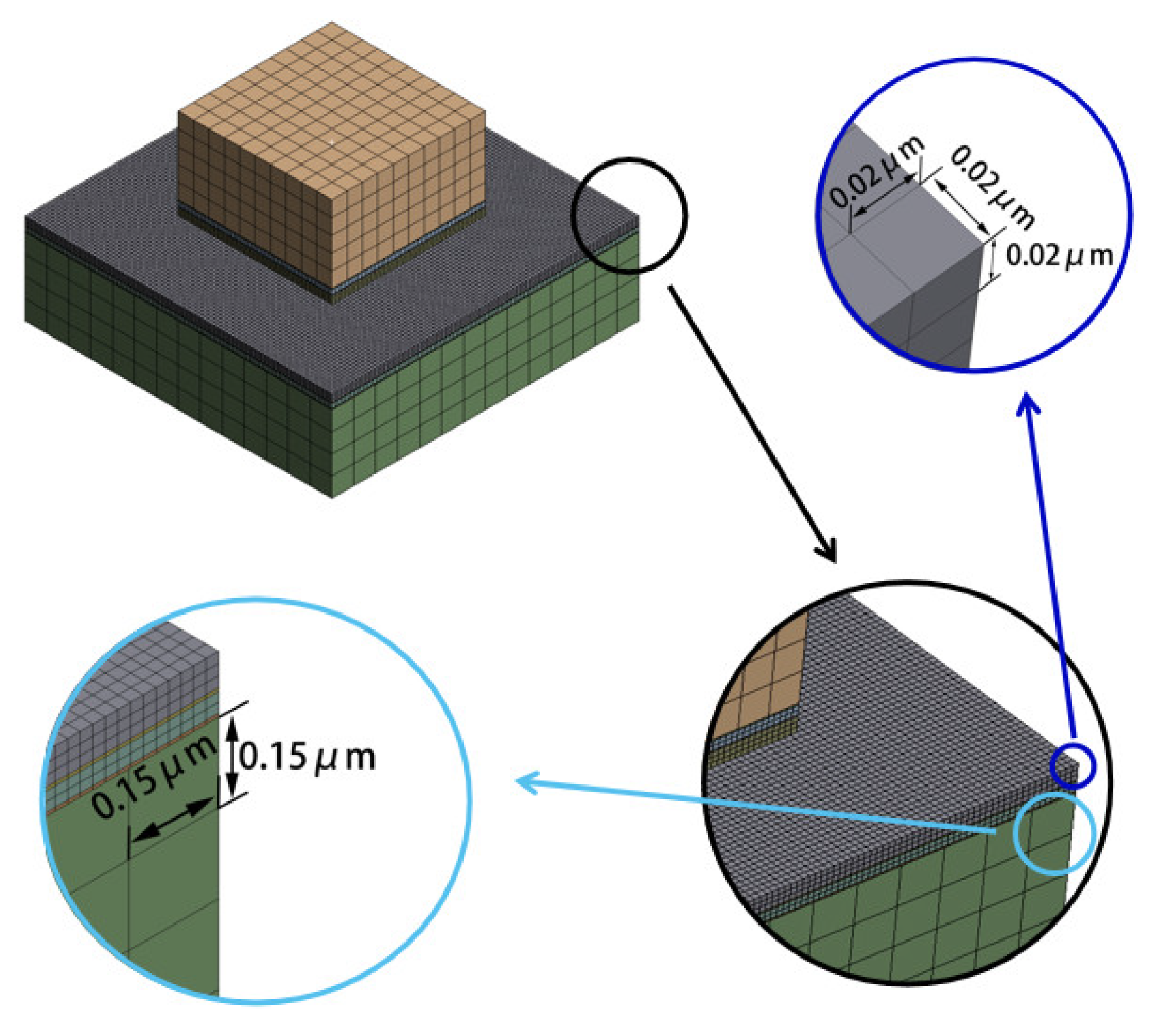

2. Experimental

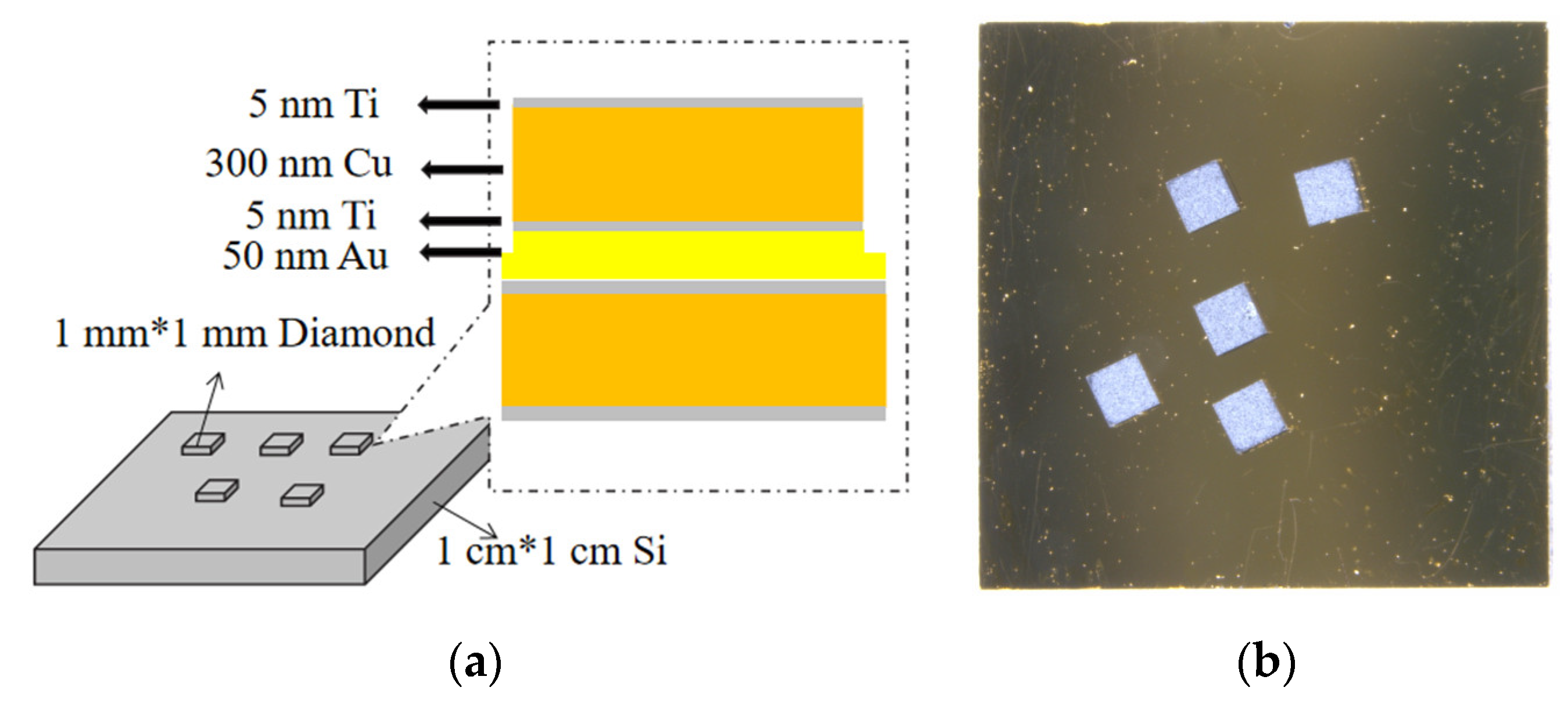

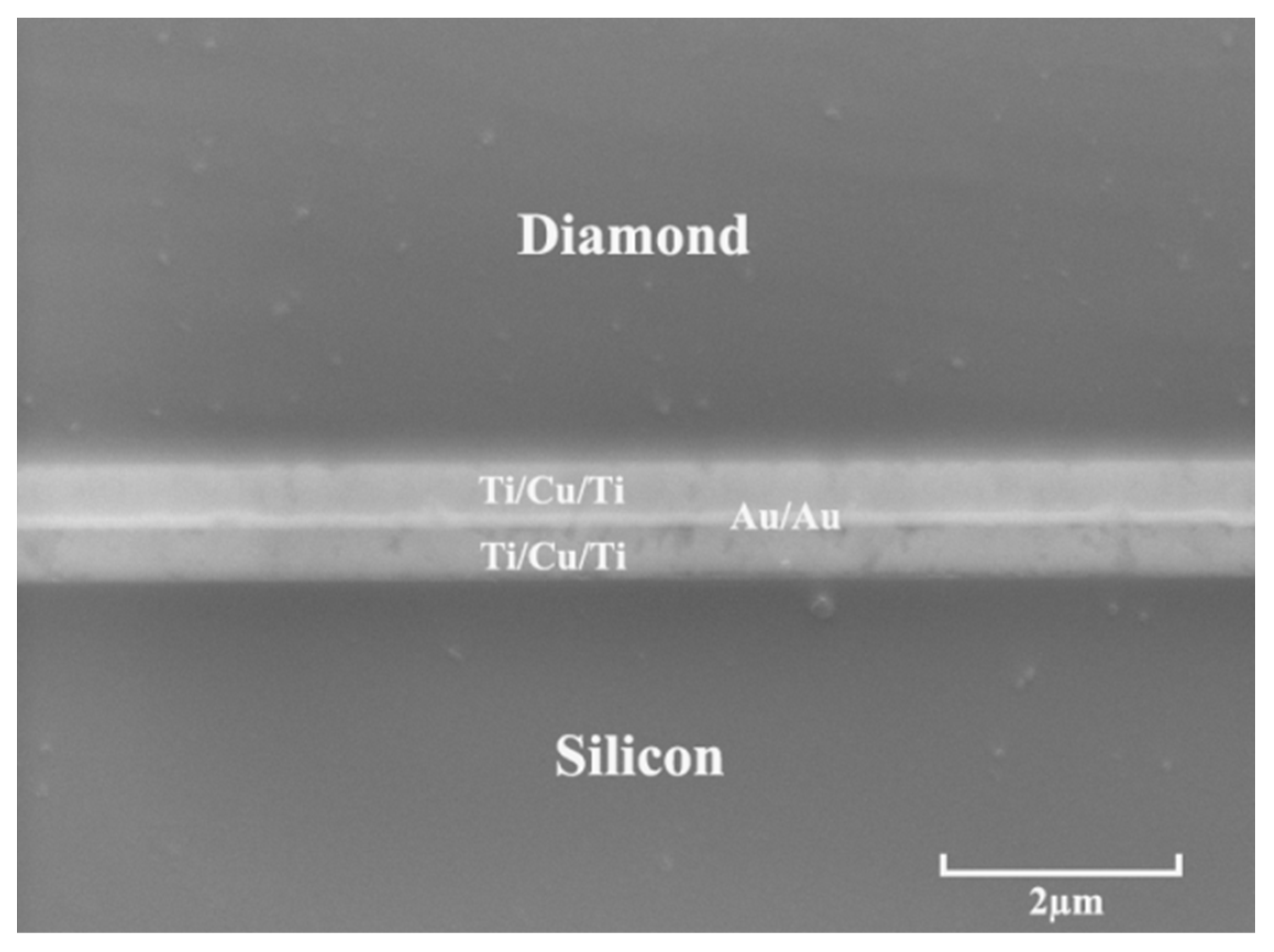

2.1. Sample Preparation

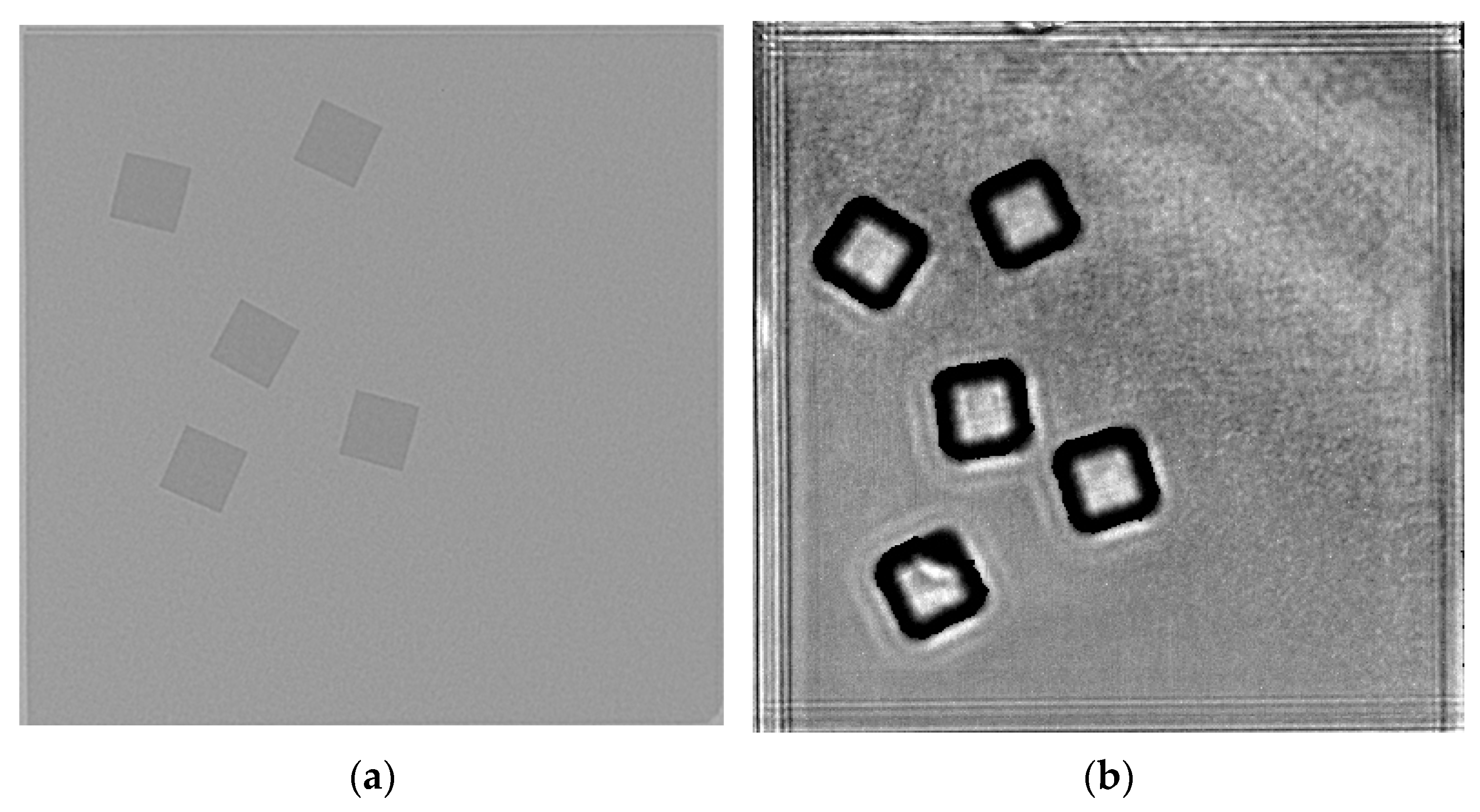

2.2. Characterizations

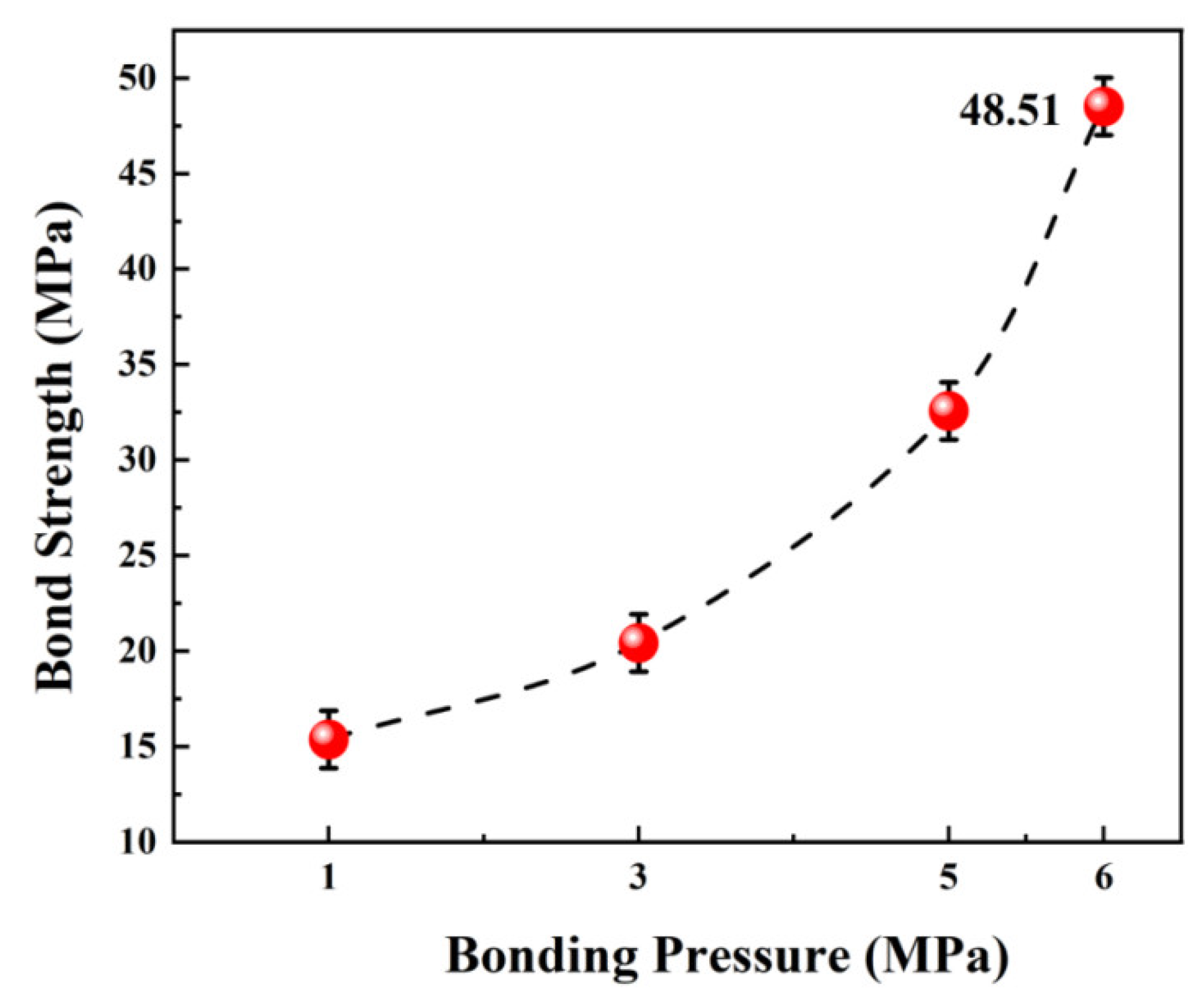

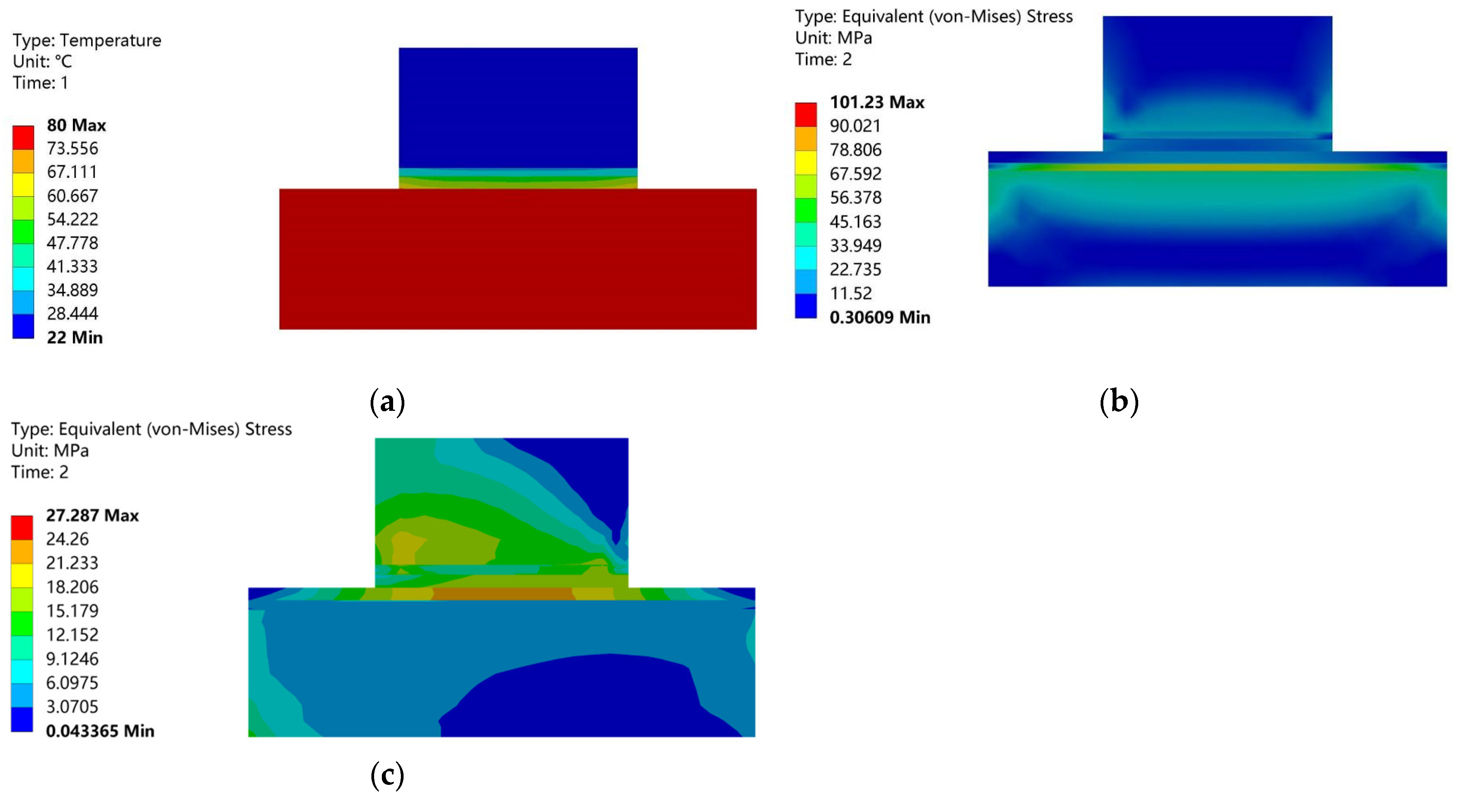

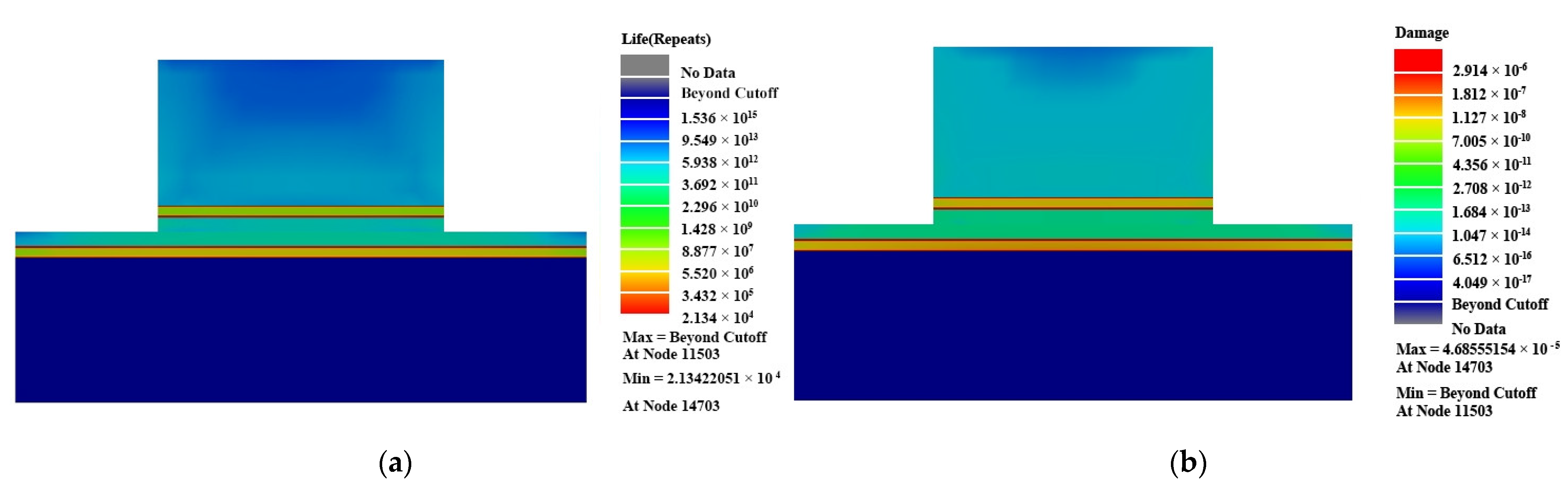

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Venkateswarlu, S.; Mishra, S.; Oprins, H.; Vermeersch, B.; Brunion, M.; Han, J.H.; Stan, M.R.; Biswas, D.; Weckx, P.; Catthoor, F. Impact of 3-D Integration on Thermal Performance of RISC-V MemPool Multicore SOC. In IEEE Transactions on Very Large Scale Integration (VLSI) Systems; IEEE: Piscataway, NJ, USA, 2023; pp. 1–9. [Google Scholar] [CrossRef]

- Abdullah, M.F.; Mat Hussin, M.R.; Ismail, M.A.; Wan Sabli, S.K. Chip-level thermal management in GaN HEMT: Critical review on recent patents and inventions. Microelectron. Eng. 2023, 273, 111958. [Google Scholar] [CrossRef]

- Martin, H.; Reintjes, M.; Reijs, D.; Dorrestein, S.; Kengen, M.; Libon, S.; Smits, E.; Tang, X.; Koelink, M.; Poelma, R.; et al. Heterogeneous Integration of Diamond Heat Spreaders for Power Electronics Application. In Proceedings of the 2023 IEEE 73rd Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 30 May–2 June 2023; IEEE: New York, NY, USA, 2023; pp. 118–125. [Google Scholar]

- Xin, J.; Junjun, W.; Yabo, H. Application progress of diamond heat dissipation substrate in GaN-based power devices. Surface Technol. 2020, 49, 120–132. [Google Scholar]

- Anupam, K.C.; Anderson, J.; Ayala, A.; Engdahl, C.; Piner, E.L.; Holtz, M.W. Heterogeneous integration of high-quality diamond on aluminum nitride with low and high seeding density. J. Cryst. Growth 2023, 610, 127172. [Google Scholar] [CrossRef]

- Minoura, Y.; Ohki, T.; Okamoto, N.; Yamada, A.; Makiyama, K.; Kotani, J.; Ozaki, S.; Sato, M.; Nakamura, N. Surface activated bonding of SiC/diamond for thermal management of high-output power GaN HEMTs. Jpn. J. Appl. Phys. 2020, 59, SGGD03. [Google Scholar] [CrossRef]

- Kwak, T.; Lee, J.; Choi, U.; So, B.; Yoo, G.; Kim, S.; Nam, O. Diamond Schottky barrier diodes fabricated on sapphire-based freestanding heteroepitaxial diamond substrate. Diam. Relat. Mater. 2021, 114, 108335. [Google Scholar] [CrossRef]

- Kim, S.-W.; Takaya, R.; Hirano, S.; Kasu, M. Two-inch high-quality (001) diamond heteroepitaxial growth on sapphire (1120) misoriented substrate by step-flow mode. Appl. Phys. Express 2021, 14, 115501. [Google Scholar] [CrossRef]

- Ahmed, R.; Siddique, A.; Anderson, J.; Gautam, C.; Holtz, M.; Piner, E. Integration of GaN and diamond using epitaxial lateral overgrowth. ACS Appl. Mater. Interfaces 2020, 12, 39397–39404. [Google Scholar] [CrossRef]

- Ling, B.; Jing, N.; Jincheng, Z.; Dong, W.; Boyu, W.; Haidi, W.; Jianglin, Z.; Ran, T.; Zhonghui, L. Van der waals epitaxial GaN thin films on polycrystalline diamond substrate. J. Synth. Cryst. 2023, 52, 901–908. [Google Scholar] [CrossRef]

- Caoyuan, M.; Genzhuang, L.; Wenliang, X.; Qiliang, W.; Xianyi, L.; Liu’an, L.; Guangtian, Z. Research progress in preparation of large size single crystal diamond by microwave plasma chemical vapor deposition. Electron. Packag. 2023, 23, 36–45. [Google Scholar] [CrossRef]

- Wenqiang, X. A Study of Nitride Epitaxy and Properties on Diamond Substrates. Master’s Thesis, Xidian University, Xi’an, China, 2022. [Google Scholar]

- Srimurugan, R.; Vijay Ananth, S.; Geethan, A.; Jayaseelan, V.; Xavier, J.F. Experimental investigation on diffusion bonding of dissimilar metals. AIP Conf. Proc. 2020, 2283, 020062. [Google Scholar] [CrossRef]

- Matsumae, T.; Kurashima, Y.; Umezawa, H.; Mokuno, Y.; Takagi, H. Room-temperature bonding of single-crystal diamond and Si using Au/Au atomic diffusion bonding in atmospheric air. Microelectron. Eng. 2018, 195, 68–73. [Google Scholar] [CrossRef]

- Matsumae, T.; Kurashima, Y.; Takagi, H. Surface activated bonding of Ti/Au and Ti/Pt/Au films after vacuum annealing for MEMS packaging. Microelectron. Eng. 2018, 197, 76–82. [Google Scholar] [CrossRef]

- Fei, W.; Kang, W.; Genqiang, C.; Fang, L.; Ruozhen, W.; Wei, W.; Minghui, Z.; Wenbo, H.; Hongxing, W. Room temperature bonding of diamond/Si with Mo/Au interlayers in atmospheric air. Diam. Relat. Mater. 2023, 135, 109844. [Google Scholar] [CrossRef]

- Shimatsu, T.; Uomoto, M.; Oba, K.; Furukata, Y. Atomic diffusion bonding of wafers in air with thin Au films and its application to optical devices fabrication. In Proceedings of the 2012 3rd IEEE International Workshop on Low Temperature Bonding for 3D Integration, LTB-3D 2012, Tokyo, Japan, 22–23 May 2012; p. 103. [Google Scholar]

- Zeguang, L.; Dengquan, C.; Ximing, L.; Kun, X. Gold-tin alloy solder for the package of microelectronics. Precious Met. 2005, 26, 62–65. [Google Scholar]

- Bao, S.; Zhong, Y.; He, Y.; Li, K.; Yu, D. Low-temperature die to glass wafer bonding based on Au-Au atomic diffusion. In Proceedings of the 2022 China Semiconductor Technology International Conference (CSTIC), Shanghai, China, 20–21 June 2022; pp. 1–3. [Google Scholar]

- Guo, C.; Fangyuan, S.; Jialiang, D.; Zifan, C.; Xitao, W.; Jinguo, W.; Kim, M.J.; Hailong, Z. Effect of Ti interlayer on interfacial thermal conductance between Cu and diamond. Acta Mater. 2018, 160, 235–246. [Google Scholar] [CrossRef]

- Higurashi, E.; Okumura, K.; Kunimune, Y.; Suga, T.; Hagiwara, K. Room-temperature bonding of wafers with smooth au thin films in ambient air using a surface-activated bonding method. IEICE Trans. Electron. 2017, E100C, 156–160. [Google Scholar] [CrossRef]

- Sukkurji, P.A.; Issac, I.; Singaraju, S.A.; Velasco, L.; Hagmann, J.A.; Bessler, W.; Hahn, H.; Botros, M.; Breitung, B. Tailored silicon/carbon compounds for printed Li–Ion anodes. Batter. Supercaps 2020, 3, 713–720. [Google Scholar] [CrossRef]

- Xuefeng, R.; Ying, S.; Anmin, L.; Jie, Z.; Peixia, Y.; Jinqiu, Z.; Maozhong, A. Experimental and theoretical studies of DMH as a complexing agent for a cyanide-free gold electroplating electrolyte. RSC Adv. 2015, 5, 64997–65004. [Google Scholar] [CrossRef]

- Dongsheng, W.; Mingyue, F.; Tingyu, H.; Fanming, Z.; Xiaoli, H.; Li, C.; Zhongmin, S. Cu/CuxS-embedded N,S-doped porous carbon derived in situ from a MOF designed for efficient catalysis. Chem. Eur. J. 2021, 27, 11468–11476. [Google Scholar] [CrossRef]

- Mohaghegh, F.; Akhbari, K.; Phuruangrat, A. Preparation of thallium nanomaterials from thallium(I) coordination polymers precursors synthesized by green sonochemical and mechanochemical processes. Ultrason. Sonochem. 2018, 40, 594–600. [Google Scholar] [CrossRef]

- Goldfarb, I.; Pelleg, J.; Zevin, L.; Croitoru, N. Lattice distortion in thin films of IVB metal (Ti, Zr, Hr) nitrides. Thin Solid Films 1991, 200, 117–127. [Google Scholar] [CrossRef]

- Tenghiri, L.; Khalil, Y.; Abdi, F.; Bentamy, A. Structural design and analysis of a small wind turbine blade using Simple Load Model, FAST-MLife codes, and ANSYS nCode DesignLife. Wind Eng. 2019, 45, 0309524X1988243. [Google Scholar] [CrossRef]

- Sivachev, S.; Myagkov, L. Thermomechanical fatigue analysis of diesel engine piston: Finite element simulation and lifetime prediction technique. In Proceedings of the 5th International Conference on Industrial Engineering (ICIE 2019), Sochi, Russia, 25–29 March 2019; Volume I 5, pp. 109–117. [Google Scholar]

- Xianming, L.; Zheng, H.; Bo, W.; Zhilin, L.; Lei, L.; Chongjun, H.; Feng, G. Fatigue life analysis on hydraulic end of fracturing pump based on nCode DesignLife. China Pet. Mach. 2023, 51, 90–96. [Google Scholar] [CrossRef]

- Pengfei, C. Research on Thermal Fatigue of Electric Connectors. Master’s Thesis, Beijing University of Posts and Telecommunications, Beijing, China, 2022. [Google Scholar]

- Sener, A.S. Fatigue life evaluation of an electrically driven shuttle frame using finite element analysis. Mater. Test. 2021, 63, 329–335. [Google Scholar] [CrossRef]

- Xiangyu, C.; Qingyu, L.; Wenzhen, L.; Fan, Y.; Tingting, H. Research about thermal fatigue characteristic of IGBT module in considering of electrothermal-mechanism coupling and crack. Smart Grid 2017, 7, 443–451. [Google Scholar]

- Lifeng, G.; Ruijing, Z.; Liguo, L.; Hui, G.; Jianping, X. Fatigue reliability analysis for the mechanical system of large-scale medical imaging equipment SPECT. In Proceedings of the 2018 2nd International Conference on Advances in Energy, Environment and Chemical Science (AEECS 2018), Zhuhai, China, 2–4 February 2018; pp. 168–172. [Google Scholar]

| Element | Crystal Structure | a-Axis Lattice Constant (Å) | c-Axis Lattice Constant (Å) | Plane Spacing (Å) |

|---|---|---|---|---|

| Si | FCC | 5.430 | - | 1.357 (4 0 0) |

| Ti | HCP | 3.456 | 5.525 | 1.496 (2 0 0) |

| Cu | FCC | 3.615 | - | 2.088 (1 1 1) |

| Au | FCC | 4.078 | - | 2.355 (1 1 1) |

| Material Properties | Material Name | ||||

|---|---|---|---|---|---|

| Si | Ti | Cu | Au | Diamond | |

| Density (kg/m−3) | 2330 | 4500 | 8933 | 19,300 | 3510 |

| Elastic modulus (GPa) | 190 | 102.04 | 110 | 78.5 | 1000 |

| Poisson’s ratio | 0.2782 | 0.3 | 0.34 | 0.42 | 0.2 |

| Thermal expansion coefficient (k−1) | 2.5 × 10−6 | 7.6 × 10−6 | 1.6 × 10−5 | 1.4 × 10−5 | 1.2 × 10−12 |

| Thermal conductivity (W/m·K) | 148 | 21 | 400 | 315 | 2000 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhao, M.; Jian, X.; Chen, S.; Chen, M.; Wang, G.; Gong, T.; Tian, Y.; Lu, X.; Zhao, Z.; Yang, X. Research on the Mechanical Failure Risk Points of Ti/Cu/Ti/Au Metallization Layer. Crystals 2023, 13, 1625. https://doi.org/10.3390/cryst13121625

Zhao M, Jian X, Chen S, Chen M, Wang G, Gong T, Tian Y, Lu X, Zhao Z, Yang X. Research on the Mechanical Failure Risk Points of Ti/Cu/Ti/Au Metallization Layer. Crystals. 2023; 13(12):1625. https://doi.org/10.3390/cryst13121625

Chicago/Turabian StyleZhao, Mingrui, Xiaodong Jian, Si Chen, Minghui Chen, Gang Wang, Tao Gong, Yangning Tian, Xiangjun Lu, Zhenbo Zhao, and Xiaofeng Yang. 2023. "Research on the Mechanical Failure Risk Points of Ti/Cu/Ti/Au Metallization Layer" Crystals 13, no. 12: 1625. https://doi.org/10.3390/cryst13121625