A Primer on Design Aspects and Recent Advances in Shuffle Exchange Multistage Interconnection Networks

Abstract

:1. Introduction

1.1. Related Surveys and Motivation

1.2. Contribution

- It reviews the recent technical contributions towards improving fault-tolerance, analysis, assessment, and modelling of the reliability property of shuffle exchange MINs while comparing some of their key metrics, objectives and features. Topologies for enhanced SEN designs are also provided to facilitate a deeper understanding of the reviewed works.

- It highlights further recommendations towards the design and analysis of shuffle exchange networks based on lessons learnt from prior art and current research trends.

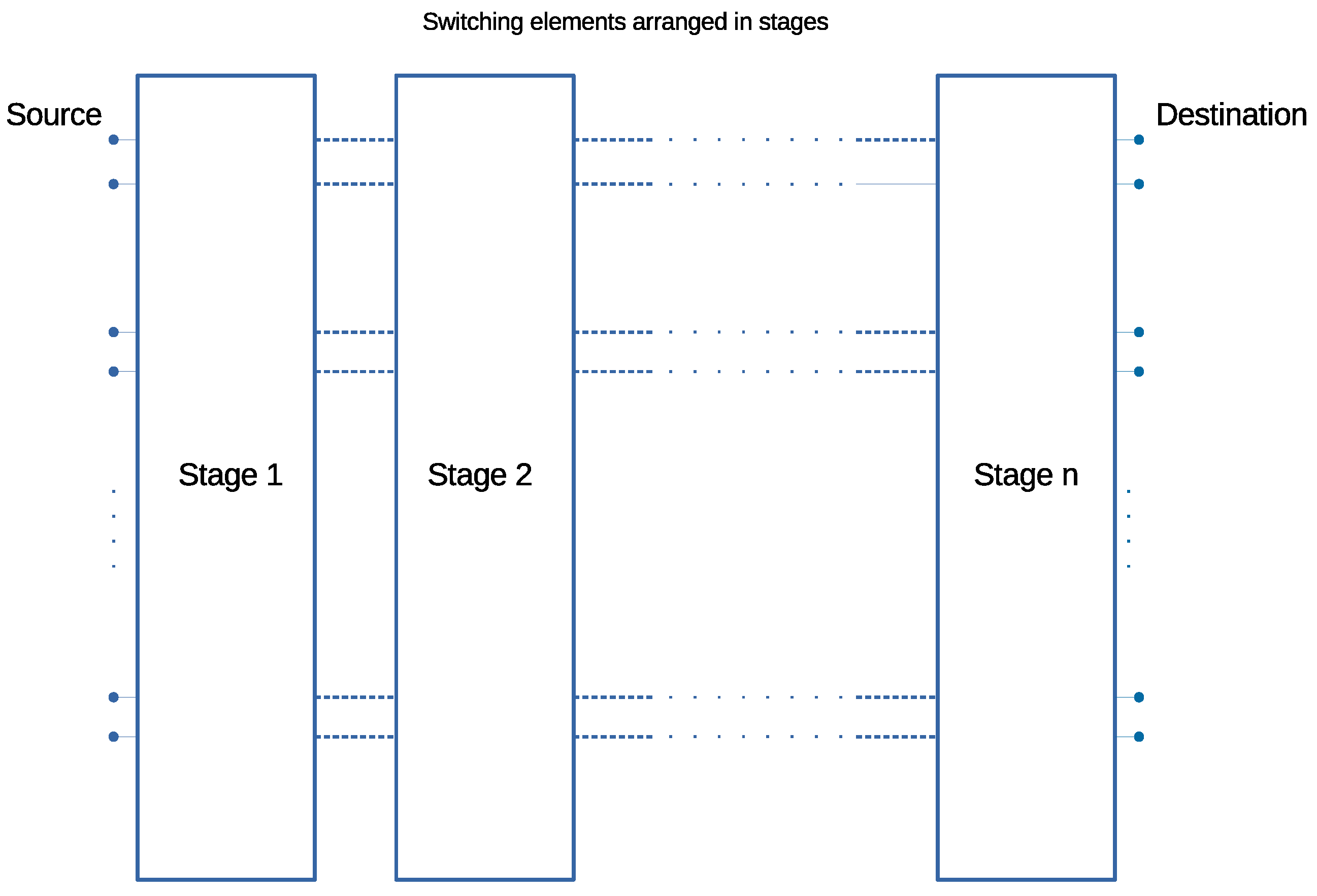

2. Multistage Interconnection Networks

2.1. Architecture of MINs

2.2. Categories of MINs

2.3. Design Aspects of MINs

Improving Efficiency in MINs

2.4. Shuffle Exchange MINs

3. Fault Tolerance

3.1. Improving Fault Tolerance

Recent Advances

4. Reliability

4.1. Reliability Measurement

Recent Advances

4.2. Reliability Modelling

Recent Advances

4.3. Reliability Assessment

Recent Advances

5. Future Recommendations

5.1. Configuration

5.2. Cost-Effectiveness

5.3. Congestion

5.4. Traffic

5.5. Scalability

5.6. Practical Assumptions

5.7. Switching

5.8. Performance Analysis

5.9. Network Optimization

5.10. Deadlock Avoidance

5.11. Application to NOC

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Yunus, N.A.M.; Othman, M.; Hanapi, Z.M.; Lun, K.Y. Enhancement Replicated Network: A Reliable Multistage Interconnection Network Topology. IEEE Syst. J. 2018, 13, 2653–2663. [Google Scholar] [CrossRef]

- Owens, J.D.; Dally, W.J.; Ho, R.; Jayasimha, D.; Keckler, S.W.; Peh, L.S. Research challenges for on-chip interconnection networks. IEEE Micro 2007, 27, 96–108. [Google Scholar] [CrossRef]

- Chen, P.Y.; Lawrie, D.H.; Yew, P.C.; Padua, D.A. Interconnection networks using shuffles. Computer 1981, 14, 55–64. [Google Scholar] [CrossRef]

- Feng, T.Y. A survey of interconnection networks. Computer 1981, 14, 12–27. [Google Scholar] [CrossRef]

- Padmanabhan, K.; Lawrie, D.H. A class of redundant path multistage interconnection networks. IEEE Trans. Comput. 1983, 32, 1099–1108. [Google Scholar] [CrossRef]

- Bistouni, F.; Jahanshahi, M. Rearranging links: A cost-effective approach to improve the reliability of multistage interconnection networks. Int. J. Internet Technol. Secur. Trans. 2018, 8, 336–373. [Google Scholar] [CrossRef]

- Siegel, H.J.; Hsu, W.T.Y.; Jeng, M. An introduction to the multistage cube family of interconnection networks. J. Supercomput. 1987, 1, 13–42. [Google Scholar] [CrossRef]

- Siegel, H.J. Interconnection networks for SIMD machines. Computer 1979, 12, 57–65. [Google Scholar] [CrossRef]

- Thurber, K.J. Interconnection networks: A survey and assessment. In Proceedings of the National Computer Conference and Exposition, Chicago, IL, USA, 6–10 May 1974; pp. 909–919. [Google Scholar]

- Siegel, H.J.; McMillen, R.J.; Mueller, P.T. A survey of interconnection methods for reconfigurable parallel processing systems. In Proceedings of the IEEE 1979 International Workshop on Managing Requirements Knowledge (MARK), New York, NY, USA, 4–7 June 1979; pp. 529–542. [Google Scholar] [CrossRef]

- Radunović, B.; Milutinović, V. A survey of reconfigurable computing architectures. In International Workshop on Field Programmable Logic and Applications; Springer: Berlin/Heidelberg, Germany, 1998; pp. 376–385. [Google Scholar] [CrossRef]

- Yunus, N.A.M.; Othman, M. Shuffle Exchange Network in Multistage InterconnectionNetwork: A Review and Challenges. Int. J. Comput. Electr. Eng. 2011, 3, 724. [Google Scholar] [CrossRef]

- Sadawarti, H.; Bansal, S.; Kaur, N. A Survey on Multi-Stage Interconnection Networks. Int. J. Comput. Sci. Trends Technol. 2015, 3, 143–151. [Google Scholar]

- Md Yunus, N.A.; Othman, M.; Mohd Hanapi, Z.; Lun, K.Y. Reliability review of interconnection networks. IETE Tech. Rev. 2016, 33, 596–606. [Google Scholar] [CrossRef]

- Rajkumar, S.; Goyal, N.K. Review of multistage interconnection networks reliability and fault-tolerance. IETE Tech. Rev. 2016, 33, 223–230. [Google Scholar] [CrossRef]

- Gupta, S.; Pahuja, G. Regular Shuffle Exchange Interconnection Networks: Review and Comparison. In Proceedings of the 2018 International Conference on Sustainable Energy, Electronics, and Computing Systems (SEEMS), Greater Noida, India, 26–27 October 2018; pp. 1–6. [Google Scholar] [CrossRef]

- Gupta, S.; Pahuja, G. A review on gamma interconnection network. Int. J. Comput. Syst. Eng. 2019, 5, 137–151. [Google Scholar] [CrossRef]

- Prakash, A.; Yadav, D.K.; Choubey, A. A Survey of Multistage Interconnection Networks. Recent Adv. Electr. Electron. Eng. Former. Recent Patents Electr. Electron. Eng. 2020, 13, 165–183. [Google Scholar] [CrossRef]

- Gaur, V.; Yadav, O.P.; Soni, G.; Rathore, A.P.S. A literature review on network reliability analysis and its engineering applications. Proc. Inst. Mechan. Eng. Part O J. Risk Reliab. 2020, 1748006X20962258. [Google Scholar] [CrossRef]

- Yunus, N.A.M.; Othman, M.; Hanapi, Z.; Kweh, Y. Integrating Replicated Network in Reliability Shuffle Exchange Network System. J. Commun. 2018, 13, 385–390. [Google Scholar] [CrossRef]

- Stergiou, E.; Garofalakis, J. Quantitative analysis of multilayer switching networks providing multiple internal routes. Int. J. Commun. Syst. 2018, 31, e3785. [Google Scholar] [CrossRef]

- Panda, D.K.; Dash, R.K.; Mishra, A.K.; Mohapatra, S.K. Reliability Evaluation and Analysis of Multistage Interconnection Networks. Int. J. Pure Appl. Math. 2018, 119, 1729–1737. [Google Scholar]

- Gupta, S.; Pahuja, G. FTSM: Design and reliability measures. In Advances in System Optimization and Control; Springer: Singapore, 2019; pp. 3–11. [Google Scholar] [CrossRef]

- Stergiou, E.; Liarokapis, D.; Glavas, E.; Angelis, C.; Margariti, S. Reliability study of U-type multistage interconnection networks. In IOP Conference Series: Materials Science and Engineering, Kota Kinabalu, Malaysia, 29–30 November 2018; IOP Publishing: Bristol, UK, 2019; Volume 575, p. 012001. [Google Scholar] [CrossRef]

- Abutaleb, M. A novel QCA shuffle-exchange network architecture with multicast and broadcast communication capabilities. Microelectron. J. 2019, 93, 104640. [Google Scholar] [CrossRef]

- Abedini, R.; Ravanmehr, R. Parallel SEN: A new approach to improve the reliability of shuffle-exchange network. J. Supercomput. 2020, 76, 10319–10353. [Google Scholar] [CrossRef]

- Gupta, S.; Pahuja, G.L. SEGIN-Minus: A New Approach to Design Reliable and Fault-Tolerant MIN. Recent Adv. Comput. Sci. Commun. Former. Recent Patents Comput. Sci. 2020, 13, 370–380. [Google Scholar] [CrossRef]

- Gholizadeh, R.; Valinataj, M. Reliability Improvement of Fault-Tolerant Shuffle Exchange Interconnection Networks. In Proceedings of the IEEE 2020 10th International Conference on Computer and Knowledge Engineering (ICCKE), Mashhad, Iran, 29–30 October 2020; pp. 336–341. [Google Scholar]

- Prakash, A.; Yadav, D.K.; Choubey, A. Terminal reliability analysis of multistage interconnection networks. Int. J. Syst. Assur. Eng. Manag. 2020, 11, 110–125. [Google Scholar] [CrossRef]

- Kamiura, N.; Kodera, T.; Matsui, N. A fault tolerant multistage interconnection network with partly duplicated switches. J. Syst. Archit. 2002, 47, 901–916. [Google Scholar] [CrossRef]

- Diab, H.; Tabbara, H.; Mansour, N. Simulation of dynamic input buffer space in multistage interconnection networks. Adv. Eng. Softw. 2000, 31, 13–24. [Google Scholar] [CrossRef]

- Agrawal, D.P.; Leu, J.S. Dynamic accessibility testing and path length optimization of multistage interconnection networks. IEEE Trans. Comput. 1985, 34, 255–266. [Google Scholar] [CrossRef]

- Potlapalli, Y.R.; Agrawal, D.P. Bounds on the number of passes in multistage interconnection networks. In Proceedings of the 1994 6th IEEE Symposium on Parallel and Distributed Processing, Dallas, TX, USA, 26–29 October 1994; pp. 460–467. [Google Scholar]

- Yunus, N.A.M.; Othman, M. Empirical analysis of terminal reliability in multistage interconnection networks. In Computational Intelligence and Efficiency in Engineering Systems; Springer: Cham, Switzerland, 2015; pp. 157–169. [Google Scholar] [CrossRef]

- Bistouni, F.; Jahanshahi, M. Analyzing the reliability of shuffle-exchange networks using reliability block diagrams. Reliab. Eng. Syst. Saf. 2014, 132, 97–106. [Google Scholar] [CrossRef]

- Gupta, S.; Pahuja, G. A new SEN Minus: Design and reliability measures. Int. J. Reliab. Qual. Saf. Eng. 2016, 23, 1650012. [Google Scholar] [CrossRef]

- Bhardwaj, V.P. A new fault tolerant routing algorithm for advance irregular alpha multistage interconnection network. In Advances in Computer Science, Engineering & Applications; Springer: Berlin/Heidelberg, Germany, 2012; pp. 979–987. [Google Scholar] [CrossRef]

- Chen, Z.; Liu, Z.J.; Qiu, Z.L. The C1-networks: A scalable multistage interconnection network with backward links for deflecting routing. In Proceedings of the IEEE International Conference on Communication Technology Proceedings, 2003. ICCT 2003, Beijing, China, 9–11 April 2003; Volume 1, pp. 281–285. [Google Scholar] [CrossRef]

- Arya, S.; Singh, N. Reliability Analysis of Modified Irregular Augmented Shuffle Exchange Network (MIASEN). Int. J. Comput. Sci. Issues (IJCSI) 2017, 14, 59. [Google Scholar]

- Ferreira, R.; Vendramini, J.; Nacif, M. Dynamic reconfigurable multicast interconnections by using radix-4 multistage networks in fpga. In Proceedings of the 2011 9th IEEE International Conference on Industrial Informatics, Lisbon, Portugal, 26–29 July 2011; pp. 810–815. [Google Scholar] [CrossRef]

- Mashhadi, F.; Asaduzzaman, A.; Mridha, M.F. A novel resource scheduling approach to improve the reliability of Shuffle-exchange networks. In Proceedings of the 2017 IEEE International Conference on Imaging, Vision & Pattern Recognition (icIVPR), Dhaka, Bangladesh, 13–14 February 2017; pp. 1–6. [Google Scholar]

- Jahanshahi, M.; Bistouni, F. A new approach to improve reliability of the multistage interconnection networks. Comput. Electr. Eng. 2014, 40, 348–374. [Google Scholar] [CrossRef]

- Bistouni, F.; Jahanshahi, M. Reliability analysis of multilayer multistage interconnection networks. Telecommun. Syst. 2016, 62, 529–551. [Google Scholar] [CrossRef]

- Cam, H. Analysis of shuffle-exchange networks under permutation trafic. In Switching Networks: Recent Advances; Springer: Boston, MA, USA, 2001; pp. 215–256. [Google Scholar] [CrossRef]

- Gaughan, P.T.; Dao, B.V.; Yalamanchili, S.; Schimmel, D.E. Distributed, deadlock-free routing in faulty, pipelined, direct interconnection networks. IEEE Trans. Comput. 1996, 45, 651–665. [Google Scholar] [CrossRef]

- Edirisooriya, S.; Edirisooriya, G. Distributing load in the presence of failures in extra-stage shuffle-exchange networks. In Proceedings of the IEEE 35th Midwest Symposium on Circuits and Systems, Washington, DC, USA, 9–12 August 1992; pp. 1404–1407. [Google Scholar] [CrossRef]

- Bistouni, F.; Jahanshahi, M. Determining the reliability importance of switching elements in the shuffle-exchange networks. Int. J. Parallel Emergent Distrib. Syst. 2019, 34, 448–476. [Google Scholar] [CrossRef]

- Chau, S.C.; Zhang, W.; Liestman, A.L. Fault Tolerance for Multistage Interconnection Networks. In Proceedings of the Fourth International Conference on Computing and Information: Computing and Information, Toronto, On, Canada, 28–30 May 1992; pp. 430–435. [Google Scholar] [CrossRef]

- Bistouni, F.; Jahanshahi, M. Evaluating failure rate of fault-tolerant multistage interconnection networks using Weibull life distribution. Reliab. Eng. Syst. Saf. 2015, 144, 128–146. [Google Scholar] [CrossRef]

- Yunus, N.A.M.; Othman, M. Reliability performance of shuffle exchange omega network. In Proceedings of the 2012 International Symposium on Telecommunication Technologies, Kuala Lumpur, Malaysia, 26–28 November 2012; pp. 26–30. [Google Scholar] [CrossRef]

- Ishii, M.; Hamilton, P. Multistage Interconnection Network and Parallel Computer Using the Same. U.S. Patent 5,852,407, 22 December 1998. [Google Scholar]

- Ahmad, W.; Hasan, O.; Pervez, U.; Qadir, J. Reliability modeling and analysis of communication networks. J. Netw. Comput. Appl. 2017, 78, 191–215. [Google Scholar] [CrossRef] [Green Version]

- Jones, A.K.; Schwarz, P. Experience using multiprocessor systems—A status report. ACM Comput. Surv. CSUR 1980, 12, 121–165. [Google Scholar] [CrossRef]

- Jereb, L. Network reliability: Models, measures and analysis. In Proceedings of the 6th IFIP Workshop on Performance Modeling and Evaluation of ATM Networks, Ilkley, UK, 20–22 July 1998; Volume 2. [Google Scholar]

- Fathi, E.T.; Krieger, M. Multiple microprocessor systems: What, why, and when. Computer 1983, 3, 23–32. [Google Scholar] [CrossRef]

- Khanna, G.; Mishra, R.; Chaturvedi, S.K. 4DGIN-3: A new design layout of 4-disjoint gamma interconnection network. J. Parallel Distrib. Comput. 2016, 98, 40–47. [Google Scholar] [CrossRef]

- Rajkumar, S.; Goyal, N.K. Design of 4-disjoint gamma interconnection network layouts and reliability analysis of gamma interconnection networks. J. Supercomput. 2014, 69, 468–491. [Google Scholar] [CrossRef]

- Bistouni, F.; Jahanshahi, M. Impact of Raising Switching Stages on the Reliability of Interconnection Networks. J. Inst. Electron. Comput. 2020, 2, 93–120. [Google Scholar] [CrossRef]

- Goldberg, B.E.; Everhart, K.; Stevens, R.; Babbitt III, N.; Clemens, P.; Stout, L. System Engineering Toolbox for Design-Oriented Engineers; NASA Reference Publication 1358; Marshall Space Flight Center: Huntsville, AL, USA, 1994. [Google Scholar]

- Dantas, J.; Matos, R.; Araujo, J.; Maciel, P. Models for dependability analysis of cloud computing architectures for eucalyptus platform. Int. Trans. Syst. Sci. Appl. 2012, 8, 13–25. [Google Scholar]

- Bistouni, F.; Jahanshahi, M. Reliability analysis of fault-tolerant bus-based interconnection networks. J. Electron. Test. 2016, 32, 541–568. [Google Scholar] [CrossRef]

- Rajkumar, S.; Goyal, N.K. Reliable multistage interconnection network design. Peer-to-Peer Netw. Appl. 2016, 9, 979–990. [Google Scholar] [CrossRef]

- Gunawan, I. Reliability analysis of shuffle-exchange network systems. Reliab. Eng. Syst. Saf. 2008, 93, 271–276. [Google Scholar] [CrossRef]

- Garofalakis, J.; Stergiou, E. An analytical model for the performance evaluation of multistage interconnection networks with two class priorities. Future Gener. Comput. Syst. 2013, 29, 114–129. [Google Scholar] [CrossRef]

- Chiang, C.M.; Bhattacharya, S.; Ni, L.M. Multicast in extra-stage multistage interconnection networks. In Proceedings of the IEEE 1994 6th IEEE Symposium on Parallel and Distributed Processing, Dallas, TX, USA, 26–29 October 1994; pp. 452–459. [Google Scholar] [CrossRef]

- García, P.J.; Quiles, F.J.; Flich, J.; Duato, J.; Johnson, I.; Naven, F. Efficient, scalable congestion management for interconnection networks. IEEE Micro 2006, 26, 52–66. [Google Scholar] [CrossRef]

- Tutsch, D.; Malek, M. Comparison of network-on-chip topologies for multicore systems considering multicast and local traffic. In Proceedings of the 2nd International Conference on Simulation Tools and Techniques, Rome, Italy, 2–6 March 2009; pp. 1–9. [Google Scholar] [CrossRef]

- Tutsch, D.; Hommel, G. MLMIN: A multicore processor and parallel computer network topology for multicast. Comput. Oper. Res. 2008, 35, 3807–3821. [Google Scholar] [CrossRef]

- Abd-El-Barr, M.; Al-Somani, T.F. Topological properties of hierarchical interconnection networks: A review and comparison. J. Electr. Comput. Eng. 2011, 2011, 189434. [Google Scholar] [CrossRef]

- Chalasani, S.; Varma, A.M. Method and Apparatus for Dynamic Detection and Routing of Non-Uniform Traffic in Parallel Buffered Multistage Interconnection Networks. U.S. Patent 5,274,782, 28 December 1993. [Google Scholar]

- Du, W.; Lin, Y.; Jiang, L. Method, System and Node for Backpressure in Multistage Switching Network. U.S. Patent 8,102,763, 24 January 2012. [Google Scholar]

- Brenner, M.; Zimmermann, A. Analysis of Delay Time Distributions in Multistage Interconnection Networks Considering Multicast Traffic. In Proceedings of the 2008 Seventh IEEE International Symposium on Network Computing and Applications, Cambridge, MA, USA, 10–12 July 2008; pp. 236–239. [Google Scholar] [CrossRef] [Green Version]

- Dongarra, J. Report on the Fujitsu Fugaku system. In University of Tennessee-Knoxville Innovative Computing Laboratory; Tech Report No. ICL-UT-20-06; University of Tennessee: Knoxville, TN, USA, 2020. [Google Scholar]

- Aljundi, A.C.; Dekeyser, J.L.; Kechadi, M.T. On the scalability of multistage interconnection networks. In Proceedings of the IEEE 2004 International Conference on Information and Communication Technologies: From Theory to Applications, Damascus, Syria, 23 April 2004; pp. 655–656. [Google Scholar] [CrossRef]

- Kumar, V.P.; Reibman, A.L. Failure dependent performance analysis of a fault-tolerant multistage interconnection network. IEEE Trans. Comput. 1989, 38, 1703–1713. [Google Scholar] [CrossRef]

- Mnejja, S.; Aydi, Y.; Abid, M.; Monteleone, S.; Catania, V.; Palesi, M.; Patti, D. Delta Multi-Stage Interconnection Networks for Scalable Wireless On-Chip Communication. Electronics 2020, 9, 913. [Google Scholar] [CrossRef]

- Sabbaghi-Nadooshan, R. Analytical performance modeling of shuffle–exchange inspired mesh-based Network-on-Chips. Perform. Eval. 2013, 70, 934–947. [Google Scholar] [CrossRef]

- Aydi, Y.; Tligue, R.; Abid, M.; Dekeyser, J.L. Exploring multistage interconnection network implementations for FPGA-based MPSOCs. In Proceedings of the 2009 4th International Design and Test Workshop (IDT), Riyadh, Saudi Arabia, 15–17 November 2009; pp. 1–6. [Google Scholar] [CrossRef]

- Mazaheri, A.; Sabbaghi-Nadooshan, R. Fault-tolerant MIN Shuffle-Exchange NoC. In Proceedings of the IEEE 2013 21st Iranian Conference on Electrical Engineering (ICEE), Mashhad, Iran, 14–16 May 2013; pp. 1–6. [Google Scholar] [CrossRef]

| Aspects | References | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| [1] | [20] | [21] | [6] | [22] | [23] | [24] | [25] | [26] | [27] | ||

| Metric/Objective | Cost | • | • | ✓ | ✓ | • | • | • | • | ✓ | ✓ |

| Delay | • | • | • | ✓ | • | • | • | • | • | • | |

| Latency | • | • | • | • | • | ✓ | ✓ | ✓ | • | • | |

| Complexity | • | • | • | ✓ | • | • | • | ✓ | • | • | |

| Reliability | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | • | ✓ | ✓ | |

| Fault-tolerance | • | • | • | ✓ | • | ✓ | ✓ | ✓ | ✓ | ✓ | |

| Feature | Min. Path set Graph | • | • | • | • | ✓ | • | • | • | • | • |

| Logic graph | • | • | • | • | ✓ | • | • | • | • | • | |

| MUX/DEMUX | ✓ | • | ✓ | ✓ | • | ✓ | • | • | ✓ | ✓ | |

| Loop | ✓ | • | • | • | • | • | • | • | • | • | |

| Replication/Parallelism | ✓ | ✓ | • | • | • | • | • | • | ✓ | • | |

| Stage+ | • | • | • | • | • | • | ✓ | • | ✓ | • | |

| Stage− | • | • | • | • | ✓ | • | ✓ | • | • | ✓ | |

| Re-arranged link | • | • | • | ✓ | • | • | • | • | • | • | |

| Multi-internal path | ✓ | • | ✓ | • | • | • | • | • | ✓ | • | |

| Disjoint path | • | • | • | • | • | ✓ | • | • | • | • | |

| Bi-directional | • | • | • | • | ✓ | • | • | • | • | • | |

| Broadcast | • | • | • | • | ✓ | • | • | ✓ | ✓ | ✓ | |

| Multicast | • | • | ✓ | • | • | • | • | ✓ | • | • | |

| New Fabric | • | • | • | • | • | • | ✓ | • | • | • | |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Amodu, O.A.; Othman, M.; Yunus, N.A.M.; Hanapi, Z.M. A Primer on Design Aspects and Recent Advances in Shuffle Exchange Multistage Interconnection Networks. Symmetry 2021, 13, 378. https://doi.org/10.3390/sym13030378

Amodu OA, Othman M, Yunus NAM, Hanapi ZM. A Primer on Design Aspects and Recent Advances in Shuffle Exchange Multistage Interconnection Networks. Symmetry. 2021; 13(3):378. https://doi.org/10.3390/sym13030378

Chicago/Turabian StyleAmodu, Oluwatosin Ahmed, Mohamed Othman, Nur Arzilawati Md Yunus, and Zurina Mohd Hanapi. 2021. "A Primer on Design Aspects and Recent Advances in Shuffle Exchange Multistage Interconnection Networks" Symmetry 13, no. 3: 378. https://doi.org/10.3390/sym13030378