Array of Graphene Variable Capacitors on 100 mm Silicon Wafers for Vibration-Based Applications

Abstract

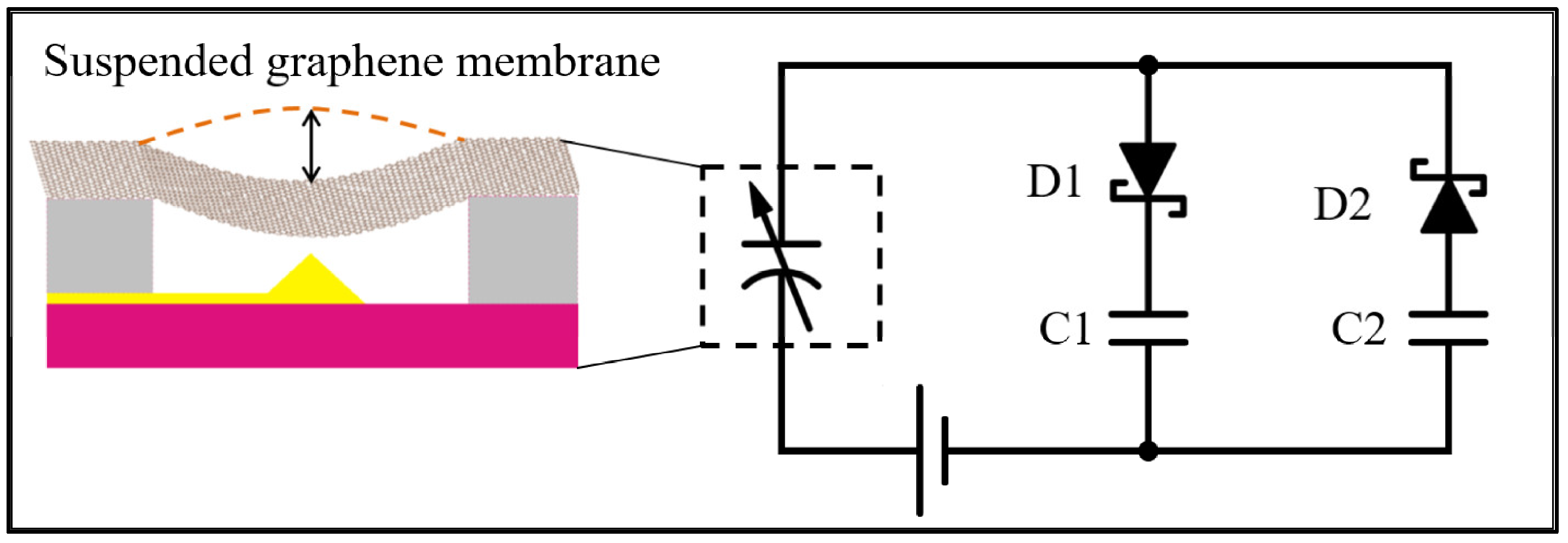

:1. Introduction

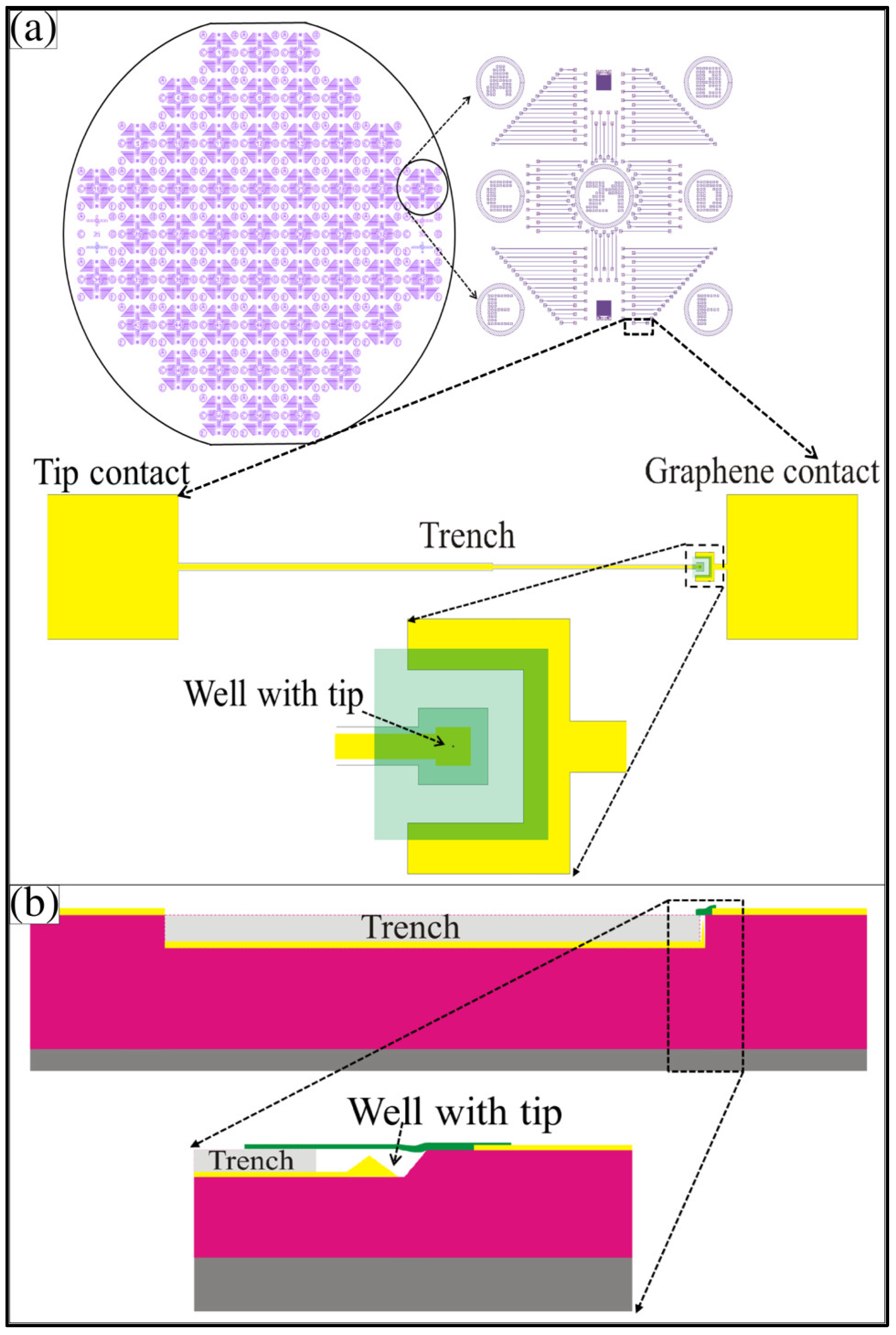

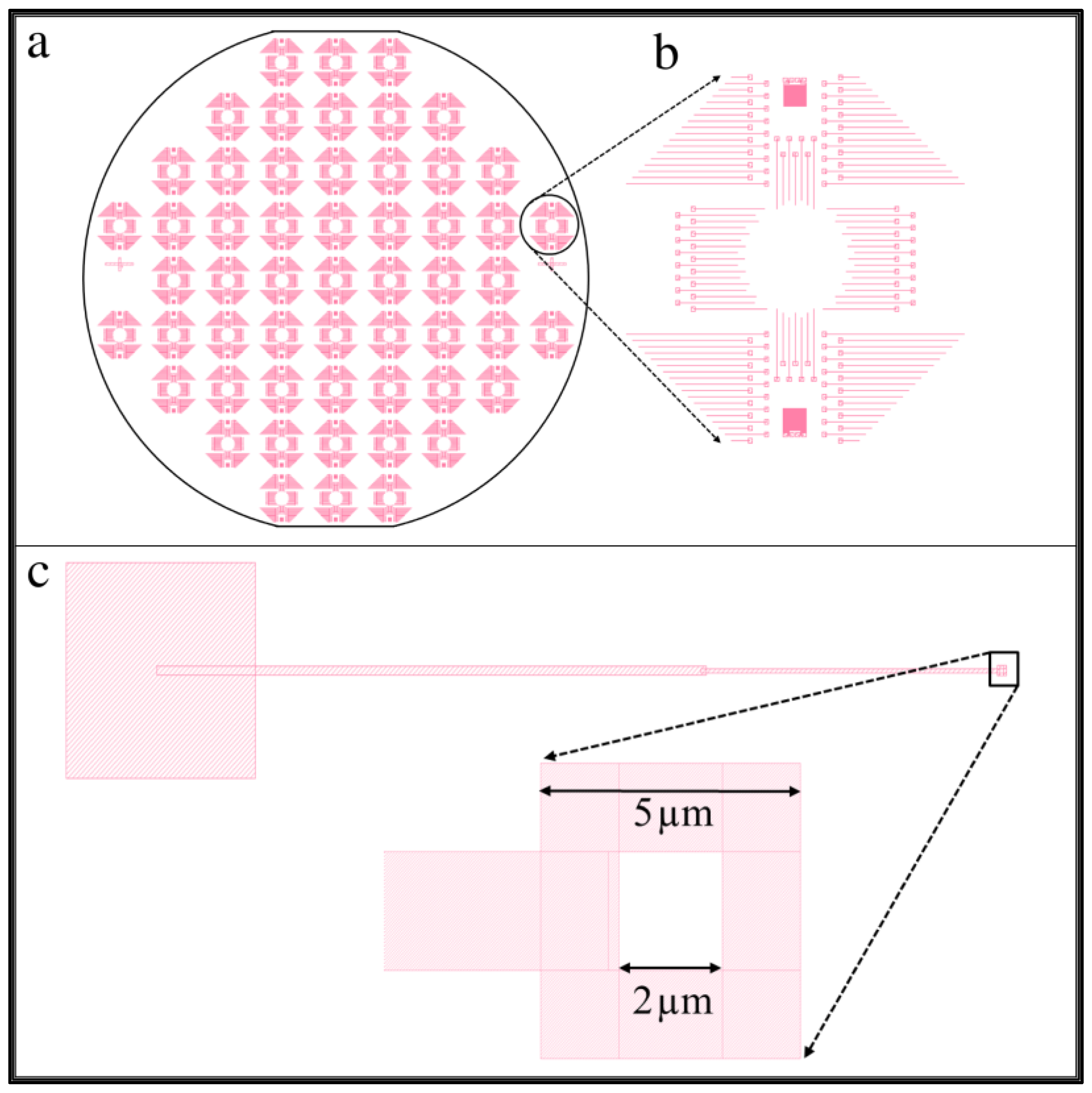

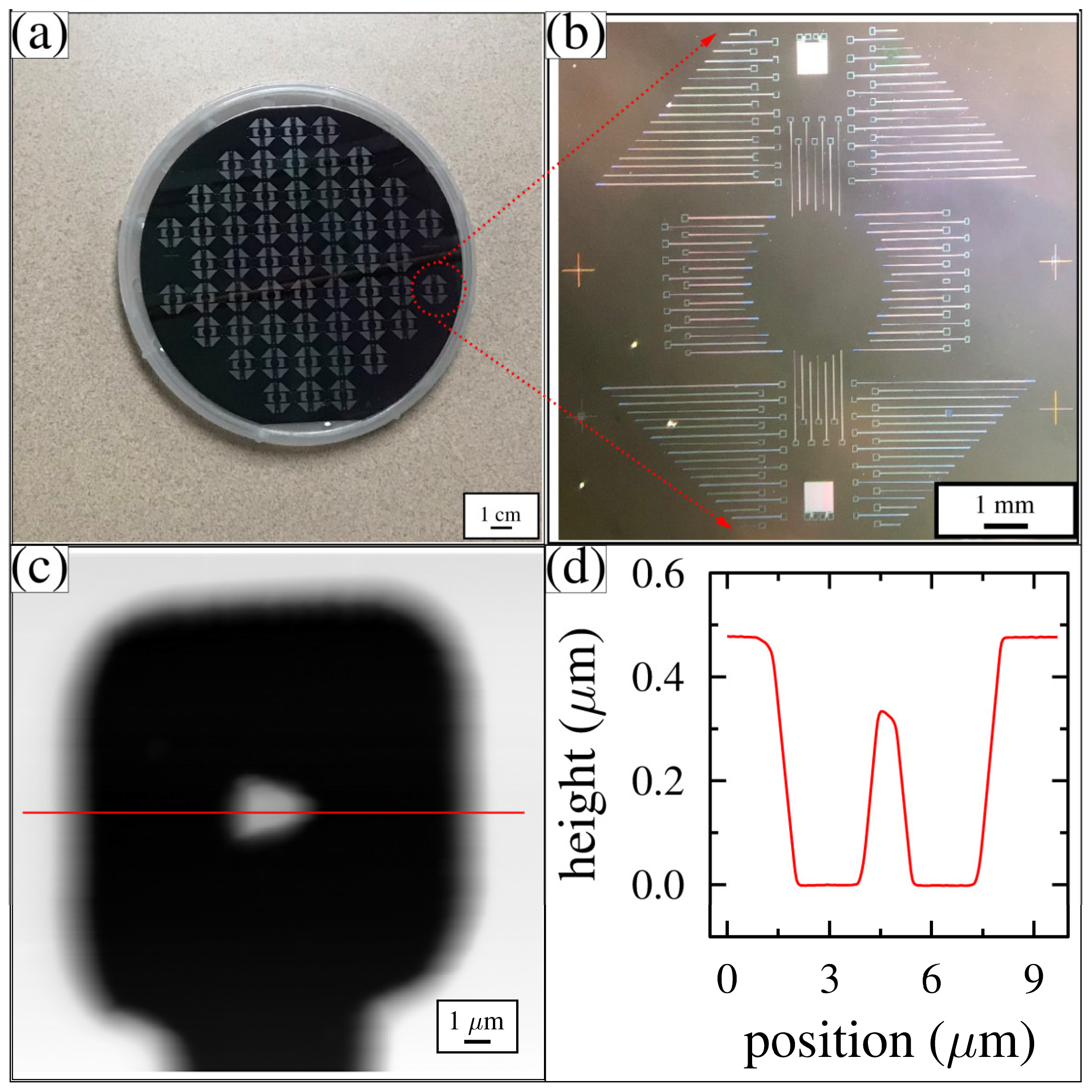

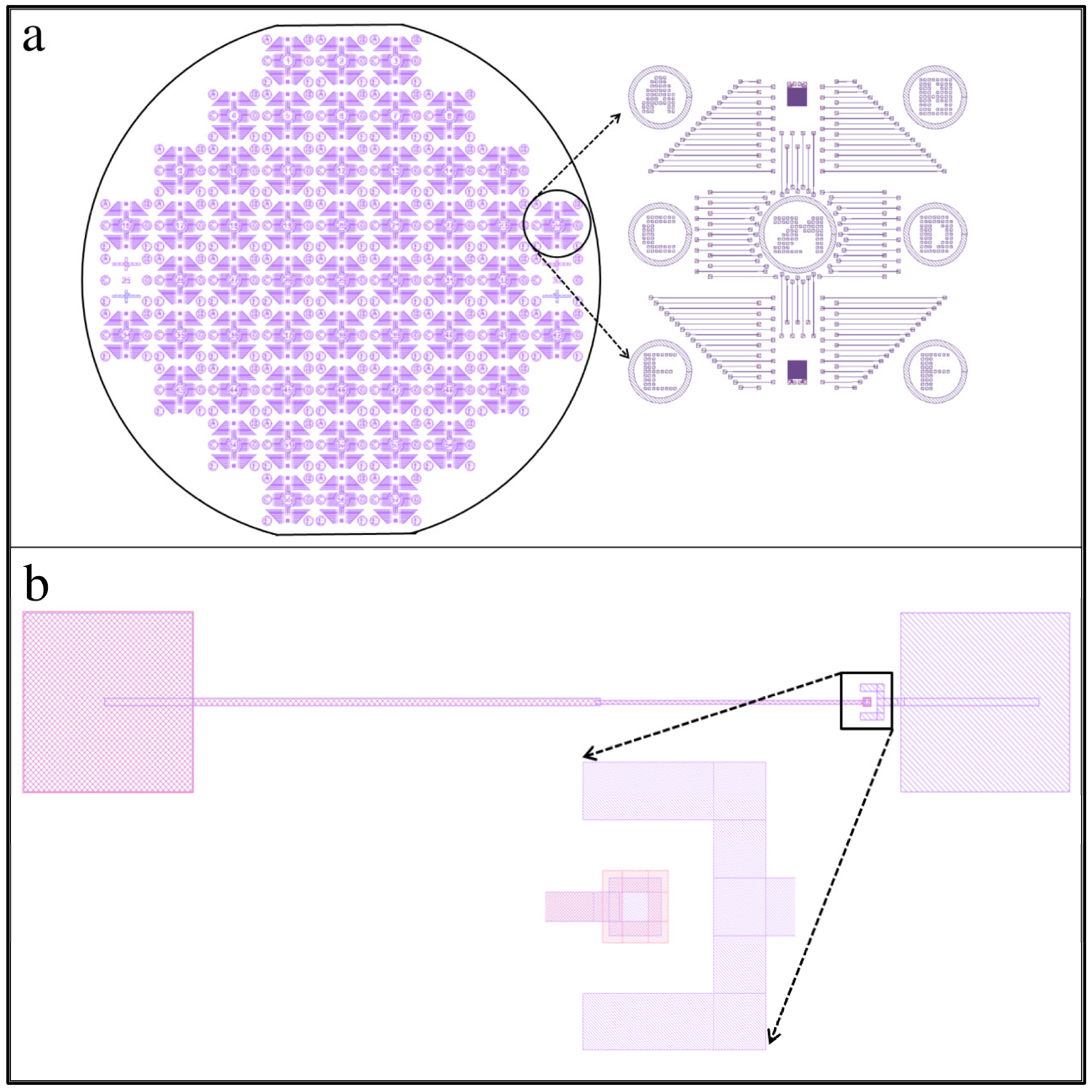

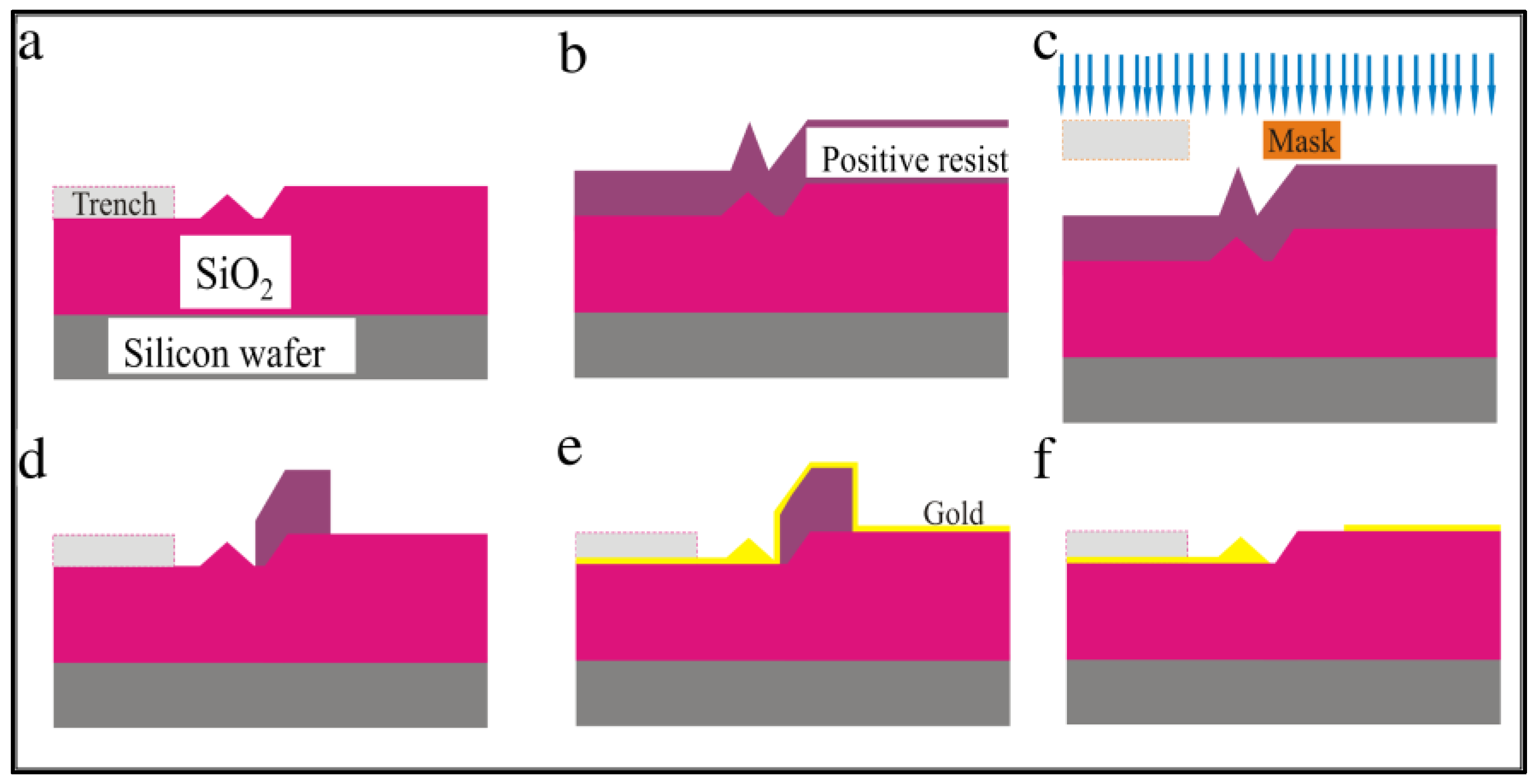

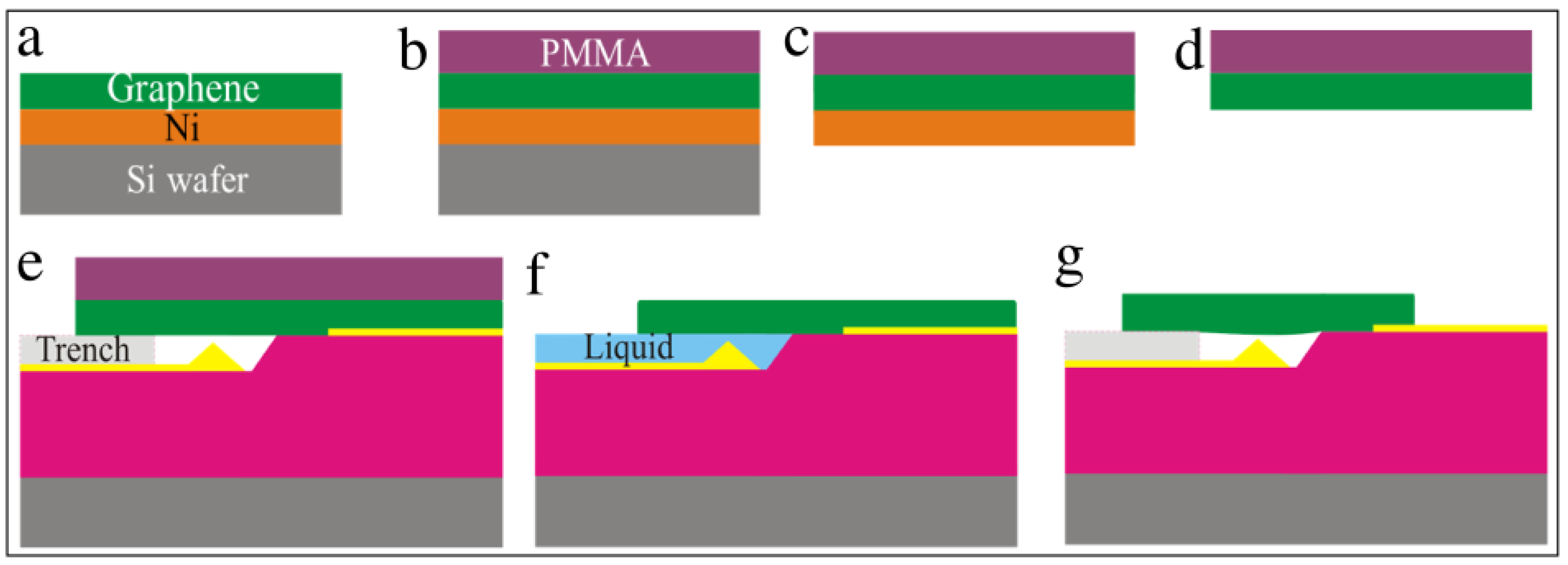

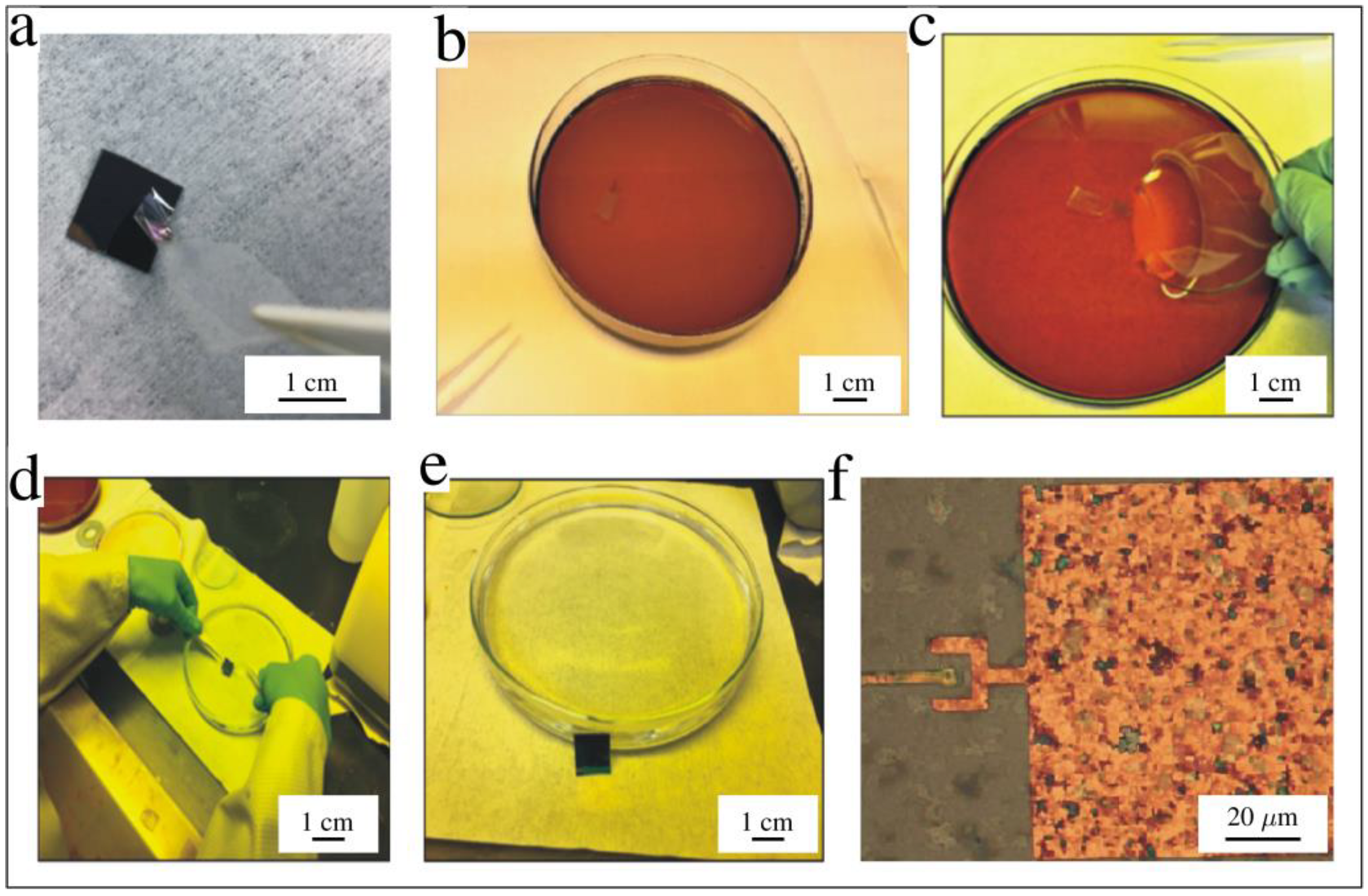

2. Materials and Methods

3. Results and Discussion

3.1. Mask 1 Processes: Trench, Well, and Tip

3.2. Mask 2 Processes: Metal Traces and Bonding Pads

3.3. Graphene Membrane Placement and Suspension

3.4. Processing Bare Die with a Subsurface Integrated Circuit

3.5. Capacitance Characterization

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Li, J.; Wang, X. Research Update: Materials design of implantable nanogenerators for biomechanical energy harvesting. APL Mater. 2017, 5, 073801. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Cook-Chennault, K.A.; Thambi, N.; Bitetto, M.A.; Hameyie, E.B. Piezoelectric Energy Harvesting: A Green and Clean Alternative for Sustained Power Production. Bull. Sci. Technol. Soc. 2008, 28, 496–509. [Google Scholar] [CrossRef]

- Edlund, C.; Ramakrishnan, S. An analytic study of vibrational energy harvesting using piezoelectric tiles in stairways subjected to human traffic. Eur. J. Appl. Math. 2019, 30, 968–985. [Google Scholar] [CrossRef]

- Priya, S.; Song, H.-C.; Zhou, Y.; Varghese, R.; Chopra, A.; Kim, S.-G.; Kanno, I.; Wu, L.; Ha, D.S.; Ryu, J.; et al. A Review on Piezoelectric Energy Harvesting: Materials, Methods, and Circuits. Energy Harvest. Syst. 2017, 4, 3–39. [Google Scholar] [CrossRef]

- Chandrakasan, A.; Amirtharajah, R.; Goodman, J.; Rabiner, W. Trends in low power digital signal processing. In Proceedings of the 1998 IEEE International Symposium on Circuits and Systems (ISCAS), Monterey, CA, USA, 31 May–3 June 1998; IEEE: New York, NY, USA, 1998; Volume 4, pp. 604–607. [Google Scholar]

- Atienza, D.; Ayala, J.L. Special Issue of GLSVLSI 2011: Current Trends on VLSI and Ultra Low-Power Design; Elsevier: Amsterdam, The Netherlands, 2012; Volume 45, pp. 229–438. [Google Scholar]

- Alioto, M. Ultra-Low Power VLSI Circuit Design Demystified and Explained: A Tutorial. IEEE Trans. Circuits Syst. I Regul. Pap. 2012, 59, 3–29. [Google Scholar] [CrossRef]

- Bae, S.-H.; Kahya, O.; Sharma, B.K.; Kwon, J.; Cho, H.J.; Özyilmaz, B.; Ahn, J.-H. Graphene-P(VDF-TrFE) Multilayer Film for Flexible Applications. ACS Nano 2013, 7, 3130–3138. [Google Scholar] [CrossRef]

- Schlicke, H.; Rebber, M.; Kunze, S.; Vossmeyer, T. Resistive pressure sensors based on freestanding membranes of gold nanoparticles. Nanoscale 2016, 8, 183–186. [Google Scholar] [CrossRef] [Green Version]

- le Ouay, B.; Guldin, S.; Luo, Z.; Allegri, S.; Stellacci, F. Freestanding Ultrathin Nanoparticle Membranes Assembled at Transient Liquid-Liquid Interfaces. Adv. Mater. Interfaces 2016, 3, 1600191. [Google Scholar] [CrossRef] [Green Version]

- Bunch, J.S.; van der Zande, A.M.; Verbridge, S.S.; Frank, I.W.; Tanenbaum, D.M.; Parpia, J.M.; Craighead, H.G.; McEuen, P.L. Electromechanical Resonators from Graphene Sheets. Science 2007, 315, 490–493. [Google Scholar] [CrossRef] [Green Version]

- de Alba, R.; Abhilash, T.S.; Hui, A.; Storch, I.R.; Craighead, H.G.; Parpia, J.M. Temperature-dependence of stress and elasticity in wet-transferred graphene membranes. J. Appl. Phys. 2018, 123, 095109. [Google Scholar] [CrossRef]

- Li, X.; Zhang, R.; Yu, W.; Wang, K.; Wei, J.; Wu, D.; Cao, A.; Li, Z.; Cheng, Y.; Zheng, Q.; et al. Stretchable and highly sensitive graphene-on-polymer strain sensors. Sci. Rep. 2012, 2, 870. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Lee, J.-H.; Park, S.-J.; Choi, J.-W. Electrical Property of Graphene and Its Application to Electrochemical Biosensing. Nanomaterials 2019, 9, 297. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Wu, Y.; Farmer, D.B.; Xia, F.; Avouris, P. Graphene Electronics: Materials, Devices, and Circuits. Proc. IEEE 2013, 101, 1620–1637. [Google Scholar] [CrossRef]

- Naumis, G.G.; Barraza-Lopez, S.; Oliva-Leyva, M.; Terrones, H. Electronic and optical properties of strained graphene and other strained 2D materials: A review. Rep. Prog. Phys. 2017, 80, 096501. [Google Scholar] [CrossRef] [PubMed]

- Jiang, J.-W.; Wang, B.-S.; Wang, J.-S.; Park, H.S. A review on the flexural mode of graphene: Lattice dynamics, thermal conduction, thermal expansion, elasticity and nanomechanical resonance. J. Phys. Condens. Matter 2015, 27, 083001. [Google Scholar] [CrossRef] [Green Version]

- Sang, M.; Shin, J.; Kim, K.; Yu, K. Electronic and Thermal Properties of Graphene and Recent Advances in Graphene Based Electronics Applications. Nanomaterials 2019, 9, 374. [Google Scholar] [CrossRef] [Green Version]

- Meyer, J.C.; Geim, A.K.; Katsnelson, M.I.; Novoselov, K.S.; Booth, T.J.; Roth, S. The structure of suspended graphene sheets. Nature 2007, 446, 60–63. [Google Scholar] [CrossRef]

- Geim, A.K.; Novoselov, K.S. The rise of graphene. Nat. Mater. 2007, 6, 183–191. [Google Scholar] [CrossRef]

- He, N.; Pan, Q.; Liu, Y.; Gao, W. Graphene-Fiber-Based Supercapacitors Favor N-Methyl-2-pyrrolidone/Ethyl Acetate as the Spinning Solvent/Coagulant Combination. ACS Appl. Mater. Interfaces 2017, 9, 24568–24576. [Google Scholar] [CrossRef]

- Huang, Y.; Liang, J.; Chen, Y. An Overview of the Applications of Graphene-Based Materials in Supercapacitors. Small 2012, 8, 1805–1834. [Google Scholar] [CrossRef]

- Yin, Z.; Wu, S.; Zhou, X.; Huang, X.; Zhang, Q.; Boey, F.; Zhang, H. Electrochemical Deposition of ZnO Nanorods on Transparent Reduced Graphene Oxide Electrodes for Hybrid Solar Cells. Small 2010, 6, 307–312. [Google Scholar] [CrossRef] [PubMed]

- Smith, A.D.; Niklaus, F.; Paussa, A.; Vaziri, S.; Fischer, A.C.; Sterner, M.; Forsberg, F.; Delin, A.; Esseni, D.; Palestri, P.; et al. Electromechanical Piezoresistive Sensing in Suspended Graphene Membranes. Nano Lett. 2013, 13, 3237–3242. [Google Scholar] [CrossRef] [PubMed]

- Khan, Z.H.; Kermany, A.R.; Öchsner, A.; Iacopi, F. Mechanical and electromechanical properties of graphene and their potential application in MEMS. J. Phys. D Appl. Phys. 2017, 50, 053003. [Google Scholar] [CrossRef] [Green Version]

- Zang, X.; Zhou, Q.; Chang, J.; Liu, Y.; Lin, L. Graphene and carbon nanotube (CNT) in MEMS/NEMS applications. Microelectron. Eng. 2015, 132, 192–206. [Google Scholar] [CrossRef]

- Khan, A.U.; Zeltzer, G.; Speyer, G.; Croft, Z.L.; Guo, Y.; Nagar, Y.; Artel, V.; Levi, A.; Stern, C.; Naveh, D.; et al. Mutually Reinforced Polymer—Graphene Bilayer Membranes for Energy-Efficient Acoustic Transduction. Adv. Mater. 2021, 33, 2004053. [Google Scholar] [CrossRef]

- AbdelGhany, M.; Ledwosinska, E.; Szkopek, T. Theory of the suspended graphene varactor. Appl. Phys. Lett. 2012, 101, 153102. [Google Scholar] [CrossRef]

- AbdelGhany, M.; Mahvash, F.; Mukhopadhyay, M.; Favron, A.; Martel, R.; Siaj, M.; Szkopek, T. Suspended graphene variable capacitor. 2D Mater. 2016, 3, 041005. [Google Scholar] [CrossRef] [Green Version]

- Liang, X.; Sperling, B.A.; Calizo, I.; Cheng, G.; Hacker, C.A.; Zhang, Q.; Obeng, Y.; Yan, K.; Peng, H.; Li, Q.; et al. Toward Clean and Crackless Transfer of Graphene. ACS Nano 2011, 5, 9144–9153. [Google Scholar] [CrossRef]

- Avouris, P. Graphene: Electronic and Photonic Properties and Devices. Nano Lett. 2010, 10, 4285–4294. [Google Scholar] [CrossRef]

- Andrei, E.Y.; Li, G.; Du, X. Electronic properties of graphene: A perspective from scanning tunneling microscopy and magnetotransport. Rep. Prog. Phys. 2012, 75, 056501. [Google Scholar] [CrossRef] [Green Version]

- Beeby, S.P.; Tudor, M.J.; White, N.M. Energy harvesting vibration sources for microsystems applications. Meas. Sci. Technol. 2006, 17, R175–R195. [Google Scholar] [CrossRef]

- Kim, S.-G.; Priya, S.; Kanno, I. Energy Frontier Research, C. Solid-State Solar-Thermal Energy Conversion, Piezoelectric MEMS for energy harvesting. MRS Bull. 2012, 37, 1039–1050. [Google Scholar] [CrossRef] [Green Version]

- Lopez-Suarez, M.; Rurali, R.; Gammaitoni, L.; Abadal, G. Nanostructured graphene for energy harvesting. Phys. Rev. B 2011, 84, 161401. [Google Scholar] [CrossRef]

- Meninger, S.; Mur-Miranda, J.O.; Amirtharajah, R.; Chandrakasan, A.P.; Lang, J.H. Vibration-to-electric energy conversion. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2001, 9, 64–76. [Google Scholar] [CrossRef]

- Mitcheson, P.D.; Miao, P.; Stark, B.H.; Yeatman, E.M.; Holmes, A.S.; Green, T.C. MEMS electrostatic micropower generator for low frequency operation. Sens. Actuators A Phys. 2004, 115, 523–529. [Google Scholar] [CrossRef] [Green Version]

- Yen, B.C.; Lang, J.H. A variable-capacitance vibration-to-electric energy harvester. IEEE Trans. Circuits Syst. 2006, 53, 288–295. [Google Scholar] [CrossRef]

- Greene, N.R. Energy Flow for a Variable-Gap Capacitor. Phys. Teach. 2005, 43, 340–343. [Google Scholar] [CrossRef]

- Philp, S.F. The Vacuum-Insulated, Varying-Capacitance Machine. IEEE Trans. Electr. Insul. 1977, EI-12, 130–136. [Google Scholar] [CrossRef]

- Harerimana, F.; Peng, H.; Otobo, M.; Luo, F.; Gikunda, M.N.; Mangum, J.M.; Labella, V.P.; Thibado, P.M. Efficient circuit design for low power energy harvesting. AIP Adv. 2020, 10, 105006. [Google Scholar] [CrossRef]

- Thibado, P.M.; Kumar, P.; Singh, S.; Ruiz-Garcia, M.; Lasanta, A.; Bonilla, L.L. Fluctuation-induced current from freestanding graphene. Phys. Rev. E 2020, 102, 042101. [Google Scholar] [CrossRef]

- Ristic, L. Sensor Technology and Devices. Meas. Sci. Technol. 2000, 11, 1829–1830. [Google Scholar]

- French, P.J. Development of surface micromachining techniques compatible with on-chip electronics. J. Micromech. Microeng. 1996, 6, 197–211. [Google Scholar] [CrossRef]

- Avis, C.; Jang, J. Understanding the Origin of the Hysteresis of High-Performance Solution Processed Polycrystalline SnO2 Thin-Film Transistors and Applications to Circuits. Membranes 2022, 12, 7. [Google Scholar] [CrossRef] [PubMed]

- Woo, G.; Yoo, H.; Kim, T. Hybrid Thin-Film Materials Combinations for Complementary Integration Circuit Implementation. Membranes 2021, 11, 931. [Google Scholar] [CrossRef] [PubMed]

- Yue, D.W.; Rong, X.M.; Han, S.; Cao, P.J.; Zeng, Y.X.; Xu, W.Y.; Fang, M.; Liu, W.J.; Zhu, D.L.; Lu, Y.M. High Photoresponse Black Phosphorus TFTs Capping with Transparent Hexagonal Boron Nitride. Membranes 2021, 11, 952. [Google Scholar] [CrossRef] [PubMed]

- Lee, S.S. An Empirical Modeling of Gate Voltage-Dependent Behaviors of Amorphous Oxide Semiconductor Thin-Film Transistors including Consideration of Contact Resistance and Disorder Effects at Room Temperature. Membranes 2021, 11, 954. [Google Scholar] [CrossRef]

- Kao, C.H.; Liu, C.S.; Chan, S.M.; Kuo, C.C.; Tsai, S.C.; Lee, M.L.; Chen, H. Effects of NH3 Plasma and Mg Doping on InGaZnO pH Sensing Membrane. Membranes 2021, 11, 994. [Google Scholar] [CrossRef]

- Bagolini, A.; Correale, R.; Picciotto, A.; di Lorenzo, M.; Scapinello, M. MEMS Membranes with Nanoscale Holes for Analytical Applications. Membranes 2021, 11, 74. [Google Scholar] [CrossRef]

- Yusof, N.; Bais, B.; Yunas, J.; Soin, N.; Majlis, B.Y. Fabrication of Suspended PMMA-Graphene Membrane for High Sensitivity LC-MEMS Pressure Sensor. Membranes 2021, 11, 996. [Google Scholar] [CrossRef]

- Moreau, W.M. Semiconductor Lithography: Principles, Practices, and Materials; Springer: Berlin/Heidelberg, Germany, 2012. [Google Scholar]

- Seidler, P. Optimized process for fabrication of free-standing silicon nanophotonic devices. J. Vac. Sci. Technol. B 2017, 35, 031209. [Google Scholar] [CrossRef] [Green Version]

- Pal, P.; Sato, K. Fabrication methods based on wet etching process for the realization of silicon MEMS structures with new shapes. Microsyst. Technol. 2010, 16, 1165–1174. [Google Scholar] [CrossRef]

- Wang, C.A.; Shiau, D.A.; Murphy, P.G.; O’Brien, P.W.; Huang, R.K.; Connors, M.K.; Anderson, A.C.; Donetsky, D.; Anikeev, S.; Belenky, G.; et al. Wafer bonding and epitaxial transfer of GaSb-based epitaxy to GaAs for monolithic interconnection of thermophotovoltaic devices. J. Electron. Mater. 2004, 33, 213–217. [Google Scholar] [CrossRef] [Green Version]

- Liang, D.; Fang, A.; Oakley, D.; Napoleone, A.; Chapman, D.; Chen, C.-L.; Juodawlkis, P.; Raday, O.; Bowers, J.E. 150 mm InP-to-Silicon Direct Wafer Bonding for Silicon Photonic Integrated Circuits. ECS Trans. 2019, 16, 235–241. [Google Scholar] [CrossRef]

- Nam, J.; Lee, Y.; Choi, W.; Kim, C.S.; Kim, H.; Kim, J.; Kim, D.-H.; Jo, S. Transfer Printed Flexible and Stretchable Thin Film Solar Cells Using a Water-Soluble Sacrificial Layer. Adv. Energy Mater. 2016, 6, 1601269. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Gikunda, M.N.; Harerimana, F.; Mangum, J.M.; Rahman, S.; Thompson, J.P.; Harris, C.T.; Churchill, H.O.H.; Thibado, P.M. Array of Graphene Variable Capacitors on 100 mm Silicon Wafers for Vibration-Based Applications. Membranes 2022, 12, 533. https://doi.org/10.3390/membranes12050533

Gikunda MN, Harerimana F, Mangum JM, Rahman S, Thompson JP, Harris CT, Churchill HOH, Thibado PM. Array of Graphene Variable Capacitors on 100 mm Silicon Wafers for Vibration-Based Applications. Membranes. 2022; 12(5):533. https://doi.org/10.3390/membranes12050533

Chicago/Turabian StyleGikunda, Millicent N., Ferdinand Harerimana, James M. Mangum, Sumaya Rahman, Joshua P. Thompson, Charles Thomas Harris, Hugh O. H. Churchill, and Paul M. Thibado. 2022. "Array of Graphene Variable Capacitors on 100 mm Silicon Wafers for Vibration-Based Applications" Membranes 12, no. 5: 533. https://doi.org/10.3390/membranes12050533

APA StyleGikunda, M. N., Harerimana, F., Mangum, J. M., Rahman, S., Thompson, J. P., Harris, C. T., Churchill, H. O. H., & Thibado, P. M. (2022). Array of Graphene Variable Capacitors on 100 mm Silicon Wafers for Vibration-Based Applications. Membranes, 12(5), 533. https://doi.org/10.3390/membranes12050533