Charging Effect by Fluorine-Treatment and Recess Gate for Enhancement-Mode on AlGaN/GaN High Electron Mobility Transistors

Abstract

:1. Introduction

2. Device Fabrication and Electrical Characterization

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Dora, Y.; Chakraborty, A.; Mccarthy, L.; Keller, S.; Denbaars, S.P.; Mishra, U.K. High Breakdown Voltage Achieved on AlGaN/GaN HEMTs With Integrated Slant Field Plates. IEEE Electron Device Lett. 2006, 27, 713–715. [Google Scholar] [CrossRef]

- Moens, P.; Banerjee, A.; Uren, M.J.; Meneghini, M.; Karboyan, S.; Chatterjee, I.; Vanmeerbeek, P.; Cäsar, M.; Liu, C.; Salih, A.; et al. Impact of buffer leakage on intrinsic reliability of 650V AlGaN/GaN HEMTs. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 35.2.1–35.2.4. [Google Scholar]

- Ando, Y.; Kaneki, S.; Hashizume, T. Improved operation stability of Al2O3/AlGaN/GaN MOS high-electron-mobility transistors grown on GaN substrates. Appl. Phys. Express 2019, 12, 024002. [Google Scholar] [CrossRef]

- Sippel, J.C.; Islam, S.S.; Mukheijee, S.S. A physics-based analytical model of a GaN/AlGaN HEMT incorporating spontaneous and piezoelectric polarization. In Proceedings of the Canadian Conference on Electrical and Computer Engineering 2004 (IEEE Cat. No.04CH37513), Niagara Falls, ON, Canada, 2–5 May 2004; Volume 3, pp. 1401–1404. [Google Scholar]

- Chiu, H.-C.; Yang, C.-W.; Chen, C.-H.; Fu, J.S.; Chien, F.-T. Characterization of enhancement-mode AlGaN/GaN high electron mobility transistor using N2O plasma oxidation technology. Appl. Phys. Lett. 2011, 99, 153508. [Google Scholar] [CrossRef]

- Palacios, T.; Suh, C.-S.; Chakraborty, A.; Keller, S.; DenBaars, S.P.; Mishra, U.K. High-performance E-mode AlGaN/GaN HEMTs. IEEE Electron Device Lett. 2006, 27, 428–430. [Google Scholar] [CrossRef]

- Majumdar, S.; Sahu, C.; Biswas, D. Fabrication of E-mode InGaN/AlGaN/GaN HEMT using FIB based lithography. In Proceedings of the 2017 IEEE Electron Devices Technology and Manufacturing Conference (EDTM), Toyama, Japan, 28 February–2 March 2017; pp. 175–177. [Google Scholar]

- Lee, F.; Su, L.-Y.; Wang, C.-H.; Wu, Y.-R.; Huang, J. Impact of Gate Metal on the Performance of p-GaN/AlGaN/GaN High Electron Mobility Transistors. IEEE Electron Device Lett. 2015, 36, 232–234. [Google Scholar] [CrossRef]

- Dutta Gupta, S.; Soni, A.; Joshi, V.; Kumar, J.; Sengupta, R.; Khand, H.; Shankar, B.; Mohan, N.; Raghavan, S.; Bhat, N.; et al. Positive Threshold Voltage Shift in AlGaN/GaN HEMTs and E-Mode Operation By AlxTi1−xO Based Gate Stack Engineering. IEEE Trans. Electron Devices 2019, 66, 2544–2550. [Google Scholar] [CrossRef]

- Wu, T.-L.; Franco, J.; Marcon, D.; De Jaeger, B.; Bakeroot, B.; Stoffels, S.; Van Hove, M.; Groeseneken, G.; Decoutere, S. Toward Understanding Positive Bias Temperature Instability in Fully Recessed-Gate GaN MISFETs. IEEE Trans. Electron Devices 2016, 63, 1853–1860. [Google Scholar] [CrossRef]

- Lagger, P.; Ostermaier, C.; Pobegen, G.; Pogany, D. Towards understanding the origin of threshold voltage instability of AlGaN/GaN MIS-HEMTs. In Proceedings of the 2012 International Electron Devices Meeting, San Francisco, CA, USA, 10–13 December 2012; pp. 13.1.1–13.1.4. [Google Scholar]

- Kim, K.-W.; Jung, S.-D.; Kim, D.-S.; Kang, H.-S.; Im, K.-S.; Oh, J.-J.; Ha, J.-B.; Shin, J.-K.; Lee, J.-H. Effects of TMAH Treatment on Device Performance of Normally Off Al2O3/GaN MOSFET. IEEE Electron Device Lett. 2011, 32, 1376–1378. [Google Scholar] [CrossRef]

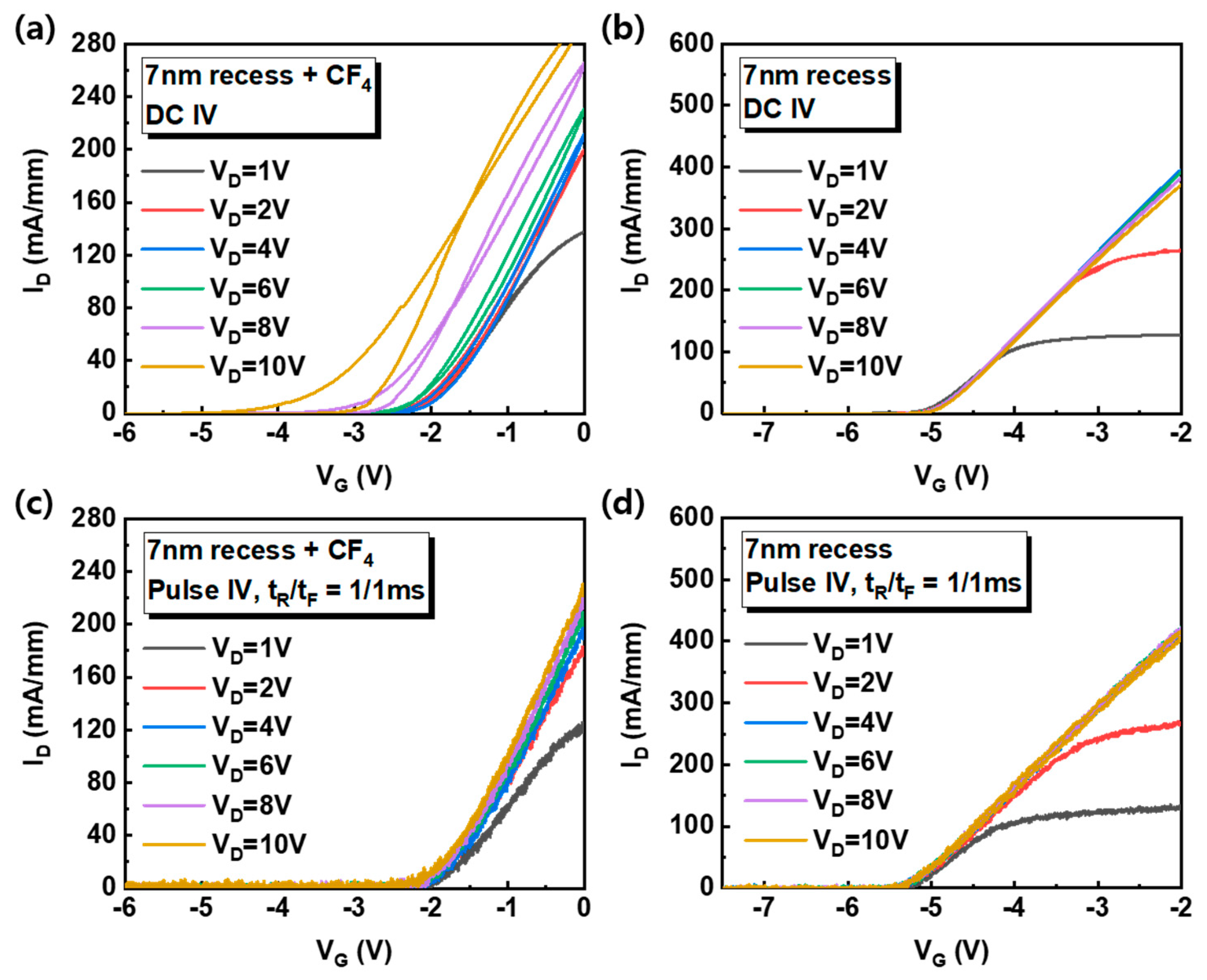

- Jung, H.-W.; Chang, S.-J.; Do, J.-W.; Ahn, H.-K.; Cho, K.-J.; Kim, J.-J.; Kim, S.-I.; Min, B.-G.; Kim, H.; Yoon, H.S.; et al. DC and RF Characteristics of Enhancement-Mode Al2O3/AlGaN/GaN MIS-HEMTs Fabricated by Shallow Recess Combined with Fluorine-Treatment and Deep Recess. ECS J. Solid State Sci. Technol. 2018, 7, 197–200. [Google Scholar] [CrossRef]

- Wang, Y.; Wang, M.; Xie, B.; Wen, C.P.; Wang, J.; Hao, Y.; Wu, W.; Chen, K.J.; Shen, B. High-Performance Normally-Off Al2O3/GaN MOSFET Using a Wet Etching-Based Gate Recess Technique. IEEE Electron Device Lett. 2013, 34, 1370–1372. [Google Scholar] [CrossRef]

- Li, S.; Hu, Q.; Wang, X.; Li, T.; Li, X.; Wu, Y. Improved Interface Properties and Dielectric Breakdown in Recessed AlGaN/GaN MOS-HEMTs Using HfSiOx as Gate Dielectric. IEEE Electron Device Lett. 2019, 40, 295–298. [Google Scholar] [CrossRef]

- Zhao, Y.; Wang, C.; Zheng, X.; Ma, X.; He, Y.; Liu, K.; Li, A.; Peng, Y.; Zhang, C.; Hao, Y. Effects of recess depths on performance of AlGaN/GaN power MIS-HEMTs on the Si substrates and threshold voltage model of different recess depths for the using HfO2 gate insulator. Solid State Electron. 2020, 163, 107649. [Google Scholar] [CrossRef]

- Klein, B.A.; Douglas, E.A.; Armstrong, A.M.; Allerman, A.A.; Abate, V.M.; Fortune, T.R.; Baca, A.G. Enhancement-mode Al0.85Ga0.15N/Al0.7Ga0.3N high electron mobility transistor with fluorine treatment. Appl. Phys. Lett. 2019, 114, 112104. [Google Scholar] [CrossRef]

- Du, J.; Chen, N.; Jiang, Z.; Bai, Z.; Liu, Y.; Liu, Y.; Yu, Q. Study on transconductance non-linearity of AlGaN/GaN HEMTs considering acceptor-like traps in barrier layer under the gate. Solid State Electron. 2016, 115, 60–64. [Google Scholar] [CrossRef]

- Meneghini, M.; Rossetto, I.; Bisi, D.; Ruzzarin, M.; Van Hove, M.; Stoffels, S.; Wu, T.-L.; Marcon, D.; Decoutere, S.; Meneghesso, G.; et al. Negative Bias-Induced Threshold Voltage Instability in GaN-on-Si Power HEMTs. IEEE Electron Device Lett. 2016, 37, 474–477. [Google Scholar] [CrossRef]

- Guo, A.; del Alamo, J.A. Unified Mechanism for Positive- and Negative-Bias Temperature Instability in GaN MOSFETs. IEEE Trans. Electron Devices 2017, 64, 2142–2147. [Google Scholar] [CrossRef]

- Cheng, L.; Xu, W.; Pan, D.; Liang, H.; Wang, R.; Zhu, Y.; Ren, F.; Zhou, D.; Ye, J.; Chen, D.; et al. Gate-first AlGaN/GaN HEMT technology for enhanced threshold voltage stability based on MOCVD-grown in situ SiNx. J. Phys. Appl. Phys. 2020. [Google Scholar] [CrossRef]

- Ma, C.; Chen, H.; Zhou, C.; Huang, S.; Yuan, L.; Roberts, J.; Chen, K.J. ON-state critical gate overdrive voltage for fluorine-implanted enhancement-mode AlGaN/GaN high electron mobility transistors. J. Appl. Phys. 2011, 110, 114514. [Google Scholar] [CrossRef]

- Huang, S.; Chen, H.; Chen, K.J. Effects of the fluorine plasma treatment on the surface potential and Schottky barrier height of AlxGa1−xN/GaN heterostructures. Appl. Phys. Lett. 2010, 96, 233510. [Google Scholar] [CrossRef]

- Kang, S.C.; Kim, S.M.; Jung, U.; Kim, Y.; Park, W.; Lee, B.H. Interface state degradation during AC positive bias temperature instability stress. Solid State Electron 2019, 158, 46–50. [Google Scholar] [CrossRef]

- Cho, M.; Roussel, P.; Kaczer, B.; Degraeve, R.; Franco, J.; Aoulaiche, M.; Chiarella, T.; Kauerauf, T.; Horiguchi, N.; Groeseneken, G. Channel Hot Carrier Degradation Mechanism in Long/Short Channel $n$-FinFETs. IEEE Trans. Electron Devices 2013, 60, 4002–4007. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kang, S.C.; Jung, H.-W.; Chang, S.-J.; Kim, S.M.; Lee, S.K.; Lee, B.H.; Kim, H.; Noh, Y.-S.; Lee, S.-H.; Kim, S.-I.; et al. Charging Effect by Fluorine-Treatment and Recess Gate for Enhancement-Mode on AlGaN/GaN High Electron Mobility Transistors. Nanomaterials 2020, 10, 2116. https://doi.org/10.3390/nano10112116

Kang SC, Jung H-W, Chang S-J, Kim SM, Lee SK, Lee BH, Kim H, Noh Y-S, Lee S-H, Kim S-I, et al. Charging Effect by Fluorine-Treatment and Recess Gate for Enhancement-Mode on AlGaN/GaN High Electron Mobility Transistors. Nanomaterials. 2020; 10(11):2116. https://doi.org/10.3390/nano10112116

Chicago/Turabian StyleKang, Soo Cheol, Hyun-Wook Jung, Sung-Jae Chang, Seung Mo Kim, Sang Kyung Lee, Byoung Hun Lee, Haecheon Kim, Youn-Sub Noh, Sang-Heung Lee, Seong-Il Kim, and et al. 2020. "Charging Effect by Fluorine-Treatment and Recess Gate for Enhancement-Mode on AlGaN/GaN High Electron Mobility Transistors" Nanomaterials 10, no. 11: 2116. https://doi.org/10.3390/nano10112116