Investigation on Ge0.8Si0.2-Selective Atomic Layer Wet-Etching of Ge for Vertical Gate-All-Around Nanodevice

Abstract

:1. Introduction

2. Materials and Methods

3. Results and Discussion

3.1. Dual-Selective Etching Ge to p+-Ge0.8Si0.2 with ALE

3.2. Effect of HNO3 Temperature on Ge ALE

3.3. Structure Characterization and Material Quality Analysis

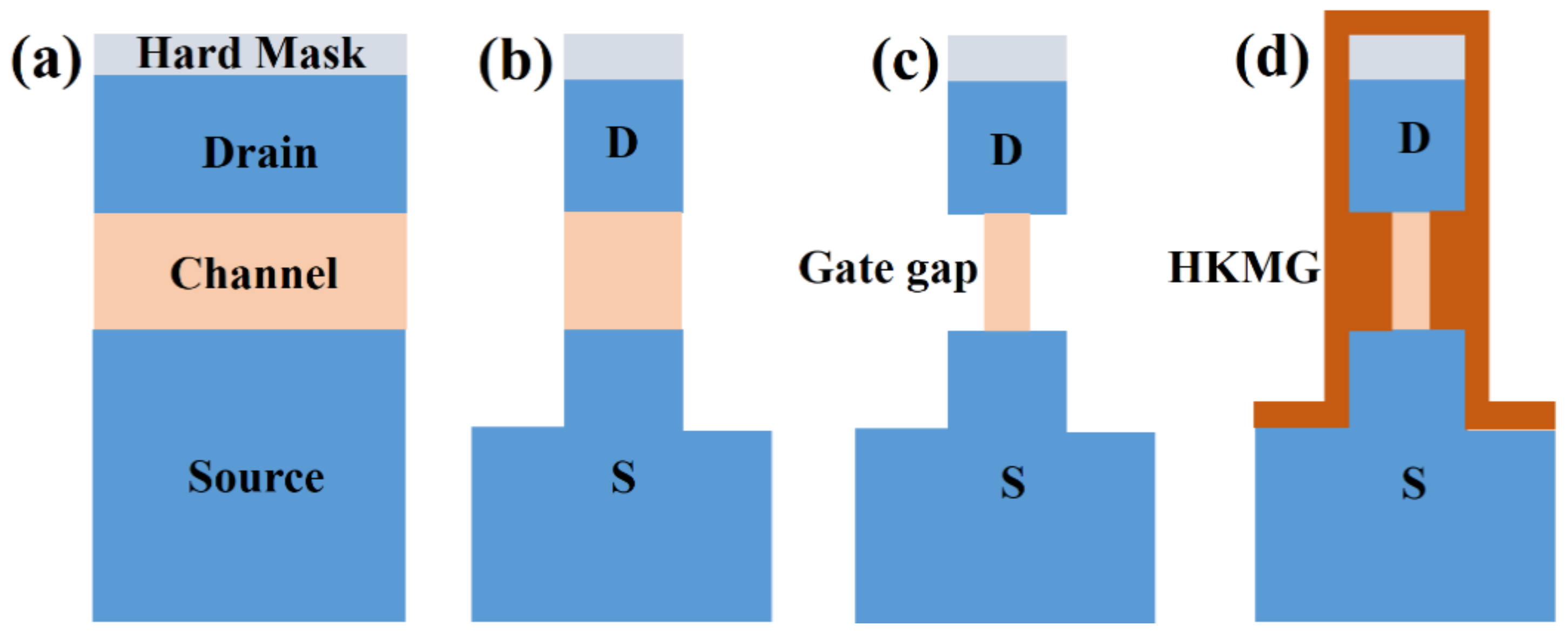

3.4. Application of ALE for Ge Vertical Sandwich GAAFETs (VSAFETs)

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Radamson, H.H.; Zhu, H.L.; Wu, Z.H.; He, X.B.; Lin, H.X.; Liu, J.B.; Xiang, J.J.; Kong, Z.Z.; Wang, G.L.; Li, J.; et al. State of the Art and Future Perspectives in Advanced CMOS Technology. Nanomaterials 2020, 10, 1555. [Google Scholar] [CrossRef] [PubMed]

- Radamson, H.H. Monolithic Nanoscale Photonics-Electronics Integration in Silicon and Other Group IV Elements; Academic Press: Cambridge, MA, USA, 2014; ISBN 978-0124199750. [Google Scholar]

- Liu, M.S.; Schlykow, V.; Hartmann, J.M.; Knoch, J.; Grützmacher, D.; Buca, D.; Zhao, Q.T. Vertical Heterojunction Ge0.92Sn0.08/Ge GAA Nanowire pMOSFETs: Low SS of 67 mV/dec, Small DIBL of 24 mV/V and Highest Gm, ext of 870 µS/µm. In Proceedings of the IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 16–19 June 2020; pp. 1–2. [Google Scholar] [CrossRef]

- Loubet, N.; Hook, T.; Montanini, P.; Yeung, C.-W.; Kanakasabapathy, S.; Guillom, M.; Yamashita, T.; Zhang, J.; Miao, X.; Wang, J.; et al. Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET. Symp. VLSI Technol. 2017, T230–T231. [Google Scholar] [CrossRef]

- Radamson, H.H.; Zhang, Y.B.; He, X.B.; Cui, S.H.; Li, J.J.; Xiang, J.J.; Liu, J.B.; Gu, S.H.; Wang, G.L. The Challenges of Advanced CMOS Process from 2D to 3D. Appl. Sci. 2017, 7, 1047. [Google Scholar] [CrossRef]

- Gu, J.J.; Wang, X.W.; Shao, J.; Neal, A.T.; Manfra, M.J.; Gordon, R.G.; Ye, P.D. III-V gate-all-around nanowire MOSFET process technology: From 3D to 4D. Int. Electron Devices Meet. (IEDM) 2012, 23.7.1–23.7.4. [Google Scholar] [CrossRef] [Green Version]

- Radamson, H.H.; Simoen, E.; Luo, J.; Zhao, C. Past, Present and Future of CMOS; Woodhead Publishing: Cambridge, UK, 2018; pp. 95–114. ISBN 978-008-102-139-2. [Google Scholar]

- Singh, N.; Buddharaju, K.D.; Manhas, S.K.; Agarwal, A.; Rustagi, S.C.; Lo, G.Q.; Balasubramanian, N.; Kwong, D.L. Si, SiGe nanowire devices by top–down technology and their applications. IEEE Trans. Electron. Devices 2008, 55, 3107–3118. [Google Scholar] [CrossRef]

- Xu, W.J.; Wong, H.; Kakushima, K.; Iwai, H. Quasi-analytical model of ballistic cylindrical surrounding gate nanowire MOSFET. Microelectron. Eng. 2015, 138, 111–117. [Google Scholar] [CrossRef]

- Bae, G.; Bae, D.I.; Kang, M.; Hwang, S.M.; Kim, S.S.; Seo, B.; Kwon, T.Y.; Lee, T.J.; Moon, C.; Choi, Y.M.; et al. 3 nm GAA technology featuring multi-bridge-channel FET for low power and high-performance applications. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 28.7.1–28.7.4. [Google Scholar] [CrossRef]

- Veloso, A.; Altamirano-Sánchez, E.; Brus, S.; Chan, B.T.; Cupak, M.; Dehan, M.; Delvaux, C.; Devriendt, K.; Eneman, G.; Ercken, M.; et al. Vertical Nanowire FET Integration and Device Aspects. ECS Trans. 2016, 72, 31–42. [Google Scholar] [CrossRef]

- Radamson, H.H.; He, X.B.; Zhang, Q.Z.; Liu, J.B.; Cui, H.S.; Xiang, J.J.; Kong, Z.Z.; Xiong, W.; Li, J.; Gao, J.; et al. Miniaturization of CMOS. Micromachines 2019, 10, 293. [Google Scholar] [CrossRef] [Green Version]

- Toriumi, A.; Tabata, T.; Lee, C.H.; Nishimura, T.; Kita, K.; Nagashio, K. Opportunities and challenges for Ge CMOS-Control of interfacing field on Ge is a key. Microelectron. Eng. 2009, 86, 1571–1576. [Google Scholar] [CrossRef]

- Yin, X.G.; Zhang, Y.K.; Zhu, H.L.; Wang, G.L.; Li, J.J.; Du, A.Y.; Li, C.; Zhao, L.H.; Huang, W.X.; Yang, H.; et al. Vertical Sandwich Gate-All-Around Field-Effect Transistors with Self-Aligned High-k Metal Gates and Small Effective-Gate-Length Variation. IEEE Electron Device Lett. 2020, 41, 8–11. [Google Scholar] [CrossRef]

- Zhang, Y.K.; Ai, X.Z.; Yin, X.G.; Zhu, H.L.; Yang, H.; Wang, G.L.; Li, J.J.; Du, A.Y.; Li, C.; Huang, W.X.; et al. Vertical Sandwich GAA FETs with Self Aligned High-k Metal Gate Made by Quasi Atomic Layer Etching Process. IEEE Trans. Electron Devices 2021. [Google Scholar] [CrossRef]

- Porret, C.; Vohra, A.; Sebaai, F.; Douhard, B.; Hikavyy, A.; Loo, R. A New Method to Fabricate Ge Nanowires: Selective Lateral Etching of GeSn:P/Ge Multi-Stacks. Solid State Phenom. 2018, 282, 113–118. [Google Scholar] [CrossRef]

- Fischer, A.C.; Belova, L.M.; Rikers, Y.G.M.; Malm, B.G.; Radamson, H.H.; Kolahdouz, M.; Gylfason, K.B.; Stemme, G.; Niklaus, F. 3D free-form patterning of silicon by ion implantation, silicon deposition and selective silicon etching. Adv. Funct. Mater. 2012, 22, 4004–4008. [Google Scholar] [CrossRef] [Green Version]

- Gupta, S.; Chen, R.; Huang, Y.C.; Kim, Y.; Sanchez, E.; Harris, J.S.; Saraswat, K.C. Highly Selective Dry Etching of Germanium over Germanium–Tin (Ge1−xSnx): A Novel Route for Ge1−xSnx Nanostructure Fabrication. Nano Lett. 2013, 13, 3783–3790. [Google Scholar] [CrossRef]

- Lee, Y.J.; Hou, F.J.; Chuang, S.S.; Hsueh, F.K.; Kao, K.H.; Sung, P.J.; Yuan, W.Y.; Yao, J.Y.; Lu, Y.C.; Lin, K.L.; et al. Diamond-shaped Ge and Ge0.9Si0.1 Gate-All-Around Nanowire FETs with Four {111} Facets by Dry Etch Technology. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 15.1.1–15.1.4. [Google Scholar] [CrossRef]

- Xie, L.; Zhu, H.L.; Zhang, Y.K.; Ai, X.Z.; Wang, G.L.; Li, J.J.; Du, A.Y.; Kong, Z.Z.; Yin, X.G.; Li, C.; et al. Strained Si0.2Ge0.8/Ge multilayer Stacks Epitaxially Grown on a Low-/High-Temperature Ge Buffer Layer and Selective Wet-Etching of Germanium. Nanomaterials 2020, 10, 1715. [Google Scholar] [CrossRef]

- Sebaai, F.; Witters, L.; Holsteyns, F.; Wostyn, K.; Rip, J.; Yukifumi, Y.; Lieten, R.R.; Bilodeau, S.; Cooper, E. Wet Selective SiGe Etch to Enable Ge Nanowire Formation. Solid State Phenom. 2016, 255, 3–7. [Google Scholar] [CrossRef]

- Liu, W.D.; Lee, Y.C.; Sekiguchi, R.; Yoshida, Y.; Komori, K.; Wostyn, K.; Sebaai, F.; Holsteyns, F. Selective Wet Etching in Fabricating SiGe and Ge Nanowires for Gate-All-Around MOSFETs. Solid State Phenom. 2018, 282, 101–106. [Google Scholar] [CrossRef]

- Holländer, B.; Buca, D.; Mantl, S.; Hartmann, J.M. Wet Chemical Etching of Si, Si1−xGex, and Ge in HF: H2O2:CH3COOH. J. Electrochem. Soc. 2010, 157, H643–H646. [Google Scholar] [CrossRef]

- Witters, L.; Arimura, H.; Sebaai, F.; Hikavyy, A.; Milenin, A.P.; Loo, R.; De Keersgieter, A.; Eneman, G.; Schram, T.; Wostyn, K.; et al. Strained Germanium Gate-All-Around pMOS Device Demonstration Using Selective Wire Release Etch Prior to Replacement Metal Gate Deposition. IEEE Trans. Electron Devices 2017, 64, 4587–4593. [Google Scholar] [CrossRef]

- Kanarika, K.J.; Tan, S.; Yang, W.; Kim, T.; Lill, T.; Kabansky, A.; Hudson, E.A.; Ohba, T.; Nojiri, K.; Yu, J.; et al. Predicting synergy in atomic layer etching. J. Vac. Sci. Technol. A 2017, 35, 05C302. [Google Scholar] [CrossRef]

- Kanarika, K.J.; Lill, T.; Hudson, E.A.; Sriraman, S.; Tan, S.; Marks, J.; Vahedi, V.; Gottscho, R.A. Overview of atomic layer etching in the semiconductor industry. J. Vac. Sci. Technol. A 2015, 33, 020802. [Google Scholar] [CrossRef] [Green Version]

- Ikeda, K.; Imai, S.; Matsumura, M. Atomic layer etching of germanium. Appl. Surf. Sci. 1997, 112, 87–91. [Google Scholar] [CrossRef]

- Li, C.; Zhu, H.L.; Zhang, Y.K.; Yin, X.G.; Jia, K.P.; Li, J.J.; Wang, G.L.; Kong, Z.Z.; Du, A.Y.; Yang, T.Z.; et al. Selective Digital Etching of Silicon–Germanium Using Nitric and Hydrofluoric Acids. ACS Appl. Mater. Interfaces 2020, 12, 48170–48178. [Google Scholar] [CrossRef] [PubMed]

- Yin, X.G.; Zhu, H.L.; Zhao, L.H.; Wang, G.L.; Li, C.; Huang, W.X.; Zhang, Y.K.; Jia, K.P.; Li, J.J.; Radamson, H.H. Study of Isotropic and Si-Selective Quasi Atomic Layer Etching of Si1−xGex. ECS J. Solid-State Sci. Technol. 2020. [Google Scholar] [CrossRef]

- Li, Y.Y.; Zhu, H.L.; Kong, Z.Z.; Zhang, Y.K.; Ai, X.Z.; Wang, G.L.; Wang, Q.; Liu, Z.Y.; Lu, S.S.; Xie, L.; et al. The Effect of Doping on the Digital Etching of Silicon-Selective Silicon–Germanium Using Nitric Acids. Nanomaterials 2021, 11, 1209. [Google Scholar] [CrossRef]

- Radamson, H.H.; Joelsson, K.B.; Ni, W.-X.; Hultman, L.; Hansson, G.V. Characterization of highly boron-doped Si, Si1−xGex and Ge layers by high-resolution transmission electron microscopy. J. Cryst. Growth 1995, 157, 80–84. [Google Scholar] [CrossRef]

- Du, Y.; Kong, Z.Z.; Toprak, M.S.; Wang, G.L.; Miao, Y.H.; Xu, B.Q.; Yu, J.H.; Li, B.; Lin, H.X.; Han, J.H.; et al. Investigation of the Heteroepitaxial Process Optimization of Ge Layers on Si (001) by RPCVD. Nanomaterials 2021, 11, 928. [Google Scholar] [CrossRef]

- Prabhakaran, K.; Ogino, T. Oxidation of Ge (100) and Ge (ll1) surfaces: An UPS and XPS study. Surf. Sci. 1995, 325, 263–271. [Google Scholar] [CrossRef]

- Wostyn, K.; Sebaai, F.; Rip, J.; Mertens, H.; Witters, L.; Loo, R.; Hikavyy, A.; Milenin, A.; Horiguchi, N.; Collaert, N.; et al. Selective Etch of Si and SiGe for Gate All-Around Device Architecture. ECS Trans. 2015, 69, 147–152. [Google Scholar] [CrossRef]

- Cretella, M.C.; Gatos, H.C. The Reaction of Germanium with Nitric Acid Solutions. J. Electrochem. Soc. 1958, 105, 487. [Google Scholar] [CrossRef]

- Xue, Z.Y.; Wei, X.; Liu, L.J.; Chen, D.; Zhang, B.; Zhang, M.; Wang, X. Etch characteristics of Si1−xGex films in HNO3: H2O: HF. Sci. China Technol. Sci. 2011, 54, 2802. [Google Scholar] [CrossRef]

- Koyama, K.; Hiroi, M.; Tatsumi, T.; Hirayama, H. Etching characteristics of Si1−xGex alloy in ammoniac wet cleaning. Appl. Phys. Lett. 1990, 57, 2202–2204. [Google Scholar] [CrossRef]

- Spadafora, M.; Privitera, G.; Terrasi, A. Oxidation rate enhancement of SiGe epitaxial films oxidized in dry ambient. Appl. Phys. Lett. 2003, 83, 3713–3715. [Google Scholar] [CrossRef]

- Yeo, C.C.; Cho, B.J.; Gao, F.; Lee, S.J.; Lee, M.H.; Yu, C.Y.; Liu, C.W.; Tang, L.J.; Lee, T.W. Electron mobility enhancement using ultrathin pure Ge on Si substrate. IEEE Electron Device Lett. 2005, 26, 761–763. [Google Scholar] [CrossRef]

- Seidel, H.; Csepregi, L.; Heuberger, A.; Baumgartel, H. Anisotropic etching of crystalline silicon in alkaline solutions. J. Electrochem. Soc. 1990, 137, 3612. [Google Scholar]

- Radamson, H.H.; Hallstedt, J. Application of high-resolution X-ray diffraction for detecting defects in SiGe (C) materials. J. Phys. Condens. Matter 2005, 17, S2315–S2322. [Google Scholar] [CrossRef]

| As-Grown | 20 °C ALE | 15 °C ALE | 10 °C ALE | 5 °C ALE | HF:HNO3:CH3COOH | |

|---|---|---|---|---|---|---|

| RMS (nm) | 0.67 | 0.85 | 1.12 | 1.39 | 1.59 | 2.52 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Xie, L.; Zhu, H.; Zhang, Y.; Ai, X.; Li, J.; Wang, G.; Du, A.; Kong, Z.; Wang, Q.; Lu, S.; et al. Investigation on Ge0.8Si0.2-Selective Atomic Layer Wet-Etching of Ge for Vertical Gate-All-Around Nanodevice. Nanomaterials 2021, 11, 1408. https://doi.org/10.3390/nano11061408

Xie L, Zhu H, Zhang Y, Ai X, Li J, Wang G, Du A, Kong Z, Wang Q, Lu S, et al. Investigation on Ge0.8Si0.2-Selective Atomic Layer Wet-Etching of Ge for Vertical Gate-All-Around Nanodevice. Nanomaterials. 2021; 11(6):1408. https://doi.org/10.3390/nano11061408

Chicago/Turabian StyleXie, Lu, Huilong Zhu, Yongkui Zhang, Xuezheng Ai, Junjie Li, Guilei Wang, Anyan Du, Zhenzhen Kong, Qi Wang, Shunshun Lu, and et al. 2021. "Investigation on Ge0.8Si0.2-Selective Atomic Layer Wet-Etching of Ge for Vertical Gate-All-Around Nanodevice" Nanomaterials 11, no. 6: 1408. https://doi.org/10.3390/nano11061408

APA StyleXie, L., Zhu, H., Zhang, Y., Ai, X., Li, J., Wang, G., Du, A., Kong, Z., Wang, Q., Lu, S., Li, C., Li, Y., Huang, W., & Radamson, H. H. (2021). Investigation on Ge0.8Si0.2-Selective Atomic Layer Wet-Etching of Ge for Vertical Gate-All-Around Nanodevice. Nanomaterials, 11(6), 1408. https://doi.org/10.3390/nano11061408