Design Technology Co-Optimization Strategy for Ge Fraction in SiGe Channel of SGOI FinFET

Abstract

1. Introduction

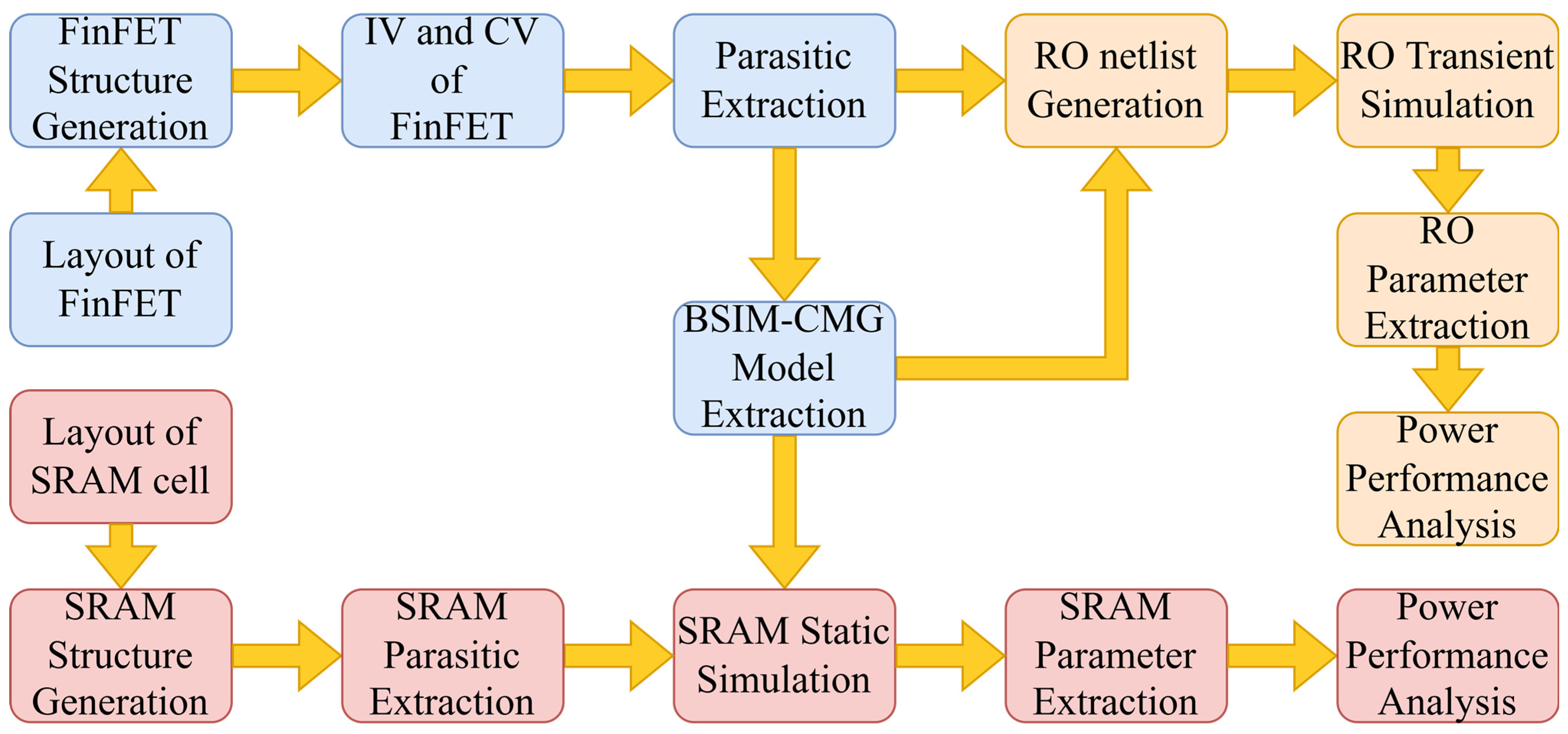

2. Device Structure and Simulation Flow

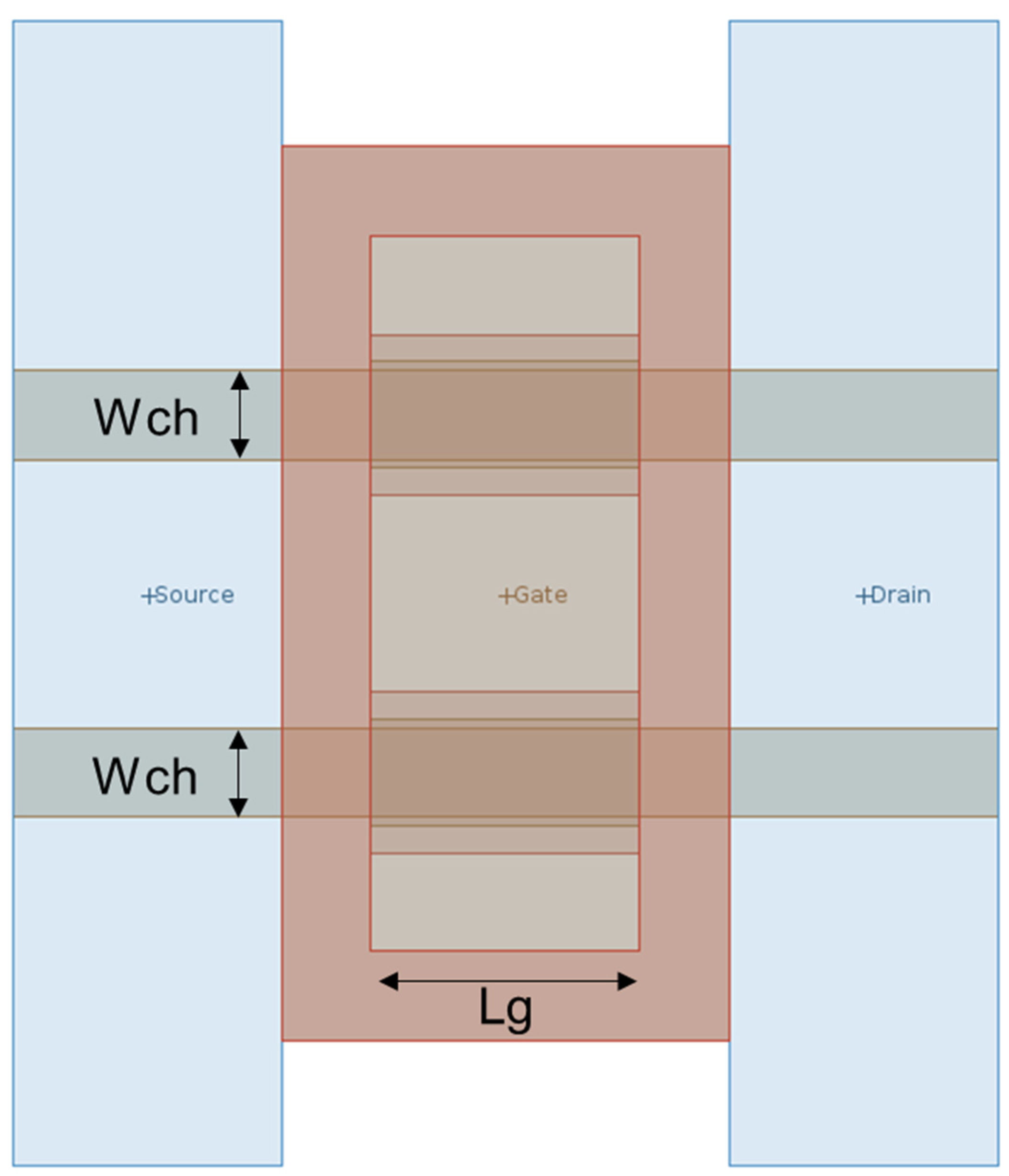

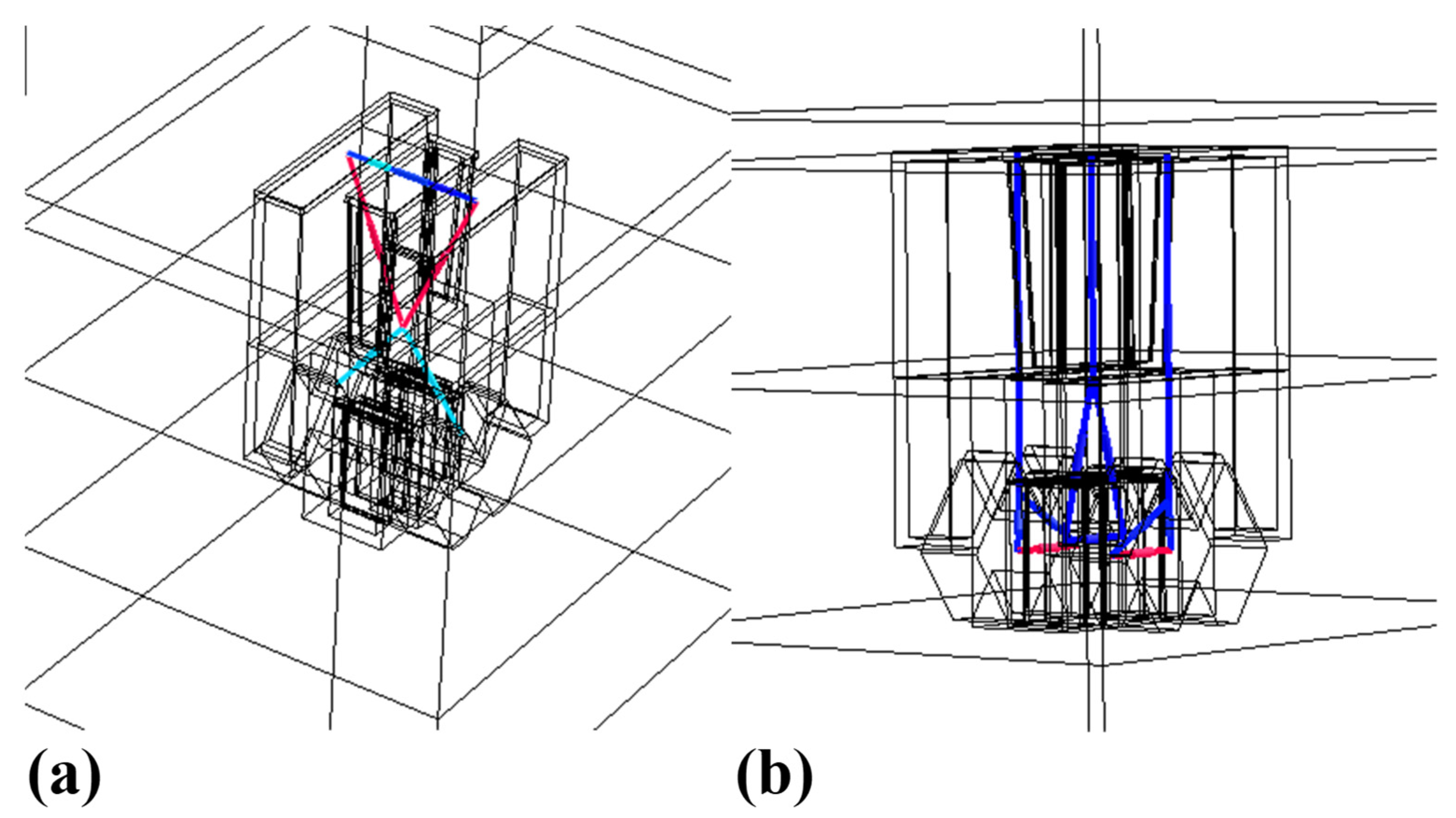

2.1. Device Structure Generation

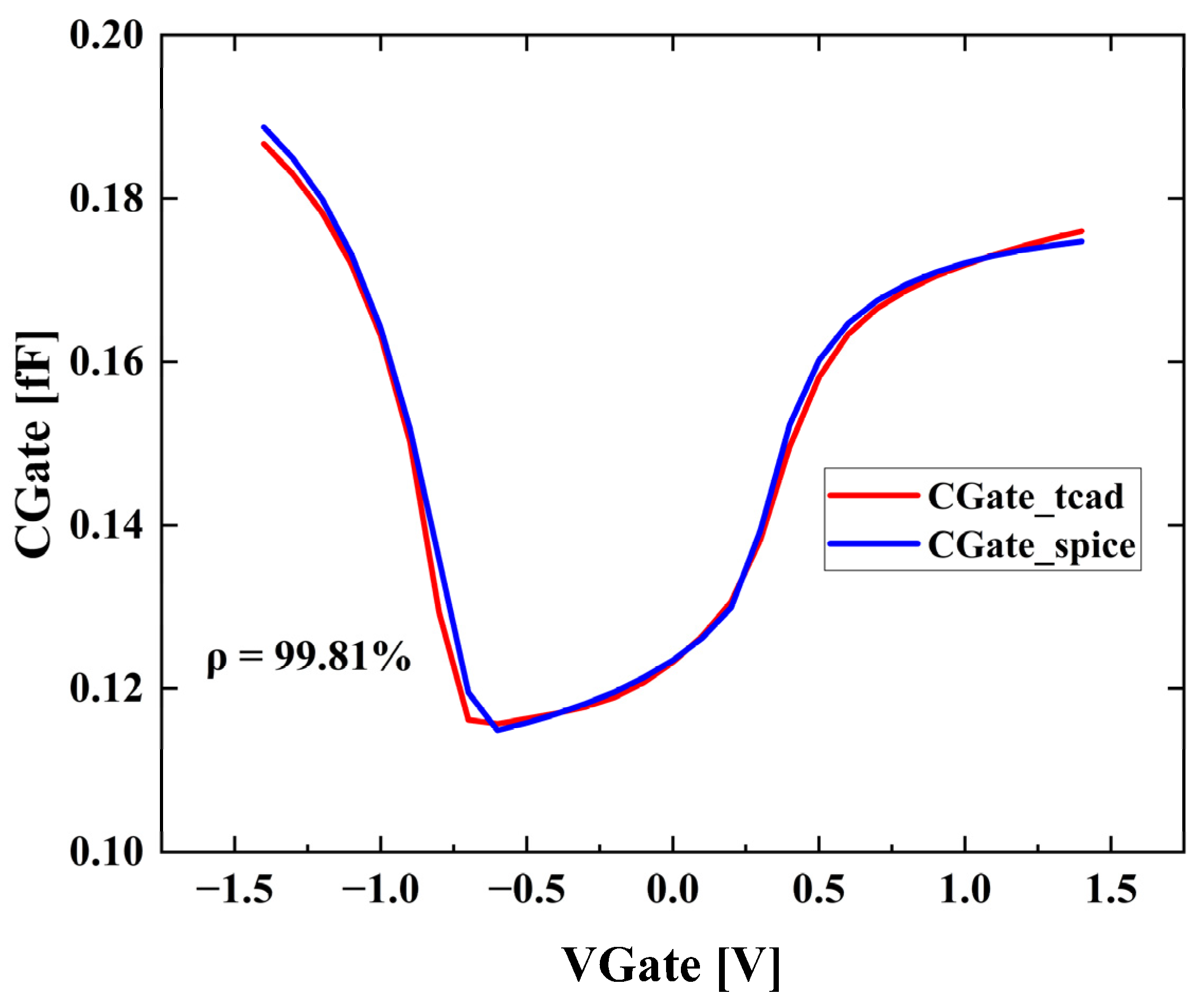

2.2. Device Simulation and Model Extraction

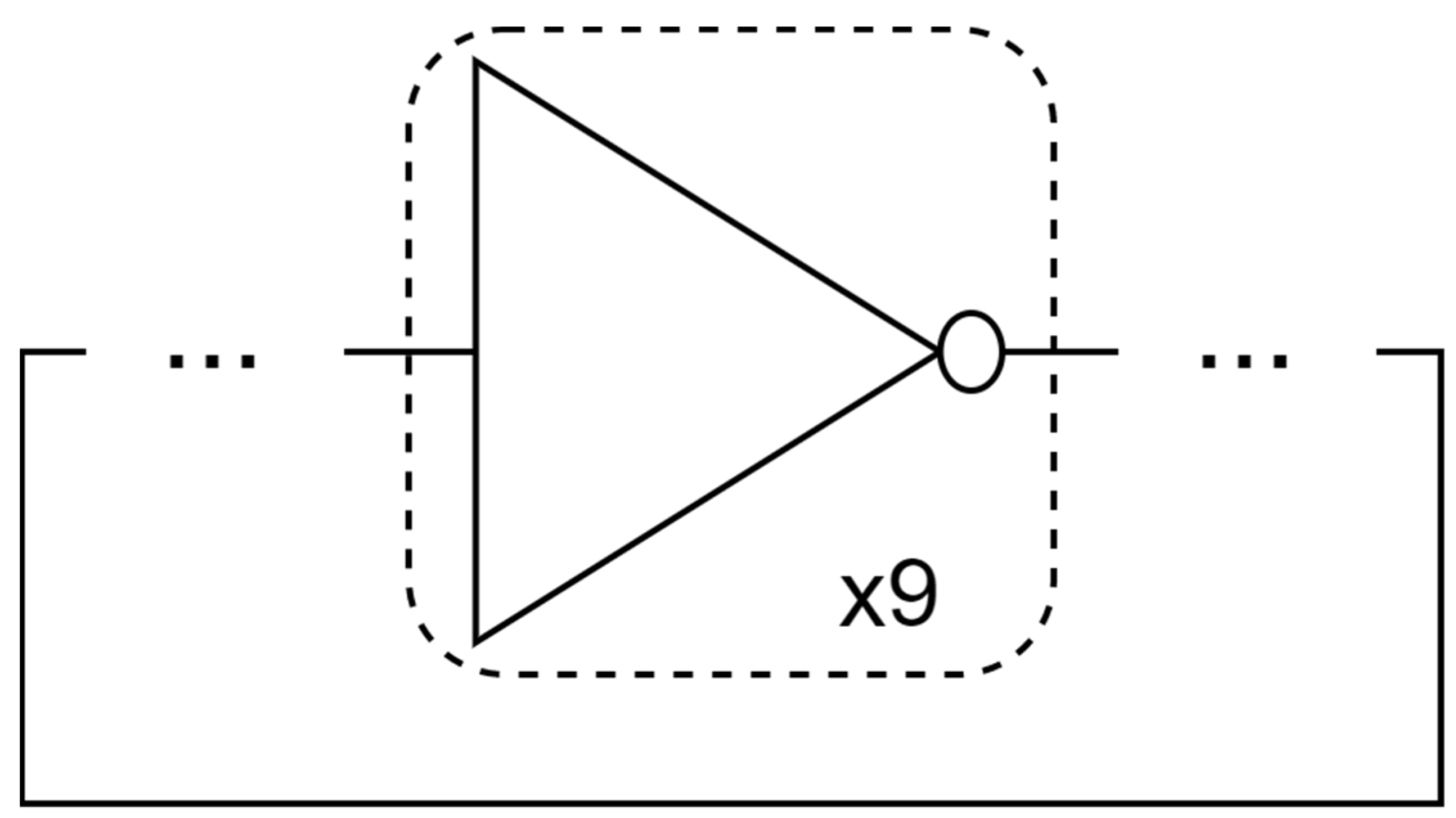

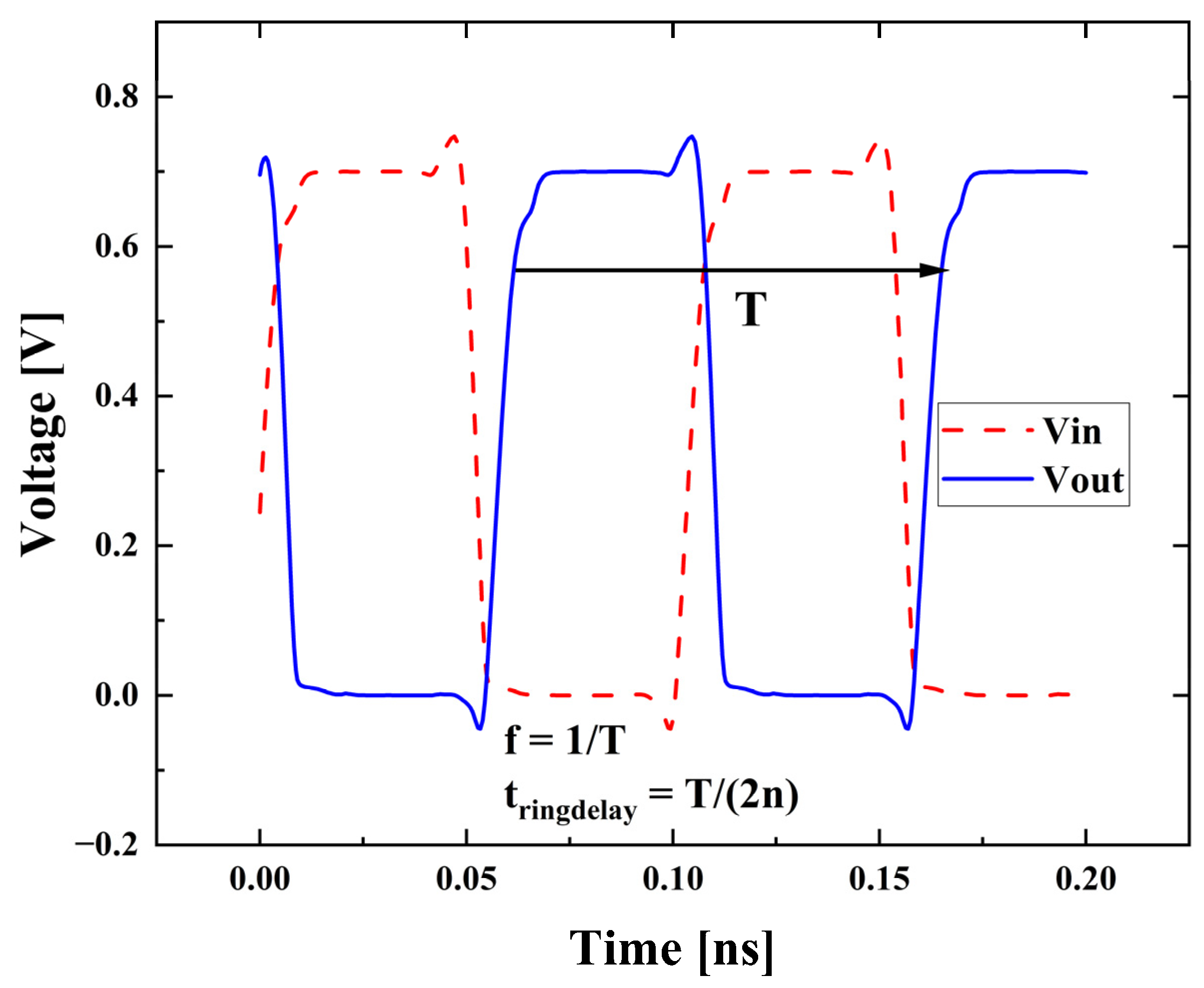

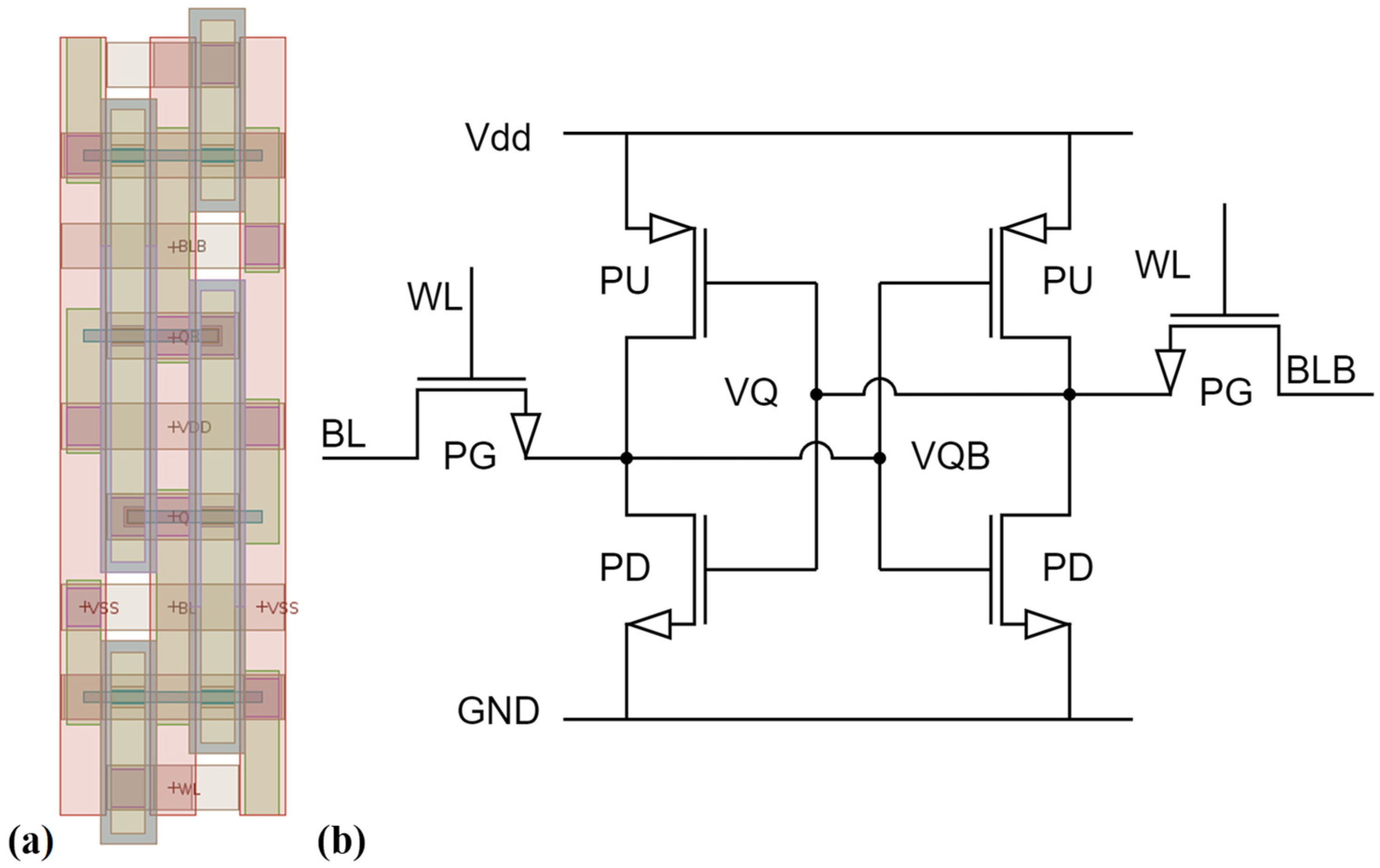

2.3. Cell Circuits SPICE Simulation

- The carrier transport and electrostatic potential problem is solved from the coupled Poisson’s equation and continuity equations, with the drift-diffusion model on.

- The density gradient model is activated to improve the accuracy of the drift diffusion model in simulating nanoscale devices [21].

- In order to accelerate the simulation process, the quasi-Fermi potential model is activated. As no continuity equation is to be solved, the size of the carrier equation system is reduced and the simulation time is shortened.

- The bandgap narrowing model from Slotboom is included to modify the bandgap of silicon at a high doping level [22].

- A ballistic transport model is considered because the gate length has reached the ballistic limit [23].

- The carrier mobility for SiGe alloy is assumed to be linear and positively correlated to the Ge fraction in SiGe, which can be expressed as μSiGe = μSi·(1 + C0x), where x denotes the material composition, and C0 is a constant factor that differs for electrons and holes.

- The most important effect of altering the Ge content in this work is to modify the carrier mobility in the SiGe channel. The influence of mechanical stress and trap states is not taken into consideration of this simulation work.

3. Results and Discussion

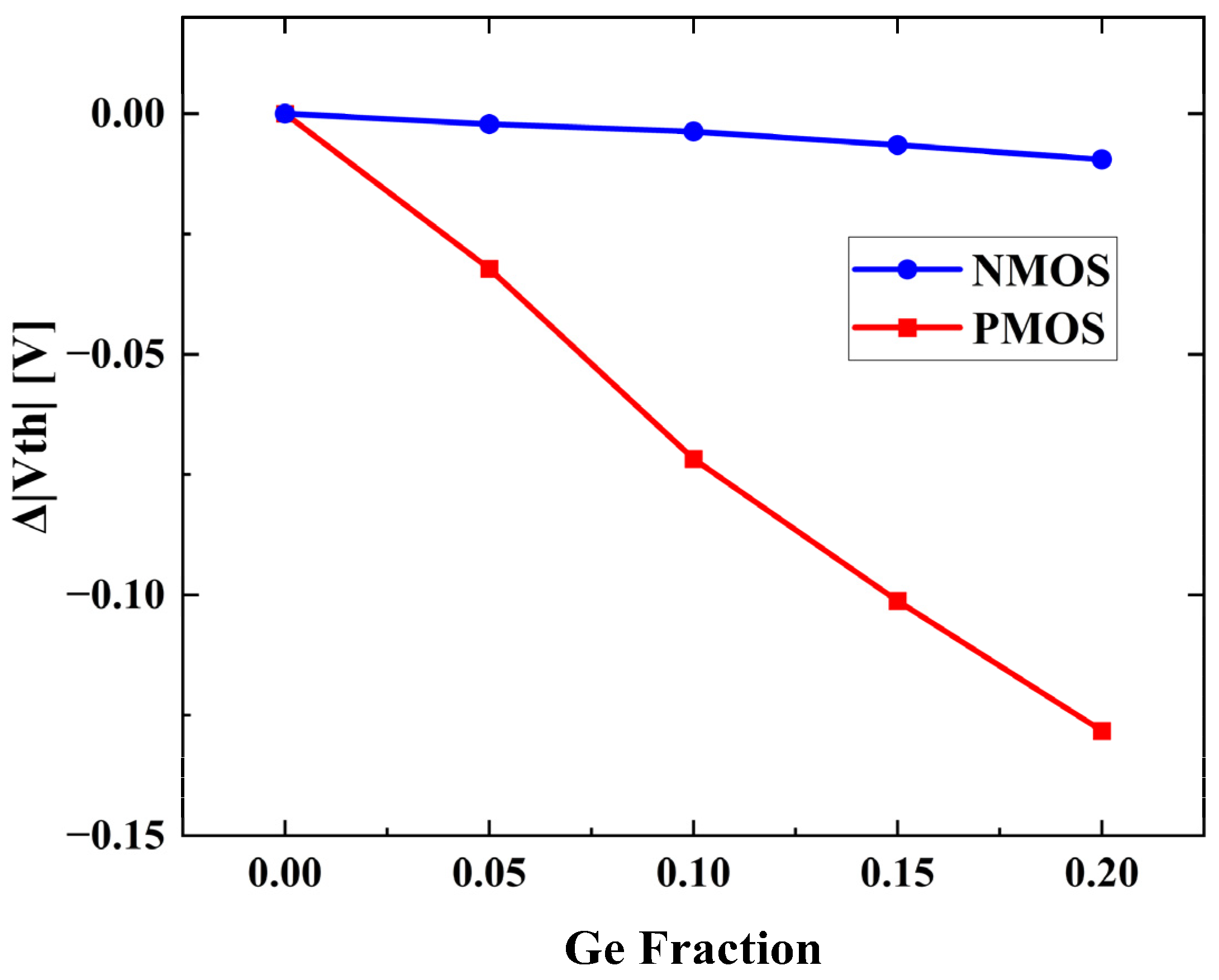

3.1. Device Simulation Results

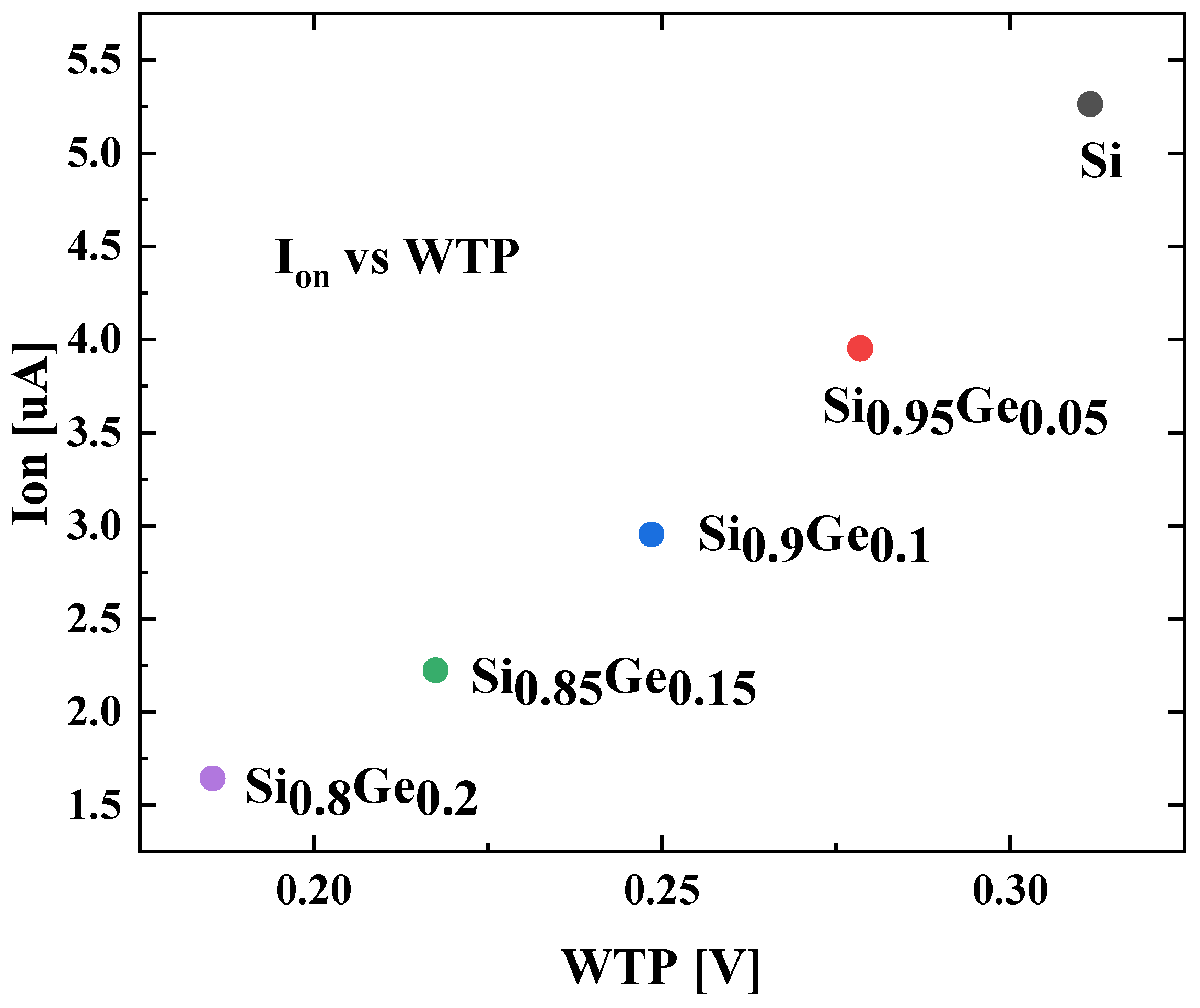

3.2. RO Results and Discussion

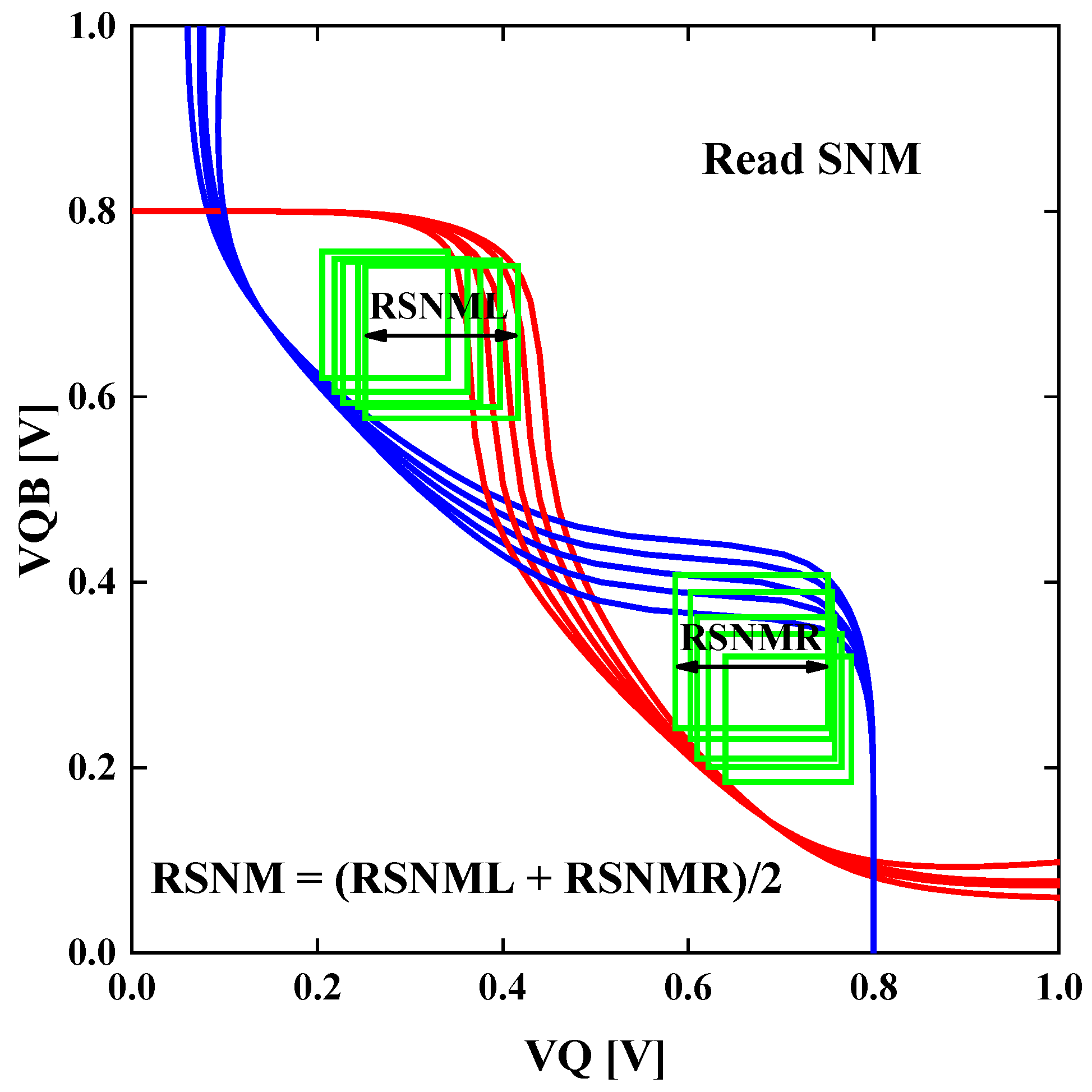

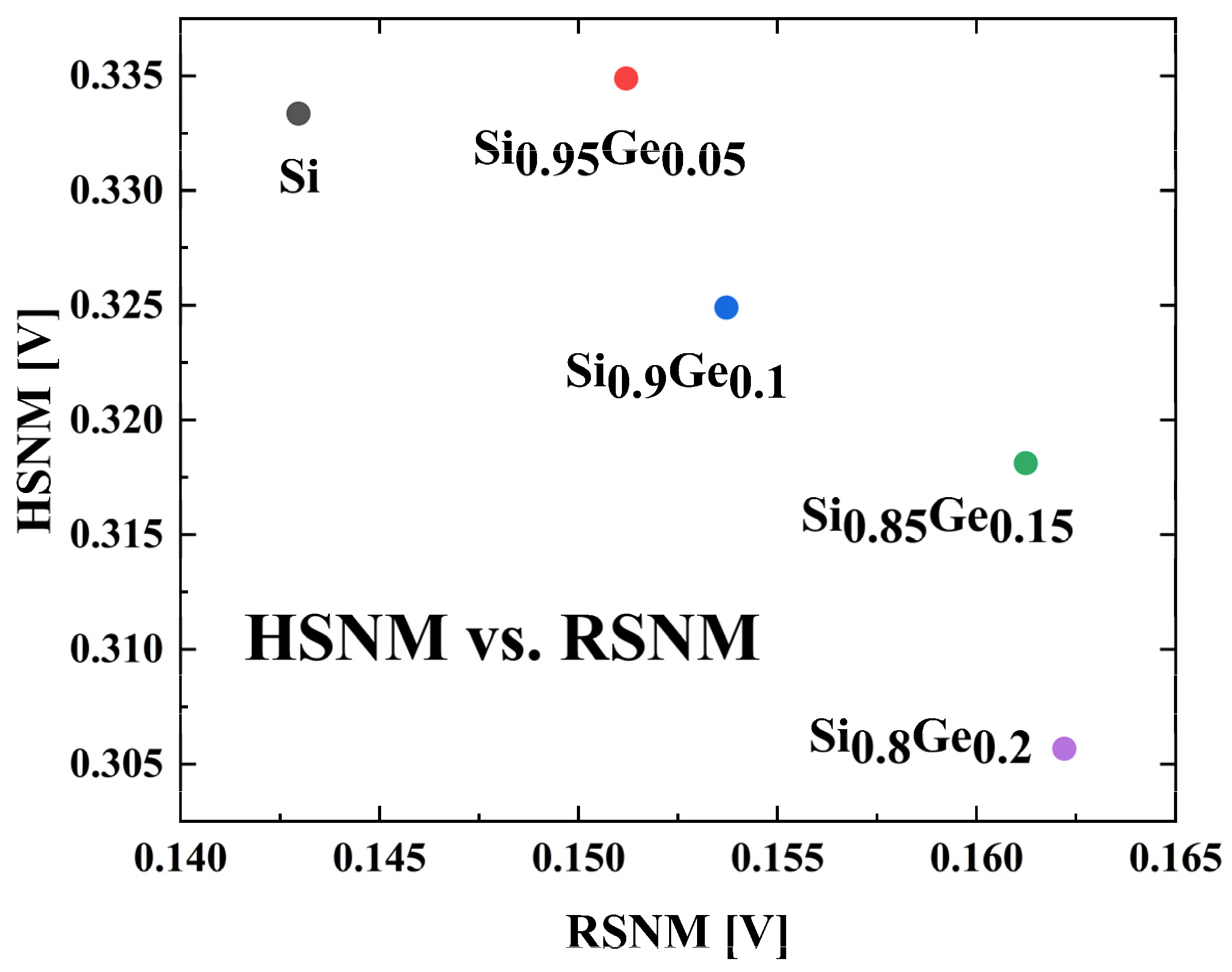

3.3. SRAM Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Parvais, B.; Mercha, A.; Collaert, N.; Rooyackers, R.; Ferain, I.; Jurczak, M.; Subramanian, V.; Keersgieter, A.D.; Chiarella, T.; Kerner, C.; et al. The device architecture dilemma for CMOS technologies: Opportunities & challenges of finFET over planar MOSFET. In Proceedings of 2009 International Symposium on VLSI Technology, Systems, and Applications, Hsinchu, Taiwan, 27–29 April 2009; pp. 80–81. [Google Scholar]

- Chiarella, T.; Witters, L.; Mercha, A.; Kerner, C.; Rakowski, M.; Ortolland, C.; Ragnarsson, L.-Å.; Parvais, B.; De Keersgieter, A.; Kubicek, S. Benchmarking SOI and bulk FinFET alternatives for PLANAR CMOS scaling succession. Solid-State Electron. 2010, 54, 855–860. [Google Scholar] [CrossRef]

- Yan, R.H.; Ourmazd, A.; Lee, K.F. Scaling the Si MOSFET: From bulk to SOI to bulk. IEEE Trans. Electron Devices 1992, 39, 1704–1710. [Google Scholar] [CrossRef]

- Hisamoto, D.; Lee, W.-C.; Kedzierski, J.; Takeuchi, H.; Asano, K.; Kuo, C.; Anderson, E.; King, T.-J.; Bokor, J.; Chenming, H. FinFET-a self-aligned double-gate MOSFET scalable to 20 nm. IEEE Trans. Electron Devices 2000, 47, 2320–2325. [Google Scholar] [CrossRef]

- Yuan, T.; Buchanan, D.A.; Wei, C.; Frank, D.J.; Ismail, K.E.; Shih-Hsien, L.; Sai-Halasz, G.A.; Viswanathan, R.G.; Wann, H.J.C.; Wind, S.J.; et al. CMOS scaling into the nanometer regime. Proc. IEEE 1997, 85, 486–504. [Google Scholar] [CrossRef]

- IEEE. International Roadmap for Devices and Systems—More Moore White Paper, 2022 Edition; IEEE: Manhattan, NY, USA, 2022. [Google Scholar]

- Chang, J.B.; Guillorn, M.; Solomon, P.M.; Lin, C.H.; Engelmann, S.U.; Pyzyna, A.; Ott, J.A.; Haensch, W.E. Scaling of SOI FinFETs down to fin width of 4 nm for the 10nm technology node. In Proceedings of 2011 Symposium on VLSI Technology—Digest of Technical Papers, Kyoto, Japan, 14–16 June 2011; pp. 12–13. [Google Scholar]

- Xuejue, H.; Wen-Chin, L.; Kuo, C.; Hisamoto, D.; Leland, C.; Kedzierski, J.; Anderson, E.; Takeuchi, H.; Yang-Kyu, C.; Asano, K.; et al. Sub-50 nm P-channel FinFET. IEEE Trans. Electron Devices 2001, 48, 880–886. [Google Scholar] [CrossRef]

- Verdonckt-Vandebroek, S.; Crabbe, E.F.; Meyerson, B.S.; Harame, D.L.; Restle, P.J.; Stork, J.M.C.; Johnson, J.B. SiGe-channel heterojunction p-MOSFET's. IEEE Trans. Electron Devices 1994, 41, 90–101. [Google Scholar] [CrossRef]

- Cheng, K.; Khakifirooz, A.; Loubet, N.; Luning, S.; Nagumo, T.; Vinet, M.; Liu, Q.; Reznicek, A.; Adam, T.; Naczas, S.; et al. High performance extremely thin SOI (ETSOI) hybrid CMOS with Si channel NFET and strained SiGe channel PFET. In Proceedings of 2012 International Electron Devices Meeting, San Francisco, CA, USA, 10–13 December 2012; pp. 18.11.11–18.11.14. [Google Scholar]

- Verdonckt-Vandebroek, S.; Crabbe, E.F.; Meyerson, B.S.; Harame, D.L.; Restle, P.J.; Stork, J.M.C.; Megdanis, A.C.; Stanis, C.L.; Bright, A.A.; Kroesen, G.M.W.; et al. High-mobility modulation-doped SiGe-channel p-MOSFETs. IEEE Electron Device Lett. 1991, 12, 447–449. [Google Scholar] [CrossRef]

- Li, Y.; Zhao, F.; Cheng, X.; Liu, H.; Zan, Y.; Li, J.; Zhang, Q.; Wu, Z.; Luo, J.; Wang, W. Four-Period Vertically Stacked SiGe/Si Channel FinFET Fabrication and Its Electrical Characteristics. Nanomaterials 2021, 11, 1689. [Google Scholar] [CrossRef] [PubMed]

- Li, Y.; Zan, Y.; Cheng, X.; Zhao, F.; Liu, H.; Wang, W. Si0.5Ge0.5 channel introduction technique for the preparation of high mobility FinFET device. Mater. Sci. Semicond. Process. 2022, 139, 106373. [Google Scholar] [CrossRef]

- Hutin, L.; Cassé, M.; Royer, C.L.; Damlencourt, J.F.; Pouydebasque, A.; Xu, C.; Tabone, C.; Hartmann, J.M.; Carron, V.; Grampeix, H.; et al. 20nm gate length trigate pFETs on strained SGOI for high performance CMOS. In Proceedings of 2010 Symposium on VLSI Technology, Honolulu, HI, USA, 15–17 June 2010; pp. 37–38. [Google Scholar]

- Oh, J.; Lee, S.H.; Min, K.S.; Huang, J.; Min, B.G.; Sassman, B.; Jeon, K.; Loh, W.Y.; Barnett, J.; Ok, I.; et al. SiGe CMOS on (110) channel orientation with mobility boosters: Surface orientation, channel directions, and uniaxial strain. In Proceedings of 2010 Symposium on VLSI Technology, Honolulu, HI, USA, 15–17 June 2010; pp. 39–40. [Google Scholar]

- Yao, J.; Li, J.; Luo, K.; Yu, J.; Zhang, Q.; Hou, Z.; Gu, J.; Yang, W.; Wu, Z.; Yin, H.; et al. Physical Insights on Quantum Confinement and Carrier Mobility in Si, Si0.45Ge0.55, Ge Gate-All-Around NSFET for 5 nm Technology Node. IEEE J. Electron Devices Soc. 2018, 6, 841–848. [Google Scholar] [CrossRef]

- Guo, D.; Karve, G.; Tsutsui, G.; Lim, K.Y.; Robison, R.; Hook, T.; Vega, R.; Liu, D.; Bedell, S.; Mochizuki, S.; et al. FINFET technology featuring high mobility SiGe channel for 10nm and beyond. In Proceedings of 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; pp. 1–2. [Google Scholar]

- Tezuka, T.; Sugiyama, N.; Mizuno, T.; Takagi, S. Ultrathin body SiGe-on-insulator pMOSFETs with high-mobility SiGe surface channels. IEEE Trans. Electron Devices 2003, 50, 1328–1333. [Google Scholar] [CrossRef]

- Tezuka, T.; Nakaharai, S.; Moriyama, Y.; Sugiyama, N.; Takagi, S. High-mobility strained SiGe-on-insulator pMOSFETs with Ge-rich surface channels fabricated by local condensation technique. IEEE Electron Device Lett. 2005, 26, 243–245. [Google Scholar] [CrossRef]

- IEEE. International Roadmap for Devices and Systems—More Moore White Paper, 2018 Edition; IEEE: Manhattan, NY, USA, 2018. [Google Scholar]

- Ancona, M.G.; Tiersten, H.F. Macroscopic physics of the silicon inversion layer. Phys. Rev. B Condens. Matter. 1987, 35, 7959–7965. [Google Scholar] [CrossRef] [PubMed]

- Slotboom, J.W.; de Graaff, H.C. Measurements of bandgap narrowing in Si bipolar transistors. Solid-State Electron. 1976, 19, 857–862. [Google Scholar] [CrossRef]

- Erlebach, A.; Lee, K.; Bufler, F.M. Empirical ballistic mobility model for drift-diffusion simulation. In Proceedings of 2016 46th European Solid-State Device Research Conference (ESSDERC), Lausanne, Switzerland, 12–15 September 2016; pp. 420–423. [Google Scholar]

| Parameter | Quantity | Value |

|---|---|---|

| Lg | Gate Length | 15 nm |

| Wch | Fin Width | 5 nm |

| H | Fin Height | 30 nm |

| Tox | Oxide Thickness | 2 nm |

| Lspacer | Spacer Length | 5 nm |

| CPP | Contact Poly Pitch | 40 nm |

| NSD | S/D Doping Concentration | 3 × 20 cm−3 |

| NCH | Channel Doping Concentration | 3 × 15 cm−3 |

| Channel Material | Channel Material | Si1−xGex |

| Variable | Quantity | value |

| x | Ge content | 0, 0.05, 0.1, 0.15, 0.2 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, S.; Wu, Z. Design Technology Co-Optimization Strategy for Ge Fraction in SiGe Channel of SGOI FinFET. Nanomaterials 2023, 13, 1709. https://doi.org/10.3390/nano13111709

Li S, Wu Z. Design Technology Co-Optimization Strategy for Ge Fraction in SiGe Channel of SGOI FinFET. Nanomaterials. 2023; 13(11):1709. https://doi.org/10.3390/nano13111709

Chicago/Turabian StyleLi, Shixin, and Zhenhua Wu. 2023. "Design Technology Co-Optimization Strategy for Ge Fraction in SiGe Channel of SGOI FinFET" Nanomaterials 13, no. 11: 1709. https://doi.org/10.3390/nano13111709

APA StyleLi, S., & Wu, Z. (2023). Design Technology Co-Optimization Strategy for Ge Fraction in SiGe Channel of SGOI FinFET. Nanomaterials, 13(11), 1709. https://doi.org/10.3390/nano13111709