The Impact of Ambient Temperature on Electrothermal Characteristics in Stacked Nanosheet Transistors with Multiple Lateral Stacks

Abstract

:1. Introduction

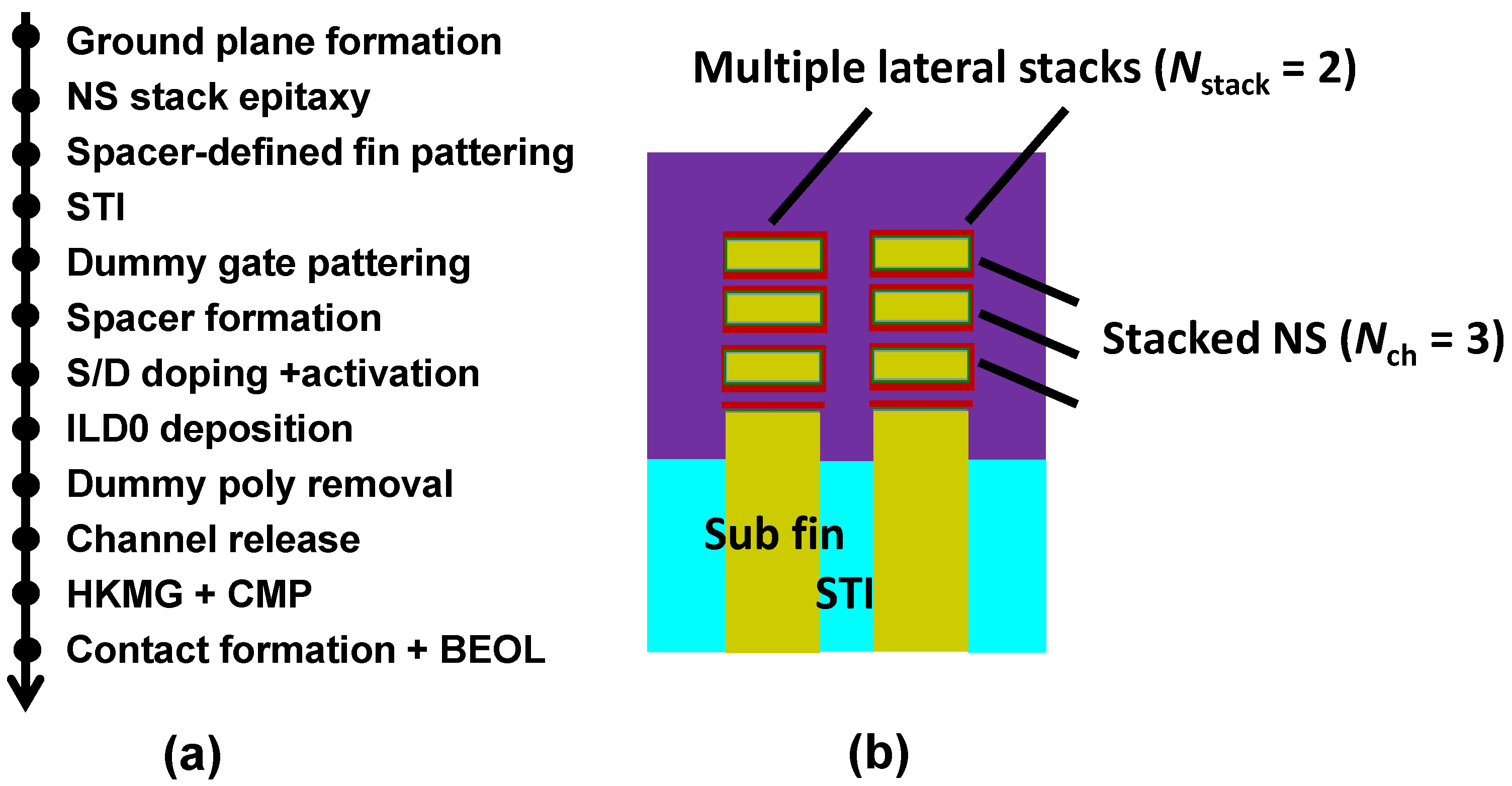

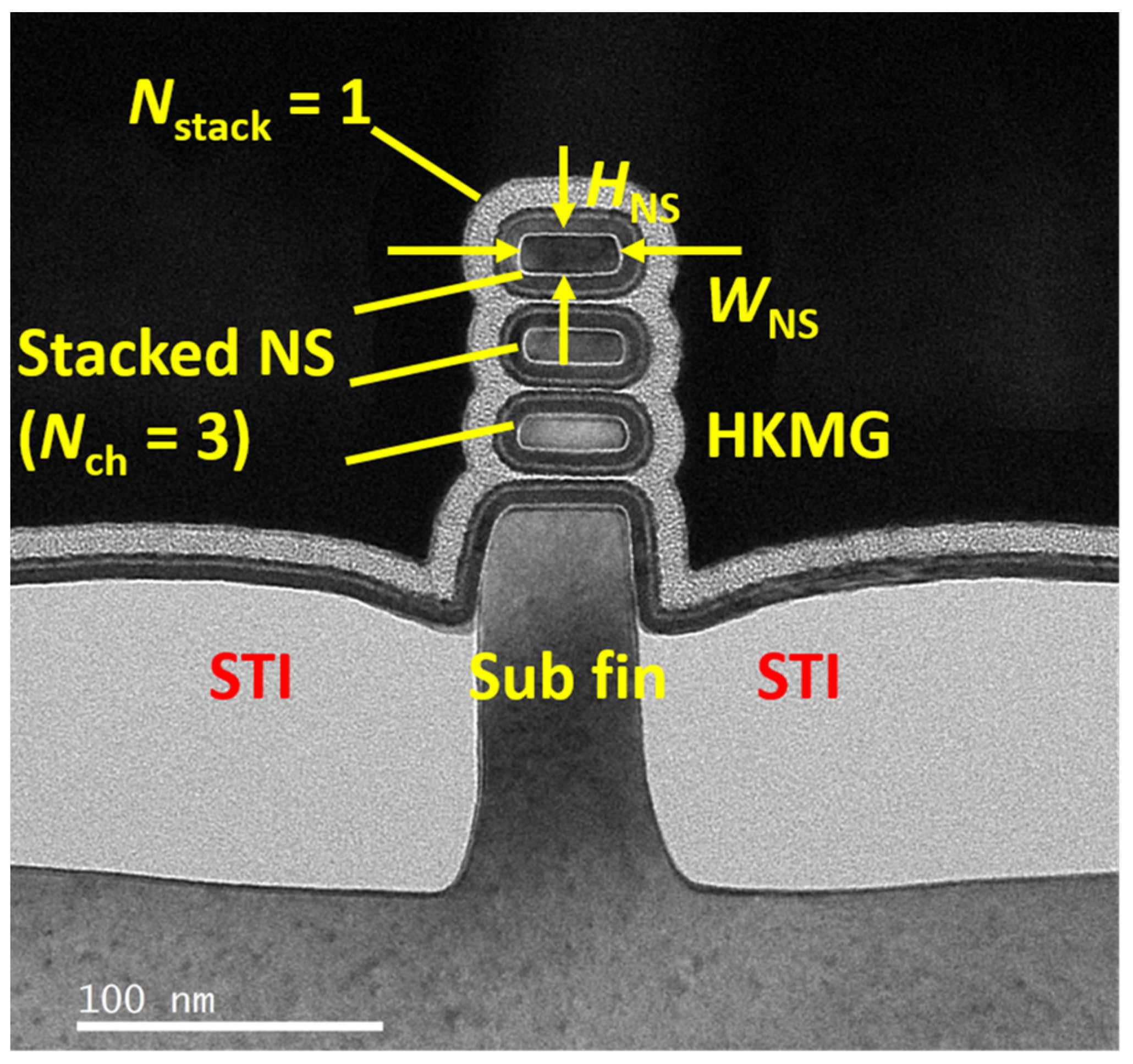

2. Device Fabrication

3. Results and Discussion

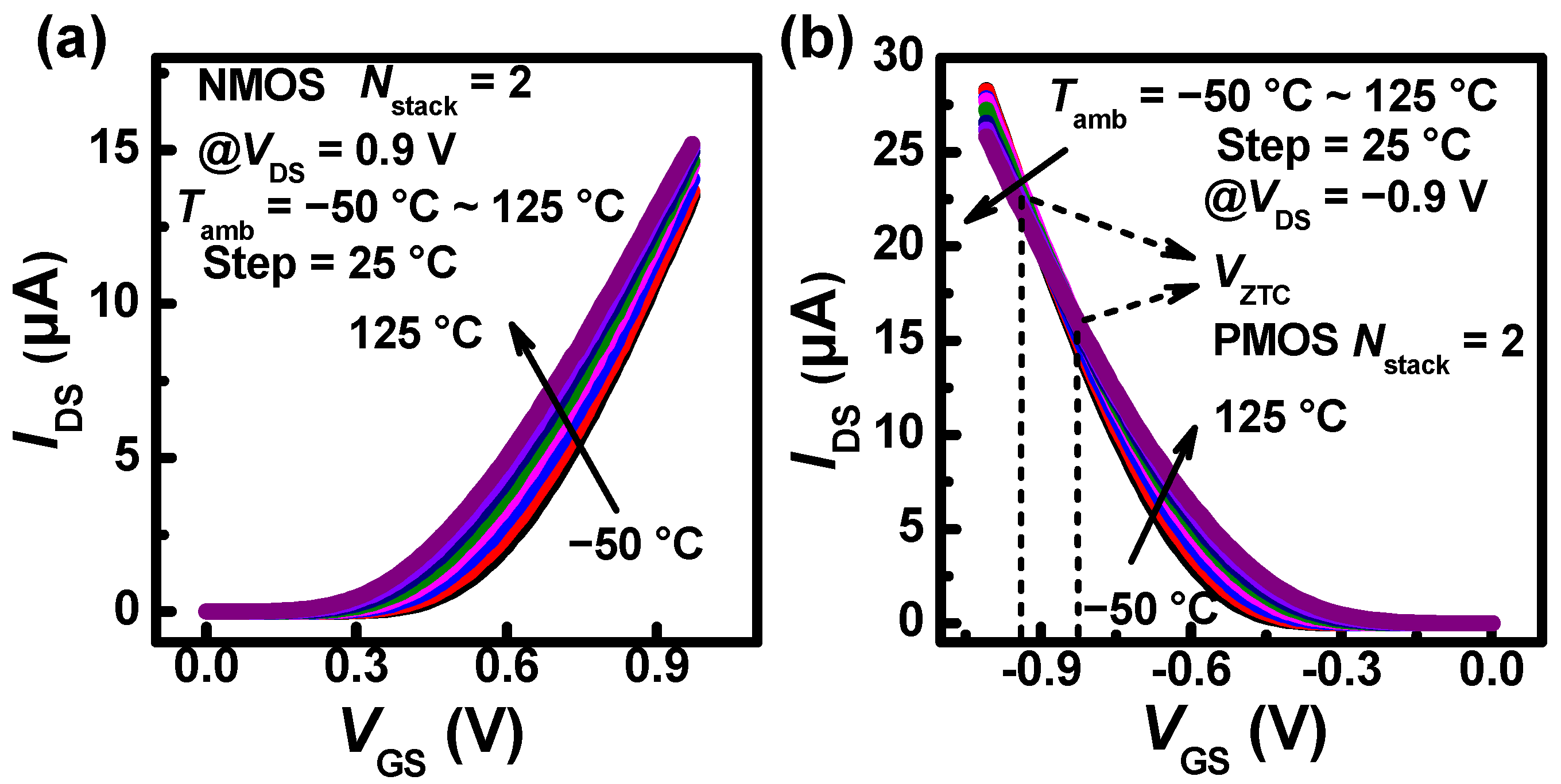

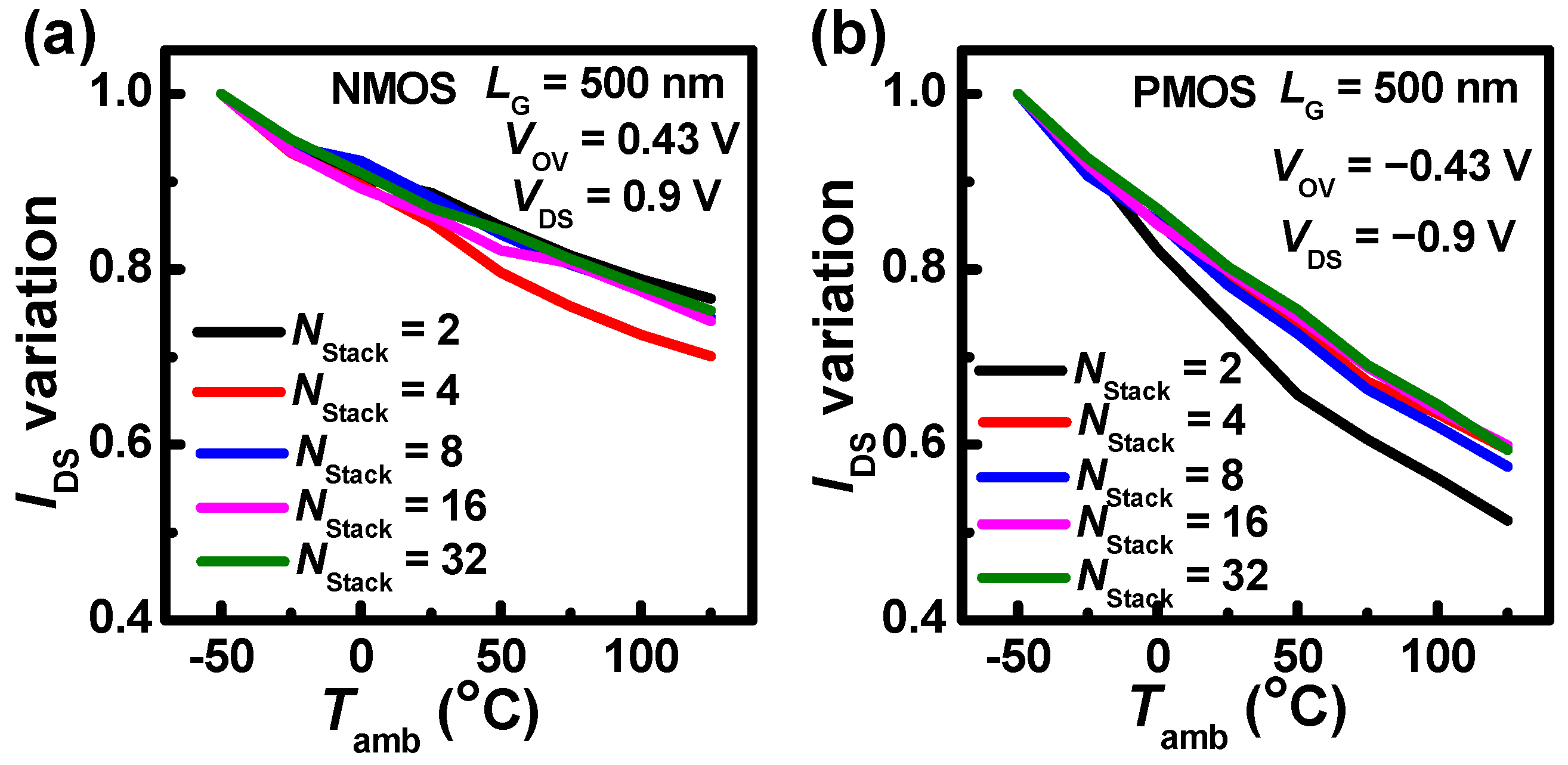

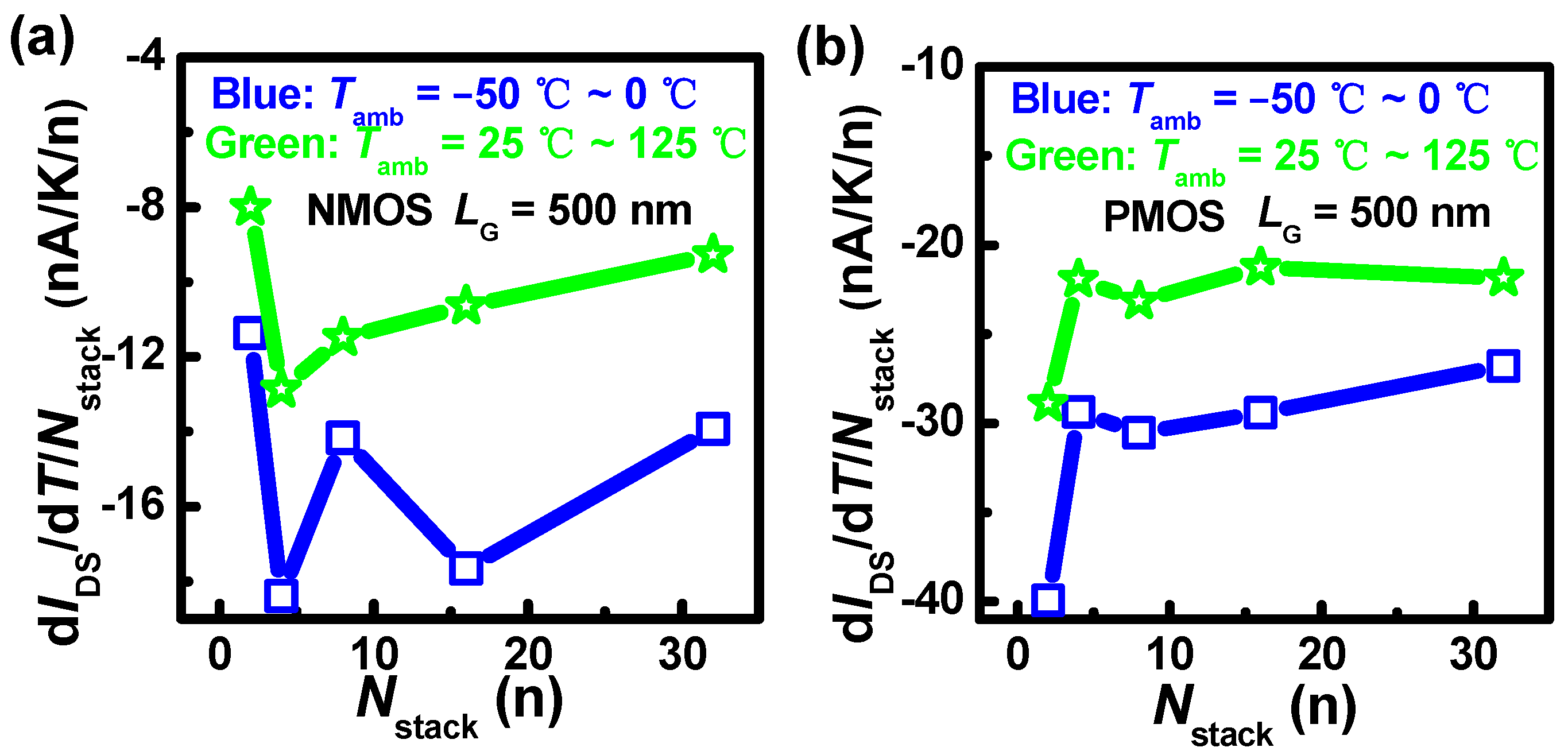

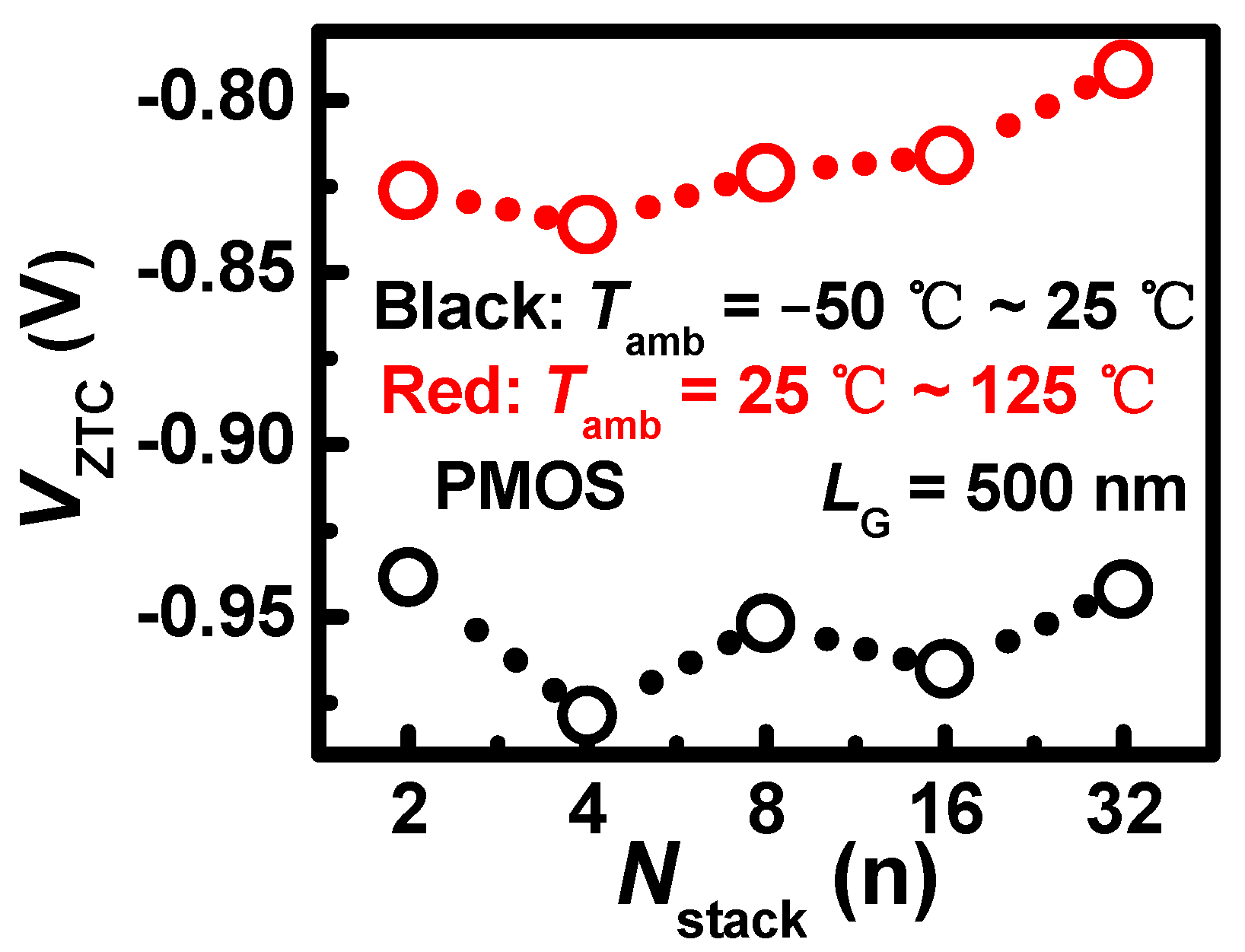

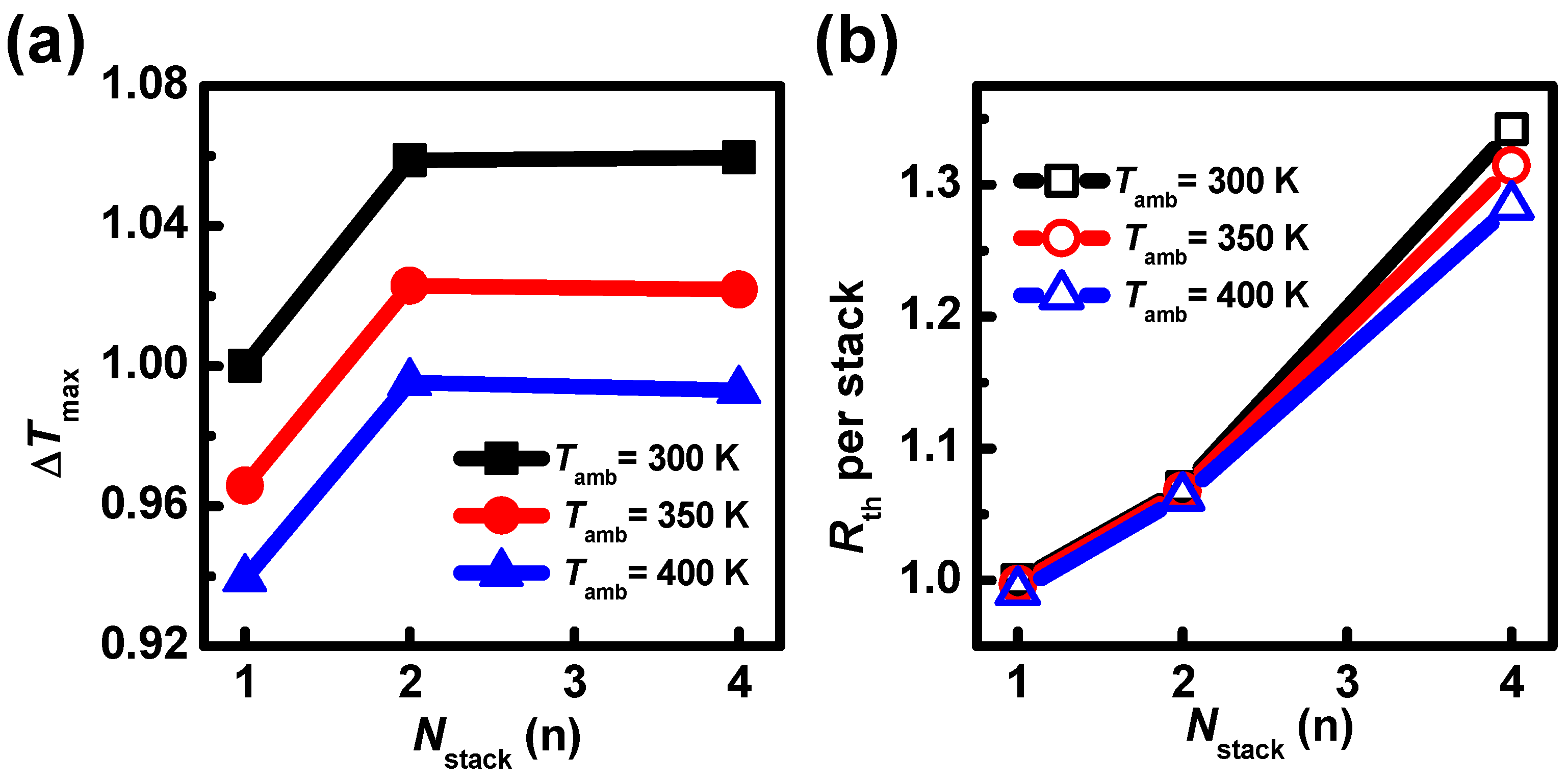

3.1. Electrothermal Performance of Different Numbers of Stacks under the Impact of Ambient Temperature

3.2. Electrothermal Performance of Different Gate Lengths with Different Nstacks under the Impact of Tamb

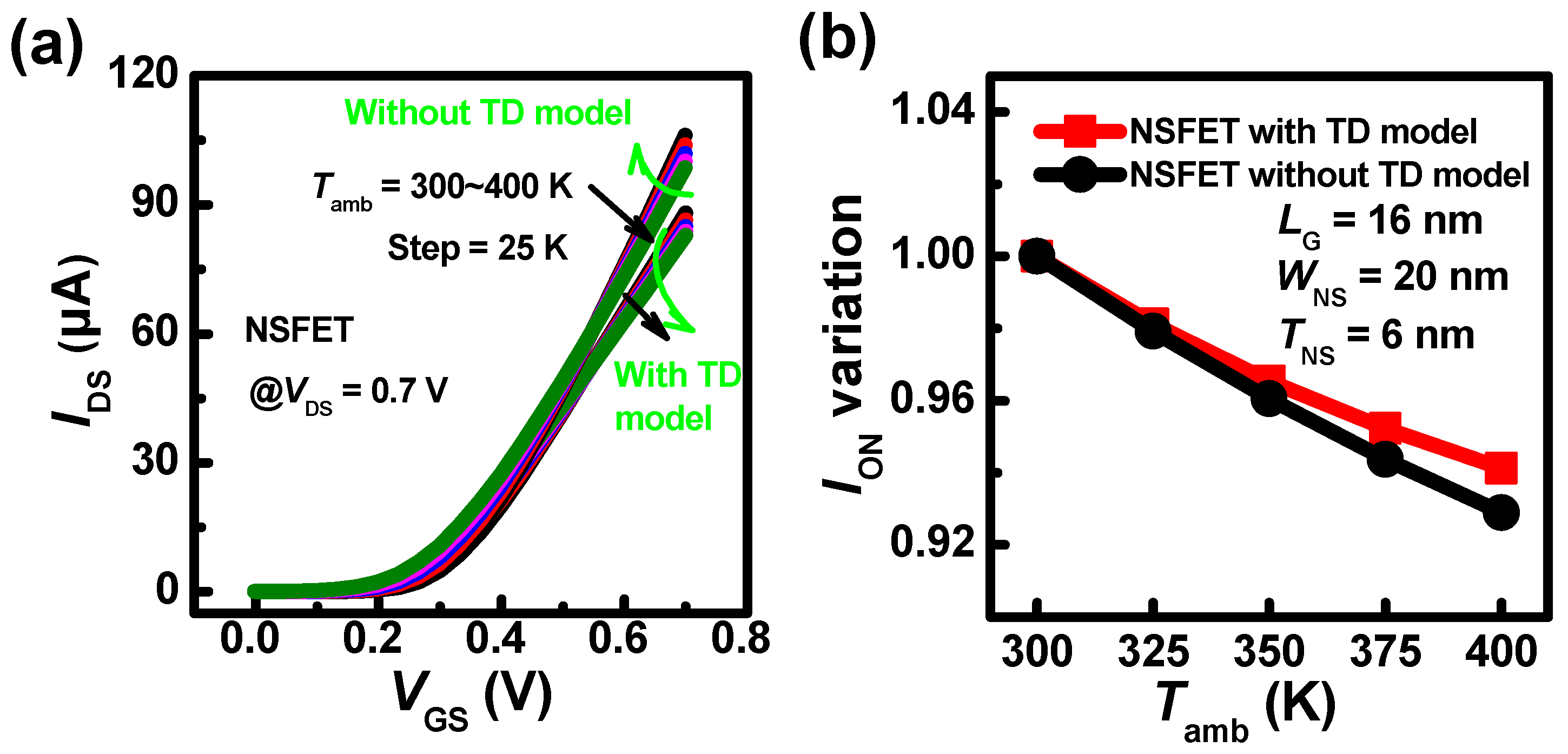

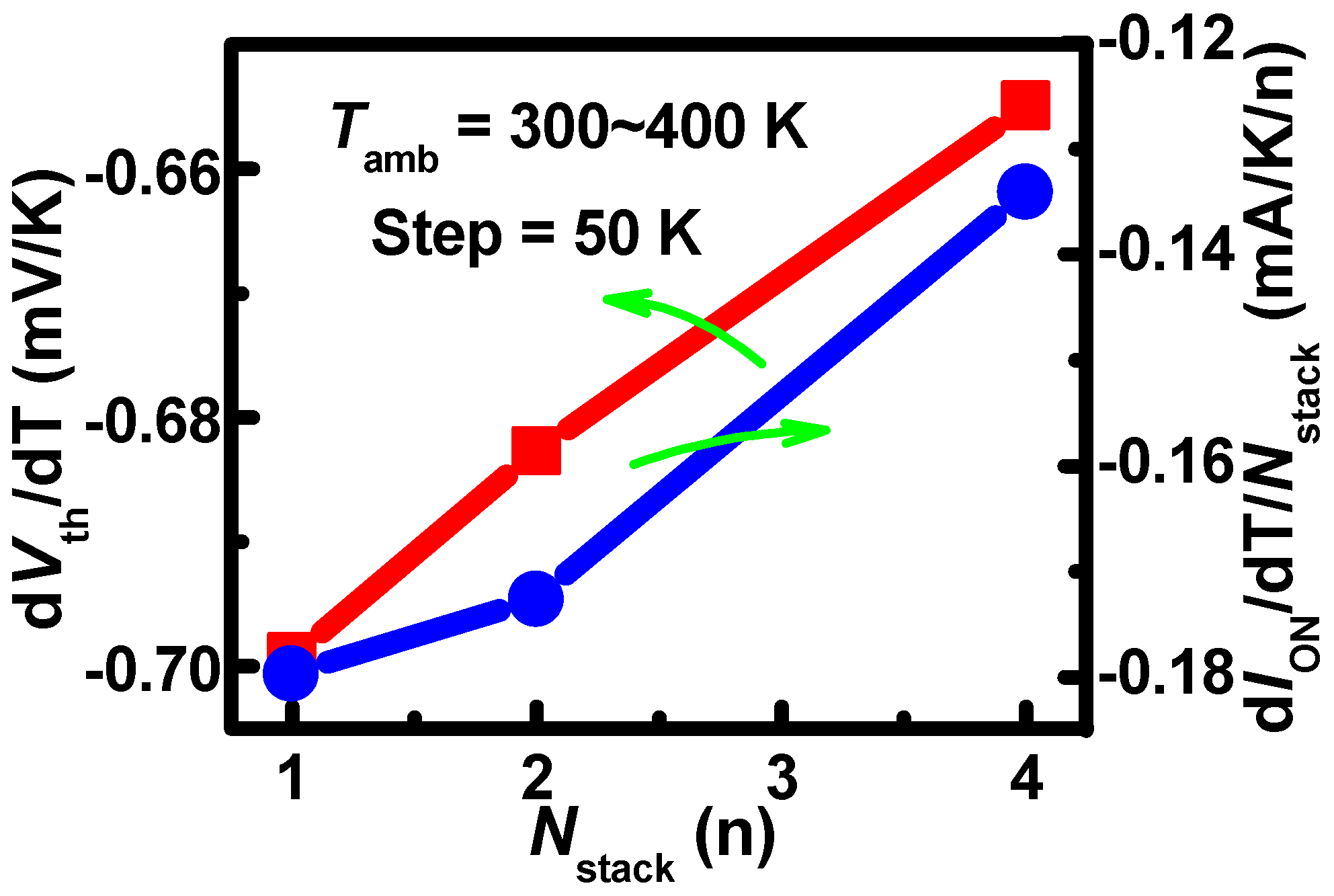

3.3. Simulation Verification

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- International Roadmap for Devices and Systems (IRDS). 2020. Available online: https://irds.ieee.org/editions/2020 (accessed on 1 May 2023).

- Bae, G.; Bae, D.-I.; Kang, M.; Hwang, S.M.; Kim, S.S.; Seo, B.; Kwon, T.Y.; Lee, T.J.; Moon, C.; Choi, Y.M.; et al. 3nm GAA Technology Featuring Multi-Bridge-Channel FET for Low Power and High Performance Applications. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; IEEE: Piscataway, NJ, USA, 2018; pp. 28.7.1–28.7.4. [Google Scholar]

- Loubet, N.; Hook, T.; Montanini, P.; Yeung, C.-W.; Kanakasabapathy, S.; Guillom, M.; Yamashita, T.; Zhang, J.; Miao, X.; Wang, J.; et al. Stacked Nanosheet Gate-All-around Transistor to Enable Scaling beyond FinFET. In Proceedings of the 2017 Symposium on VLSI Technology, Kyoto, Japan, 5–8 June 2017; IEEE: Piscataway, NJ, USA, 2017; pp. T230–T231. [Google Scholar]

- Myeong, I.; Song, I.; Kang, M.J.; Shin, H. Self-Heating and Electrothermal Properties of Advanced Sub-5-nm Node Nanoplate FET. IEEE Electron Device Lett. 2020, 41, 977–980. [Google Scholar] [CrossRef]

- Vermeersch, B.; Bury, E.; Xiang, Y.; Schuddinck, P.; Bhuwalka, K.K.; Hellings, G.; Ryckaert, J. Self-Heating in iN8–iN2 CMOS Logic Cells: Thermal Impact of Architecture (FinFET, Nanosheet, Forksheet and CFET) and Scaling Boosters. In Proceedings of the 2022 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Honolulu, HI, USA, 12–17 June 2022; IEEE: Piscataway, NJ, USA, 2022; pp. 371–372. [Google Scholar]

- Yoo, C.; Chang, J.; Seon, Y.; Kim, H.; Jeon, J. Analysis of Self-Heating Effects in Multi-Nanosheet FET Considering Bottom Isolation and Package Options. IEEE Trans. Electron Devices 2022, 69, 1524–1531. [Google Scholar] [CrossRef]

- Cai, L.; Chen, W.; Du, G.; Zhang, X.; Liu, X. Layout Design Correlated with Self-Heating Effect in Stacked Nanosheet Transistors. IEEE Trans. Electron Devices 2018, 65, 2647–2653. [Google Scholar] [CrossRef]

- Chung, C.-C.; Ye, H.-Y.; Lin, H.H.; Wan, W.K.; Yang, M.-T.; Liu, C.W. Self-Heating Induced Interchannel Vt Difference of Vertically Stacked Si Nanosheet Gate-All-Around MOSFETs. IEEE Electron Device Lett. 2019, 40, 1913–1916. [Google Scholar] [CrossRef]

- Shin, S.H.; Masuduzzaman, M.; Gu, J.J.; Wahab, M.A.; Conrad, N.; Si, M.; Ye, P.D.; Alam, M.A. Impact of Nanowire Variability on Performance and Reliability of Gate-All-around III-V MOSFETs. In Proceedings of the 2013 IEEE International Electron Devices Meeting, Washington, DC, USA, 9–11 December 2013; IEEE: Piscataway, NJ, USA, 2013; pp. 7.5.1–7.5.4. [Google Scholar]

- Myeong, I.; Son, D.; Kim, H.; Shin, H. Analysis of Self Heating Effect in DC/AC Mode in Multi-Channel GAA-Field Effect Transistor. IEEE Trans. Electron Devices 2019, 66, 4631–4637. [Google Scholar] [CrossRef]

- Venkateswarlu, S.; Nayak, K. Hetero-Interfacial Thermal Resistance Effects on Device Performance of Stacked Gate-All-Around Nanosheet FET. IEEE Trans. Electron Devices 2020, 67, 4493–4499. [Google Scholar] [CrossRef]

- Ahn, W.; Jiang, C.; Xu, J.; Alam, M.A. A New Framework of Physics-Based Compact Model Predicts Reliability of Self-Heated Modern ICs: FinFET, NWFET, NSHFET Comparison. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; IEEE: Piscataway, NJ, USA, 2017; pp. 13.6.1–13.6.4. [Google Scholar]

- Jiang, H.; Shin, S.; Liu, X.; Zhang, X.; Alam, M.A. The Impact of Self-Heating on HCI Reliability in High-Performance Digital Circuits. IEEE Electron Device Lett. 2017, 38, 430–433. [Google Scholar] [CrossRef]

- Qu, Y.; Lin, X.; Li, J.; Cheng, R.; Yu, X.; Zheng, Z.; Lu, J.; Chen, B.; Zhao, Y. Ultra Fast (<1 Ns) Electrical Characterization of Self-Heating Effect and Its Impact on Hot Carrier Injection in 14nm FinFETs. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; IEEE: Piscataway, NJ, USA, 2017; pp. 39.2.1–39.2.4. [Google Scholar]

- Zhao, Y.; Qu, Y. Impact of Self-Heating Effect on Transistor Characterization and Reliability Issues in Sub-10 nm Technology Nodes. IEEE J. Electron Devices Soc. 2019, 7, 829–836. [Google Scholar] [CrossRef]

- Jiang, H.; Xu, N.; Chen, B.; Zeng, L.; He, Y.; Du, G.; Liu, X.; Zhang, X. Experimental Investigation of Self Heating Effect (SHE) in Multiple-Fin SOI FinFETs. Semicond. Sci. Technol. 2014, 29, 115021. [Google Scholar] [CrossRef]

- Wang, R.; Zhuge, J.; Liu, C.; Huang, R.; Kim, D.-W.; Park, D.; Wang, Y. Experimental Study on Quasi-Ballistic Transport in Silicon Nanowire Transistors and the Impact of Self-Heating Effects. In Proceedings of the 2008 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2008; IEEE: Piscataway, NJ, USA, 2008; pp. 1–4. [Google Scholar]

- Jain, I.; Gupta, A.; Hook, T.B.; Dixit, A. Modeling of Effective Thermal Resistance in Sub-14-Nm Stacked Nanowire and FinFETs. IEEE Trans. Electron Devices 2018, 65, 4238–4244. [Google Scholar] [CrossRef]

- Liu, R.; Li, X.; Sun, Y.; Shi, Y. A Vertical Combo Spacer to Optimize Electrothermal Characteristics of 7-Nm Nanosheet Gate-All-Around Transistor. IEEE Trans. Electron Devices 2020, 67, 2249–2254. [Google Scholar] [CrossRef]

- Jang, D.; Bury, E.; Ritzenthaler, R.; Bardon, M.G.; Chiarella, T.; Miyaguchi, K.; Raghavan, P.; Mocuta, A.; Groeseneken, G.; Mercha, A.; et al. Self-Heating on Bulk FinFET from 14nm down to 7nm Node. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; IEEE: Piscataway, NJ, USA, 2015; pp. 11.6.1–11.6.4. [Google Scholar]

- Rodriguez, N.; Navarro, C.; Andrieu, F.; Faynot, O.; Gamiz, F.; Cristoloveanu, S. Self-Heating Effects in Ultrathin FD SOI Transistors. In Proceedings of the IEEE 2011 International SOI Conference, Tempe, AZ, USA, 3–6 October 2011; IEEE: Piscataway, NJ, USA, 2011; pp. 1–2. [Google Scholar]

- Tu, R.H.; Wann, C.; King, J.C.; Ko, P.K.; Hu, C. An AC Conductance Technique for Measuring Self-Heating in SOI MOSFET’s. IEEE Electron Device Lett. 1995, 16, 67–69. [Google Scholar] [CrossRef]

- Venkateswarlu, S.; Sudarsanan, A.; Singh, S.G.; Nayak, K. Ambient Temperature-Induced Device Self-Heating Effects on Multi-Fin Si n-FinFET Performance. IEEE Trans. Electron Devices 2018, 65, 2721–2728. [Google Scholar] [CrossRef]

- Kumar, N.; Kaushik, P.K.; Kumar, S.; Gupta, A.; Singh, P. Thermal Conductivity Model to Analyze the Thermal Implications in Nanowire FETs. IEEE Trans. Electron Devices 2022, 69, 6388–6393. [Google Scholar] [CrossRef]

- Takahashi, T.; Beppu, N.; Chen, K.; Oda, S.; Uchida, K. Thermal-Aware Device Design of Nanoscale Bulk/SOI FinFETs: Suppression of Operation Temperature and Its Variability. In Proceedings of the 2011 International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011; IEEE: Piscataway, NJ, USA, 2011; pp. 34.6.1–34.6.4. [Google Scholar]

- Venkateswarlu, S.; Nayak, K. Ambient Temperature-Induced Device Self-Heating Effects on Multi-Fin Si CMOS Logic Circuit Performance in N-14 to N-7 Scaled Technologies. IEEE Trans. Electron Devices 2020, 67, 1530–1536. [Google Scholar] [CrossRef]

- Mertens, H.; Ritzenthaler, R.; Hikavyy, A.; Kim, M.S.; Tao, Z.; Wostyn, K.; Chew, S.A.; De Keersgieter, A.; Mannaert, G.; Rosseel, E.; et al. Gate-All-around MOSFETs Based on Vertically Stacked Horizontal Si Nanowires in a Replacement Metal Gate Process on Bulk Si Substrates. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; IEEE: Piscataway, NJ, USA, 2016; pp. 1–2. [Google Scholar]

- Zhang, Q.; Gu, J.; Xu, R.; Cao, L.; Li, J.; Wu, Z.; Wang, G.; Yao, J.; Zhang, Z.; Xiang, J.; et al. Optimization of Structure and Electrical Characteristics for Four-Layer Vertically-Stacked Horizontal Gate-All-Around Si Nanosheets Devices. Nanomaterials 2021, 11, 646. [Google Scholar] [CrossRef] [PubMed]

- Triantopoulos, K.; Casse, M.; Brunet, L.; Batude, P.; Fenouillet-Beranger, C.; Reimbold, G.; Ghibaudo, G. Self-Heating Assessment and Cold Current Extraction in FDSOI MOSFETs. In Proceedings of the 2017 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Burlingame, CA, USA, 16–19 October 2017; IEEE: Piscataway, NJ, USA, 2017; pp. 1–3. [Google Scholar]

- Lundstrom, M. Elementary Scattering Theory of the Si MOSFET. IEEE Electron Device Lett. 1997, 18, 361–363. [Google Scholar] [CrossRef]

- Chen, M.-J.; Huang, H.-T.; Huang, K.-C.; Chen, P.-N.; Chang, C.-S.; Diaz, C.H. Temperature Dependent Channel Backscattering Coefficients in Nanoscale MOSFETs. In Proceedings of the Digest. International Electron Devices Meeting, San Francisco, CA, USA, 8–11 December 2002; IEEE: Piscataway, NJ, USA, 2002; pp. 39–42. [Google Scholar]

- Zhao, P.; Cao, L.; Zhang, F.; Xu, H.; Gan, W.; Zhang, Q.; Zhang, Z.; Yao, J.; Tian, G.; Luo, K.; et al. Investigation on Dependency of Thermal Characteristics on Gate/Drain Bias Voltages in Stacked Nanosheet Transistors. Microelectron. J. 2023, 141, 105970. [Google Scholar] [CrossRef]

- Sentaurus Device User Guide, Version P-2019.03; Synopsys: Mountain View, CA, USA, 2019.

- Kang, S.J.; Kim, J.H.; Song, Y.S.; Go, S.; Kim, S. Investigation of Self-Heating Effects in Vertically Stacked GAA MOSFET with Wrap-Around Contact. IEEE Trans. Electron Devices 2022, 69, 910–914. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhao, P.; Cao, L.; Wang, G.; Wu, Z.; Yin, H. The Impact of Ambient Temperature on Electrothermal Characteristics in Stacked Nanosheet Transistors with Multiple Lateral Stacks. Nanomaterials 2023, 13, 2971. https://doi.org/10.3390/nano13222971

Zhao P, Cao L, Wang G, Wu Z, Yin H. The Impact of Ambient Temperature on Electrothermal Characteristics in Stacked Nanosheet Transistors with Multiple Lateral Stacks. Nanomaterials. 2023; 13(22):2971. https://doi.org/10.3390/nano13222971

Chicago/Turabian StyleZhao, Peng, Lei Cao, Guilei Wang, Zhenhua Wu, and Huaxiang Yin. 2023. "The Impact of Ambient Temperature on Electrothermal Characteristics in Stacked Nanosheet Transistors with Multiple Lateral Stacks" Nanomaterials 13, no. 22: 2971. https://doi.org/10.3390/nano13222971