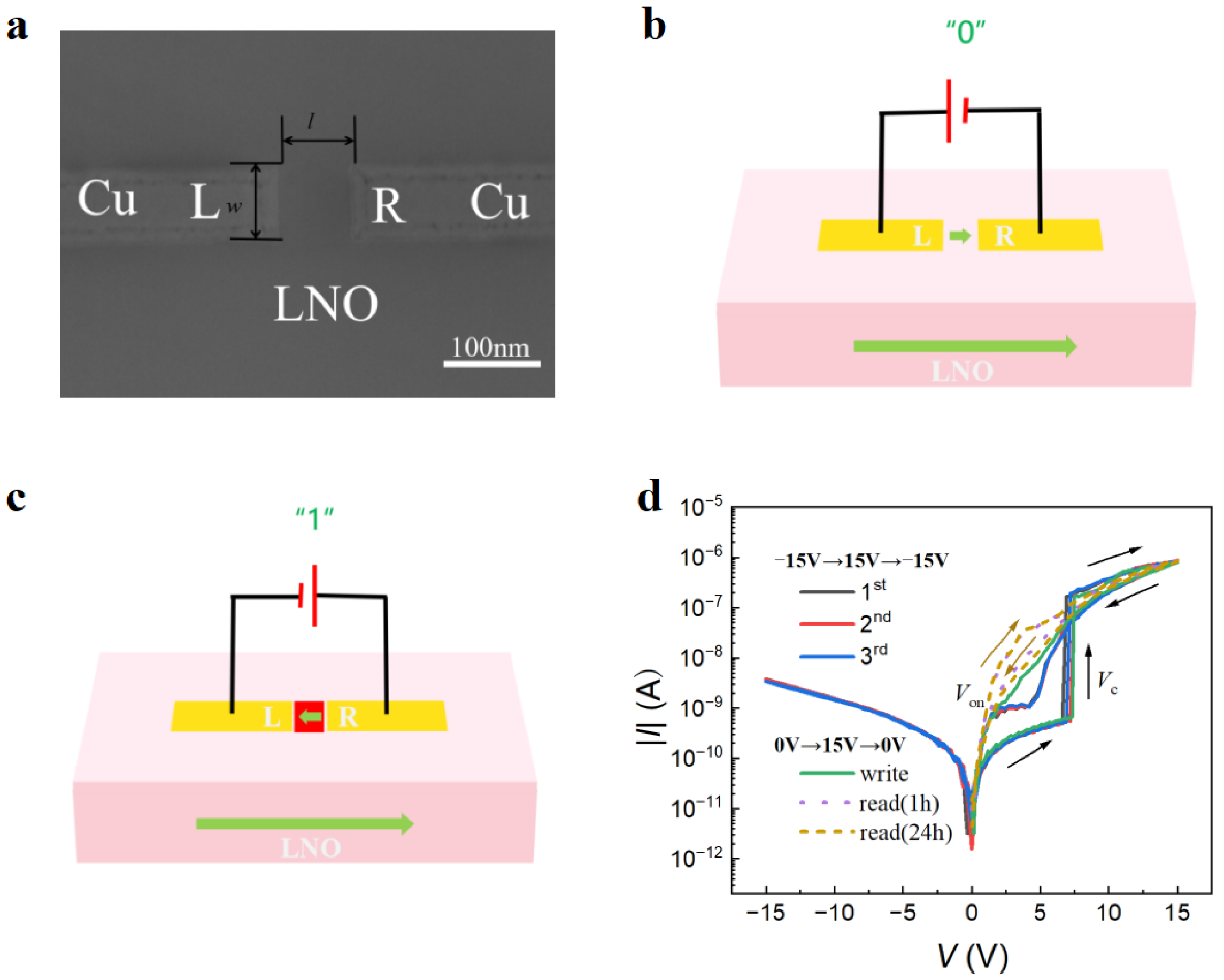

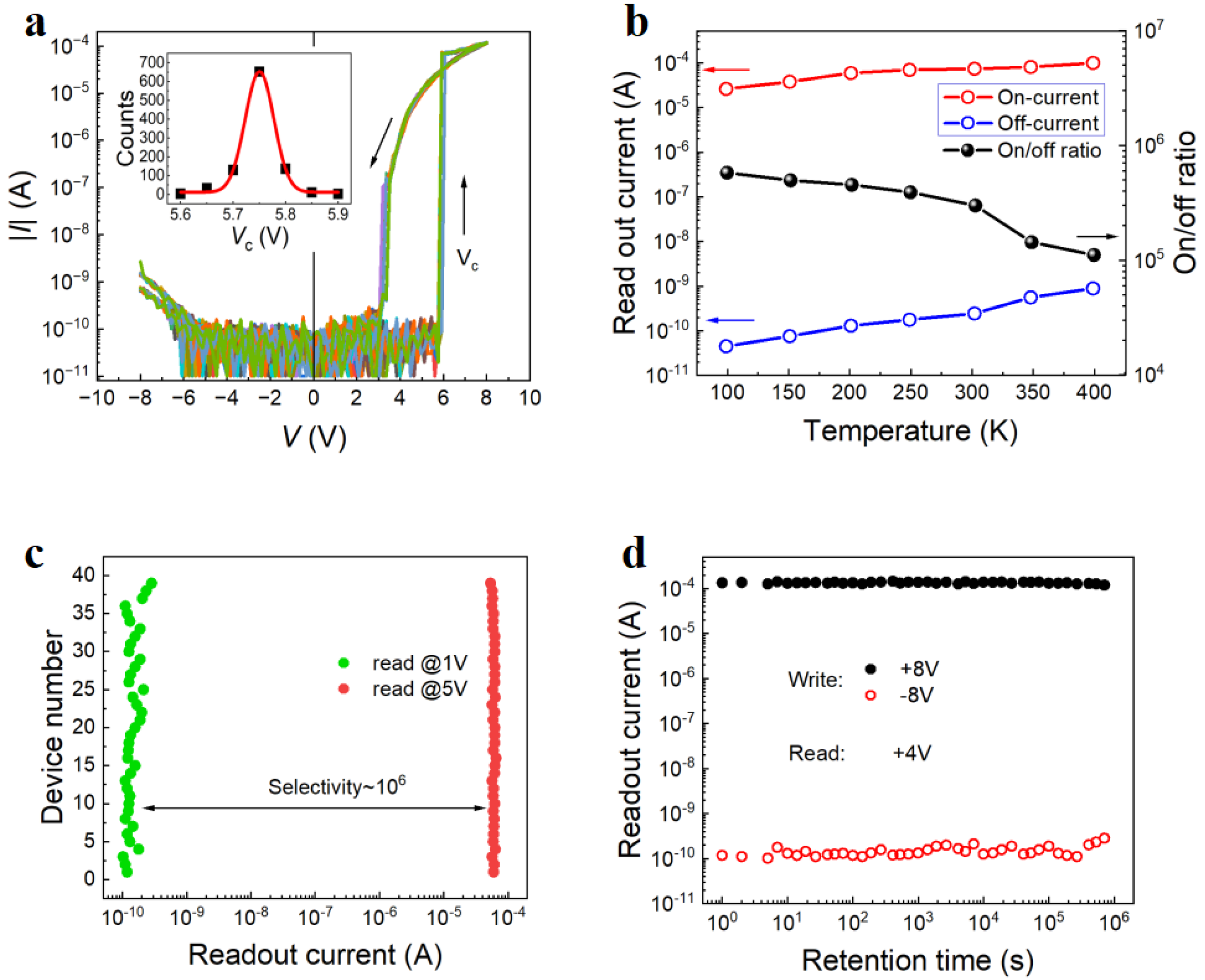

High-Performance LiNbO3 Domain Wall Memory Devices with Enhanced Selectivity via Optimized Metal–Semiconductor Contact

Abstract

1. Introduction

2. Experimental Methods

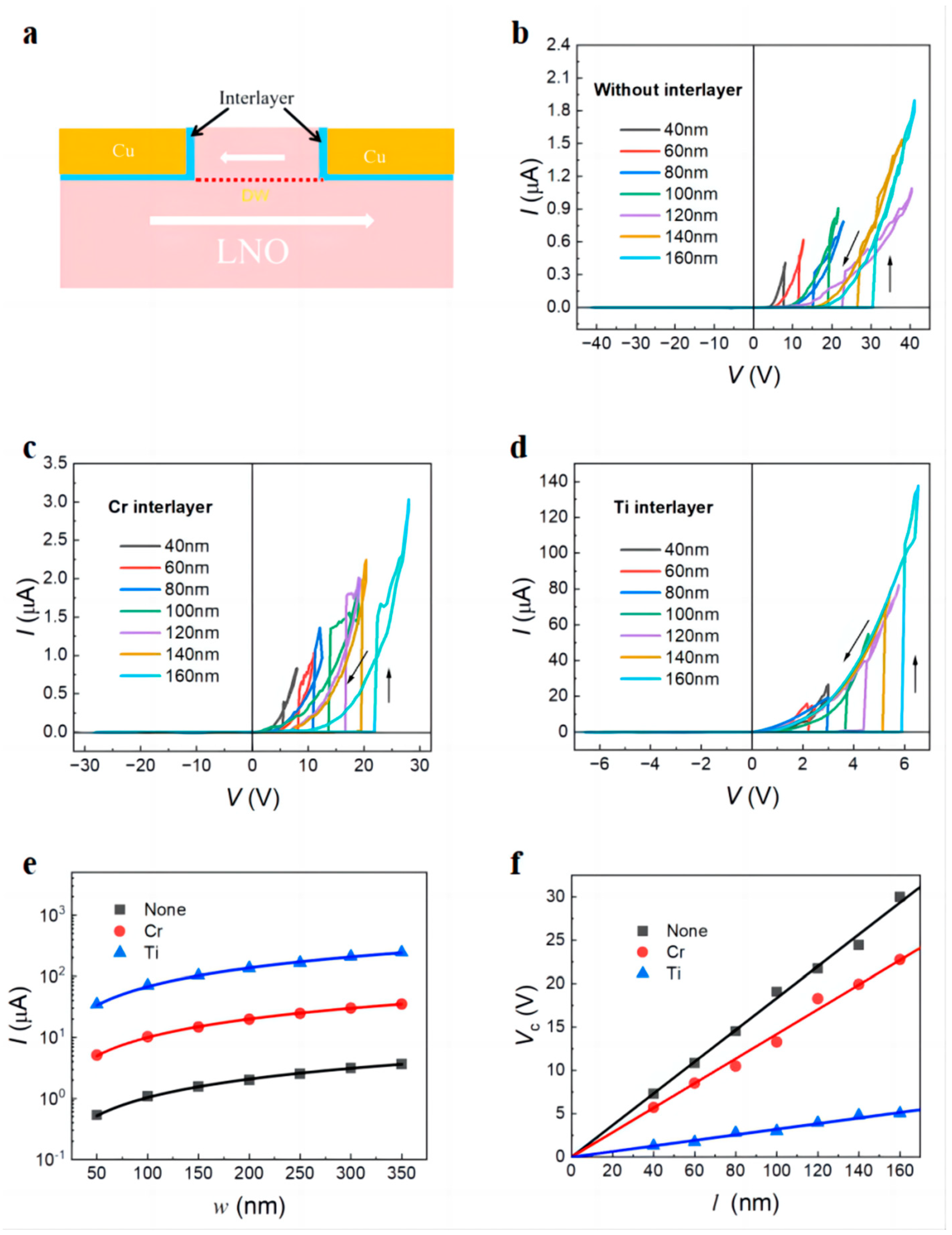

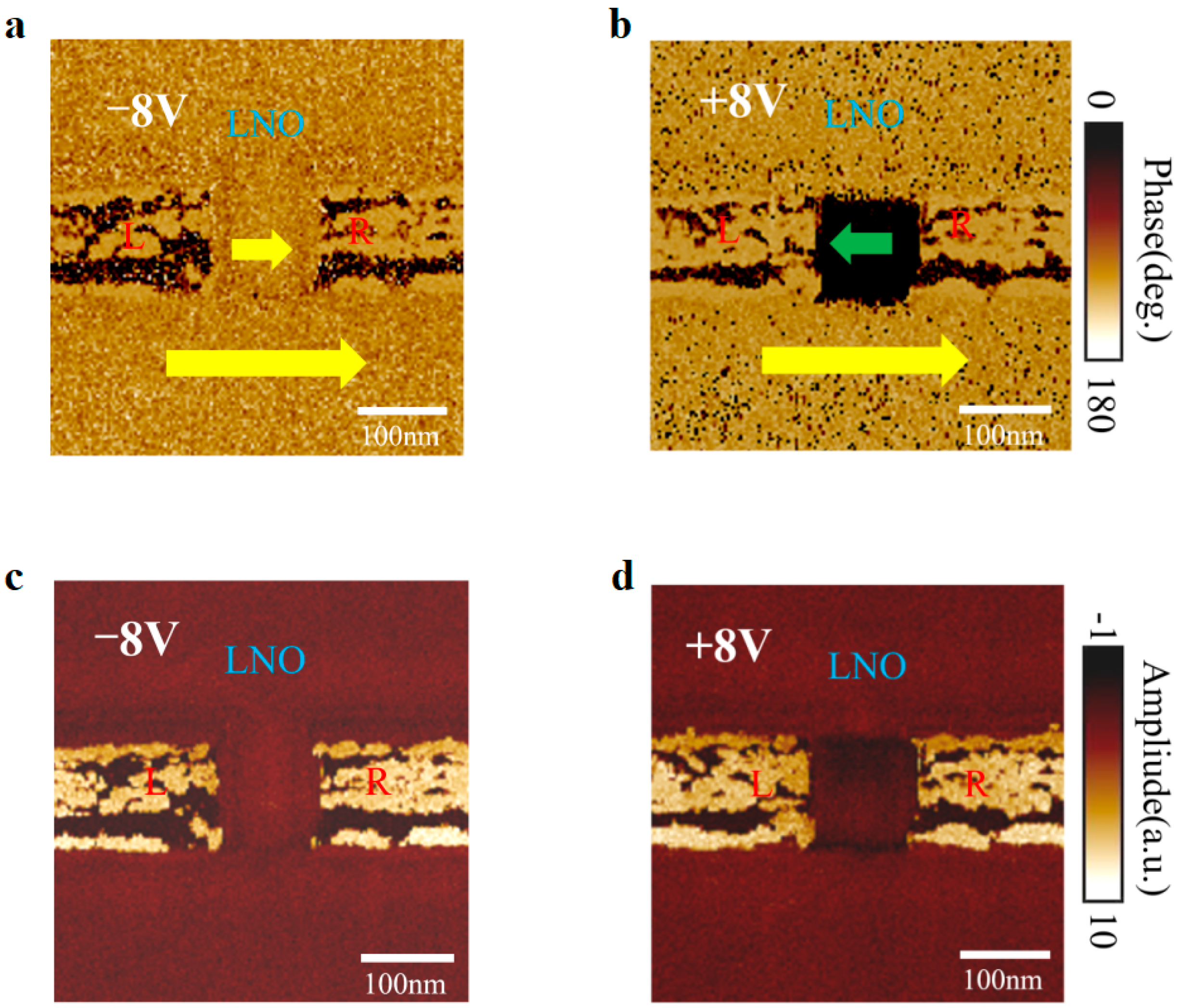

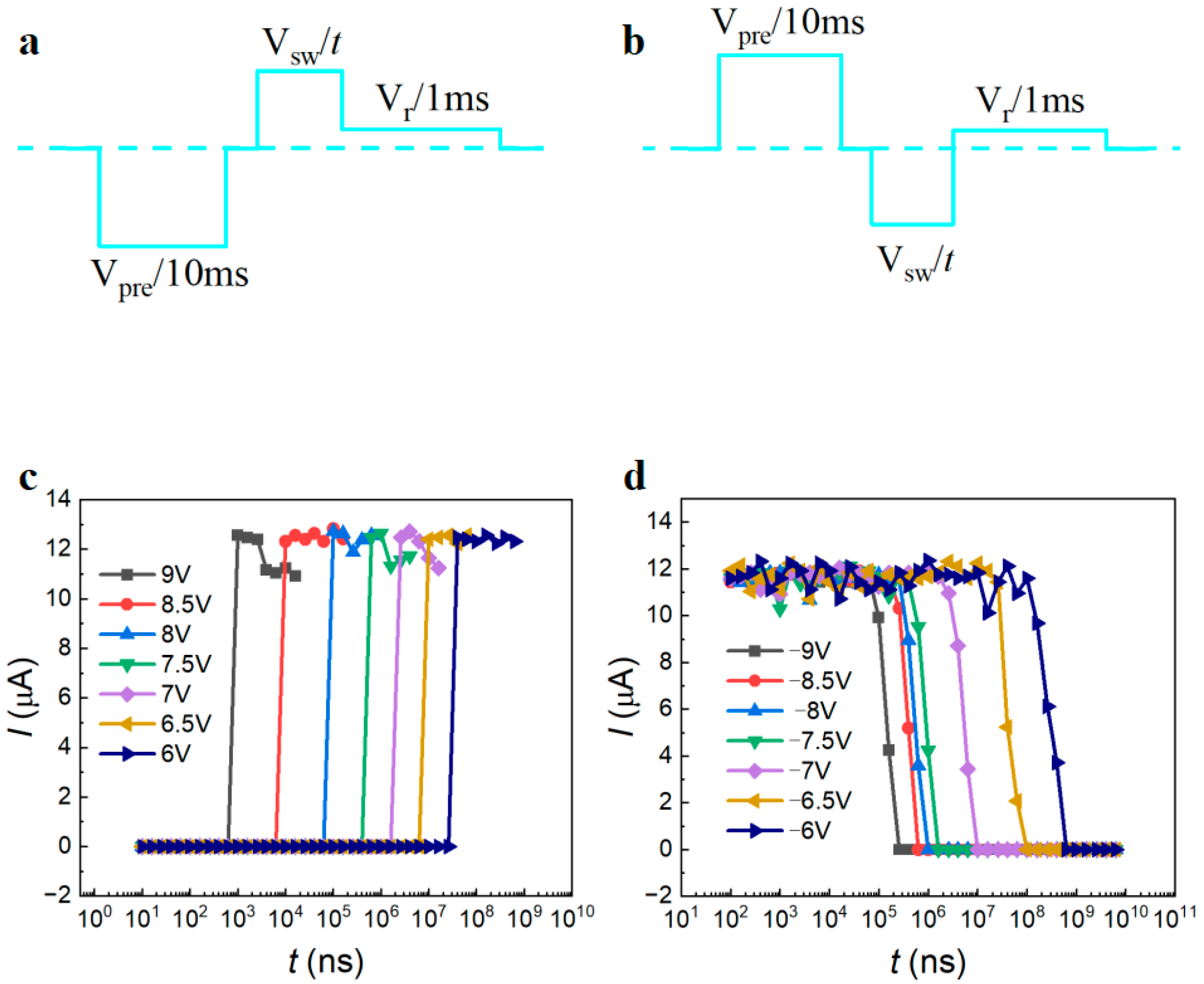

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Li, Z.; Meng, J.; Yu, J.; Liu, Y.; Wang, T.; Xu, K.; Zhu, H.; Sun, Q.; Zhang, D.W.; Chen, L. Stabilizing the Ferroelectric Phase in HfAlO Ferroelectric Tunnel Junction with Different Bottom Electrodes. IEEE Electron. Device Lett. 2023, 6, 947–950. [Google Scholar] [CrossRef]

- Liu, C.; Yang, Q.; Zeng, B.; Jiang, Y.; Zheng, S.; Liao, J.; Dai, S.; Zhong, X.; Zhou, Y.; Liao, M. Orientation independent growth of uniform ferroelectric Hf0.5Zr0.5O2 thin films on silicon for high-density 3D memory applications. Adv. Fun. Mater. 2022, 49, 2209604. [Google Scholar] [CrossRef]

- Wang, T.Y.; Meng, J.L.; Rao, M.Y.; He, Z.Y.; Chen, L.; Zhu, H.; Sun, Q.; Ding, S.J.; Bao, W.Z.; Zhou, P.; et al. Three-dimensional nanoscale flexible memristor networks with ultralow power for information transmission and processing application. Nano Lett. 2022, 6, 4111–4120. [Google Scholar] [CrossRef]

- Meng, J.L.; Wang, T.Y.; He, Z.Y.; Chen, L.; Zhu, H.; Ji, L.; Sun, Q.; Ding, S.J.; Bao, W.Z.; Zhou, P.; et al. Flexible boron nitride-based memristor for in situ digital and analogue neuromorphic computing applications. Mater. Horiz. 2021, 2, 538–546. [Google Scholar] [CrossRef]

- Wang, T.; Meng, J.; Zhou, X.; Liu, Y.; He, Z.; Han, Q.; Li, Q.; Yu, J.; Li, Z.; Liu, Y.; et al. Reconfigurable neuromorphic memristor network for ultralow-power smart textile electronics. Nat. Commun. 2022, 1, 7432. [Google Scholar] [CrossRef]

- Xia, F.; Jiang, D.J.; Xiong, J.; Sun, N.H. A Survey of Phase Change Memory Systems. J. Comput. Sci. Technol. 2015, 30, 121–144. [Google Scholar] [CrossRef]

- Dong, X.; Jouppi, N.P.; Xie, Y. PCRAMsim: System-Level Performance, Energy, and Area Modeling for Phase-Change RAM. In Proceedings of the IEEE/ACM International Conference on Computer-Aided Design, ICCAD, San Jose, CA, USA, 2–5 November 2009. [Google Scholar]

- Chen, Y.Y.; Goux, L.; Clima, S.; Govoreanu, B.; Degraeve, R.; Kar, G.S.; Fantini, A.; Groeseneken, G.; Wouters, D.J.; Jurczak, M. Endurance/Retention Trade-Off on HfO2/Metal Cap 1T1R Bipolar RRAM. IEEE Trans. Electron Dev. 2013, 60, 1114–1121. [Google Scholar] [CrossRef]

- Boukhobza, J.; Rubini, S.; Chen, R.; Shao, Z. Emerging NVM: A Survey on Architectural Integration and Research Challenges. ACM Trans. Design Autom. Electr. Syst. 2018, 23, 14. [Google Scholar] [CrossRef]

- Khan, A.I.; Keshavarzi, A.; Datta, S. The Future of Ferroelectric Field-Effect Transistor Technology. Nat. Electron. 2020, 3, 588–597. [Google Scholar] [CrossRef]

- Endoh, T.; Koike, H.; Ikeda, S.; Hanyu, T.; Ohno, H. An Overview of Nonvolatile Emerging Memories-Spintronics for Working Memories. IEEE J. Emerg. Sel. Top. Circuits Syst. 2016, 6, 109–119. [Google Scholar] [CrossRef]

- Sun, J.; Zheng, X.J. Modeling of MFIS-FETS for the Application of Ferroelectric Random Access Memory. IEEE Trans. Electron. Devices 2011, 58, 3559–3565. [Google Scholar] [CrossRef]

- Hiroshi, I. Current Status and Prospects of FET-type Ferroelectric Memories. In Proceedings of the 1999 57th Annual Device Research Conference Digest, Santa Barbara, CA, USA, 23 June 1999. [Google Scholar]

- Eliseev, E.A.; Morozovska, A.N.; Svechnikov, G.S.; Gopalan, V.; Shur, V.Y. Static Conductivity of Charged Domain Walls in Uniaxial Ferroelectric Semiconductors. Phys. Rev. B 2011, 83, 235313. [Google Scholar] [CrossRef]

- Schröder, M.; Haußmann, A.; Thiessen, A.; Soergel, E.; Woike, T.; Eng, L.M. Conducting Domain Walls in Lithium Niobate Single Crystals. Adv. Funct. Mater. 2012, 22, 3936–3944. [Google Scholar] [CrossRef]

- Gureev, M.Y.; Mokry, P.; Tagantsev, A.K.; Setter, N. Ferroelectric Charged Domain Walls in an Applied Electric Field. Phys. Rev. B 2012, 86, 104104. [Google Scholar] [CrossRef]

- McCluskey, C.J.; Colbear, M.G.; McConville, J.P.V.; McCartan, S.J.; Maguire, J.R.; Conroy, M.; Moore, K.; Harvey, A.; Trier, F.; Bangert, U.; et al. Ultrahigh Carrier Mobilities in Ferroelectric Domain Wall Corbino Cones at Room Temperature. Adv. Mater. 2022, 34, 2204298. [Google Scholar] [CrossRef] [PubMed]

- Ma, J.; Ma, J.; Zhang, Q.; Peng, R.; Wang, J.; Liu, C.; Wang, M.; Li, N.; Chen, M.; Cheng, X.; et al. Controllable Conductive Readout in Self-assembled, Topologically Confined Ferroelectric Domain Walls. Nat. Nanotechnol. 2018, 13, 947–952. [Google Scholar] [CrossRef] [PubMed]

- Wang, J.; Ma, J.; Huang, H.; Ma, J.; Jafri, H.M.; Fan, Y.; Yang, H.; Wang, Y.; Chen, M.; Liu, D.; et al. Ferroelectric Domain-wall Logic Units. Nat. Commun. 2022, 13, 3255. [Google Scholar] [CrossRef] [PubMed]

- Seidel, J.; Martin, L.W.; He, Q.; Zhan, Q.; Chu, Y.H.; Rother, A.; Hawkridge, M.E.; Maksymovych, P.; Yu, P.; Gajek, M.; et al. Conduction at Domain Walls in Oxide Multiferroics. Nat. Mater. 2009, 8, 229–234. [Google Scholar] [CrossRef]

- Sharma, P.; Zhang, Q.; Sando, D.; Lei, C.H.; Liu, Y.; Li, J.Y.; Nagarajan, V.; Seidel, J. Nonvolatile Ferroelectric Domain Wall Memory. Sci. Adv. 2017, 3, 1700512. [Google Scholar] [CrossRef]

- Crassous, A.; Sluka, T.; Tagantsev, A.K.; Setter, N. Polarization Charge as A Reconfigurable Quasi-Dopant in Ferroelectric Thin Films. Nat. Nanotechnol. 2015, 10, 614–618. [Google Scholar] [CrossRef]

- Bai, Z.L.; Cheng, X.X.; Chen, D.F.; Zhang, D.W.; Chen, L.Q.; Scott, J.F.; Hwang, C.S.; Jiang, A.Q. Hierarchical Domain Structure and Extremely Large Wall Current in Epitaxial BiFeO3 Thin Films. Adv. Funct. Mater. 2018, 28, 1801725. [Google Scholar] [CrossRef]

- Guyonnet, J.; Gaponenko, I.; Gariglio, S.; Paruch, P. Conduction at Domain Walls in Insulating Pb(Zr0.2Ti0.8)O3 Thin Films. Adv. Mater. 2011, 23, 5377–5382. [Google Scholar] [CrossRef] [PubMed]

- Jiang, J.; Bai, Z.L.; Chen, Z.H.; He, L.; Zhang, D.W.; Zhang, Q.H.; Shi, J.A.; Park, M.H.; Scott, J.F.; Hwang, C.S.; et al. Temporary Formation of Highly Conducting Domain Walls for Non-Destructive Read-Out of Ferroelectric Domain-wall Resistance Switching Memories. Nat. Mater. 2018, 17, 49–56. [Google Scholar] [CrossRef] [PubMed]

- Farokhipoor, S.; Noheda, B. Conduction Through 71 Degrees Domain Walls in BiFeO3 Thin Films. Phys. Rev. Lett. 2011, 107, 127601. [Google Scholar] [CrossRef] [PubMed]

- Johnson, J.B. Thermal Agitation of Electricity in Conductors. Nature 1927, 119, 50–51. [Google Scholar] [CrossRef]

- Nyquist, H. Thermal Agitation of Electric Charge in Conductors. Phys. Rev. 1928, 32, 110–113. [Google Scholar] [CrossRef]

- Werner, C.S.; Herr, S.J.; Buse, K.; Sturman, B.; Soergel, E.; Razzaghi, C.; Breunig, I. Large and Accessible Conductivity of Charged Domain Walls in Lithium Niobate. Sci. Rep. 2017, 7, 9862. [Google Scholar] [CrossRef]

- Godau, C.; Kampfe, T.; Thiessen, A.; Eng, L.M.; Haussmann, A. Enhancing the Domain Wall Conductivity in Lithium Niobate Single Crystals. ACS Nano 2017, 11, 4816–4824. [Google Scholar] [CrossRef]

- Jiang, A.Q.; Zhang, Y. Next-generation ferroelectric domain-wall memories: Principle and architecture. NPG Asia Mater. 2019, 11, 2. [Google Scholar] [CrossRef]

- Chai, X.; Jiang, J.; Zhang, Q.; Hou, X.; Meng, F.; Wang, J.; Gu, L.; Zhang, D.W.; Jiang, A.Q. Nonvolatile ferroelectric field-effect transistors. Nat. Commun. 2020, 11, 2811. [Google Scholar] [CrossRef]

- Jiang, A.Q.; Jiang, J.; Wang, C. Low-voltage operation of high-density ferroelectric domain wall memory. In Proceedings of the 2020 IEEE 15th International Conference on Solid-State & Integrated Circuit Technology (ICSICT), Kunming, China, 3–6 November 2020. [Google Scholar]

- Wang, C.; Wang, T.; Zhang, W.; Jiang, J.; Chen, L.; Jiang, A. Analog ferroelectric domain-wall memories and synaptic devices integrated with Si substrates. Nano Res. 2022, 15, 3606–3613. [Google Scholar] [CrossRef]

- Sun, J.; Li, Y.; Ou, Y.; Huang, Q.; Liao, X.; Chen, Z.; Chai, X.; Zhuang, X.; Zhang, W.; Wang, C.; et al. In-Memory Computing of Multilevel Ferroelectric Domain Wall Diodes at LiNbO3 Interfaces. Adv. Funct. Mater. 2022, 32, 2207418. [Google Scholar] [CrossRef]

- Lu, H.D.; Tan, Y.Z.; McConville, J.P.V.; Ahmadi, Z.; Wang, B.; Conroy, M.; Moore, K.; Bangert, U.; Shield, J.E.; Chen, L.Q.; et al. Electrical Tunability of Domain Wall Conductivity in LiNbO3 Thin Films. Adv. Mater. 2019, 31, 1902890. [Google Scholar] [CrossRef]

- Tselev, A.; Yu, P.; Cao, Y.; Dedon, L.R.; Martin, L.W.; Kalinin, S.V.; Maksymovych, P. Microwave ac conductivity of domain walls in ferroelectric thin films. Nat. Commun. 2016, 7, 11630. [Google Scholar] [CrossRef]

- Jiang, A.Q.; Geng, W.P.; Lv, P.; Hong, J.W.; Jiang, J.; Wang, C.; Chai, X.J.; Lian, J.W.; Zhang, Y.; Huang, R.; et al. Ferroelectric Domain Wall Memory with Embedded Selector Realized in LiNbO3 Single Crystals Integrated on Si Wafers. Nat. Mater. 2020, 19, 1188–1194. [Google Scholar] [CrossRef] [PubMed]

- Warren, W.L.; Dimos, D.; Pike, G.E.; Tuttle, B.A.; Raymond, M.V.; Ramesh, R.; Evans, J.T. Voltage shifts and imprint in ferroelectric capacitors. Appl. Phys. Lett. 1995, 67, 866. [Google Scholar] [CrossRef]

- Grossmann, M.; Lohse, O.; Bolten, D.; Boettger, U.; Schneller, T.; Waser, R. The Interface Screening Model as Origin of Imprint in PbZrxTi1-xO3 Thin Films. I. Dopant, Illumination, and Bias Dependence. J. Appl. Phys. 2002, 92, 2680. [Google Scholar] [CrossRef]

- Buragohain, P.; Erickson, A.; Kariuki, P.; Mittmann, T.; Richter, C.; Patrick, D.; Lomenzo, P.D.; Lu, H.D.; Schenk, T.; Mikolajick, T.; et al. Fluid Imprint and Inertial Switching in Ferroelectric La:HfO2 Capacitors. ACS Appl. Mater. Interfaces 2019, 11, 35115–35121. [Google Scholar] [CrossRef] [PubMed]

- Sharma, P.; Seidel, J. Neuromorphic functionality of ferroelectric domain walls. Neuromorphic Comput. Eng. 2023, 3, 22001. [Google Scholar] [CrossRef]

- Zhang, W.; Shen, B.W.; Fan, H.C.; Hu, D.; Jiang, A.; Jiang, J. Nonvolatile Ferroelectric LiNbO3 Domain Wall Crossbar Memory. IEEE Electron. Device Lett. 2023, 3, 420–423. [Google Scholar] [CrossRef]

- Pankaj, S.; Theodore, S.M.; Colombo, L.; Jan, S. Roadmap for Ferroelectric Domain Wall Nanoelectronics. Adv. Funct. Mater. 2022, 32, 21110263. [Google Scholar]

- Inoue, Y.; Watanabe, Y. Use of LiNbO3 for Design of Device-type Catalysts with Activity Controllable Functions. Catal. Today 1993, 16, 487–494. [Google Scholar] [CrossRef]

- Chen, Y.; Zhuang, X.; Chai, X.; Jiang, X.; Sun, J.; Jiang, J.; Jiang, A. Improved polarization retention in LiNbO3 single-crystal memory cells with enhanced etching angles. J. Mater. Sci. 2021, 56, 11209–11218. [Google Scholar] [CrossRef]

- Johnson, J.B. Thermal Agitation of Electricity in Conductors. Phys. Rev. 1928, 32, 97. [Google Scholar] [CrossRef]

- Merz, W.J. Domain Formation and Domain Wall Motions in Ferroelectric BaTiO3, Single Crystals. Phys. Rev. 1954, 95, 690–698. [Google Scholar] [CrossRef]

- Zhang, W.J.; Wang, C.; Jiang, J.; Jiang, A.Q. Fast Operations of Nonvolatile Ferroelectric Domain Wall Memory with Inhibited Space Charge Injection. ACS Appl. Mater. Interfaces 2022, 14, 32227–32235. [Google Scholar] [CrossRef] [PubMed]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jiang, H.; Dai, C.; Shen, B.; Jiang, J. High-Performance LiNbO3 Domain Wall Memory Devices with Enhanced Selectivity via Optimized Metal–Semiconductor Contact. Nanomaterials 2024, 14, 1031. https://doi.org/10.3390/nano14121031

Jiang H, Dai C, Shen B, Jiang J. High-Performance LiNbO3 Domain Wall Memory Devices with Enhanced Selectivity via Optimized Metal–Semiconductor Contact. Nanomaterials. 2024; 14(12):1031. https://doi.org/10.3390/nano14121031

Chicago/Turabian StyleJiang, Haiqing, Cuihua Dai, Bowen Shen, and Jun Jiang. 2024. "High-Performance LiNbO3 Domain Wall Memory Devices with Enhanced Selectivity via Optimized Metal–Semiconductor Contact" Nanomaterials 14, no. 12: 1031. https://doi.org/10.3390/nano14121031

APA StyleJiang, H., Dai, C., Shen, B., & Jiang, J. (2024). High-Performance LiNbO3 Domain Wall Memory Devices with Enhanced Selectivity via Optimized Metal–Semiconductor Contact. Nanomaterials, 14(12), 1031. https://doi.org/10.3390/nano14121031