High-Breakdown and Low-Leakage 4H-SiC MOS Capacitor Based on HfO2/SiO2 Stacked Gate Dielectric in Trench Structures

Abstract

1. Introduction

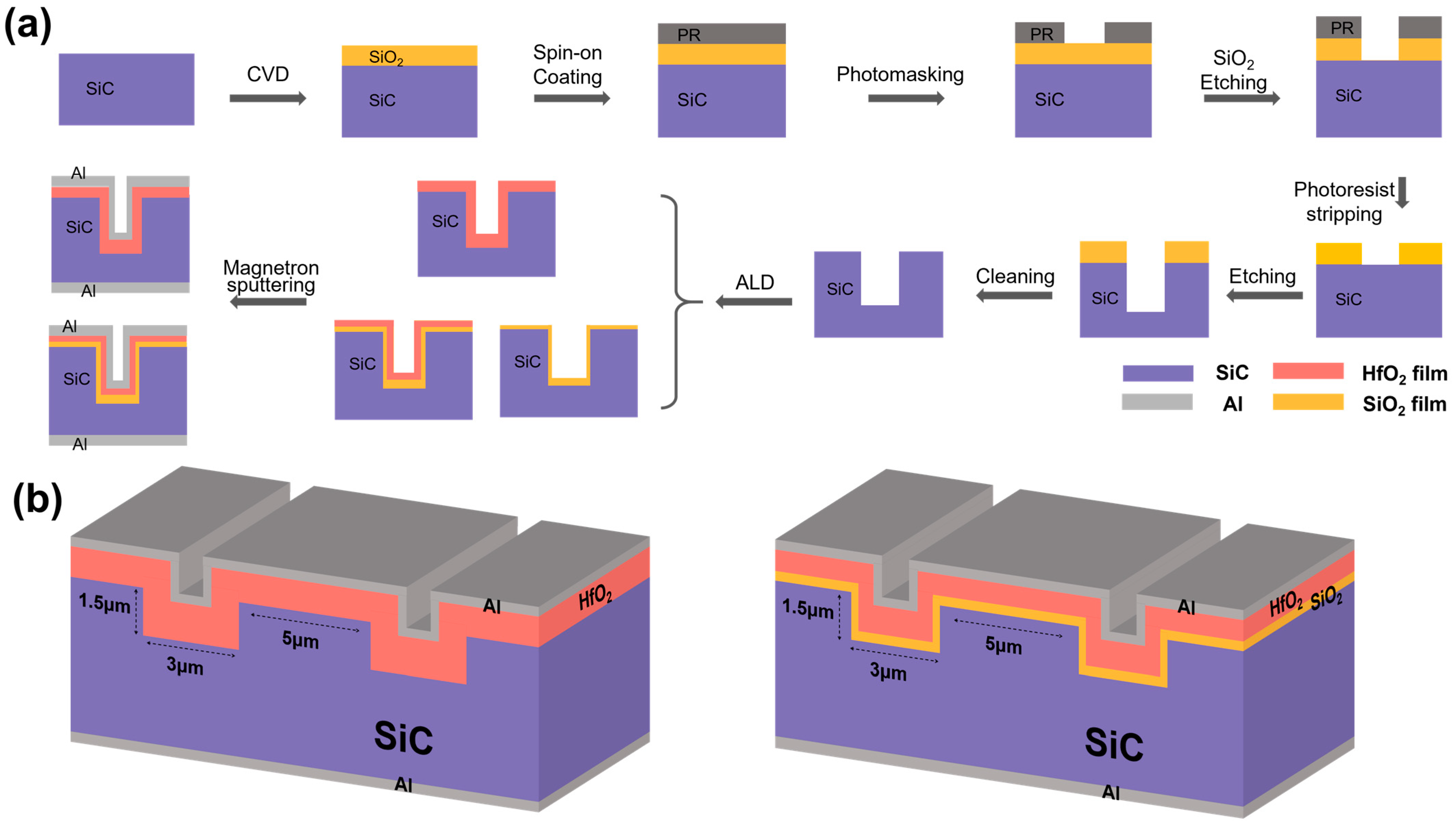

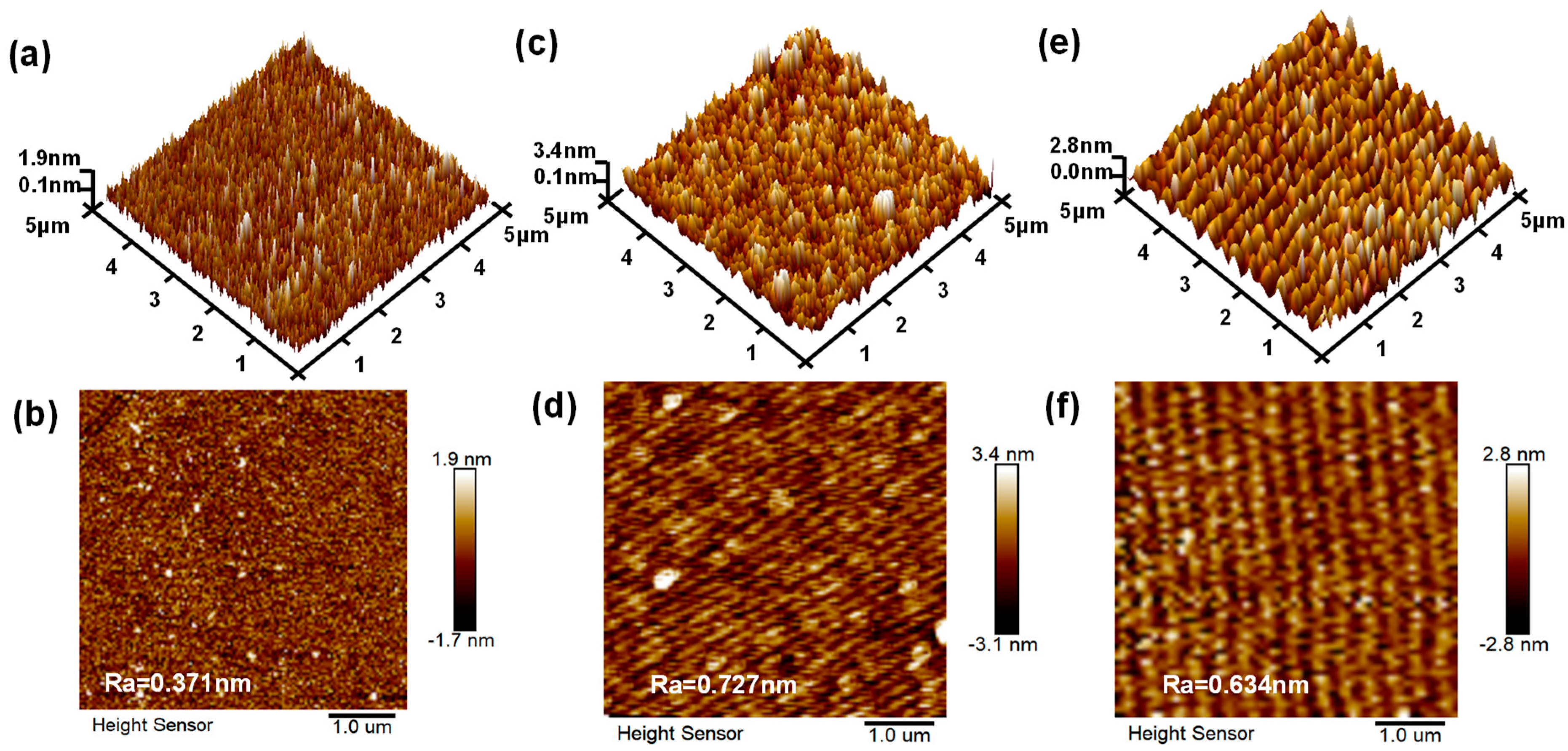

2. Experimental Section

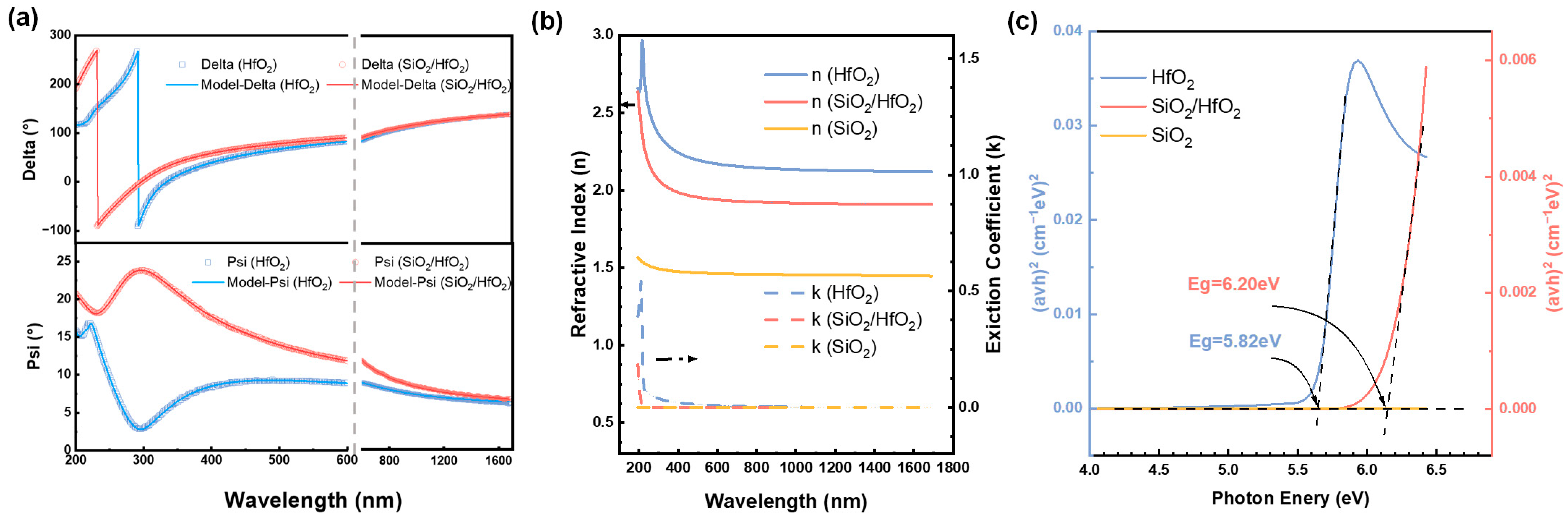

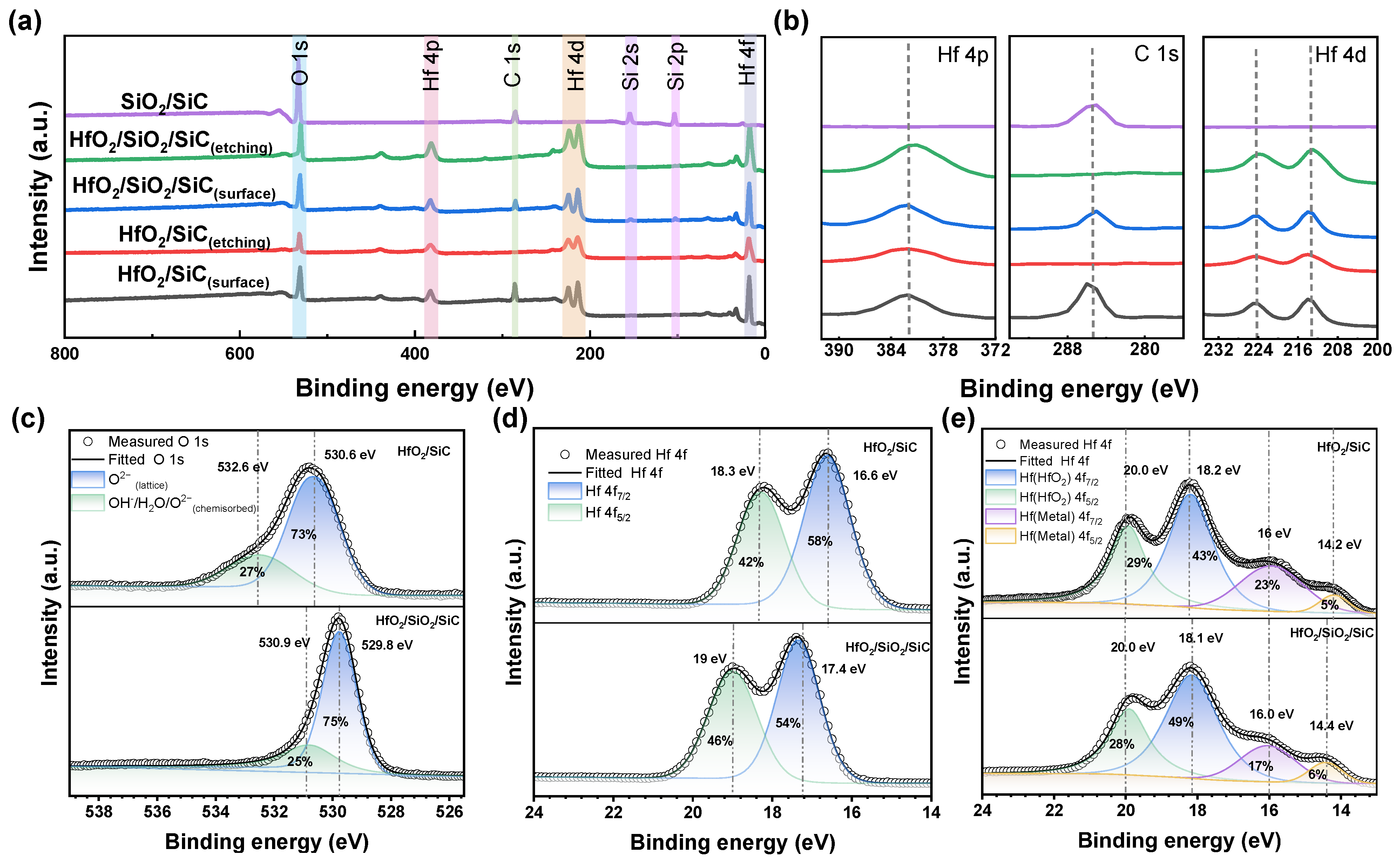

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Baliga, B.J. Fundamentals of Power Semiconductor Devices; Springer Nature: Cham, Switzerland, 2019. [Google Scholar]

- Kimoto, T. Material Science and Device Physics in SiC Technology for High-Voltage Power Devices. Jpn. J. Appl. Phys. 2015, 54, 040103. [Google Scholar] [CrossRef]

- Jayant Baliga, B. Silicon Carbide Power Devices: Progress and Future Outlook. IEEE J. Emerg. Sel. Top. Power Electron. 2023, 11, 2400–2411. [Google Scholar] [CrossRef]

- Kimoto, T. SiC Material Properties. In Wide Bandgap Semiconductor Power Devices; Woodhead Publishing: Cambridge, UK, 2019; pp. 21–42. ISBN 9780081023068. [Google Scholar]

- Qian, J.; Shi, L.; Jin, M.; Bhattacharya, M.; Shimbori, A.; Yu, H.; Houshmand, S.; White, M.H.; Agarwal, A.K. An Investigation of Body Diode Reliability in Commercial 1.2 KV SiC Power MOSFETs with Planar and Trench Structures. Micromachines 2024, 15, 177. [Google Scholar] [CrossRef] [PubMed]

- Siddiqui, A.; Khosa, R.Y.; Usman, M. High-K Dielectrics for 4H-Silicon Carbide: Present Status and Future Perspectives. J. Mater. Chem. C 2021, 9, 5055–5081. [Google Scholar] [CrossRef]

- Cheon, J.; Kim, K. Numerical Simulation Analysis of Switching Characteristics in the Source-Trench MOSFET’s. Electronics 2020, 9, 1895. [Google Scholar] [CrossRef]

- Wirths, S.; Mihaila, A.; Romano, G.; Schneider, N.; Ceccarelli, E.; Alfieri, G.; Arango, Y.; Knoll, L. Study of 1.2kV High-k SiC Power MOSFETS under Harsh Repetitive Switching Conditions. In Proceedings of the 2021 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Nagoya, Japan, 30 May–3 June 2021; pp. 107–110. [Google Scholar] [CrossRef]

- Race, S.; Kumar, P.; Natzke, P.; Kovacevic-Badstuebner, I.; Bathen, M.E.; Grossner, U.; Romano, G.; Arango, Y.; Bolat, S.; Wirths, S.; et al. Gate Impedance Analysis of SiC Power MOSFETs with SiO2 and High-k Dielectric. In Proceedings of the 2023 35th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Hong Kong, China, 28 May–1 June 2023. [Google Scholar] [CrossRef]

- Takaya, H.; Misumi, T.; Fujiwara, H.; Ito, T. 4H-SiC Trench MOSFET with Low On-Resistance at High Temperature. In Proceedings of the 2020 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Vienna, Austria, 13–18 September 2020; pp. 118–121. [Google Scholar] [CrossRef]

- Wei, J.; Wei, Z.; Fu, H.; Cao, J.; Wu, T.; Sun, J.; Zhu, X.; Li, S.; Zhang, L.; Liu, S.; et al. Review on the Reliability Mechanisms of SiC Power MOSFETs: A Comparison between Planar-Gate and Trench-Gate Structures. IEEE Trans. Power Electron. 2023, 38, 8990–9005. [Google Scholar] [CrossRef]

- Hsu, C.-M.; Hwu, J.-G. Investigation of Carbon Interstitials with Varied SiO2 Thickness in HfO2/SiO2/4H-SiC Structure. Appl. Phys. Lett. 2012, 101, 253517. [Google Scholar] [CrossRef]

- Boccarossa, M.; Maresca, L.; Borghese, A.; Riccio, M.; Breglio, G.; Irace, A.; Salvatore, G.A. Substantial Improvement of the Short-Circuit Capability of a 1.2 KV SiC MOSFET by a HfO2/SiO2 Ferroelectric Gate Stack. In Proceedings of the 2024 36th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Bremen, Germany, 2–6 June 2024; pp. 88–91. [Google Scholar] [CrossRef]

- Behera, M.K.; Yarbrough, K.A.; Bahoura, M. Study of Dielectric Properties in Stacked High-k Dielectric Metal Oxide Semiconductor Capacitor (MOSCAP) Devices. J. Mater. Sci. Mater. Electron. 2024, 35, 1316. [Google Scholar] [CrossRef]

- Cheong, K.Y.; Moon, J.H.; Park, T.J.; Kim, J.H.; Hwang, C.S.; Kim, H.J.; Bahng, W.; Kim, N.-K. Improved Electronic Performance of HfO2/SiO2 Stacking Gate Dielectric on 4H SiC. IEEE Trans. Electron Devices 2007, 54, 3409–3413. [Google Scholar] [CrossRef]

- Wang, Z.; Zhang, Z.; Shao, C.; Robertson, J.; Liu, S.; Guo, Y. Tuning the High-κ Oxide (HfO2, ZrO2)/4H-SiC Interface Properties with a SiO2 Interlayer for Power Device Applications. Appl. Surf. Sci. 2020, 527, 146843. [Google Scholar] [CrossRef]

- Zanders, D.; Ciftyurek, E.; Subaşı, E.; Huster, N.; Bock, C.; Kostka, A.; Rogalla, D.; Schierbaum, K.; Devi, A. PEALD of HfO2 Thin Films: Precursor Tuning and a New Near-Ambient-Pressure XPS Approach to in Situ Examination of Thin-Film Surfaces Exposed to Reactive Gases. ACS Appl. Mater. Interfaces 2019, 11, 28407–28422. [Google Scholar] [CrossRef] [PubMed]

- Guo, Z.; Wu, J.; Tian, R.; Wang, F.; Xu, P.; Yang, X.; Fan, Z.; Yang, F.; He, Z. Extraction of the Trench Sidewall Capacitances in an N-Type 4H-SiC Trench Metal– Oxide–Semiconductor Structure. IEEE Trans. Electron Devices 2021, 68, 2879–2885. [Google Scholar] [CrossRef]

- Cheong, K.Y.; Moon, J.H.; Kim, H.J.; Bahng, W.; Kim, N.K. Current Conduction Mechanisms in Atomic-Layer-Deposited HfO2/Nitrided SiO2 Stacked Gate on 4H Silicon Carbide. J. Appl. Phys. 2008, 103, 084113. [Google Scholar] [CrossRef]

- Giannazzo, F.; Schilirò, E.; Lo Nigro, R.; Roccaforte, F.; Yakimova, R. Atomic Layer Deposition of High-k Insulators on Epitaxial Graphene: A Review. Appl. Sci. 2020, 10, 2440. [Google Scholar] [CrossRef]

- Liang, L.; Li, W.; Li, S.; Li, X.; Wu, Y. Interface Properties Study on SiC MOS with High-k Hafnium Silicate Gate Dielectric. AIP Adv. 2018, 8, 125314. [Google Scholar] [CrossRef]

- Fowler, R.H.; Nordheim, L. Electron Emission in Intense Electric Fields. Proc. R. Soc. Lond. Ser. A Contain. Pap. A Math. Phys. Character 1928, 119, 173–181. [Google Scholar] [CrossRef]

- Nguyen, T.T.; Jung, D.H.; Lee, J.J.; Lee, H. Optical Study of Ga2-XSnxO3 (0 ≤ X ≤ 0.7) Thin Films Using Spectroscopic Ellipsometry and Cathodoluminescence. Thin Solid Films 2023, 764, 139611. [Google Scholar] [CrossRef]

- Sahoo, G.S.; Tripathy, S.P.; Joshi, D.S.; Kulkarni, M.S. Development of an Algorithm for Precise and Automated Determination of Optical Band Gap from Tauc Analysis: Case Studies Using Alpha-Irradiated CR-39 Detectors. Radiat. Eff. Defects Solids 2020, 175, 1127–1139. [Google Scholar] [CrossRef]

- Haider, M.; Shaim, A.; Elsayed-Ali, H.E. Boron and Barium Incorporation at the 4H-SiC/SiO2 Interface Using a Laser Multi-Charged Ion Source. J. Mater. Sci. Mater. Electron. 2021, 32, 16079–16087. [Google Scholar] [CrossRef]

- Kumar, M.; Singh, R.P.; Kumar, A. Opto-Electronic Properties of HfO2: A First Principle-Based Spin-Polarized Calculations. Optik 2020, 226, 165937. [Google Scholar] [CrossRef]

- Huang, H.; Wang, Y.; Chen, K.-H.; Fei, X.-X. Leakage Current Behavior in HfO2/SiO2/al2O3 Stacked Dielectric on 4H-SiC Substrate. IEEE J. Electron Devices Soc. 2023, 11, 438–443. [Google Scholar] [CrossRef]

- Renault, O.; Samour, D.; Damlencourt, J.-F.; Blin, D.; Martin, F.; Marthon, S.; Barrett, N.T.; Besson, P. HfO2/SiO2 Interface Chemistry Studied by Synchrotron Radiation X-Ray Photoelectron Spectroscopy. Appl. Phys. Lett. 2002, 81, 3627–3629. [Google Scholar] [CrossRef]

- Lee, T.-E.; Toprasertpong, K.; Takenaka, M.; Takagi, S. Re-Examination of Effects of ALD High-k Materials on Defect Reduction in SiGe Metal–Oxide–Semiconductor Interfaces. AIP Adv. 2021, 11, 085021. [Google Scholar] [CrossRef]

- Chand, U.; Bera, L.K.; Singh, N.; Zhixian, C.; Kumar, S.; Voo, Q.G.R.; Yeo, A.H.; Varghese, B.; Reddy, V.P.; Cakmak, H.; et al. High-K Gate Dielectric for High-Performance SiC Power MOSFET Technology with Low Interface Trap Density, Good Oxide Lifetime (Ttddb≥ 104S), and High Thermal Stability (≥ 800 °C). Diffus. Defect Data Solid State Data Part B Solid State Phenom./Solid State Phenom. 2024, 359, 217–221. [Google Scholar] [CrossRef]

- Esakki, P.; Kailath, B.J. Extraction and Analysis of Gate Leakage Current Mechanism in Silicon Carbide (SiC) MIS Capacitors. IETE J. Res. 2019, 68, 592–601. [Google Scholar] [CrossRef]

- Ouennoughi, Z.; Strenger, C.; Bourouba, F.; Haeublein, V.; Ryssel, H.; Frey, L. Conduction Mechanisms in Thermal Nitride and Dry Gate Oxides Grown on 4H-SiC. Microelectron. Reliab. 2013, 53, 1841–1847. [Google Scholar] [CrossRef]

- Cheong, K.Y.; Bahng, W.; Kim, N.-K. Analysis of Charge Conduction Mechanisms in Nitrided SiO2 Film on 4H SiC. Phys. Lett. A 2008, 372, 529–532. [Google Scholar] [CrossRef]

- Kuang, N.Q.; Liu, N.H.; Zhou, N.W.; Gao, N.B.; Zhao, A.; Tallavarjula, S. Transport Mechanism of the Leakage Current in MIS Capacitor with HfO2/SiO2 Stack Gate. In Proceedings of the 2009 IEEE International Conference of Electron Devices and Solid-State Circuits (EDSSC), Xi’an, China, 25–27 December 2009; Volume 25, pp. 229–232. [Google Scholar] [CrossRef]

- Shi, L.; Qian, J.; Jin, M.; Bhattacharya, M.; Houshmand, S.; Yu, H.; Shimbori, A.; White, M.H.; Agarwal, A.K. Gate Oxide Reliability in Silicon Carbide Planar and Trench Metal-Oxide-Semiconductor Field-Effect Transistors under Positive and Negative Electric Field Stress. Electronics 2024, 13, 4516. [Google Scholar] [CrossRef]

- Wang, X.; Wei, S.; Ke, H.; Ye, X.; Weng, H.; Wong, S.Y.; Yang, W. Simultaneous Electric Dipoles and Flat-Band Voltage Modulation in 4H-SiC MOS Capacitors through HfO2/SiO2 Interface Engineering. J. Phys. D Appl. Phys. 2024, 57, 37LT01. [Google Scholar] [CrossRef]

- Guo, Z.; He, Z.; Wang, F.; Wu, J.; Yang, X.; Fan, Z.; Yang, F. Study of Vertical Capacitance in an N-Type 4H-SiC Stepped Thick-Oxide Trench MOS Structure. IEEE Trans. Electron Devices 2022, 69, 4617–4623. [Google Scholar] [CrossRef]

- Galizia, B.; Fiorenza, P.; Schilirò, E.; Pecz, B.; Foragassy, Z.; Greco, G.; Saggio, M.; Cascino, S.; Lo Nigro, R.; Roccaforte, F. Towards Aluminum Oxide/Aluminum Nitride Insulating Stacks on 4H–SiC by Atomic Layer Deposition. Mater. Sci. Semicond. Process. 2024, 174, 108244. [Google Scholar] [CrossRef]

- Jia, Y.; Lv, H.; Tang, X.; Han, C.; Song, Q.; Zhang, Y.; Zhang, Y.; Dimitrijev, S.; Han, J.; Haasmann, D. Influence of Various NO Annealing Conditions on N-Type and P-Type 4H-SiC MOS Capacitors. J. Mater. Sci. Mater. Electron. 2019, 30, 10302–10310. [Google Scholar] [CrossRef]

- Yang, C.; Huang, H.; Peng, M. Non-Iterative Method for Extracting Complex Permittivity and Thickness of Materials from Reflection-Only Measurements. IEEE Trans. Instrum. Meas. 2022, 71, 1–8. [Google Scholar] [CrossRef]

- Martínez-Puente, M.A.; Horley, P.; Aguirre-Tostado, F.S.; López-Medina, J.; Borbón-Núñez, H.A.; Tiznado, H.; Susarrey-Arce, A.; Martínez-Guerra, E. ALD and PEALD Deposition of HfO2 and Its Effects on the Nature of Oxygen Vacancies. Mater. Sci. Eng. B 2022, 285, 115964. [Google Scholar] [CrossRef]

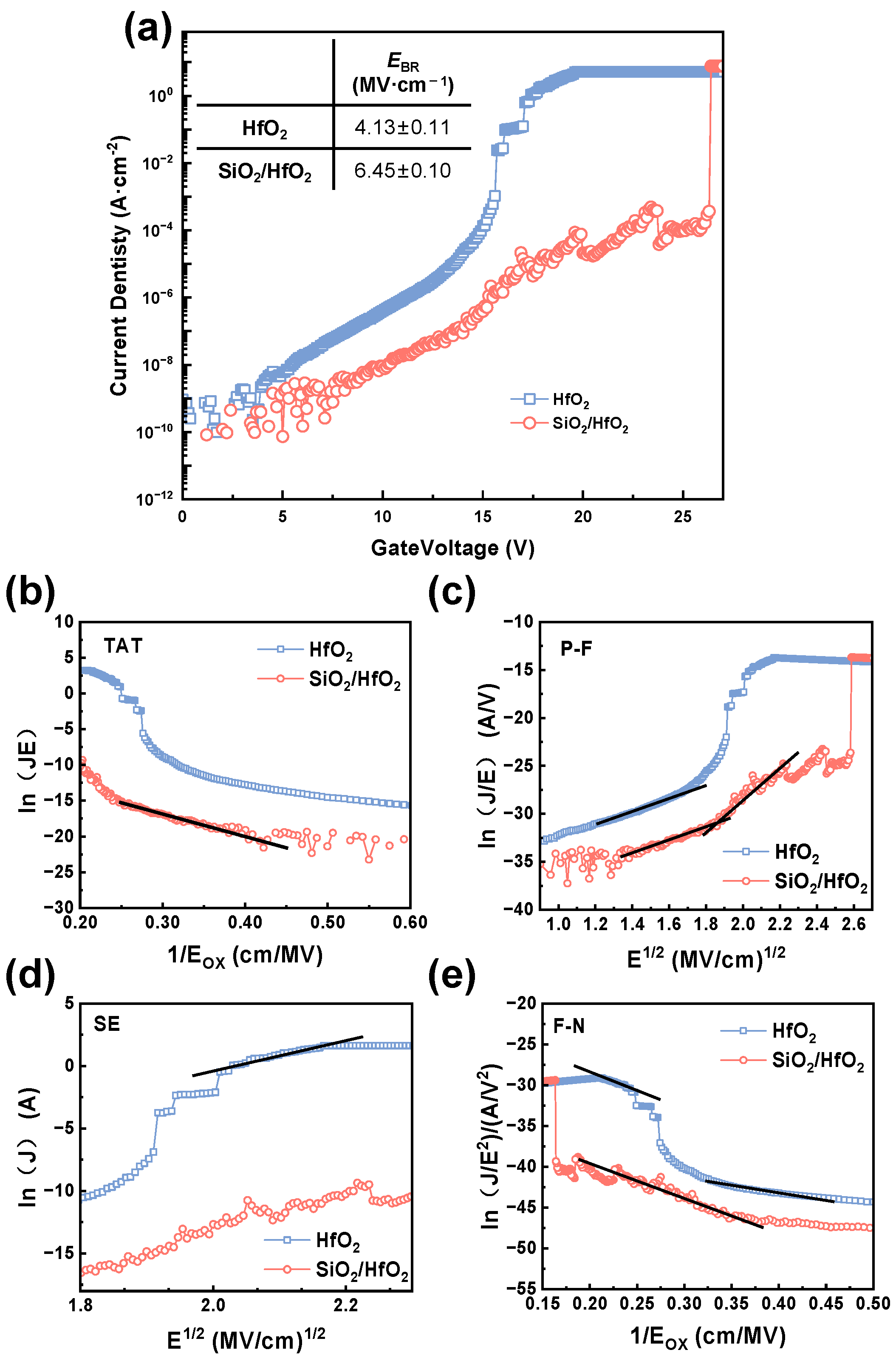

| Conduction Mechanisms | Conduction Plot | Analytical Model Equations | |

|---|---|---|---|

| TAT | ln() ∝ | [32] | |

| P–F emission | ln() ∝ | [18] | |

| Schottky emission | ln() ∝ | [18] | |

| F–N tunneling | ln() ∝ | [33] | |

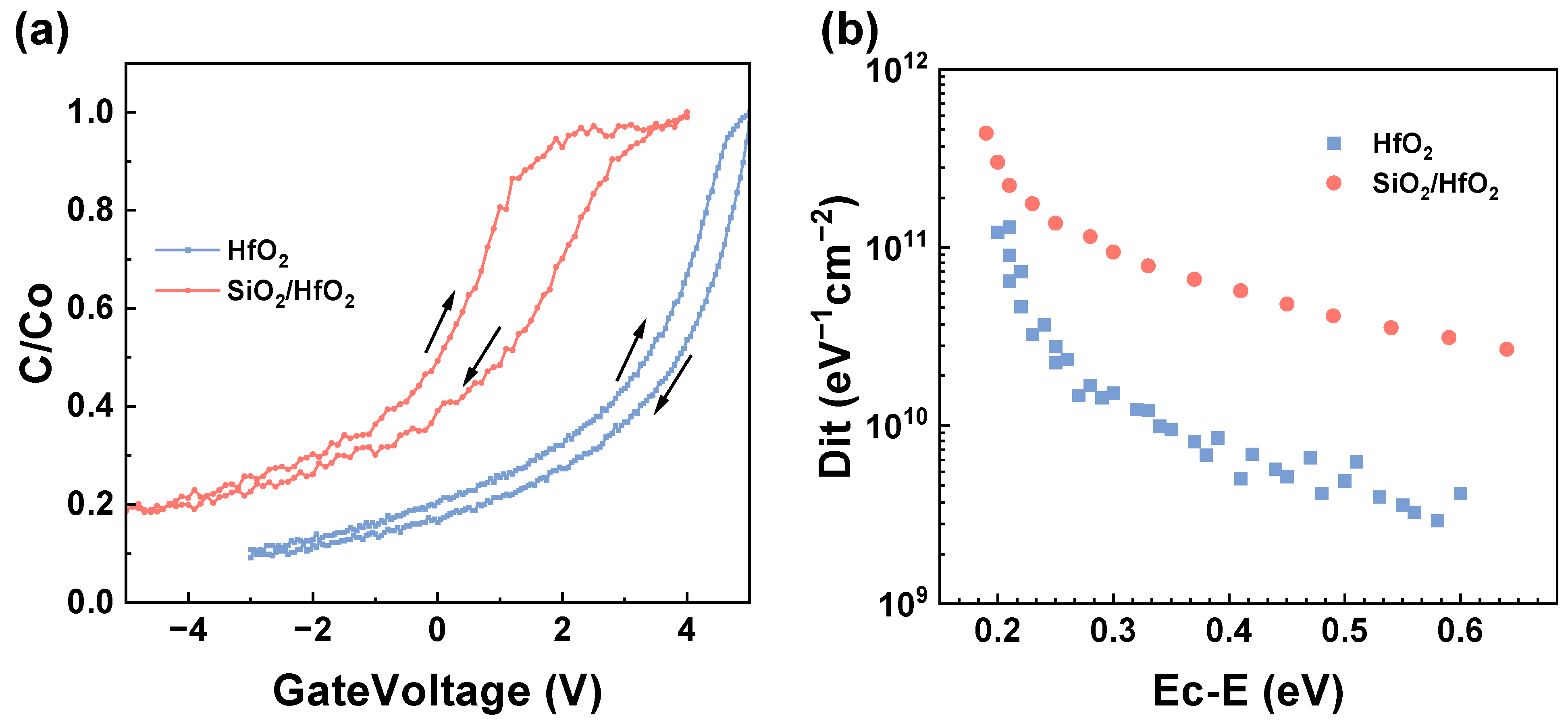

| Stack Information | VFB (V) | EBR (MV·cm−1) | ION_EBR (A·cm−2) | Dit (eV−1·cm−2) EC-0.2 eV | Neff (cm−2) |

|---|---|---|---|---|---|

| HfO2 | 1.65 | 4.1 | 1.1 × 10−3 | 1.30 × 1011 | −1.45 × 1011 |

| SiO2/HfO2 | 0.8 | 6.5 | 3.7 × 10−4 | 4.38 × 1011 | −1.01 × 1011 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Huang, Q.; Guo, Y.; Wang, A.; Gu, L.; Wang, Z.; Ding, C.; Shen, Y.; Ma, H.; Zhang, Q. High-Breakdown and Low-Leakage 4H-SiC MOS Capacitor Based on HfO2/SiO2 Stacked Gate Dielectric in Trench Structures. Nanomaterials 2025, 15, 343. https://doi.org/10.3390/nano15050343

Huang Q, Guo Y, Wang A, Gu L, Wang Z, Ding C, Shen Y, Ma H, Zhang Q. High-Breakdown and Low-Leakage 4H-SiC MOS Capacitor Based on HfO2/SiO2 Stacked Gate Dielectric in Trench Structures. Nanomaterials. 2025; 15(5):343. https://doi.org/10.3390/nano15050343

Chicago/Turabian StyleHuang, Qimin, Yunduo Guo, Anfeng Wang, Lin Gu, Zhenyu Wang, Chengxi Ding, Yi Shen, Hongping Ma, and Qingchun Zhang. 2025. "High-Breakdown and Low-Leakage 4H-SiC MOS Capacitor Based on HfO2/SiO2 Stacked Gate Dielectric in Trench Structures" Nanomaterials 15, no. 5: 343. https://doi.org/10.3390/nano15050343

APA StyleHuang, Q., Guo, Y., Wang, A., Gu, L., Wang, Z., Ding, C., Shen, Y., Ma, H., & Zhang, Q. (2025). High-Breakdown and Low-Leakage 4H-SiC MOS Capacitor Based on HfO2/SiO2 Stacked Gate Dielectric in Trench Structures. Nanomaterials, 15(5), 343. https://doi.org/10.3390/nano15050343