SnO Nanosheet Transistor with Remarkably High Hole Effective Mobility and More than Six Orders of Magnitude On-Current/Off-Current

Abstract

1. Introduction

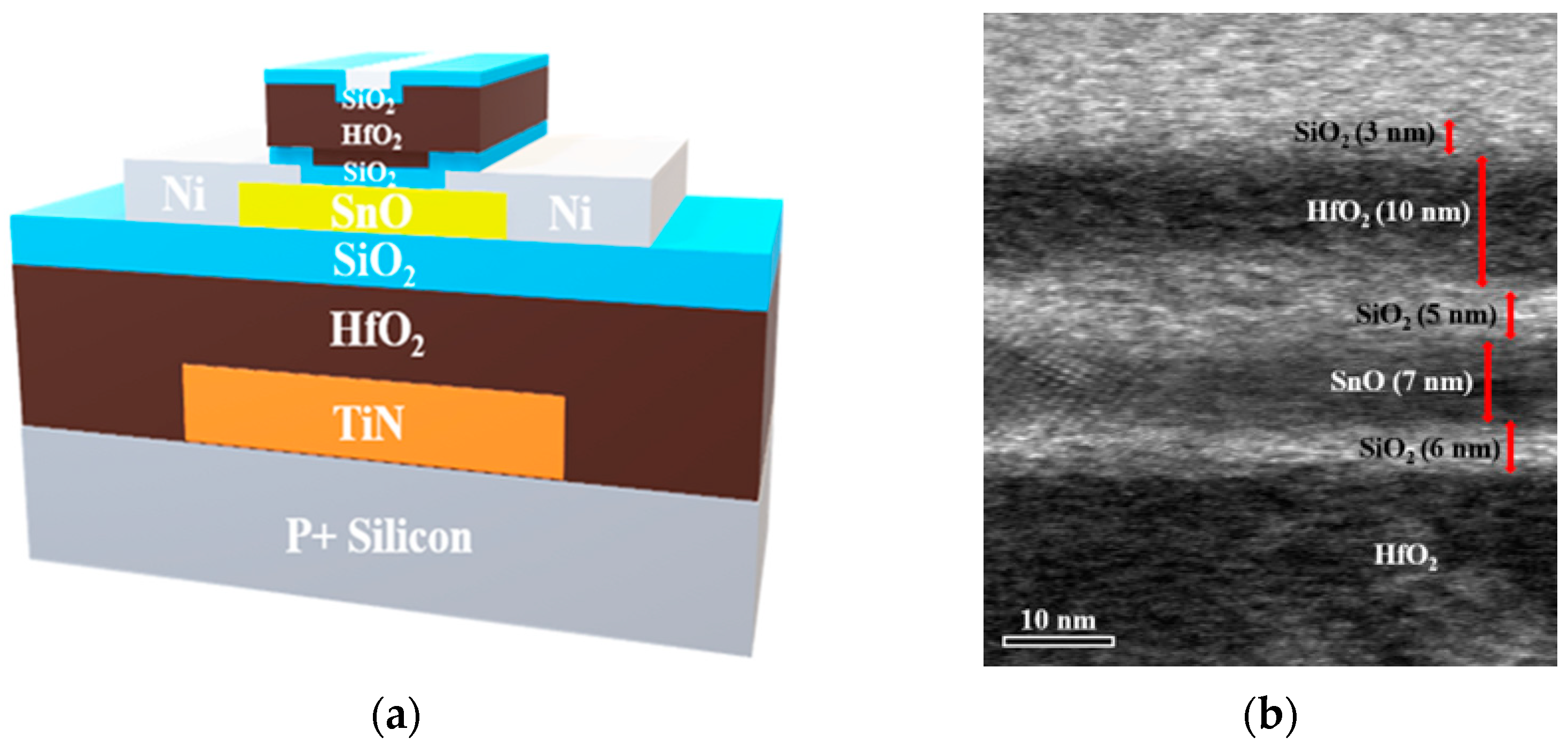

2. Materials and Methods

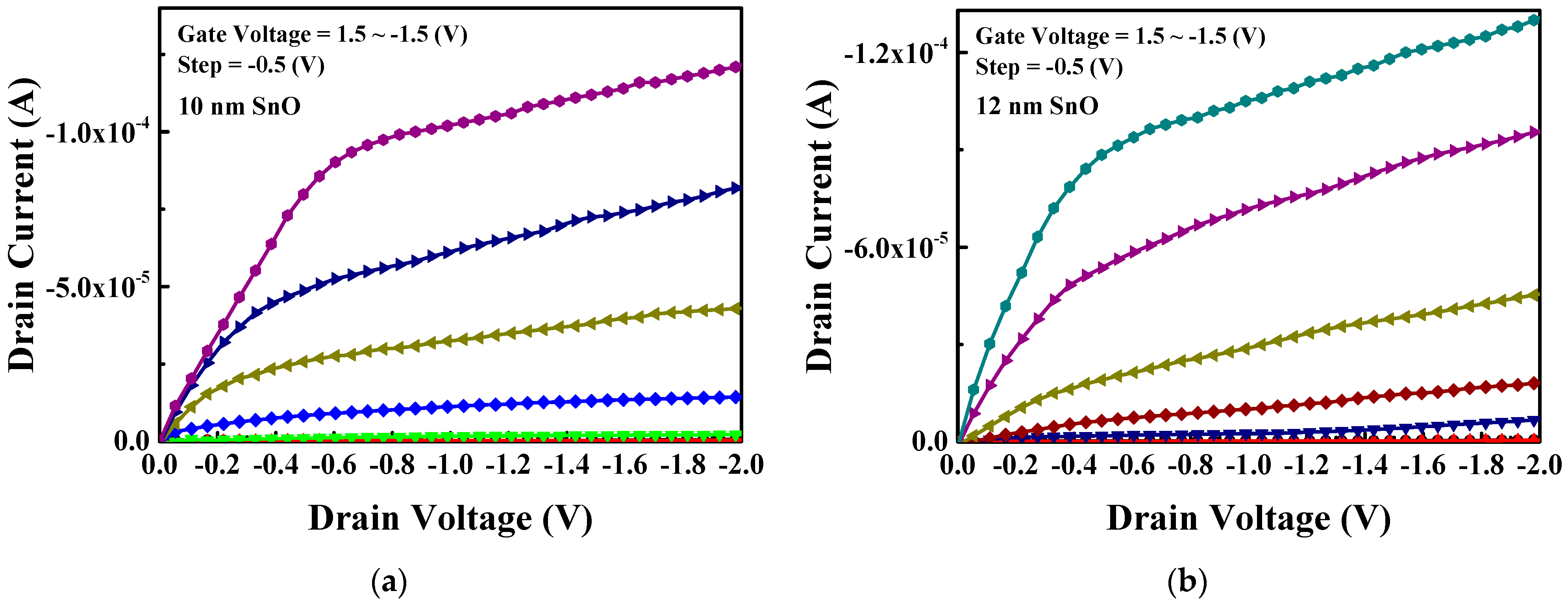

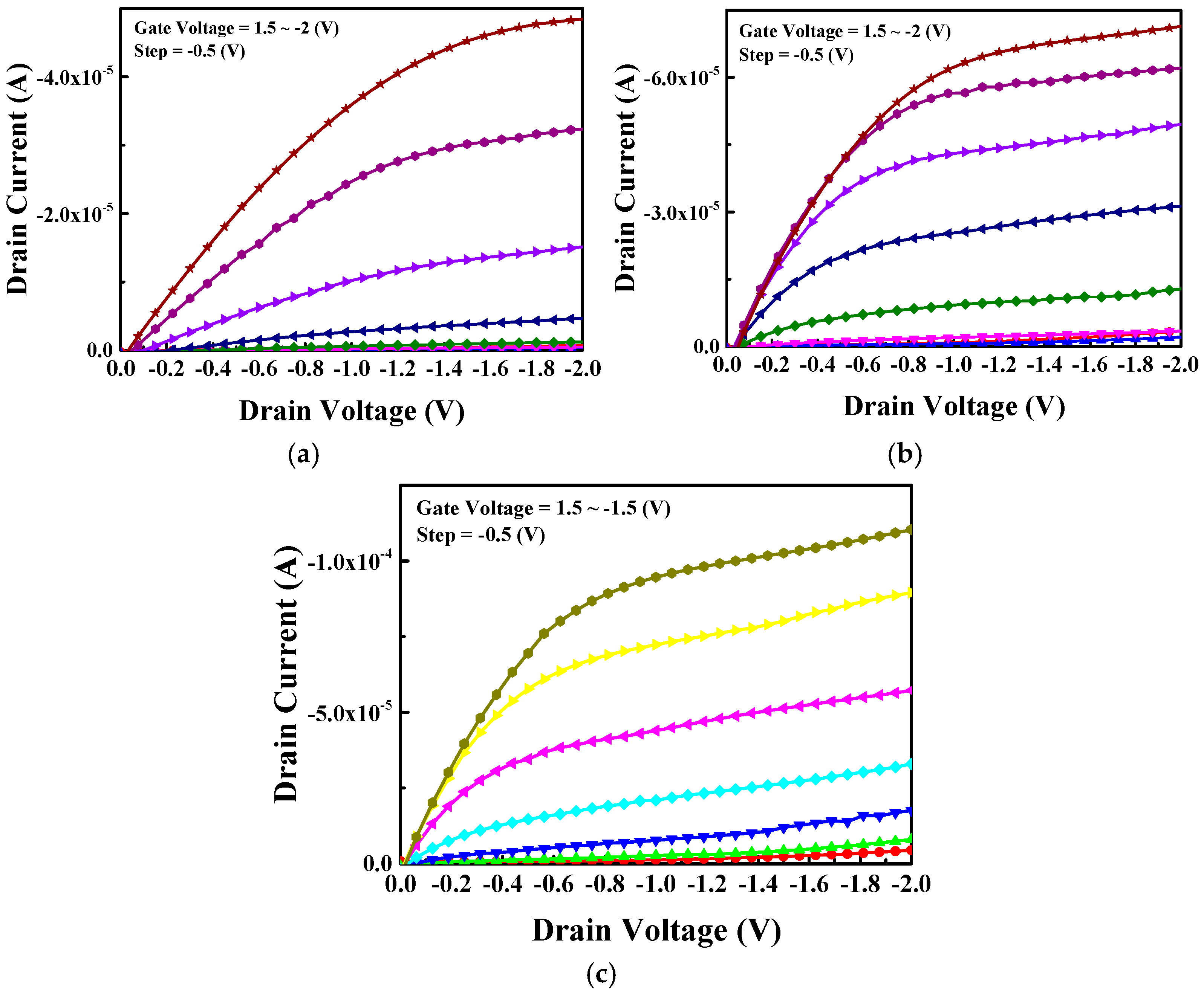

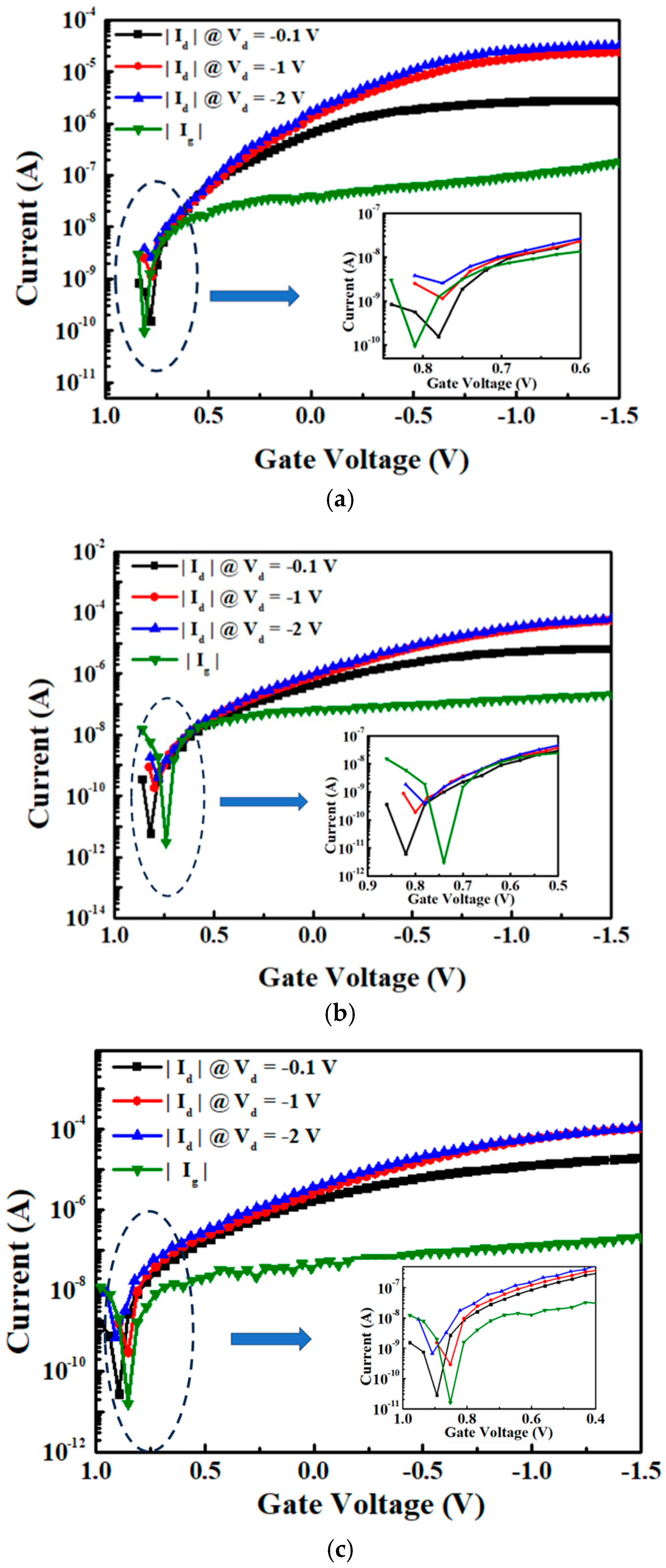

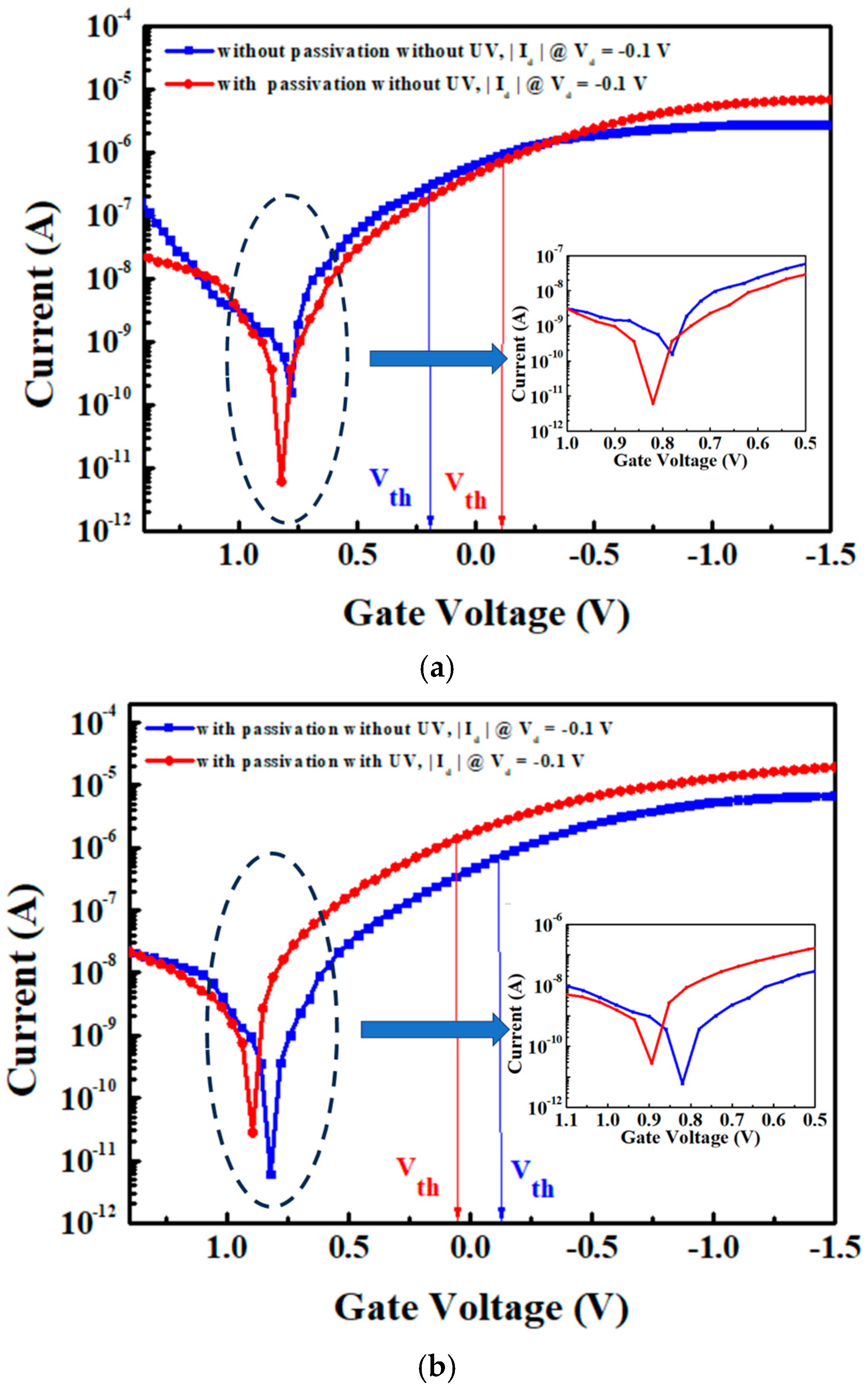

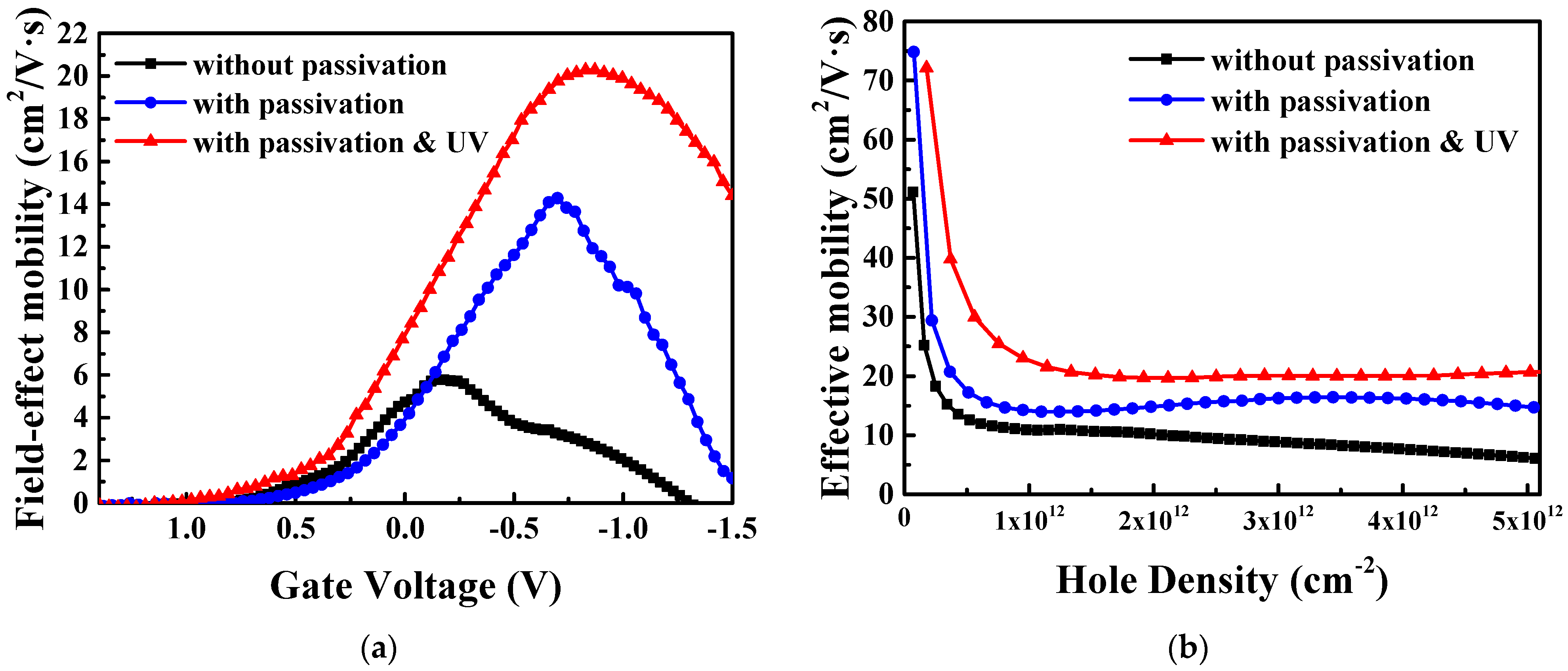

3. Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 2004, 432, 488–492. [Google Scholar] [CrossRef] [PubMed]

- Pooja, P.; Che, C.C.; Zeng, S.H.; Lee, Y.C.; Yen, T.J.; Chin, A. Outstanding high field-effect mobility of 299 cm2 V−1s−1 by nitrogen-doped SnO2 nanosheet thin-film transistor. Adv. Mater. Technol. 2023, 8, 2201521. [Google Scholar] [CrossRef]

- Li, S.L.; Wakabayashi, K.; Xu, Y.; Nakaharai, S.; Komatsu, K.; Li, W.W.; Lin, Y.F.; Aparecido-Ferreira, A.; Tsukagoshi, K. Thickness-dependent interfacial coulomb scattering in atomically thin field-effect transistors. Nano Lett. 2013, 13, 3546–3552. [Google Scholar] [CrossRef]

- Bai, Z.; He, D.; Fu, S.; Miao, Q.; Liu, S.; Huang, M.; Zhao, K.; Wang, Y.; Zhang, X. Recent progress in electron–phonon interaction of two-dimensional materials. Nano Select 2022, 3, 1112–1122. [Google Scholar] [CrossRef]

- Chang, H.; Huang, C.H.; Matsuzaki, K.; Nomura, K. Back-channel defect termination by sulfur for p-channel Cu2O thin-film transistors. ACS Appl. Mater. Interfaces 2020, 12, 51581–51588. [Google Scholar] [CrossRef]

- Hsu, S.M.; He, J.C.; Li, Y.S.; Su, D.Y.; Tsai, F.Y.; Cheng, I.C. Effect of mechanical strain on electrical performance of flexible P-type SnO thin-film transistors. IEEE Trans. Electron Devices 2019, 66, 5183–5186. [Google Scholar] [CrossRef]

- Chae, M.G.; Kim, J.; Jang, H.W.; Park, B.K.; Chung, T.M.; Kim, S.K.; Han, J.H. High field-effect mobility and on/off current ratio of p-type ALD SnO thin-film transistor. ACS Appl. Electron. Mater. 2023, 5, 1992–1999. [Google Scholar] [CrossRef]

- Ahmed, S.; Shahid, M.M.; Bakar, S.A.; Arshed, N.; Basirun, W.J.; Fouad, H. Fabrication and Characterization of SnO–Cu2O Mixed Metal Oxide Thin Films for Photoelectrochemical Applications. J. Nanosci. Nanotechnol. 2020, 20, 7705–7709. [Google Scholar] [CrossRef]

- Liu, A.; Liu, G.; Zhu, H.; Shin, B.; Fortunato, E.; Martins, R.; Shan, F. Hole mobility modulation of solution-processed nickel oxide thin-film transistor based on high-k dielectric. Appl. Phys. Lett. 2016, 108, 233506. [Google Scholar] [CrossRef]

- Caraveo-Frescas, J.A.; Nayak, P.K.; Al-Jawhari, H.A.; Granato, D.B.; Schwingenschlogl, U.; Alshareef, H.N. Record mobility in transparent p-type tin monoxide films and devices by phase engineering. ACS Nano 2013, 7, 5160–5167. [Google Scholar] [CrossRef]

- Caraveo-Frescas, J.A.; Alshareef, H.N. Transparent p-type SnO nanowires with unprecedented hole mobility among oxide semiconductors. Appl. Phys. Lett. 2013, 103, 222103. [Google Scholar] [CrossRef]

- Ogo, Y.; Hiramatsu, H.; Nomura, K.; Yanagi, H.; Kamiya, T.; Hirano, M.; Hosono, H. P-channel thin-film transistor using p-type oxide semiconductor, SnO. Appl. Phys. Lett. 2008, 93, 032113. [Google Scholar] [CrossRef]

- Shih, C.W.; Chin, A.; Lu, C.F.; Su, W.F. Remarkably high hole mobility metal-oxide thin-film transistors. Sci. Rep. 2018, 8, 889. [Google Scholar] [CrossRef]

- Hu, Y.; Schlom, D.; Datta, S.; Cho, K. Interlayer engineering of band gap and hole mobility in p-type oxide SnO. ACS Appl. Mater. Interfaces 2022, 14, 25670–25679. [Google Scholar] [CrossRef]

- Pan, X.; Fu, L. Oxidation and phase transitions of epitaxial tin oxide thin films on (1012) sapphire. J. Appl. Phys. 2001, 89, 6048–6055. [Google Scholar] [CrossRef]

- Shih, C.W.; Chin, A.; Lu, C.F.; Su, W.F. Low-temperature processed tin oxide transistor with ultraviolet irradiation. IEEE Electron Device Lett. 2019, 40, 909–912. [Google Scholar] [CrossRef]

- Zeng, S.H.; Pooja, P.; Wu, J.; Chin, A. Impact of UV annealing on the hole effective mobility in SnO pFET. Sci. Rep. 2024, 14, 26256. [Google Scholar] [CrossRef] [PubMed]

- Zhang, Y. Thermal oxidation fabrication of NiO film for optoelectronic devices. Appl. Surf. Sci. 2015, 344, 33–37. [Google Scholar] [CrossRef]

- Takagi, S.I.; Toriumi, A.; Iwase, M.; Tango, H. On the universality of inversion layer mobility in Si MOSFET’s: Part I-effects of substrate impurity concentration. IEEE Trans. Electron Devices 1994, 41, 2357–2362. [Google Scholar] [CrossRef]

- Huang, C.H.; Yu, D.S.; Chin, A.; Wu, C.H.; Chen, W.J.; Zhu, C.X.; Li, M.F.; Cho, B.J.; Kwong, D.L. Fully silicided NiSi and germanided NiGe dual gates on SiO2/Si and Al2O3/Ge-on-insulator MOSFETs. In Proceedings of the IEEE International Electron Devices Meeting 2003, Washington, DC, USA, 8–10 December 2003; pp. 319–322. [Google Scholar]

- Sun, S.; Plummer, J.D. Electron mobility in inversion and accumulation layers on thermally oxidized silicon surfaces. IEEE Trans. Electron Devices 1980, 27, 1497–1508. [Google Scholar] [CrossRef]

- Schroder, D.K. Semiconductor Material and Device Characterization; John Wiley & Sons: Hoboken, NJ, USA, 2015. [Google Scholar]

- Kobayashi, S.; Saitoh, M.; Uchida, K. More-than-universal mobility in double-gate SOI p-FETs with sub-10-nm body thickness -role of light-hole band and compatibility with uniaxial stress engineering. In Proceedings of the 2007 IEEE International Electron Devices Meeting, Washington, DC, USA, 10–12 December 2007; pp. 707–710. [Google Scholar]

- Cai, W.; Park, S.; Zhang, J.; Wilson, J.; Li, Y.; Xin, Q.; Majewski, L.; Song, A. One-volt IGZO thin-film transistors with ultra-thin, solution-processed AlxOy gate dielectric. IEEE Electron Device Lett. 2018, 39, 375–378. [Google Scholar] [CrossRef]

- Yakuphanoglu, F. Electrical conductivity, seebeck coefficient and optical properties of SnO2 film deposited on ITO by dip coating. J. Alloys Compd. 2009, 470, 55–59. [Google Scholar] [CrossRef]

- Jia, J.; Sugane, T.; Nakamura, S.I.; Shigesato, Y. P-type conduction mechanism in continuously varied non-stoichiometric SnOx thin films deposited by reactive sputtering with the impedance control. J. Appl. Phys. 2020, 127, 185703. [Google Scholar] [CrossRef]

- Kim, J.H.; Jeon, K.M.; Park, J.S.; Kang, Y.C. Excellent Li-ion storage performances of hierarchical SnO-SnO2 composite powders and SnO nanoplates prepared by one-pot spray pyrolysis. J. Power Sources 2017, 359, 363–370. [Google Scholar] [CrossRef]

- Tyckoson, D. CRC Handbook of Chemistry and Physics, 95th ed.; Chicago Booklist Publications: Boca Raton, FL, USA, 1998; p. 689. [Google Scholar]

- Yen, T.J.; Chin, A.; Gritsenko, V. Exceedingly high performance top-gate p-type SnO thin film transistor with a nanometer scale channel layer. Nanomaterials 2021, 11, 92. [Google Scholar] [CrossRef]

- Kim, H.M.; Choi, S.H.; Jeong, H.J.; Lee, J.H.; Kim, J.; Park, J.S. Highly dense and stable p-type thin-film transistor based on atomic layer deposition SnO fabricated by two-step crystallization. ACS Appl. Mater. Interfaces 2021, 13, 30818–33082. [Google Scholar] [CrossRef]

- Kim, H.M.; Choi, S.H.; Lee, H.U.; Cho, S.B.; Park, J.S. The significance of an in situ ALD Al2O3 stacked structure for p-type SnO TFT performance and monolithic all-ALD-channel CMOS inverter applications. Adv. Electron. Mater. 2023, 9, 2201202. [Google Scholar] [CrossRef]

- Lu, J.; Shen, M.; Feng, X.; Tan, T.; Guo, H.; Lin, L.; Zhou, F.; Li, Y. P-type oxide thin-film transistor with unprecedented hole field-effect mobility for an all-oxide CMOS CFET-like inverter suitable for monolithic 3D integration. Nano Lett. 2024, 24, 15260–15267. [Google Scholar] [CrossRef]

- Lee, J.H.; Kim, J.; Jin, M.; Na, H.J.; Lee, H.; Im, C.; Kim, Y.S. Cu2O p-type thin-film transistors with enhanced switching characteristics for CMOS logic circuit by controlling deposition condition and annealing in the N2 atmosphere. ACS Appl. Electron. Mater. 2023, 5, 1123–1130. [Google Scholar] [CrossRef]

- Lin, C.W.; Chung, W.C.; Zhang, Z.D.; Hsu, M.C. P-channel transparent thin-film transistor using physical-vapor-deposited NiO layer. Jpn. J. Appl. Phys. 2017, 57 (Suppl. S1), 01AE01. [Google Scholar] [CrossRef]

- Mashooq, K.; Jo, J.; Peterson, R.L. Effect of metal capping layer in achieving record high p-type SnO thin film transistor mobility. IEEE Trans. Electron Devices 2023, 71, 574–580. [Google Scholar] [CrossRef]

- Chen, Y.; Sun, Y.; Dai, X.; Zhang, B.; Ye, Z.; Wang, M.; Wu, H. Tunable electrical properties of NiO thin films and p-type thin-film transistors. Thin Solid Films 2015, 592, 195–199. [Google Scholar] [CrossRef]

- Shan, F.; Liu, A.; Zhu, H.; Kong, W.; Liu, J.; Shin, B.; Fortunato, E.; Martins, R.; Liu, G. High-mobility p-type NiOx thin-film transistors processed at low temperatures with Al2O3 high-k dielectric. J. Mater. Chem. C 2016, 4, 9438–9444. [Google Scholar] [CrossRef]

- Han, S.; Niang, K.M.; Rughoobur, G.; Flewitt, A.J. Effects of post-deposition vacuum annealing on film characteristics of p-type Cu2O and its impact on thin film transistor characteristics. Appl. Phys. Lett. 2016, 109, 173502. [Google Scholar] [CrossRef]

- Singh, V.; Sinha, J.; Avasthi, S. Two-step process using MOCVD and thermal oxidation to obtain pure-phase Cu2O thin films transistors. ACS Appl. Electron. Mater. 2021, 4, 367–374. [Google Scholar] [CrossRef]

- Kim, S.Y.; Ahn, C.H.; Lee, J.H.; Kwon, Y.H.; Hwang, S.; Lee, J.Y.; Cho, H.K. P-channel oxide thin film transistors using solution-processed copper oxide. ACS Appl. Mater. Interfaces 2013, 5, 2417–2421. [Google Scholar] [CrossRef]

- Bae, J.H.; Lee, J.H.; Park, S.P.; Jung, T.S.; Kim, H.J.; Kim, D.; Lee, S.W.; Park, K.S.; Yoon, S.; Kang, I.; et al. Gallium doping effects for improving switching performance of p-type copper (I) oxide thin-film transistors. ACS Appl. Mater. Interfaces 2020, 12, 38350–38356. [Google Scholar] [CrossRef]

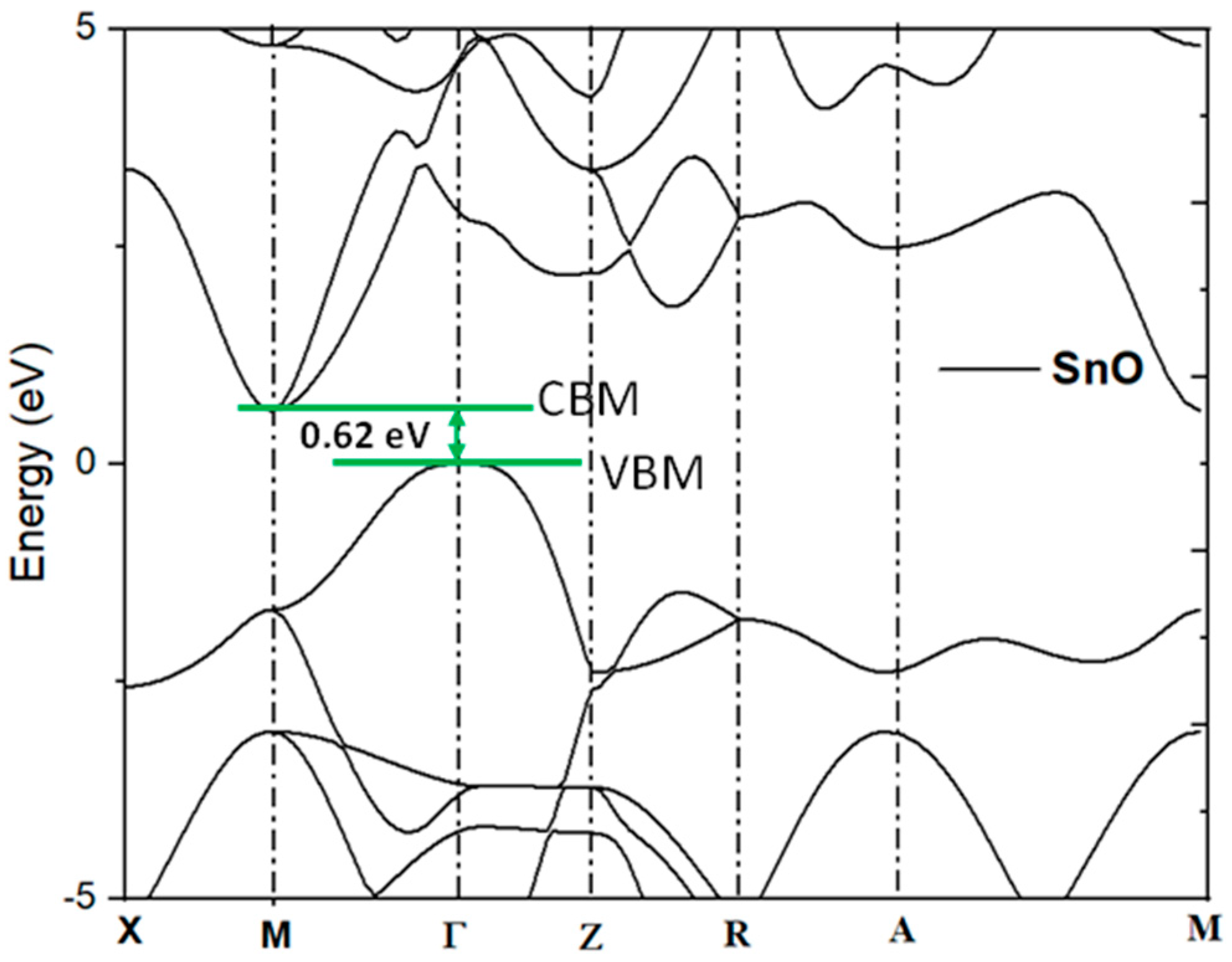

| P-Type | Eg | Hole Effective Mass (mh*) |

|---|---|---|

| SnO | 0.62 eV (Indirect) | 0.18 m0 |

| Cu2O [13] | 2.1 eV (Direct) | 0.65 m0 |

| NiO [18] | 3.6 eV (Indirect) | 0.45 m0 |

| Sample | Sn0 | Sn2+ | Sn4+ |

|---|---|---|---|

| SnO | 7.1% | 65.2% | 27.7% |

| SnO_UV | 6.3% | 62.4% | 31.3% |

| Passivated SnO | 9.3% | 68.9% | 21.8% |

| Passivated SnO_UV | 9.7% | 73.8% | 16.5% |

| Refs. | Channel | IOFF (A/μm) | ION/IOFF | SS (mV/dec) | µFE (cm2/V·s) | µeff (cm2/V·s) | Tech. and Anneal |

|---|---|---|---|---|---|---|---|

| This work | SnO | 5.6 × 10−14 | 6.9 × 106 | 231 | 20.3 | 20.7 | 200 °C RTA SiO2 passivation UV anneal |

| [12] | SnO | - | ~102 | - | 1.3 | - | 200 °C RTA |

| [10] | SnO | ~10−12 | 6 × 103 | 7630 | 6.75 | - | 180 °C 30 min |

| [11] | SnO | ~4 × 10−10 | >103 | 760 | 10.83 | - | 160 °C |

| [30] | SnO | - | 2.7 × 102 | 4600 | 6 | - | 300 °C 1 h |

| [31] | SnO | - | 6.54 × 105 | 150 | 1.14 | - | 300 °C 1 h |

| [32] | SnO | - | 2.5 × 103 | 240.9 | 38.7 | - | 175 °C 2 h |

| [17] | SnO | ~2.5 × 10−13 | 1.05 × 105 | 274 | 13.33 | 13.38 | 200 °C RTA UV anneal |

| [33] | Cu2O | - | 4.68 × 104 | 3910 | 1.11 | - | Thermal anneal 800 °C 1 h |

| [5] | Cu2O | - | 4.1 × 106 | 2350 | 1.38 | - | 100 °C 1 h |

| [34] | NiO | 2.75 × 10−7 | 3.61 × 104 | - | 1.09 | - | 200 °C 30 min |

| [9] | NiO | - | 105 | 250 | 4.4 | - | 250 °C |

| [35] | SnO | - | 4.2 × 103 | 6100 | 17.2 | 19.1 | 300 °C 1 h |

| [36] | NiO | - | 103 | 2600 | 1.07 | - | - |

| [37] | NiOx | - | 105 | 700 | 25 | - | UV treatment, 40 min and anneal 350 °C 1 h |

| [38] | Cu2O | - | 3.4 × 102 | 26,000 | 0.9 | - | 700 °C |

| [39] | Cu2O | - | - | - | 4.3 × 10−2 | - | 650 °C oxidation |

| [40] | Cu2O | - | 102 | - | 0.16 | - | 400 °C 30 min |

| [41] | Ga-doped Cu2O | - | 1.22 × 104 | 7720 | 0.74 | - | 800 °C |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, K.-C.; Wu, J.; Pooja, P.; Chin, A. SnO Nanosheet Transistor with Remarkably High Hole Effective Mobility and More than Six Orders of Magnitude On-Current/Off-Current. Nanomaterials 2025, 15, 640. https://doi.org/10.3390/nano15090640

Chen K-C, Wu J, Pooja P, Chin A. SnO Nanosheet Transistor with Remarkably High Hole Effective Mobility and More than Six Orders of Magnitude On-Current/Off-Current. Nanomaterials. 2025; 15(9):640. https://doi.org/10.3390/nano15090640

Chicago/Turabian StyleChen, Kuan-Chieh, Jiancheng Wu, Pheiroijam Pooja, and Albert Chin. 2025. "SnO Nanosheet Transistor with Remarkably High Hole Effective Mobility and More than Six Orders of Magnitude On-Current/Off-Current" Nanomaterials 15, no. 9: 640. https://doi.org/10.3390/nano15090640

APA StyleChen, K.-C., Wu, J., Pooja, P., & Chin, A. (2025). SnO Nanosheet Transistor with Remarkably High Hole Effective Mobility and More than Six Orders of Magnitude On-Current/Off-Current. Nanomaterials, 15(9), 640. https://doi.org/10.3390/nano15090640