Experimental Investigation of Thermal Annealing and Ferroelectric Capacitor Area Effects for Hafnium-Zirconium Oxide Devices

Abstract

:1. Introduction

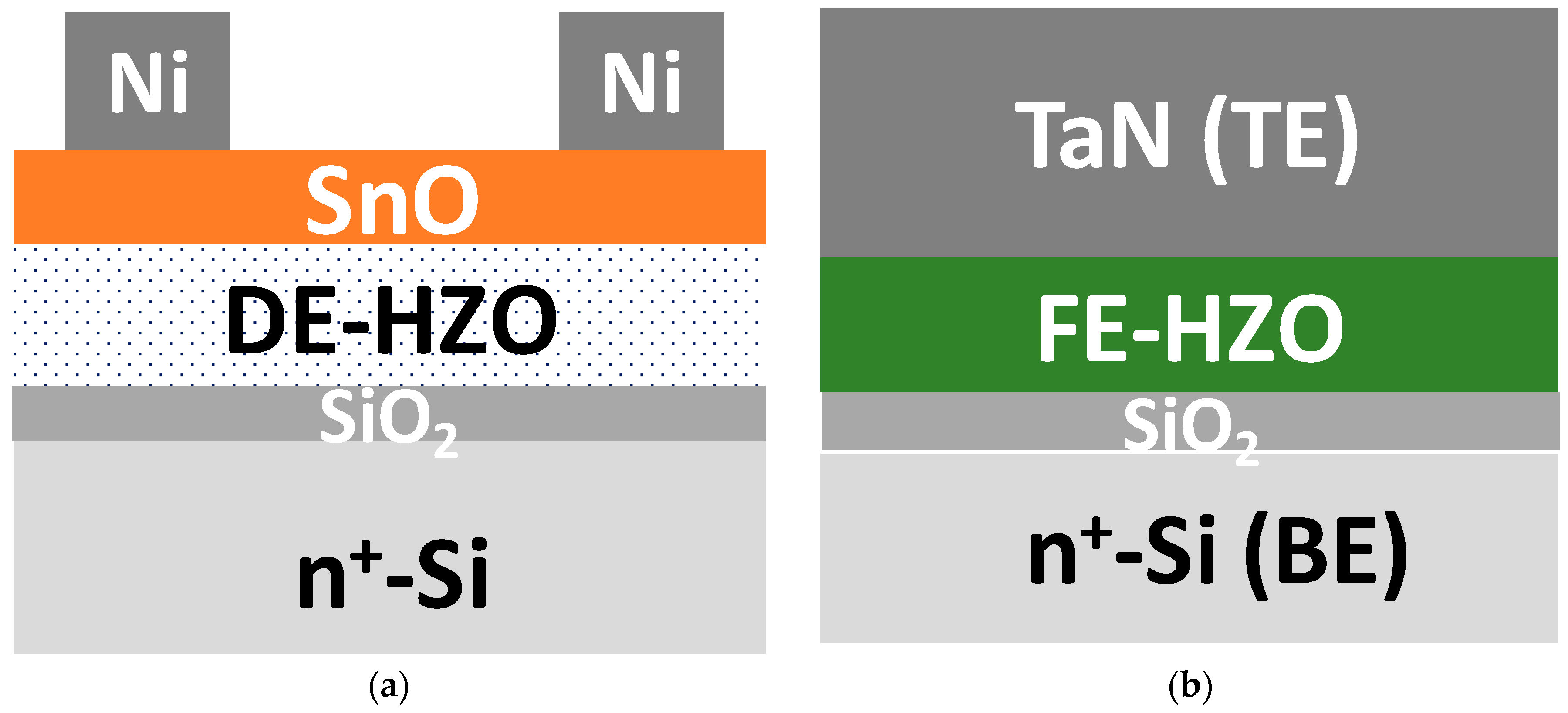

2. Materials and Methods

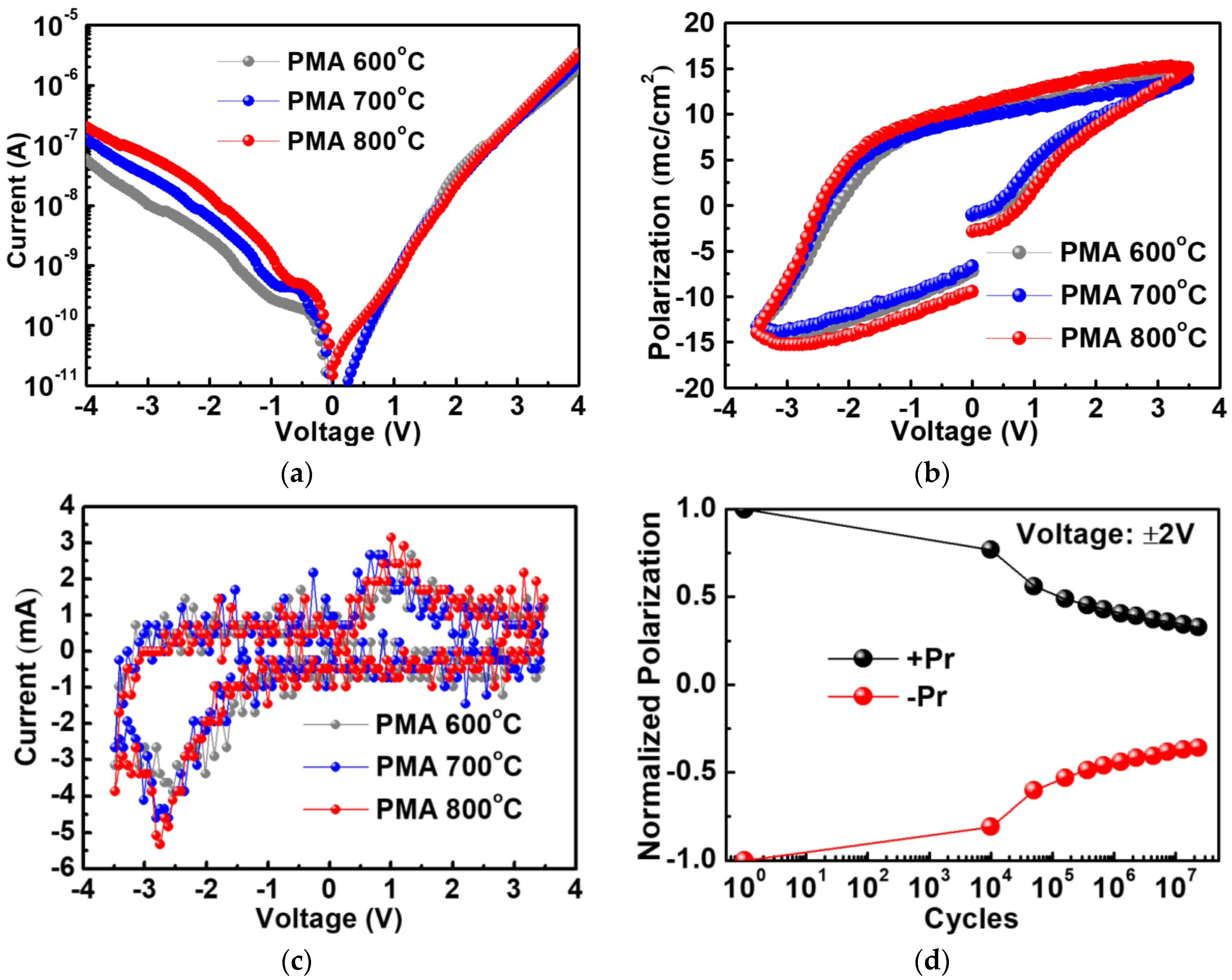

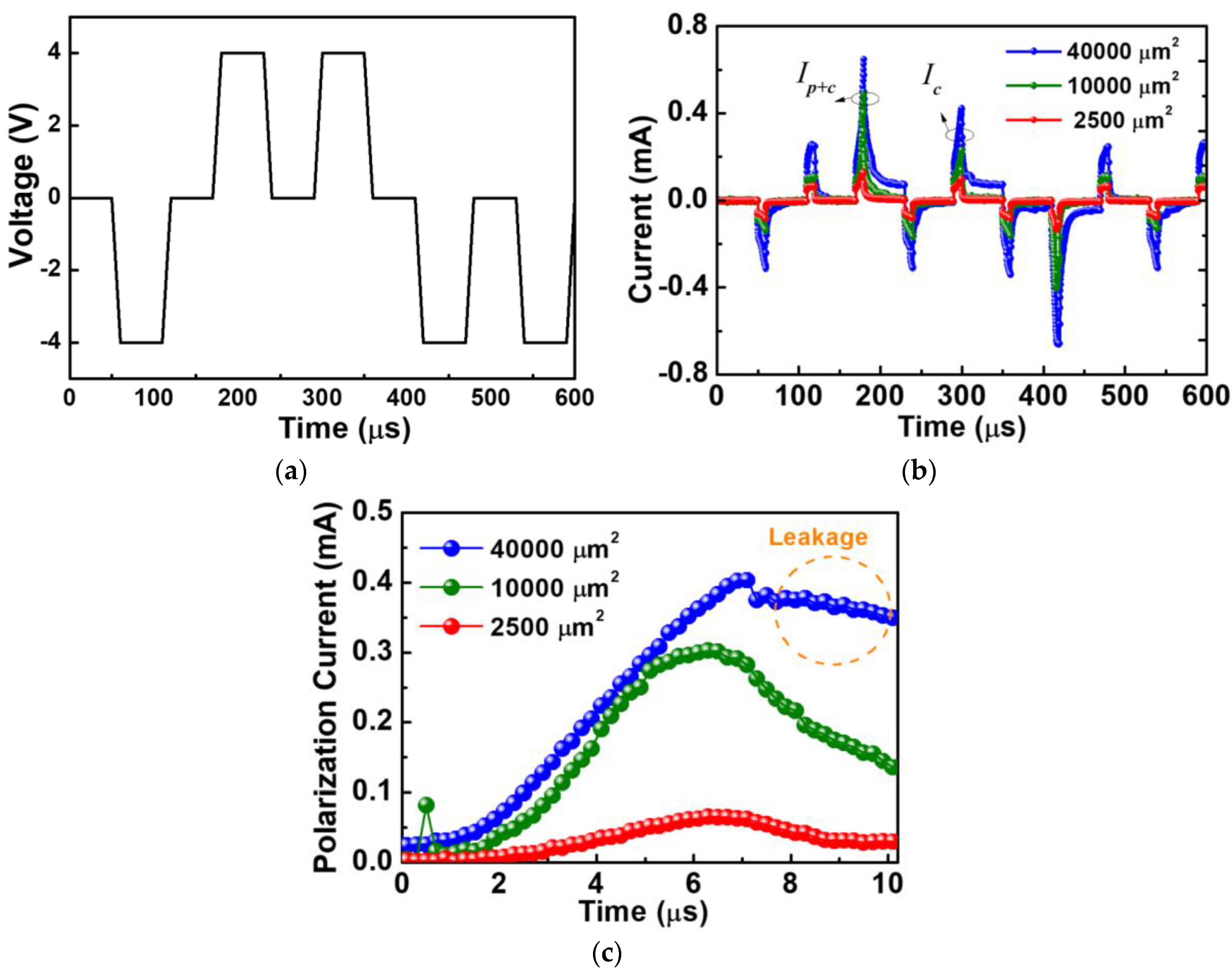

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Yurchuk, E.; Muller, J.; Muller, S.; Paul, J.; Pesic, M.; van Bentum, R.; Schroeder, U.; Mikolajick, T. Charge-trapping phenomena in HfO2-based FeFET-type nonvolatile memories. IEEE Trans. Electron Dev. 2016, 63, 3501–3507. [Google Scholar] [CrossRef]

- Müller, J.; Yurchuk, E.; Schlosser, T.; Paul, J.; Hoffmann, R.; Muller, S.; Martin, D.; Slesazeck, S.; Polakowski, P.; Sundqvist, J.; et al. Ferroelectricity in HfO2 enables nonvolatile data storage in 28 nm HKMG. In Proceedings of the 2012 Symposium on VLSI Technology (VLSIT), Honolulu, HI, USA, 12–14 June 2010; pp. 25–26. [Google Scholar]

- Trentzsch, M.; Flachowsky, S.; Richter, R.; Paul, J.; Reimer, B.; Utess, D.; Jansen, S.; Mulaosmanovic, H.; Müller, J.; Slesazeck, S.; et al. A 28 nm HKMG super low power embedded NVM technology based on ferroelectric FETs. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 11.5.1–11.5.4. [Google Scholar]

- Chen, K.T.; Chou, Y.C.; Siang, G.Y.; Chen, H.Y.; Lo, C.; Liao, C.Y.; Chang, S.T.; Lee, M.H. Evaluation of sweep modes for switch response on ferroelectric negative-capacitance FETs. Appl. Phys. Expr. 2019, 12, 071003. [Google Scholar] [CrossRef]

- Fan, C.C.; Cheng, C.H.; Chen, Y.R.; Liu, C.; Chang, C.Y. Energy-efficient HfAlOx NCFET: Using gate strain and defect passivation to realize nearly hysteresis- free sub-25mV/dec switch with ultralow leakage. In Proceedings of the International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 561–564. [Google Scholar]

- Mueller, S.; Mueller, J.; Singh, A.; Riedel, S.; Sundqvist, J.; Schröder, U.; Mikolajick, T. Incipient ferroelectricity in Al-doped HfO2 thin films. Adv. Funct. Mater. 2012, 22, 2412–2417. [Google Scholar] [CrossRef]

- Cheng, C.H.; Chin, A. Low-leakage-current DRAM-like memory using a one-transistor ferroelectric MOSFET with a Hf-based gate dielectric. IEEE Electron Device Lett. 2014, 35, 138–140. [Google Scholar] [CrossRef]

- Müller, J.; Böscke, T.S.; Bräuhaus, D.; Schröder, U.; Böttger, U.; Sundqvist, J.; Kücher, P.; Mikolajick, T.; Frey, L. Ferroelectric Zr0.5Hf0.5O2 thin films for nonvolatile memory applications. J. Appl. Phys. 2011, 99, 112901. [Google Scholar]

- Chiu, Y.C.; Cheng, C.H.; Chang, C.Y.; Lee, M.H.; Hsu, H.H.; Yen, S.S. Low power 1T DRAM/NVM versatile memory featuring steep sub-60-mV/decade operation, fast 20-ns speed, and robust 85 °C-extrapolated 1016 endurance. In Proceedings of the 2015 Symposium on VLSI Technology (VLSI Technology), Kyoto, Japan, 16–18 June 2015; pp. T184–T185. [Google Scholar]

- Kim, H.J.; Park, M.H.; Kim, Y.K.; Lee, Y.H.; Jeon, W.; Gwon, T.; Moon, T.; Kim, K.D.; Hwang, C.S. Grain size engineering for ferroelectric Hf0.5Zr0.5O2 films by an insertion of Al2O3 interlayer. Appl. Phys. Lett. 2014, 105, 192903. [Google Scholar] [CrossRef]

- Chiu, Y.C.; Cheng, C.H.; Chang, C.Y.; Tang, Y.T.; Chen, M.C. One-transistor ferroelectric versatile memory: Strained-gate engineering for realizing energy-efficient switching and fast negative-capacitance operation. In Proceedings of the 2016 Symposium on VLSI Technology (VLSIT), Honolulu, HI, USA, 14–16 June 2016; pp. T150–T151. [Google Scholar]

- Materlik, R.; Künneth, C.; Kersch, A. The origin of ferroelectricity in Hf1−xZrxO2: A computational investigation and a surface energy model. J. Appl. Phys. 2015, 117, 134109. [Google Scholar] [CrossRef] [Green Version]

- Chiu, Y.C.; Cheng, C.Y.; Yen, S.S.; Fan, C.C.; Hsu, H.H. On the variability of threshold voltage window in gate-injection versatile memories with Sub-60mV/dec subthreshold swing and 1012-cycling endurance. In Proceedings of the 2016 IEEE International Reliability Physics Symposium (IRPS), Pasadena, CA, USA, 17–21 April 2016; pp. MY.7.1–MY.7.5. [Google Scholar]

- Cheng, C.H.; Lin, M.H.; Chen, H.Y.; Fan, C.C.; Liou, C.; Hsu, H.H.; Chang, C.Y. Impact of zirconium doping on steep subthreshold switching of negative capacitance hafnium oxide based transistors. Phys. Status Solidi RRL. 2019, 13, 1800573. [Google Scholar] [CrossRef]

- Chiu, Y.C.; Cheng, C.H.; Liou, G.L.; Chang, C.Y. Energy-efficient versatile memories with ferroelectric negative capacitance by gate-strain enhancement. IEEE Trans. Electron Devices 2017, 64, 3498–3501. [Google Scholar] [CrossRef]

- Cheng, C.H.; Fan, C.C.; Tu, C.Y.; Hsu, H.H.; Chang, C.Y. Implementation of dopant-free hafnium oxide negative capacitance field-effect transistor. IEEE Trans. Electron Dev. 2018, 66, 825–828. [Google Scholar] [CrossRef]

- Fan, C.C.; Cheng, C.H.; Tu, C.Y.; Liu, C.; Chen, W.H.; Chang, T.J.; Chang, C.Y. Achieving High-Scalability Negative Capacitance FETs with Uniform Sub-35 mV/dec Switch Using Dopant-Free Hafnium Oxide and Gate Strain. In Proceedings of the 2018 Symposium on VLSI Technology (VLSIT), Honolulu, HI, USA, 18–22 June 2018; pp. T139–T140. [Google Scholar]

- Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 2004, 432, 488–492. [Google Scholar] [CrossRef] [PubMed]

- Fortunato, E.; Barquinha, P.; Martins, R. Oxide semiconductor thin-film transistors: A review of recent advances. Adv. Mater. 2012, 24, 2945–2986. [Google Scholar] [CrossRef] [PubMed]

- Noh, S.; Choi, W.; Oh, M.S.; Hwang, D.K.; Lee, K.; Im, S.; Jang, S.; Kim, E. ZnO-based nonvolatile memory thin-film transistors with polymer dielectric/ferroelectric double gate insulators. Appl. Phys. Lett. 2007, 90, 253504. [Google Scholar] [CrossRef]

- Khan, M.A.; Caraveo-Frescas, J.A.; Alshareef, H.N. Hybrid dual gate ferroelectric memory for multilevel information storage. Org. Electron. 2015, 16, 9–17. [Google Scholar] [CrossRef]

- Gupta, D.; Anand, M.; Ryu, S.W.; Choi, Y.K.; Yoo, S. Nonvolatile memory based on sol-gel ZnO thin-film transistors with Ag nanoparticles embedded in the ZnO/gate insulator interface. Appl. Phys. Lett. 2008, 93, 224106. [Google Scholar] [CrossRef]

- Chen, P.C.; Chiu, Y.C.; Liou, G.L.; Zheng, Z.W.; Cheng, C.H.; Wu, Y.H. Performance enhancements in p-type Al-doped tin-oxide thin film transistors by using fluorine plasma treatment. IEEE Electron Device Lett. 2017, 38, 210–212. [Google Scholar] [CrossRef]

- Chen, P.C.; Chiu, Y.C.; Zheng, Z.W.; Cheng, C.H.; Wu, Y.H. Influence of plasma fluorination on p-type channel tin-oxide thin film transistors. J. Alloy. Compd. 2017, 707, 162–166. [Google Scholar] [CrossRef]

- Chiu, Y.C.; Chen, P.C.; Chang, S.L.; Zheng, Z.W.; Cheng, C.H.; Liou, G.L.; Kao, H.L.; Wu, Y.H.; Chang, C.Y. Channel modification engineering by plasma processing in tin-oxide thin film transistor: Experimental results and first-principles calculation. Ecs J. Solid State Sci. Technol. 2017, 6, Q53–Q57. [Google Scholar] [CrossRef]

- Chiu, Y.C.; Cheng, C.H.; Chang, C.Y.; Tang, Y.T.; Chen, M.C. Investigation of strain-induced phase transformation in ferroelectric transistor using metal-nitride gate electrode. Phys. Status Solidi Rrl 2017, 11, 1600368. [Google Scholar] [CrossRef]

- Cheng, C.H.; Fan, C.C.; Liu, C.; Hsu, H.H.; Cheng, H.H.; Hsu, C.C.; Wang, S.A.; Chang, C.Y. Investigation of Gate-Stress Engineering in Negative Capacitance FETs Using Ferroelectric Hafnium Aluminum Oxides. IEEE Trans. Electron Dev. 2019, 66, 1082–1086. [Google Scholar] [CrossRef]

- Rajshekar, K.; Hsu, H.H.; Kumar, K.U.M.; Sathyanarayanan, P.; Velmurugan, V.; Cheng, C.H. and Kannadassan, D. Effect of plasma fluorination in p-type SnO TFTs: Experiments, modeling, and simulation. IEEE Trans. Electron Dev. 2019, 66, 1314–1321. [Google Scholar] [CrossRef]

- Tian, X.; Shibayama, S.; Nishimura, T.; Yajima, T.; Migita, S.; Toriumi, A. Evolution of ferroelectric HfO2 in ultrathin region down to 3 nm. Appl. Phys. Lett. 2018, 112, 102902. [Google Scholar]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hsu, H.-H.; Liu, H.-M.; Lee, S. Experimental Investigation of Thermal Annealing and Ferroelectric Capacitor Area Effects for Hafnium-Zirconium Oxide Devices. Coatings 2020, 10, 733. https://doi.org/10.3390/coatings10080733

Hsu H-H, Liu H-M, Lee S. Experimental Investigation of Thermal Annealing and Ferroelectric Capacitor Area Effects for Hafnium-Zirconium Oxide Devices. Coatings. 2020; 10(8):733. https://doi.org/10.3390/coatings10080733

Chicago/Turabian StyleHsu, Hsiao-Hsuan, Hsiu-Ming Liu, and Sheng Lee. 2020. "Experimental Investigation of Thermal Annealing and Ferroelectric Capacitor Area Effects for Hafnium-Zirconium Oxide Devices" Coatings 10, no. 8: 733. https://doi.org/10.3390/coatings10080733