LTPS TFTs with an Amorphous Silicon Buffer Layer and Source/Drain Extension

Abstract

:1. Introduction

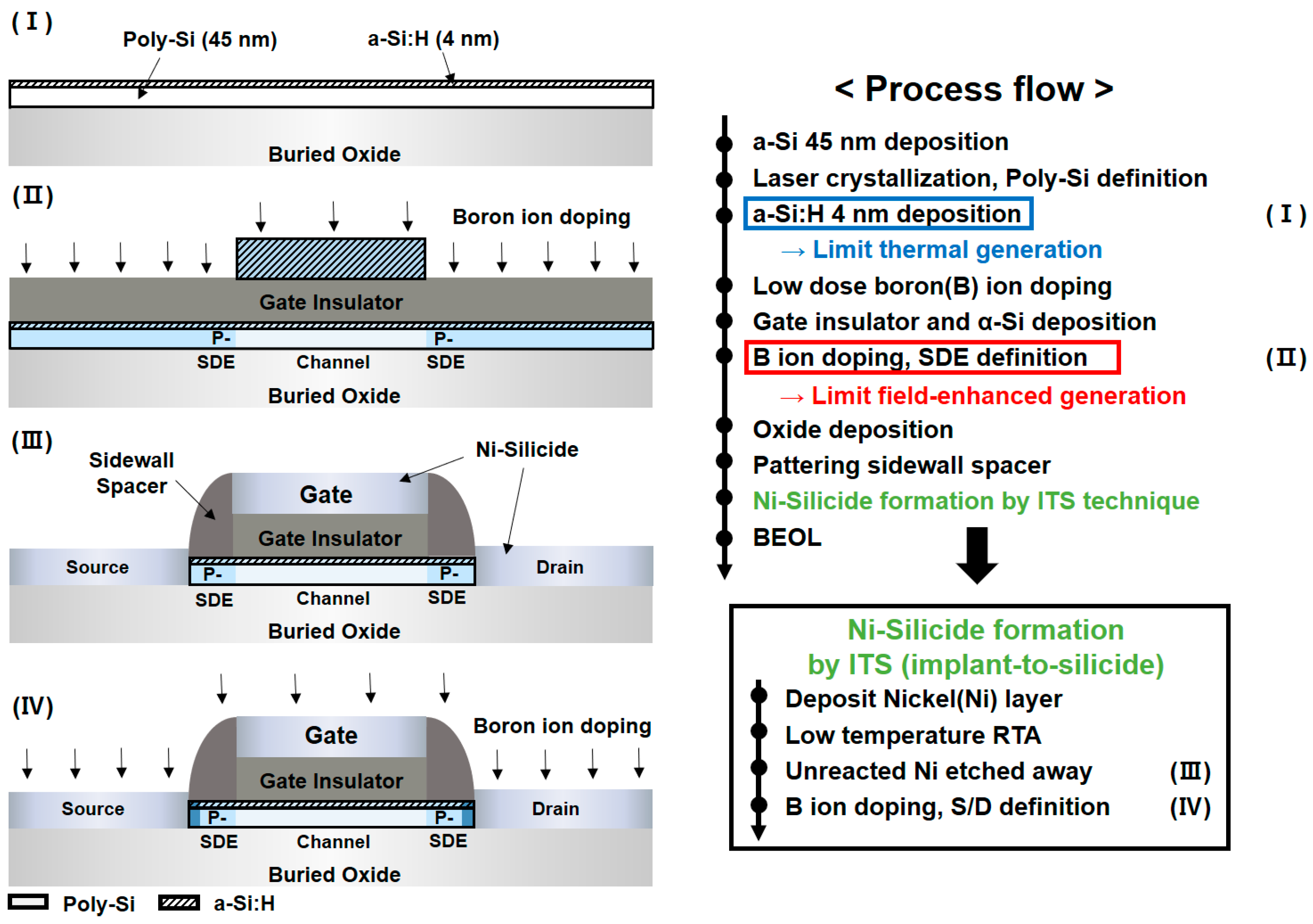

2. Proposed Process Flow

3. Device Structure and Simulation Methodology

4. Simulation Results and Discussion

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Brotherton, S.D. Polycrystalline silicon thin film transistor. Semicond. Sci. Technol. 1995, 10, 721–738. [Google Scholar] [CrossRef]

- Serikawa, T.; Shirai, T.; Okamoto, A.; Suyama, S. Low Temperature Fabrication of High-Mobility Poly-Si TFT’s for Large-Area LCD’s. IEEE Trans. Electron Devices 1989, 36, 1929–1933. [Google Scholar] [CrossRef]

- Lih, J.J.; Sung, C.F.; Li, C.H.; Hsiao, T.H.; Lee, H.H. Comparison of a-Si and poly-Si for AMOLED displays. J. Soc. Inf. Disp. 2012, 12, 367–371. [Google Scholar] [CrossRef]

- Stewart, M.; Howell, R.S.; Pires, L.; Hatalis, M.K. Polysilicon TFT Technology for Active Matrix OLED Displays. IEEE Trans. Electron Devices 2001, 48, 845–851. [Google Scholar] [CrossRef]

- Wang, H.; Jiang, L.L.; Wang, N.; Yu, H.Y.; Lin, X.P. A Charge Storage Based Enhancement Mode AlGaN/GaN High Electron Mobility Transistor. Mater. Sci. Forum 2018, 913, 870–875. [Google Scholar] [CrossRef]

- Megherbi, M.L.; Pezzimenti, F.; Dehimi, L.; Saadoune, M.A.; Della Corte, F.G. Analysis of trapping effects on the forward current-voltage characteristics of al-implanted 4H-SiC p-i-n Diodes. IEEE Trans. Electron Devices 2018, 65, 3371–3378. [Google Scholar] [CrossRef]

- Pezzimenti, F. Modeling of the steady state and switching characteristics of a normally-off 4H-SiC trench bipolar-mode FET. IEEE Trans. Electron Devices 2013, 60, 1404–1411. [Google Scholar] [CrossRef]

- Anvarifard, M.K.; Orouji, A.A. Proper Electrostatic Modulation of Electric Field in a Reliable Nano-SOI with a Developed Channel. IEEE Trans. Electron Devices 2018, 65, 1653–1657. [Google Scholar] [CrossRef]

- Shirai, S.; Serikawa, T. Electrical Analysis of High-Mobility Poly-Si TFT’s Made from Laser-Irradiated Sputtered Si Films. IEEE Trans. Electron Devices 1922, 39, 450–452. [Google Scholar] [CrossRef]

- Fossum, J.G.; Ortiz-Conde, A.; Shichijo, H.; Banerjee, S.K. Anomalous Leakage Current in LPCVD Polysilicon MOSFET’s. IEEE Trans. Electron Devices 1985, 32, 1878–1884. [Google Scholar] [CrossRef]

- Brotherton, S.D.; Ayres, J.R.; Trainor, M.J. Control and analysis of leakage currents in poly-Si thin-film transistors. J. Appl. Phys. 1996, 79, 895. [Google Scholar] [CrossRef]

- Walker, P.M.; Uno, S.; Mizuta, H. Simulation Study of the Dependence of Submicron Polysilicon Thin-Film Transistor Output Characteristics on Grain Boundary Position. Jpn. J. Appl. Phys. 2005, 44, 8322–8328. [Google Scholar] [CrossRef] [Green Version]

- Park, J.; Jang, K.S.; Shin, D.G.; Shin, M.; Yi, J.S. Gate-induced drain leakage current characteristics of p-type polycrystalline silicon thin film transistors aged by off-state stress. Solid-State Electron. 2018, 148, 20–26. [Google Scholar] [CrossRef]

- Kim, C.H.; Sohn, K.S. Temperature dependent leakage currents in polycrystalline silicon thin film transistors. J. Appl. Phys. 1997, 81, 8084–8090. [Google Scholar] [CrossRef]

- Vincent, C.; Chantre, A.; Bois, D. Electric field effect on the thermal emission of traps in semiconductor junctions. J. Appl. Phys. 1979, 50, 5484–5487. [Google Scholar] [CrossRef]

- Martin, P.A.; Streetman, B.G.; Hess, K. Electric field enhanced emission from non-Coulombic traps in semiconductors. J. Appl. Phys. 1981, 52, 7409–7415. [Google Scholar] [CrossRef]

- Pecora, A.; Schillizzi, M.; Tallarida, G.; Fortunato, G.; Reita, C.; Migliorato, P. Off-Current in Polycrystalline Silicon Thin Film Transistors: An Analysis of the Thermally Generated Component. Solid-State Electron. 1995, 38, 845–850. [Google Scholar] [CrossRef]

- Kimura, M.; Taya, J.; Nakashima, A. Temperature Dependences of I-V Characteristics of SD and LDD Poly-Si TFTs. IEEE Electron Device Lett. 2012, 33, 682–684. [Google Scholar] [CrossRef]

- Kimura, M. Behavior Analysis of an LDD Poly-Si TFT Using 2-D Device Simulation. IEEE Trans. Electron Devices 2012, 59, 705–709. [Google Scholar] [CrossRef]

- Kimura, M.; Nakashima, A. Mechanism Analysis of Current-Voltage Characteristic in a Lightly Doped Drain Polycrystalline Silicon Thin-Film Transistor Using Activation Energy. Jpn. J. Appl. Phys. 2012, 51, 03CA05. [Google Scholar] [CrossRef]

- Nakashima, A.; Kimura, M. Mechanism Analysis of Off-Leakage Current in an LDD Poly-Si TFT Using Activation Energy. IEEE Electron Device Lett. 2011, 32, 764–766. [Google Scholar] [CrossRef]

- Orouji, A.A.; Kumar, M.J. Leakage Current Reduction Techniques in Poly-Si TFTs for Active Matrix Liquid Crystal Displays: A Comprehensive Study. IEEE Trans. Device Mater. Reliab. 2006, 6, 315–325. [Google Scholar] [CrossRef]

- Lin, J.T.; Huang, K.D. A High-Performance Polysilicon Thin-Film Transistor Built on a trenched Body. IEEE Trans. Electron Devices 2008, 55, 2417–2422. [Google Scholar]

- Seki, S.; Kogure, O.; Tsujiyama, B. Laser-Recrystallized Polycrystalline-Silicon Thin Film Transistors with Low Leakage Current and High Switching Ratio. IEEE Electron Device Lett. 1987, 8, 425–427. [Google Scholar] [CrossRef]

- Kim, K.W.; Cho, K.S.; Jang, J. A Polycrystalline Silicon Thin-Film Transistor with a Thin Amorphous Buffer. IEEE Electron Device Lett. 1999, 20, 560–562. [Google Scholar]

- Jang, K.; Kim, Y.; Phong, P.D.; Lee, Y.; Park, J.; Yi, J. Improvement of Electrical Performance in P-Channel LTPS Thin-film Transistor with a-Si:H Surface Passivation. Materials 2019, 12, 161. [Google Scholar] [CrossRef] [Green Version]

- Kim, K.W.; Cho, K.S.; Jang, J. Performance improvement of polycrystalline thin-film transistor by adopting a very thin amorphous silicon buffer. J. Non-Cryst. Solids 2000, 266–269, 1265–1269. [Google Scholar] [CrossRef]

- Park, J.-H.; Kim, O. A novel self-aligned poly-Si TFT with field-induced drain formed by the damascene process. IEEE Electron Device Lett. 2005, 26, 249–251. [Google Scholar] [CrossRef]

- Ahn, J.A.; Kim, O. Influence of Field-Induced Drain on the Characteristics of Poly-Si Thin-Film Transistor using a Self-Aligned Double Spacer Process. Jpn. J. Appl. Phys. 2004, 43, 897–900. [Google Scholar] [CrossRef]

- Chien, F.T.; Hsueh, K.P.; Hong, Z.J.; Lin, K.T.; Tsai, Y.T.; Chiu, H.C. A Low Impact Ionization Rate Poly-Si TFT with a Current and Electric Field Split Design. Coatings 2019, 9, 514. [Google Scholar] [CrossRef] [Green Version]

- Lin, C.P.; Xiao, Y.H.; Tsui, B.Y. High-Performance Poly-Si TFTs Fabricated by Implant-to-Silicide Technique. IEEE Electron Device Lett. 2005, 26, 185–187. [Google Scholar] [CrossRef]

- Lin, C.P.; Hsiao, Y.H.; Tsui, B.Y. Process and Characteristics of Fully Silicided Source/Drain (FSD) Thin-Film Transistors. IEEE Trans. Electron Devices 2006, 53, 3086–3094. [Google Scholar] [CrossRef]

- Synopsys Inc. Sentaurus Device User Guide; Synopsys Inc.: Mountain View, CA, USA, 2018. [Google Scholar]

- Kim, S.; Kwon, D.W.; Park, E.; Lee, J.; Lee, R.; Lee, J.H. Investigation of silicide-induced-dopant-activation for steep tunnel junction in tunnel field effect transistor (TFET). Solid-State Electron. 2018, 140, 41–45. [Google Scholar] [CrossRef]

- Jackson, W.B.; Johnson, N.M.; Biegelsen, D.K. Density of gap states of silicon grain boundaries determined by optical absorption. J. Appl. Phys. 1983, 43, 195–197. [Google Scholar] [CrossRef]

- Valdinoci, M.; Colalongo, L.; Baccarani, G.; Pecora, A.; Policicchio, I.; Fortunato, G.; Legagneux, P.; Reita, C.; Pribat, D. Analysis and electrical characteristics of polycrystalline silicon thin-film transistors under static and dynamic conditions. Solid-State Electron. 1997, 41, 1363–1369. [Google Scholar] [CrossRef]

- Shur, M.; Hack, M.; Shaw, G. A new analytic model for amorphous silicon thin-film transistors. J. Appl. Phys. 1989, 66, 3371–3380. [Google Scholar] [CrossRef]

| Material and Device Properties | Symbol | Value | Unit |

|---|---|---|---|

| Thickness of polycrystalline silicon | tact | 45 | nm |

| Thickness of amorphous silicon | tbuf | 4 | nm |

| Bandgap of Poly-Si/a-Si | Eg | 1.1/1.8 | eV |

| Thickness of gate insulator | tGI | 120 | nm |

| Channel Width/Length | W/L | 3.5/4 | µm |

| Length of source/drain extension | LSDE | 0.75 | µm |

| Source/Drain doping density | NSD | Boron, 1.64 × 1019 | cm−3 |

| SDE doping density | NSDE | Boron, 4.6 × 1017 | cm−3 |

| Channel doping density | NCh | Boron, 2.3 × 1016 | cm−3 |

| Definition | Symbol | Poly-Si | a-Si | Unit |

|---|---|---|---|---|

| Density of donor-like tail states | NTD | 1 × 1020 | 2 × 1021 | cm−3 |

| Density of acceptor-like tail states | NTA | 1 × 1020 | 2 × 1021 | |

| Density of donor-like Gaussian states | NGD | 4.5 × 1014 | 5 × 1018 | |

| Density of acceptor-like Gaussian states | NGA | 1 × 1015 | 5 × 1018 | |

| Slop of donor-like tail states | WTD | 0.015 | 0.021 | eV−1 |

| Slop of acceptor -like tail states | WTA | 0.012 | 0.021 | |

| Width of donor-like Gaussian states | WGD | 0.15 | 0.086 | |

| Width of acceptor-like Gaussian states | WGA | 0.1 | 0.086 | |

| Peak energy position of donor-like Gaussian states | EGD | 0.6 | 0.1 | eV |

| Peak energy position of acceptor-like Gaussian states | EGA | 0.2 | 1.7 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, H.I.; Sung, J.M.; Cho, H.U.; Kim, Y.J.; Park, Y.G.; Choi, W.Y. LTPS TFTs with an Amorphous Silicon Buffer Layer and Source/Drain Extension. Electronics 2021, 10, 29. https://doi.org/10.3390/electronics10010029

Kim HI, Sung JM, Cho HU, Kim YJ, Park YG, Choi WY. LTPS TFTs with an Amorphous Silicon Buffer Layer and Source/Drain Extension. Electronics. 2021; 10(1):29. https://doi.org/10.3390/electronics10010029

Chicago/Turabian StyleKim, Hye In, Jung Min Sung, Hyung Uk Cho, Yong Jo Kim, Young Gwan Park, and Woo Young Choi. 2021. "LTPS TFTs with an Amorphous Silicon Buffer Layer and Source/Drain Extension" Electronics 10, no. 1: 29. https://doi.org/10.3390/electronics10010029

APA StyleKim, H. I., Sung, J. M., Cho, H. U., Kim, Y. J., Park, Y. G., & Choi, W. Y. (2021). LTPS TFTs with an Amorphous Silicon Buffer Layer and Source/Drain Extension. Electronics, 10(1), 29. https://doi.org/10.3390/electronics10010029