- Feature Paper

- Article

2QGRU: Power-of-Two Quantization for Efficient FPGA-Based Gated Recurrent Unit Architectures

- Miguel Molina Fernandez,

- Shao Jie Hu Chen and

- Marisa Lopez-Vallejo

- + 3 authors

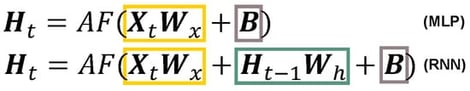

This paper proposes a power-of-two-based quantization technique aimed at improving the hardware efficiency of artificial neural networks (ANNs) implemented on field-programmable gate arrays (FPGAs). The effectiveness of the proposed approach is validated using gated recurrent unit (GRU) models. The resulting architecture, referred to as , exploits parallelism, optimized operation scheduling, and fine-grained data bit-width management to achieve efficient hardware realization. Compared with state-of-the-art FPGA implementations based on sparsity compression, demonstrates superior performance in terms of resource utilization and power consumption, while eliminating the need for dedicated DSP blocks. Furthermore, area and power efficiency can be further improved by trading latency for reduced hardware cost through an integrated implementation reduction strategy, enabling deployment on highly resource-constrained devices. Finally, the model is integrated into an automated ANN framework, allowing the proposed quantization and hardware optimization techniques to be readily extended to other ANN models and FPGA-based deployments.

7 February 2026

![The automatic mechatronic device for insect image collection: (a) An insect monitoring light trap; (b) The image captured by the device (Source: The image is sourced from the dataset published by Wang et al. [26]).](https://mdpi-res.com/cdn-cgi/image/w=281,h=192/https://mdpi-res.com/electronics/electronics-15-00714/article_deploy/html/images/electronics-15-00714-g001-550.jpg)