Temperature Dependent Analytical Model for the Threshold Voltage of the SiC VJFET with a Lateral Asymmetric Channel

Abstract

:1. Introduction

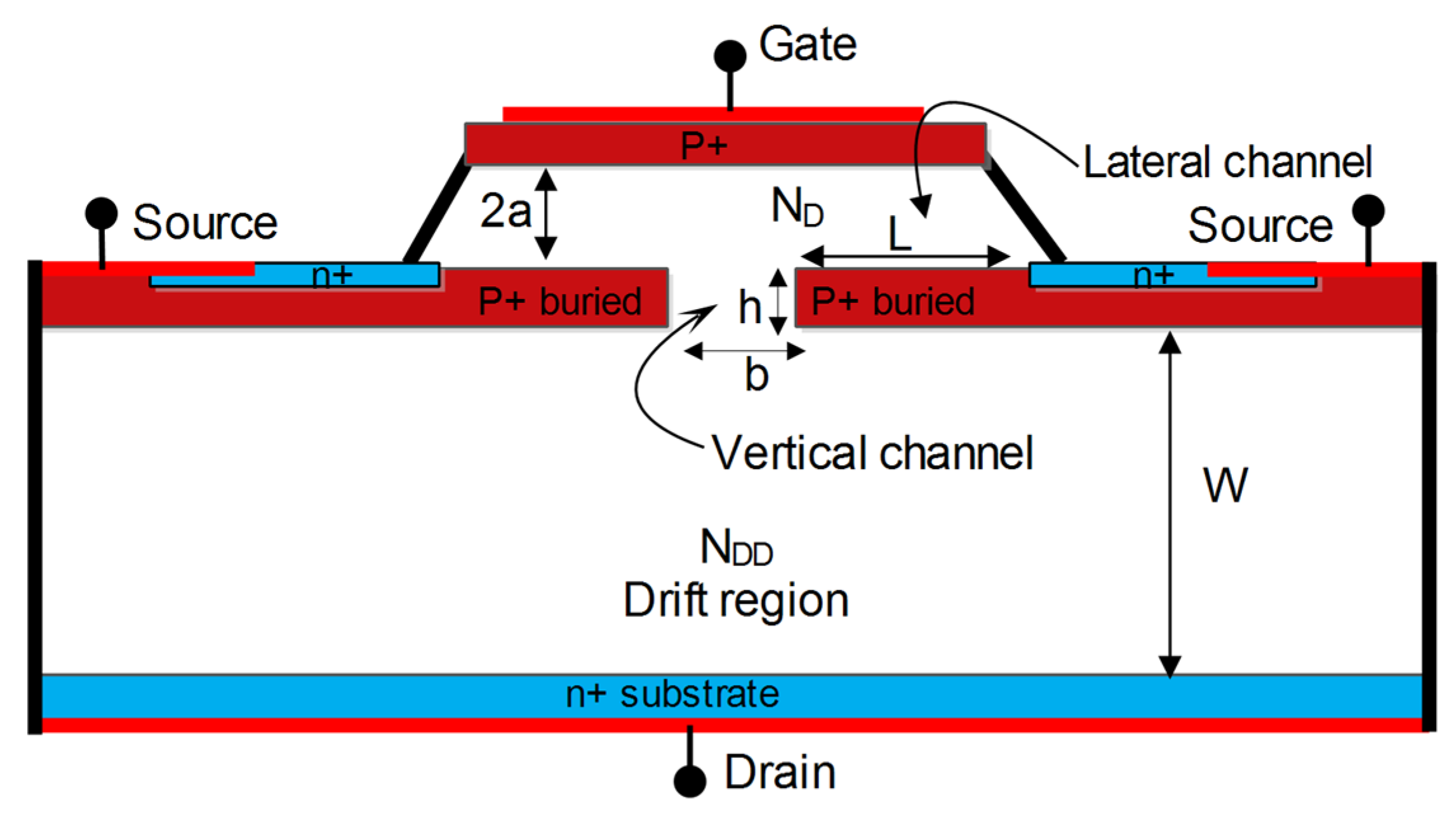

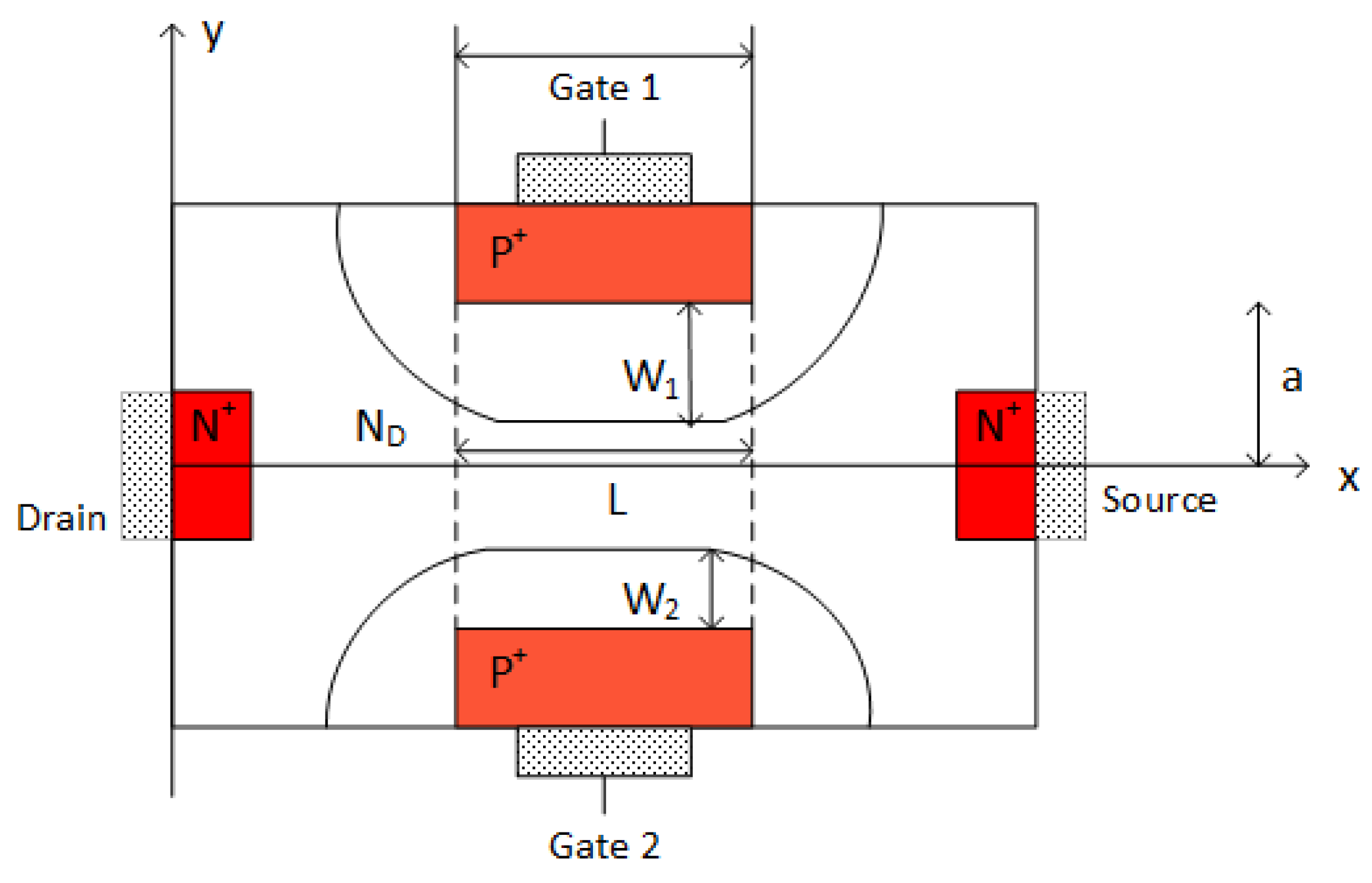

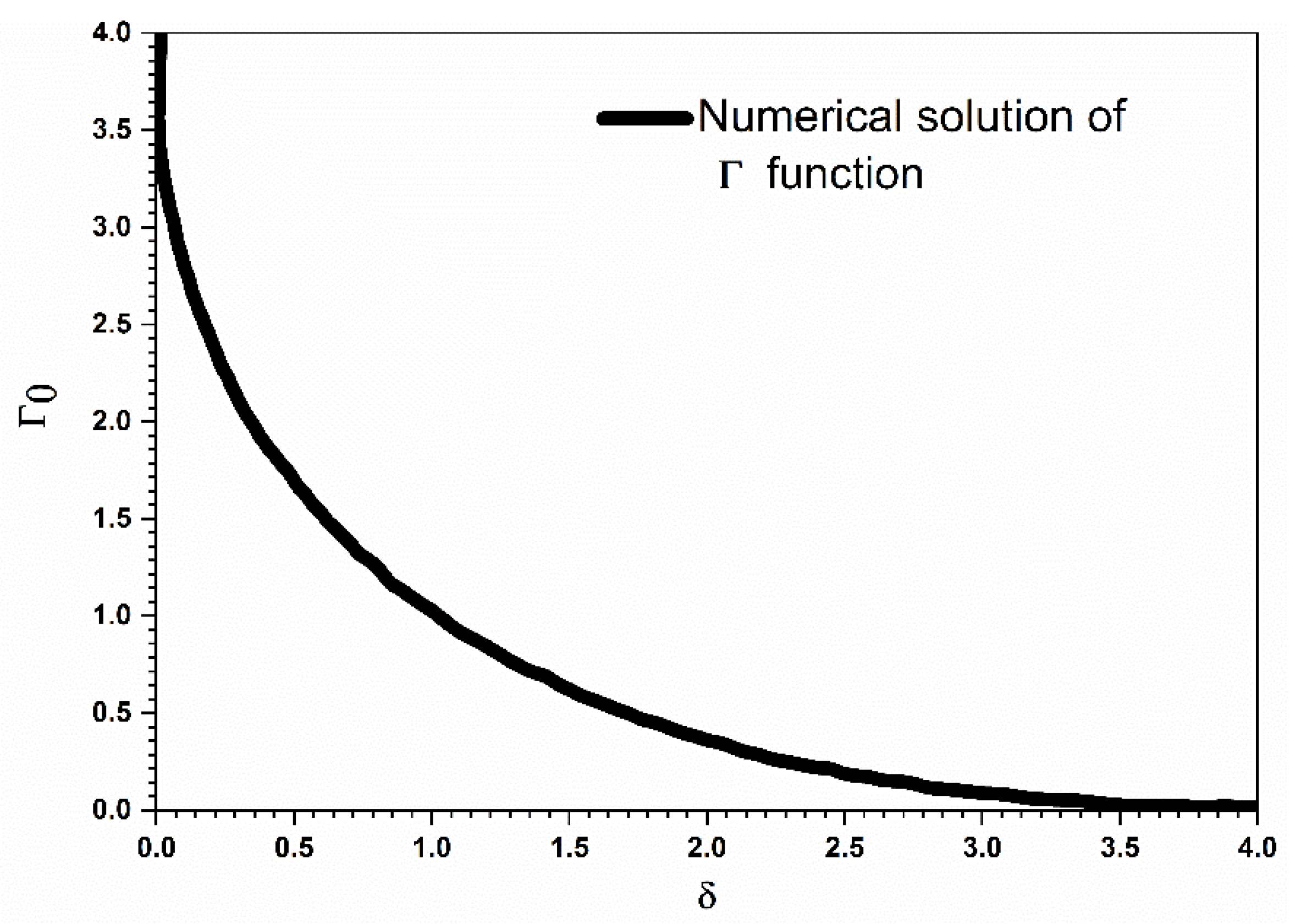

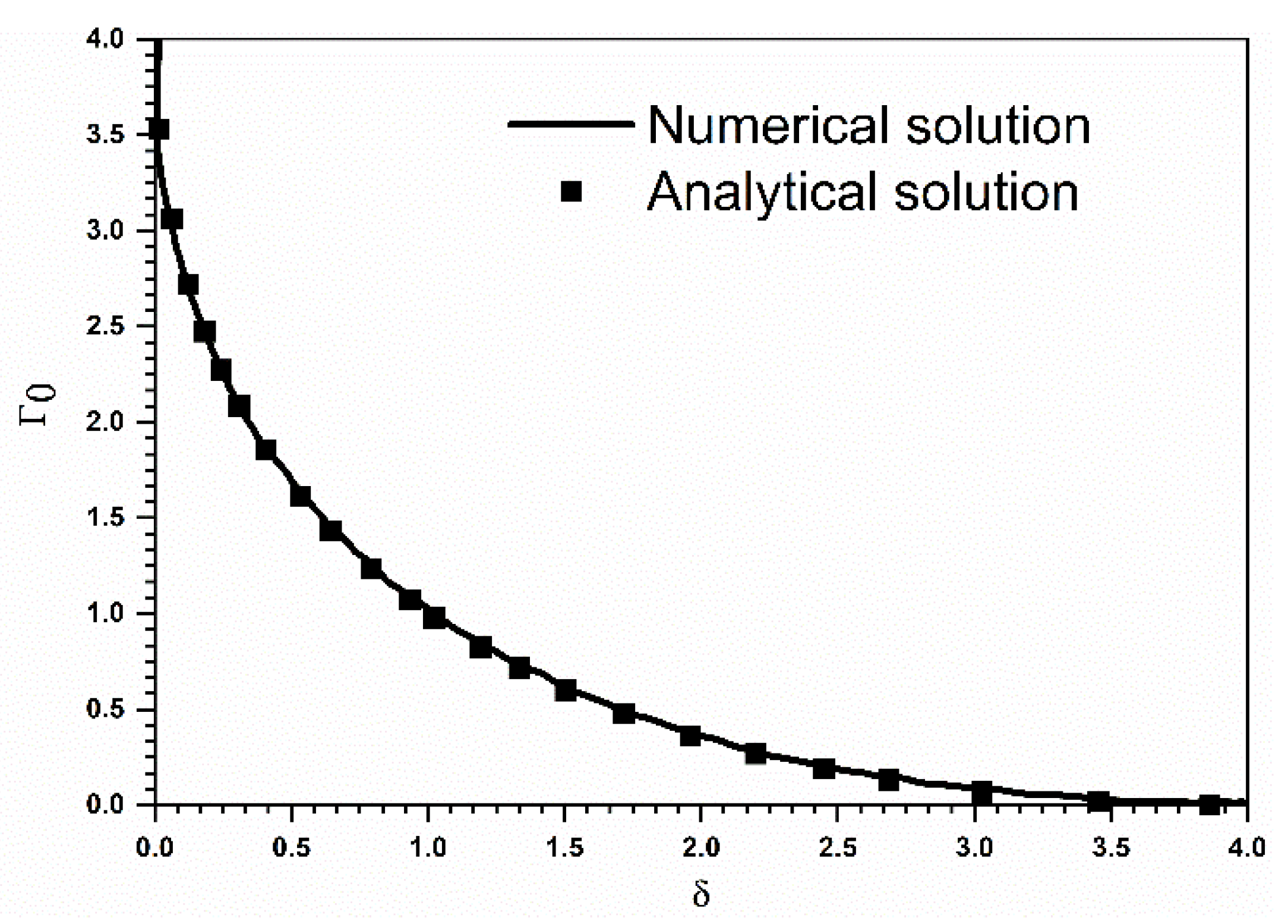

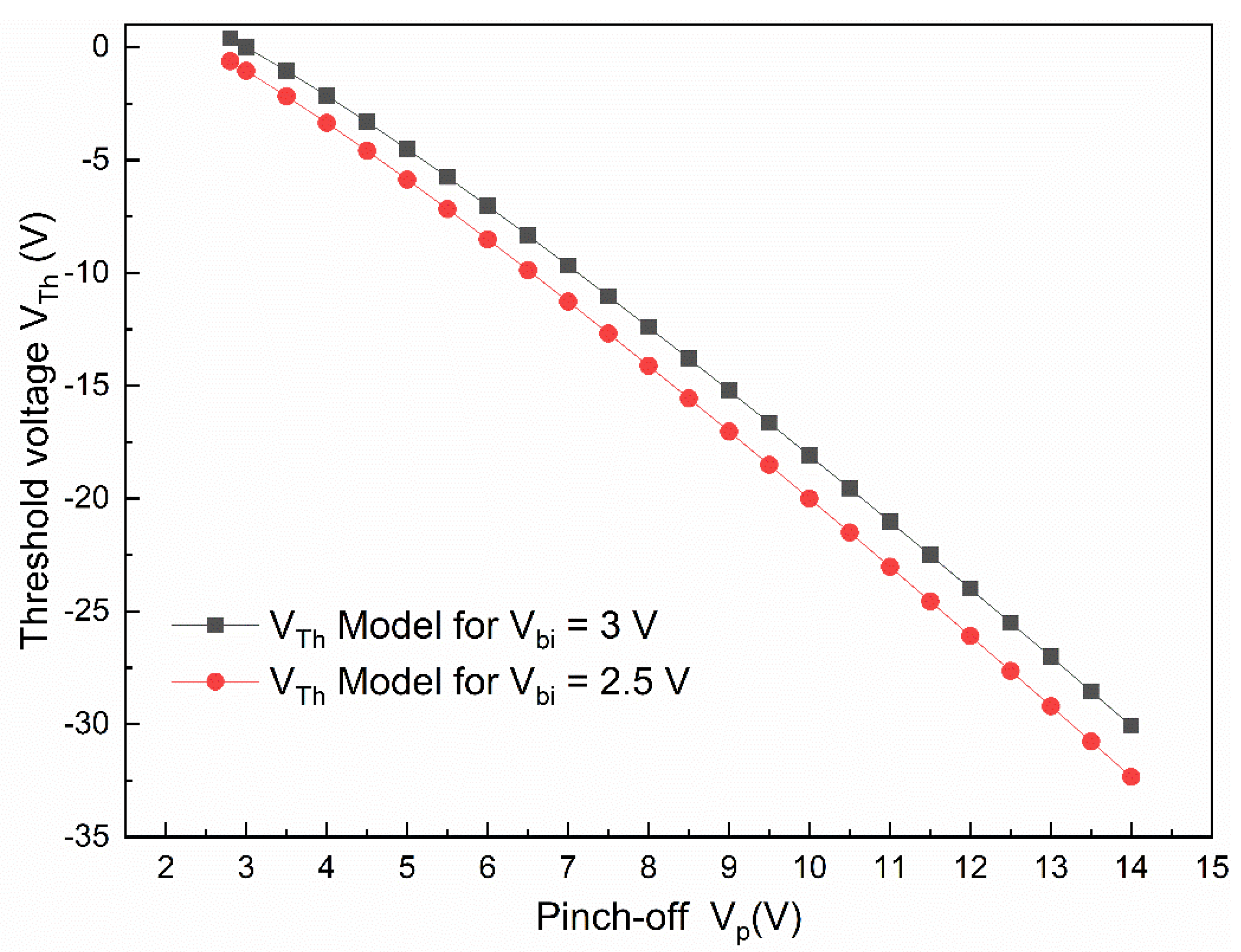

2. Analysis and Modeling of the Asymmetric Lateral Channel of the VJFET

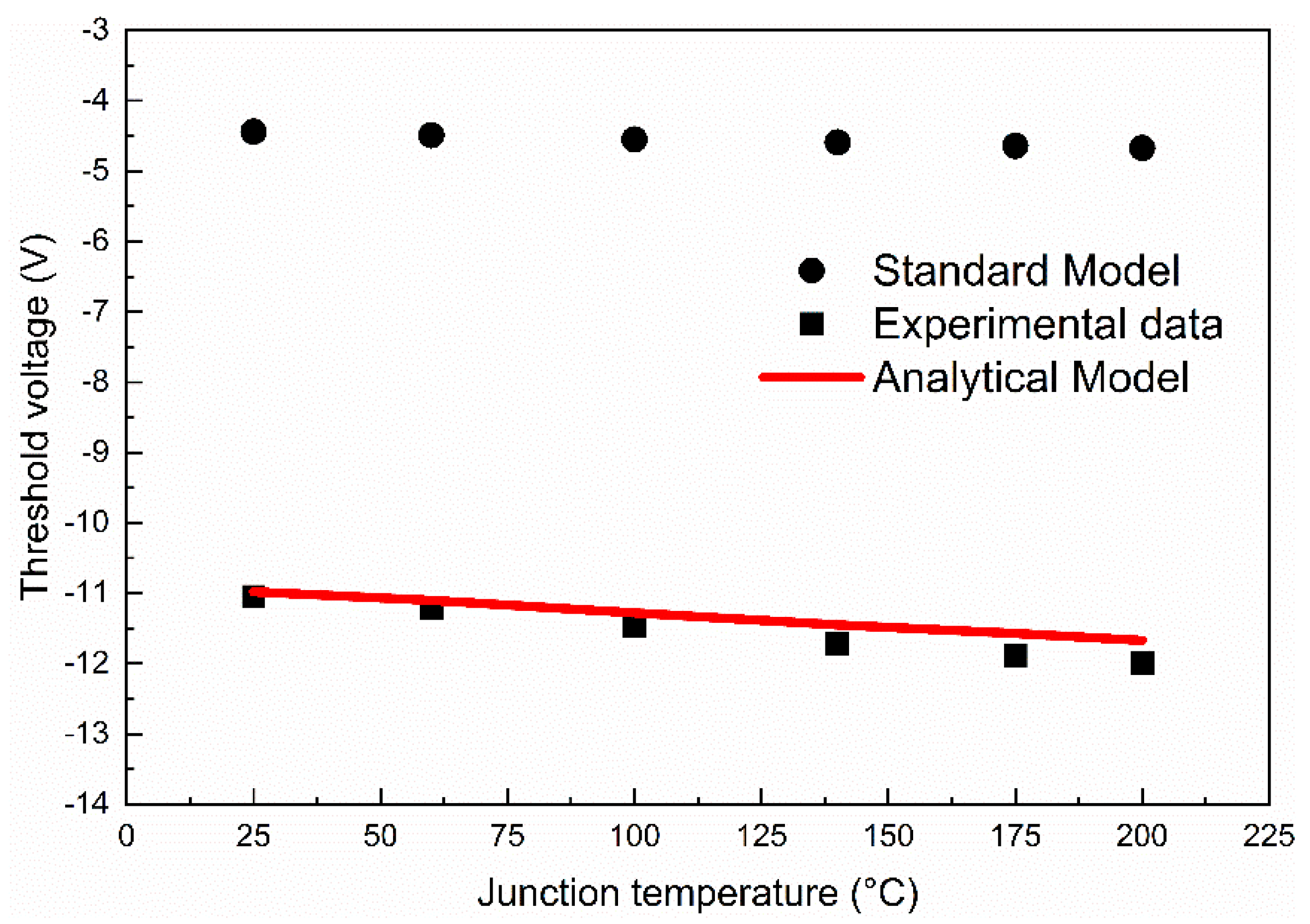

3. Threshold Voltage Model and Validation

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Ortiz-Conde, A.; García Sánchez, F.J.; Liou, J.J.; Cerdeira, A.; Estrada, M.; Yue, Y. A review of recent MOSFET threshold voltage extraction methods. Microelectron. Reliab. 2002, 42, 583–596. [Google Scholar] [CrossRef]

- Tsormpatzoglou, A.; Tassis, D.H.; Dimitriadis, C.A.; Ghibaudo, G.; Collaert, N.; Pananakakis, G. Analytical threshold voltage model for lightly doped short-channel tri-gate MOSFETs. Solid-State Electron. 2011, 57, 31–34. [Google Scholar] [CrossRef]

- Tsormpatzoglou, A.; Pappas, I.; Tassis, D.H.; Dimitriadis, C.A.; Ghibaudo, G. Analytical threshold voltage model for short-channel asymmetrical dual-gate material double-gate MOSFETs. Microelectron. Eng. 2012, 90, 9–11. [Google Scholar] [CrossRef]

- Ortiz-Conde, A.; García-Sánchez, F.J.; Muci, J.; Terán Barrios, A.; Liou, J.J.; Ho, C.-S. Revisiting MOSFET threshold voltage extraction methods. Microelectron. Reliab. 2013, 53, 90–104. [Google Scholar] [CrossRef]

- Aichinger, T.; Rescher, G.; Pobegen, G. Threshold voltage peculiarities and bias temperature instabilities of SiC MOSFETs. Microelectron. Reliab. 2018, 80, 68–78. [Google Scholar] [CrossRef]

- Guevara, E.; Herrera-Pérez, V.; Rocha, C.; Guerrero, K. Threshold Voltage Degradation for n-Channel 4H-SiC Power MOSFETs. J. Low Power Electron. Appl. 2020, 10, 3. [Google Scholar] [CrossRef] [Green Version]

- Friedrichs, P.; Stephani, D. Unipolar SiC power devices and elevated temperature. Microelectron. Eng. 2006, 83, 181–184. [Google Scholar] [CrossRef]

- Gachovska, T.K.; Hudgins, J.L. 5-SiC and GaN Power Semiconductor Devices. In Power Electronics Handbook, 4th ed.; Rashid, M.H., Ed.; Butterworth-Heinemann: Oxford, UK, 2018; pp. 95–155. [Google Scholar]

- Ji, D.; Chowdhury, S. Design of 1.2 kV Power Switches with Low RON Using GaN-Based Vertical JFET. IEEE Trans. Electron. Devices 2015, 62, 2571–2578. [Google Scholar] [CrossRef]

- Kaneko, M.; Kimoto, T. High-Temperature Operation of n- and p-Channel JFETs Fabricated by Ion Implantation into a High-Purity Semi-Insulating SiC Substrate. IEEE Electron. Device Lett. 2018, 39, 723–726. [Google Scholar] [CrossRef]

- Huang, H.; Li, F.; Sun, Z.; Sun, N.; Zhang, F.; Cao, Y.; Zhang, H.; Tao, P. Gallium Nitride Normally-Off Vertical Field-Effect Transistor Featuring an Additional Back Current Blocking Layer Structure. Electronics 2019, 8, 241. [Google Scholar] [CrossRef] [Green Version]

- Barbagallo, C.; Rizzo, S.A.; Scelba, G.; Scarcella, G.; Cacciato, M. On the Lifetime Estimation of SiC Power MOSFETs for Motor Drive Applications. Electronics 2021, 10, 324. [Google Scholar] [CrossRef]

- Kizilyalli, I.C.; Aktas, O. Characterization of vertical GaN p–n diodes and junction field-effect transistors on bulk GaN down to cryogenic temperatures. Semicond. Sci. Technol. 2015, 30, 124001. [Google Scholar] [CrossRef] [Green Version]

- Li, H.; Liao, X.; Hu, Y.; Huang, Z.; Wang, K. Analysis of Voltage Variation in Silicon Carbide MOSFETs during Turn-On and Turn-Off. Energies 2017, 10, 1456. [Google Scholar] [CrossRef] [Green Version]

- Alonso, A.R.; Díaz, M.F.; Lamar, D.G.; Azpeitia, M.A.P.d.; Hernando, M.M.; Sebastián, J. Switching Performance Comparison of the SiC JFET and SiC JFET/Si MOSFET Cascode Configuration. IEEE Trans. Power Electron. 2014, 29, 2428–2440. [Google Scholar] [CrossRef] [Green Version]

- Elpelt, R.; Friedrichs, P.; Biela, J. Fast Switching with SiC VJFETs-Influence of the Device Topology. Mater. Sci. Forum 2010, 645–648, 933–936. [Google Scholar] [CrossRef]

- Veliadis, V. Silicon Carbide Junction Field-Effect Transistors (SiC JFETs). In Wiley Encyclopedia of Electrical and Electronics Engineering; John Wiley & Sons: Linthicum, MD, USA, 2014; pp. 1–37. [Google Scholar]

- Neudeck, P.G.; Spry, D.J.; Chen, L.Y. Experimental and Theoretical Study of 4H-SiC JFET Threshold Voltage Body Bias Effect from 25 °C to 500 °C. Mater. Sci. Forum 2016, 858, 903–907. [Google Scholar] [CrossRef]

- Kayambaki, M.; Makris, N.; Stavrinidis, A.; Konstantinidis, G.; Zekentes, K. On the Optimum Determination and Use of SiC VJFET Threshold Voltage. Mater. Sci. Forum 2018, 924, 657–660. [Google Scholar] [CrossRef]

- Asllani, B.; Bevilacqua, P.; Zaoui, A.; Grosset, G.; Planson, D.; Morel, H. High-Voltage SiC-JFET Fabrication and Full Characterization. Mater. Sci. Forum 2019, 963, 688–692. [Google Scholar] [CrossRef] [Green Version]

- Fernández-Martínez, P.; Flores, D.; Hidalgo, S.; Jordà, X.; Perpiñà, X.; Quirion, D.; Ré, L.; Ullán, M.; Vellvehí, M. A New Vertical JFET Power Device for Harsh Radiation Environments. Energies 2017, 10, 256. [Google Scholar] [CrossRef] [Green Version]

- Bargieł, K.; Bisewski, D.; Zarębski, J. Modelling of Dynamic Properties of Silicon Carbide Junction Field-Effect Transistors (JFETs). Energies 2020, 13, 187. [Google Scholar] [CrossRef] [Green Version]

- Zhang, Y.; Tang, M.; Song, Q.; Tang, X.; Lv, H.; Liu, S. High temperature characterization of normally-on 4H-SiC junction field-effect transistor. Superlattices Microstruct. 2016, 99, 113–117. [Google Scholar] [CrossRef]

- Grekov, A.E.; Chen, Z.; Fu, R.; Hudgins, J.L.; Mantooth, H.A.; Sheridan, D.C.; Casady, J.; Santi, E. Parameter Extraction Procedure for Vertical SiC Power JFET. IEEE Trans. Ind. Appl. 2011, 47, 1862–1871. [Google Scholar] [CrossRef]

- Ghedira, S.; Buttay, C.; Morel, H.; Besbes, K. Measurement and numerical analysis of C-V characteristics for normally-on SiCED-JFET. Eur. Phys. J. Appl. Phys. 2014, 66, 20103. [Google Scholar] [CrossRef]

- Hervé, M.; Youness, H.; Dominique, T.; Rémi, R.; Fabien, D.; Damien, R.; Christian, M.; Dominique, B.; Cyril, B.; Régis, M. A multi-physics model of the VJFET with a lateral channel. In Proceedings of the 2011 14th European Conference on Power Electronics and Applications, Birmingham, UK, 30 August–1 September 2011; pp. 1–10. [Google Scholar]

- Dubois, F.; Bergogne, D.; Tournier, D.; Buttay, C.; Meuret, R.; Morel, H. Analysis of the SiC VJFET gate punch-through and its dependence with the temperature. In Proceedings of the 2013 15th European Conference on Power Electronics and Applications (EPE), Lille, France, 2–6 September 2013; pp. 1–10. [Google Scholar]

- Baliga, B.J. Modern Power Devices; Wiley: Hoboken, NJ, USA, 1987. [Google Scholar]

- Baliga, B.J. Fundamentals of Power Semiconductor Devices; Springer International Publishing: Berlin/Heidelberg, Germany, 2018. [Google Scholar]

- Sze, S.M.; Lee, M.K. Semiconductor Devices: Physics and Technology; John Wiley & Sons: New York, NY, USA, 2013. [Google Scholar]

- Synopsys. Sentaurus Device User Guide, Version F-2011.09 ed.; Synopsys: Mountain View, CA, USA, 2011. [Google Scholar]

| Symbol | Definition | Value |

|---|---|---|

| a | Half width of the lateral channel | 0.72 µm |

| L | Length of the lateral channel | 6 µm |

| ND | Doping level in the lateral channel | 2.4 × 1016 cm−3 |

| NA | Dopping in the gate | 1 × 1018 cm−3 |

| W | Thickness of the epilayer | 15 µm |

| NDD | Doping level in the epilayer | 5 × 1015 cm−3 |

| h | Width of the vertical channel | 0.7 µm |

| b | Length of the vertical channel | 2.6 µm |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ghedira, S.; Fargi, A.; Besbes, K. Temperature Dependent Analytical Model for the Threshold Voltage of the SiC VJFET with a Lateral Asymmetric Channel. Electronics 2021, 10, 1494. https://doi.org/10.3390/electronics10121494

Ghedira S, Fargi A, Besbes K. Temperature Dependent Analytical Model for the Threshold Voltage of the SiC VJFET with a Lateral Asymmetric Channel. Electronics. 2021; 10(12):1494. https://doi.org/10.3390/electronics10121494

Chicago/Turabian StyleGhedira, Sami, Abdelaali Fargi, and Kamel Besbes. 2021. "Temperature Dependent Analytical Model for the Threshold Voltage of the SiC VJFET with a Lateral Asymmetric Channel" Electronics 10, no. 12: 1494. https://doi.org/10.3390/electronics10121494