An Efficient On-Demand Hardware Replacement Platform for Metamorphic Functional Processing in Edge-Centric IoT Applications

Abstract

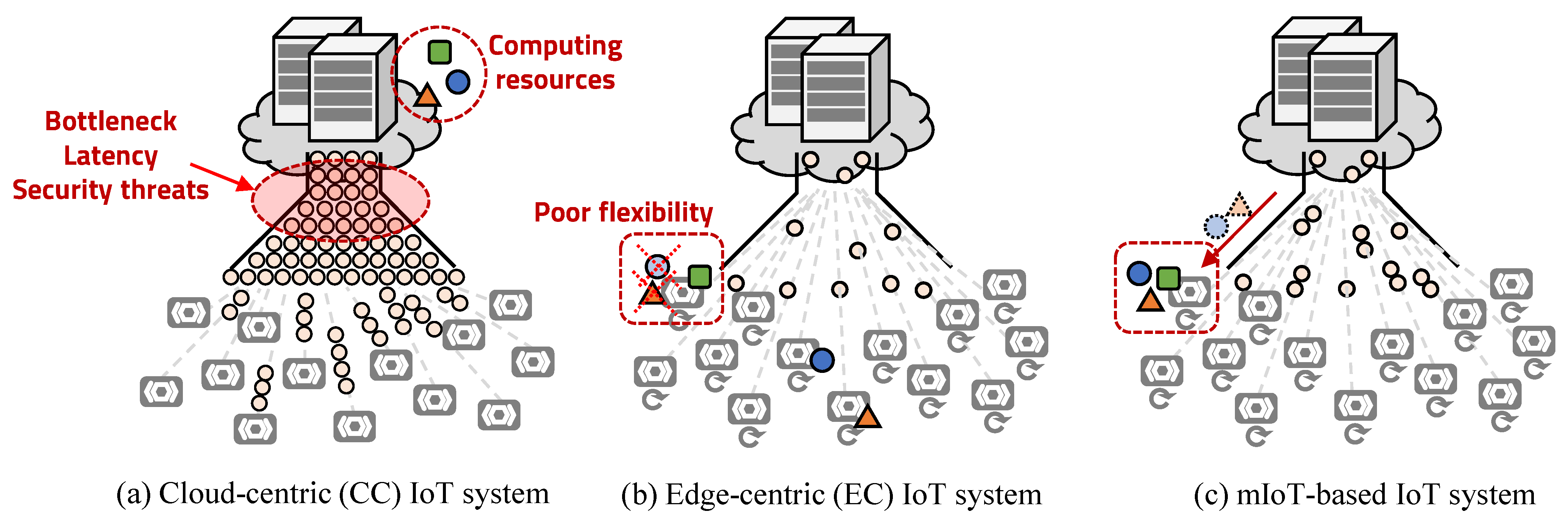

1. Introduction

2. Background

2.1. Dynamic Partial Reconfiguration (DPR)

2.2. Metamorphic IoT Platform (mIoT)

3. Edge-Centric mIoT Platform

3.1. Metamorphic IoT Processor (mIoTP)

3.2. Callability-Based Bitstream Caching Algorithm

3.3. Metamorphic IoT Server

| Algorithm 1: Edge bitstream caching algorithm. |

|

- N = Number of edges of the entire system

- = Reconfiguration time overhead average of all edges

- = Reconfiguration time overhead of one edge

- = Number of reconfiguration events of one edge

- = Reconfiguration time overhead due to L1-miss

- = Reconfiguration time overhead due to edge’s information transfer

- = Reconfiguration time overhead due to pre-reconfiguration

4. Implementation

5. Experiment

6. Discussion

7. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Zhu, C.; Leung, V.C.M.; Shu, L.; Ngai, E.C. Green Internet of Things for Smart World. IEEE Access 2015, 3, 2151–2162. [Google Scholar] [CrossRef]

- Wen, Z.; Yang, R.; Garraghan, P.; Lin, T.; Xu, J.; Rovatsos, M. Fog Orchestration for Internet of Things Services. IEEE Internet Comput. 2017, 21, 16–24. [Google Scholar] [CrossRef]

- De Vito, L.; Picariello, E.; Picariello, F.; Rapuano, S.; Tudosa, I. A Dictionary Optimization Method for Reconstruction of ECG Signals after Compressed Sensing. Sensors 2021, 21, 5282. [Google Scholar] [CrossRef]

- Porkodi, V.; Yuvaraj, D.; Khan, J.; Karuppusamy, S.A.; Goel, P.M.; Sivaram, M. A Survey on Various Machine Learning Models in IOT Applications. In Proceedings of the 2020 International Conference on Computing and Information Technology (ICCIT-1441), Tabuk, Saudi Arabia, 9–10 September 2020; pp. 1–4. [Google Scholar] [CrossRef]

- Yousefpour, A.; Ishigaki, G.; Gour, R.; Jue, J.P. On Reducing IoT Service Delay via Fog Offloading. IEEE Internet Things J. 2018, 5, 998–1010. [Google Scholar] [CrossRef]

- Liu, J.; Luo, K.; Zhou, Z.; Chen, X. ERP: Edge Resource Pooling for Data Stream Mobile Computing. IEEE Internet Things J. 2019, 6, 4355–4368. [Google Scholar] [CrossRef]

- Perera, C.; Liu, C.H.; Jayawardena, S.; Chen, M. A Survey on Internet of Things From Industrial Market Perspective. IEEE Access 2014, 2, 1660–1679. [Google Scholar] [CrossRef]

- Baker, S.B.; Xiang, W.; Atkinson, I. Internet of Things for Smart Healthcare: Technologies, Challenges, and Opportunities. IEEE Access 2017, 5, 26521–26544. [Google Scholar] [CrossRef]

- Wollschlaeger, M.; Sauter, T.; Jasperneite, J. The Future of Industrial Communication: Automation Networks in the Era of the Internet of Things and Industry 4.0. IEEE Ind. Electron. Mag. 2017, 11, 17–27. [Google Scholar] [CrossRef]

- Meloni, P.; Capotondi, A.; Deriu, G.; Brian, M.; Conti, F.; Rossi, D.; Raffo, L.; Benini, L. NEURAghe: Exploiting CPU-FPGA Synergies for Efficient and Flexible CNN Inference Acceleration on Zynq SoCs. ACM Trans. Reconfigurable Technol. Syst. 2018, 11, 1–24. [Google Scholar] [CrossRef]

- Zhong, G.; Dubey, A.; Tan, C.; Mitra, T. Synergy: An HW/SW Framework for High Throughput CNNs on Embedded Heterogeneous SoC. ACM Trans. Embed. Comput. Syst. 2019, 18, 1–23. [Google Scholar] [CrossRef]

- Lee, K.; Kong, J.; Kim, Y.G.; Chung, S.W. Memory streaming acceleration for embedded systems with CPU-accelerator cooperative data processing. Microprocess. Microsyst. 2019, 71, 102897. [Google Scholar] [CrossRef]

- Vogler, M.; Schleicher, J.M.; Inzinger, C.; Dustdar, S. Optimizing Elastic IoT Application Deployments. IEEE Trans. Serv. Comput. 2018, 11, 879–892. [Google Scholar] [CrossRef]

- Ma, L.; Sham, C.W.; Sun, J.; Valencia Tenorio, R. A Real-Time Flexible Telecommunication Decoding Architecture Using FPGA Partial Reconfiguration. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 2149–2153. [Google Scholar] [CrossRef]

- Samir, N.; Gamal, Y.; El-Zeiny, A.N.; Mahmoud, O.; Shawky, A.; Saeed, A.; Mostafa, H. Energy-Adaptive Lightweight Hardware Security Module using Partial Dynamic Reconfiguration for Energy Limited Internet of Things Applications. In Proceedings of the 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 26–29 May 2019; pp. 1–4. [Google Scholar] [CrossRef]

- Rihani, M.A.; Nouvel, F.; Prevotet, J.C.; Mroue, M.; Lorandel, J.; Mohanna, Y. Dynamic and partial reconfiguration power consumption runtime measurements analysis for ZYNQ SoC devices. In Proceedings of the 2016 International Symposium on Wireless Communication Systems (ISWCS), Poznan, Poland, 20–23 September 2016; pp. 592–596. [Google Scholar] [CrossRef]

- Kim, H.; Lee, D.; Cho, J.; Park, D. Software execution freeze-safe microcontroller using power profile tracking for IoT-driven connected services. In Proceedings of the 2018 IEEE 4th World Forum on Internet of Things (WF-IoT), Singapore, 5–8 February 2018; pp. 237–240. [Google Scholar] [CrossRef]

- Duarte, R.P.; Neto, H.C. Stochastic Processors on FPGAs to Compute Sensor Data Towards Fault-Tolerant IoT Systems. In Proceedings of the 2018 IEEE Conference on Dependable and Secure Computing (DSC), Kaohsiung, Taiwan, 10–13 December 2018; pp. 1–8. [Google Scholar] [CrossRef]

- Wang, C.; Vo, H.T.; Ni, P. An IoT Application for Fault Diagnosis and Prediction. In Proceedings of the 2015 IEEE International Conference on Data Science and Data Intensive Systems, Sydney, Australia, 11–13 December 2015; pp. 726–731. [Google Scholar] [CrossRef]

- Sadeghi, M.; Razavi, S.A.; Zamani, M.S. Reducing Reconfiguration Time in FPGAs. In Proceedings of the 2019 27th Iranian Conference on Electrical Engineering (ICEE), Yazd, Iran, 30 April–2 May 2019; pp. 1844–1848. [Google Scholar] [CrossRef]

- Xie, J.; Wang, Y.; Chen, L.; Wang, J.; Wang, Y.; Lai, J.; Tong, J. Fast configuration architecture of FPGA suitable for bitstream compression. In Proceedings of the 2009 IEEE 8th International Conference on ASIC, Changsha, China, 20–23 October 2009; pp. 126–130. [Google Scholar] [CrossRef]

- Lie, W.; Wu, F.Y. Dynamic Partial Reconfiguration in FPGAs. In Proceedings of the 2009 Third International Symposium on Intelligent Information Technology Application, Nanchang, China, 21–22 November 2009; Volume 2, pp. 445–448. [Google Scholar] [CrossRef]

- Vipin, K.; Fahmy, S.A. ZyCAP: Efficient Partial Reconfiguration Management on the Xilinx Zynq. IEEE Embed. Syst. Lett. 2014, 6, 41–44. [Google Scholar] [CrossRef]

- Paulino, N.M.C.; Ferreira, J.C.; Cardoso, J.M.P. Dynamic Partial Reconfiguration of Customized Single-Row Accelerators. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2019, 27, 116–125. [Google Scholar] [CrossRef]

- Tej, B.; Hannachi, M.; Abdelali, A.B. Partial Dynamic Reconfiguration for efficient Adaptive Implementation of a Video Shot Boundary Detection System. In Proceedings of the 2020 4th International Conference on Advanced Systems and Emergent Technologies, Hammamet, Tunisia, 15–18 December 2020; pp. 327–331. [Google Scholar] [CrossRef]

- Youssef, E.; Elsemary, H.A.; El-Moursy, M.A.; Khattab, A.; Mostafa, H. Energy Adaptive Convolution Neural Network Using Dynamic Partial Reconfiguration. In Proceedings of the 2020 IEEE 63rd International Midwest Symposium on Circuits and Systems (MWSCAS), Springfield, MA, USA, 9–12 August 2020; pp. 325–328. [Google Scholar] [CrossRef]

- Daoud, L.; Hussein, F.; Rafla, N. Real-time Bitstream Decompression Scheme for FPGAs Reconfiguration. In Proceedings of the 2018 IEEE 61st International Midwest Symposium on Circuits and Systems (MWSCAS), Windsor, ON, Canada, 5–8 August 2018; pp. 1082–1085. [Google Scholar] [CrossRef]

- Botta, A.; de Donato, W.; Persico, V.; Pescape, A. Integration of Cloud computing and Internet of Things: A survey. Future Gener. Comput. Syst. 2016, 56, 684–700. [Google Scholar] [CrossRef]

- Stanik, A.; Hovestadt, M.; Kao, O. Hardware as a Service (HaaS): Physical and virtual hardware on demand. In Proceedings of the 4th IEEE International Conference on Cloud Computing Technology and Science Proceedings, Taipei, Taiwan, 3–6 December 2012; pp. 149–154. [Google Scholar] [CrossRef]

- El-Sayed, H.; Sankar, S.; Prasad, M.; Puthal, D.; Gupta, A.; Mohanty, M.; Lin, C.T. Edge of Things: The Big Picture on the Integration of Edge, IoT and the Cloud in a Distributed Computing Environment. IEEE Access 2018, 6, 1706–1717. [Google Scholar] [CrossRef]

- Ferdian, R.; Aisuwarya, R.; Erlina, T. Edge Computing for Internet of Things Based on FPGA. In Proceedings of the 2020 International Conference on Information Technology Systems and Innovation (ICITSI), Bandung, Indonesia, 19–23 October 2020; pp. 20–23. [Google Scholar] [CrossRef]

- Gomes, T.; Pinto, S.; Gomes, T.; Tavares, A.; Cabral, J. Towards an FPGA-based edge device for the Internet of Things. In Proceedings of the 2015 IEEE 20th Conference on Emerging Technologies Factory Automation (ETFA), Luxembourg City, Luxembourg, 8–11 September 2015; pp. 1–4. [Google Scholar] [CrossRef]

- Lee, D.; Moon, H.; Oh, S.; Park, D. mIoT: Metamorphic IoT Platform for On-Demand Hardware Replacement in Large-Scaled IoT Applications. Sensors 2020, 40, 3337. [Google Scholar] [CrossRef]

- Diaz, M.; Martin, C.; Rubio, B. State-of-the-art, challenges, and open issues in the integration of Internet of things and cloud computing. J. Netw. Comput. Appl. 2016, 67, 99–117. [Google Scholar] [CrossRef]

- Roman, R.; Najera, P.; Lopez, J. Securing the Internet of Things. Computer 2011, 44, 51–58. [Google Scholar] [CrossRef]

- Esposito, C.; Castiglione, A.; Pop, F.; Choo, K.R. Challenges of Connecting Edge and Cloud Computing: A Security and Forensic Perspective. IEEE Cloud Comput. 2017, 4, 13–17. [Google Scholar] [CrossRef]

- Ostanin, S.; Matrosova, A.; Butorina, N.; Lavrov, V. A fault-tolerant sequential circuit design for soft errors based on fault-secure circuit. In Proceedings of the 2016 IEEE East-West Design Test Symposium (EWDTS), Yerevan, Armenia, 14–17 October 2016; pp. 1–4. [Google Scholar] [CrossRef]

- Thati, V.B.; Vankeirsbilck, J.; Boydens, J. Comparative study on data error detection techniques in embedded systems. In Proceedings of the 2016 XXV International Scientific Conference Electronics (ET), Sozopol, Bulgaria, 12–14 September 2016; pp. 1–4. [Google Scholar] [CrossRef]

- Veljkovi, F.; Riesgo, T.; de la Torre, E. Adaptive reconfigurable voting for enhanced reliability in medium-grained fault tolerant architectures. In Proceedings of the 2015 NASA/ESA Conference on Adaptive Hardware and Systems (AHS), Montreal, QC, Canada, 15–18 June 2015; pp. 1–8. [Google Scholar] [CrossRef]

- Choi, K.; Park, D.; Cho, J. SSCFM: Separate Signature-Based Control Flow Error Monitoring for Multi-Threaded and Multi-Core Environments. Electronics 2019, 8, 166. [Google Scholar] [CrossRef]

- An, J.; Seok, M.G.; Park, D. Automatic on-chip backup clock changer for protecting abnormal MCU operations in unsafe clock frequency. IEICE Electron. Express 2016, 13, 20160808. [Google Scholar] [CrossRef][Green Version]

- Gao, T.; Xu, X.; Zhang, H.; Yang, H. A highly-integrated wireless configuration circuit for FPGA chip. In Proceedings of the 2014 International Symposium on Integrated Circuits (ISIC), Singapore, 10–12 December 2014; pp. 260–263. [Google Scholar] [CrossRef]

- Adly, I.; Ragai, H.; Shehata, K.; Al-Henawy, A. Wireless Configuration Controller Design for FPGAs in Software Defined Radios. Online J. Electron. Electr. Eng. OJEEE 2010, 2, 293. [Google Scholar]

- Kwak, J.; Lee, S.; Cho, J.; Park, D. Lightweight Polygonal Approximation-Based ECG Signal Processing Platform. In Proceedings of the 2019 IEEE International Conference on Dependable, Autonomic and Secure Computing, Fukuoka, Japan, 5–8 August 2019; pp. 819–824. [Google Scholar] [CrossRef]

- Moon, H.; Cho, J.; Park, D. Reconfigurable Fault-Safe Processor Platform Based on RISC-V for Large-Scaled IoT-Driven Applications. In Proceedings of the 2019 IEEE International Conference on Dependable, Autonomic and Secure Computing, Fukuoka, Japan, 5–8 August 2019; pp. 627–632. [Google Scholar] [CrossRef]

| Type | L1-Miss | Information Transfer | Pre-Reconfiguration |

|---|---|---|---|

| Composition | >0.1% | 82% | 17.9% |

| Time(s) | 0.8 | >0.001 | 0.8 |

| Type | [33] (Double RMs) | EC mIoT (Single RM) | EC mIoT (Double RMs) |

|---|---|---|---|

| # Server access | 2716 | 824 | 484 |

| # Server access (relative) | 1.000 | 0.303 | 0.178 |

| BCA Lib size | - | 352 byte | 352 byte |

| BCA Lib size/ICache size | - | 8.6% | 8.6% |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Moon, H.; Park, D. An Efficient On-Demand Hardware Replacement Platform for Metamorphic Functional Processing in Edge-Centric IoT Applications. Electronics 2021, 10, 2088. https://doi.org/10.3390/electronics10172088

Moon H, Park D. An Efficient On-Demand Hardware Replacement Platform for Metamorphic Functional Processing in Edge-Centric IoT Applications. Electronics. 2021; 10(17):2088. https://doi.org/10.3390/electronics10172088

Chicago/Turabian StyleMoon, Hyeongyun, and Daejin Park. 2021. "An Efficient On-Demand Hardware Replacement Platform for Metamorphic Functional Processing in Edge-Centric IoT Applications" Electronics 10, no. 17: 2088. https://doi.org/10.3390/electronics10172088

APA StyleMoon, H., & Park, D. (2021). An Efficient On-Demand Hardware Replacement Platform for Metamorphic Functional Processing in Edge-Centric IoT Applications. Electronics, 10(17), 2088. https://doi.org/10.3390/electronics10172088