40 GHz VCO and Frequency Divider in 28 nm FD-SOI CMOS Technology for Automotive Radar Sensors

Abstract

:1. Introduction

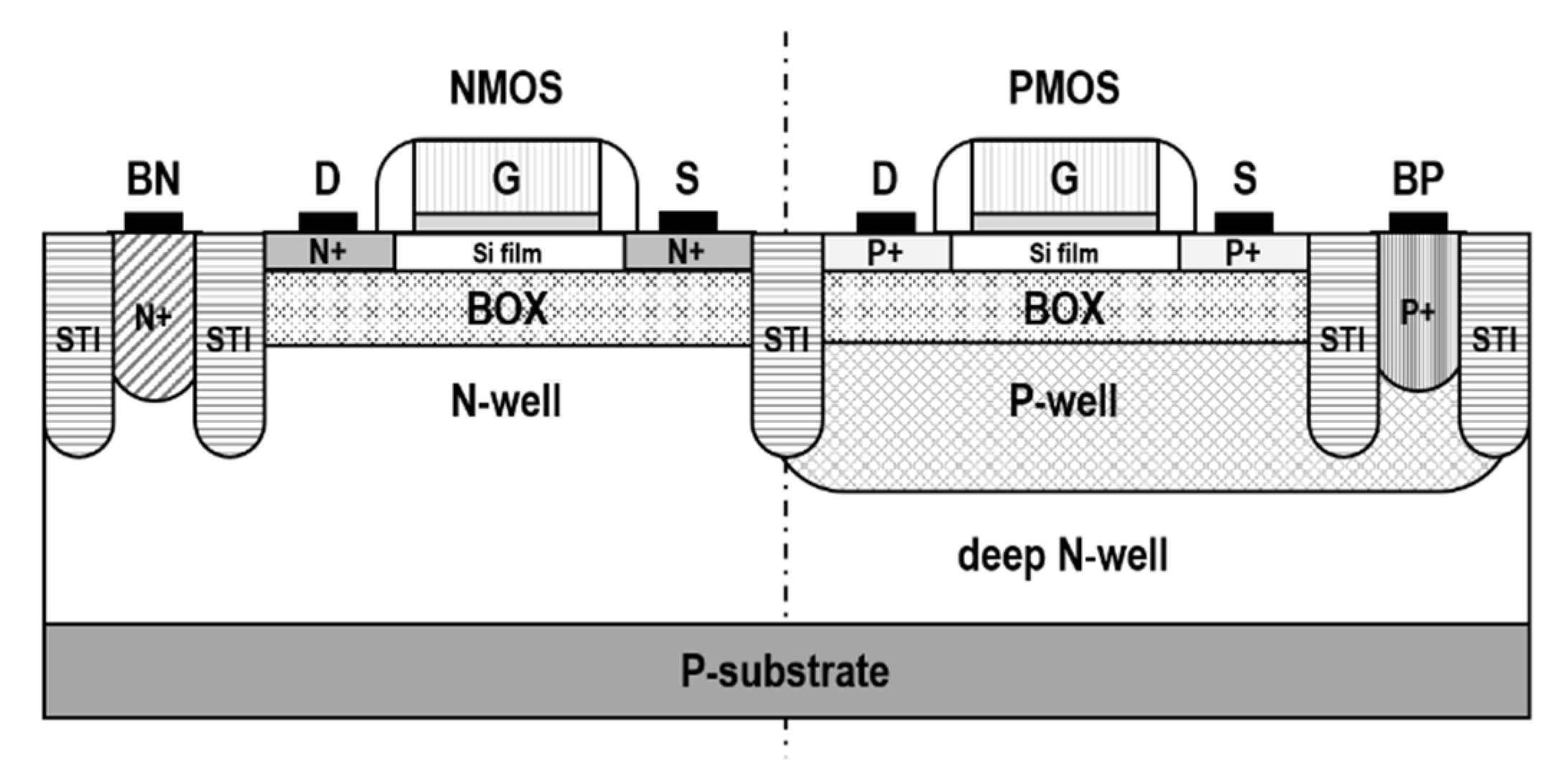

2. The 28 nm UTBB FD-SOI CMOS Technology

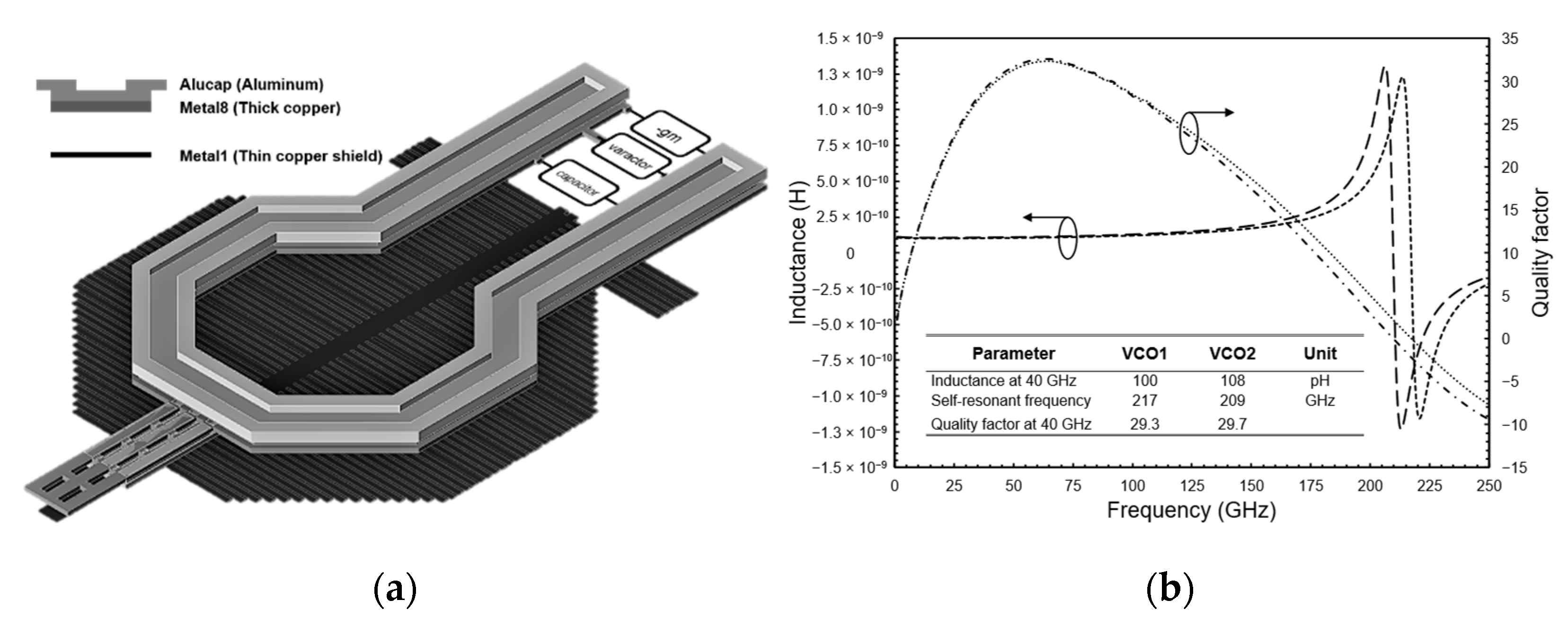

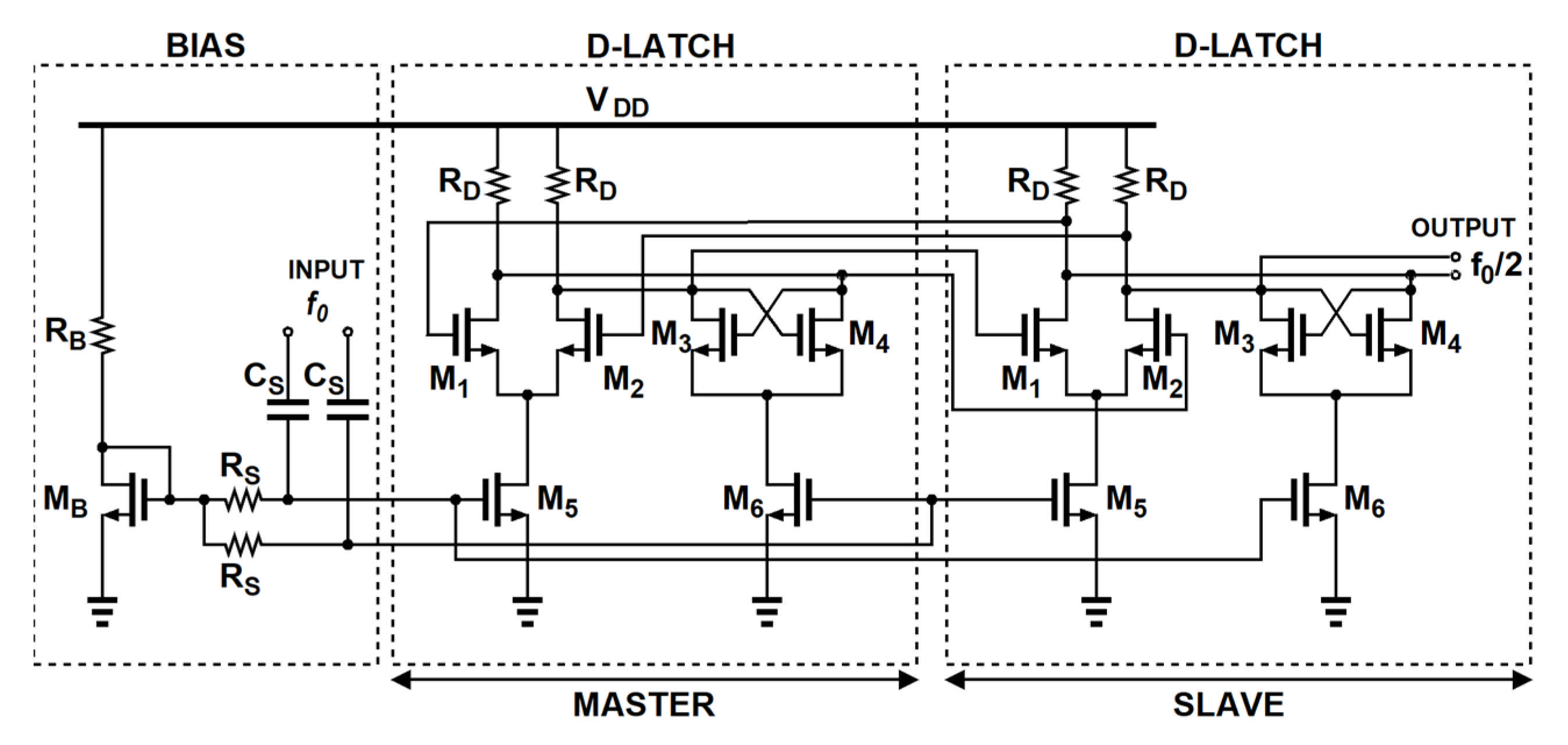

3. Circuit Design

4. Experimental Results

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Guermandi, D.; Shi, Q.; Dewilde, A.; Derudder, V.; Ahmad, U.; Spagnolo, A.; Ocket, I.; Bourdoux, A.; Wambacq, P.; Craninckx, J.; et al. A 79-GHz 2 × 2 MIMO PMCW Radar SoC in 28-nm CMOS. IEEE J. Solid-State Circuits 2017, 52, 2613–2626. [Google Scholar] [CrossRef]

- Ma, T.; Deng, W.; Chen, Z.; Wu, J.; Zheng, W.; Wang, S.; Qi, N.; Liu, Y.; Chi, B. A CMOS 76–81-GHz 2-TX 3-RX FMCW Radar Transceiver Based on Mixed-Mode PLL Chirp Generator. IEEE J. Solid-State Circuits 2020, 55, 233–248. [Google Scholar] [CrossRef]

- Giannini, V.; Goldenberg, M.; Eshraghi, A.; Maligeorgos, J.; Lim, L.; Lobo, R.; Welland, D.; Chow, C.; Dornbusch, A.; Dupuis, T.; et al. A 192-Virtual-Receiver 77/79 GHz GMSK Code-Domain MIMO Radar System-on-Chip. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2019; pp. 164–166. [Google Scholar]

- Patole, S.M.; Torlak, M.; Wang, D.; Ali, M. Automotive radars: A review of signal processing techniques. IEEE Signal. Process. Mag. 2017, 34, 22–35. [Google Scholar] [CrossRef]

- Melzer, A.; Onic, A.; Starzer, F.; Huemer, M. Short-Range Leakage Cancelation in FMCW Radar Transceivers Using an Artificial On-Chip Target. IEEE J. Sel. Top. Signal. Process. 2015, 9, 1650–1660. [Google Scholar] [CrossRef]

- Pelloux-Prayer, B.; Blagojević, M.; Haendler, S.; Valentian, A.; Amara, A.; Flatresse, P. Performance analysis of multi-VT design solutions in 28 nm UTBB FD-SOI technology. In Proceedings of the IEEE International SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Monteray, CA, USA, 7–10 October 2013; pp. 1–2. [Google Scholar]

- Shopov, S.; Voinigescu, S.P. Characterization of the High Frequency Performance of 28-nm UTBB FDSOI MOSFETs as a Function of Backgate Bias. In Proceedings of the IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), La Jolla, CA, USA, 19–22 October 2014; pp. 1–4. [Google Scholar]

- El Ghouli, S.; Scheer, P.; Minondo, M.; Juge, A.; Poiroux, T.; Sallese, J.M.; Lallement, C. Analog and RF modeling of FDSOI UTBB MOSFET using Leti-UTSOI model. In Proceedings of the MIXDES—23rd International Conference Mixed Design of Integrated Circuits and Systems, Lodz, Poland, 23–25 June 2016; pp. 41–46. [Google Scholar]

- Makovejev, S.; Kazemi Esfeh, B.; Barral, V.; Planes, N.; Haond, M.; Flandre, D.; Raskin, J.-P.; Kilchytska, V. Wide frequency band assessment of 28 nm FDSOI technology platform for analogue and RF applications. In Proceedings of the 15th International Conference on Ultimate Integration on Silicon (ULIS), Stockholm, Sweden, 7–9 April 2014; pp. 53–56. [Google Scholar]

- Lechevallier, J.; Struiksma, R.; Sherry, H.; Cathelin, A.; Klumperink, E.; Nauta, B. A forward-body-bias tuned 450 MHz Gm-C 3rd-order low-pass filter in 28 nm UTBB FD-SOI with >1 dBVp IIP3 over a 0.7-to-1 V supply. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 23–26 February 2015; pp. 1–3. [Google Scholar]

- Sourikopoulos, I.; Frappé, A.; Cathelin, A.; Clavier, L.; Kaiser, A. A digital delay line with coarse/fine tuning through gate/body biasing in 28 nm FDSOI. In Proceedings of the IEEE 42nd European Solid-State Circuits Conference, Lausanne, Switzerland, 12–15 September 2016; pp. 145–148. [Google Scholar]

- De Streel, G.; Stas, F.; Gurné, T.; Durant, F.; Frenkel, C.; Cathelin, A.; Bol, D. SleepTalker: A ULV 802.15.4a IR-UWB Transmitter SoC in 28-nm FDSOI Achieving 14 pJ/b at 27 Mb/s With Channel Selection Based on Adaptive FBB and Digitally Programmable Pulse Shaping. IEEE J. Solid-State Circuits 2017, 52, 1163–1177. [Google Scholar] [CrossRef]

- Finocchiaro, A.; Papotto, G.; Ragonese, E.; Palmisano, G. A 28-nm FD-SOI CMOS Variable-Gain Amplifier With Body-Bias-Based DC-Offset Cancellation for Automotive Radars. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 1693–1697. [Google Scholar] [CrossRef]

- Quemerais, T.; Gloria, D.; Golanski, D.; Bouvot, S. High-Q MOS Varactors for Millimeter-Wave Applications in CMOS 28-nm FDSOI. IEEE Electron. Dev. Lett. 2015, 36, 87–89. [Google Scholar] [CrossRef]

- Cao, C.; O, K.K. Millimeter-wave voltage-controlled oscillators in 0.13-/spl mu/m CMOS technology. IEEE J. Solid-State Circuits 2006, 41, 1297–1304. [Google Scholar] [CrossRef]

- Reiter, D.; Li, H.; Knapp, H.; Kammere, J.; Majied, S.; Sene, B.; Pohl, N. A Low Phase Noise, Wide Tuning Range 20GHz Magnetic-Coupled Hartley-VCO in a 28 nm CMOS Technology. In Proceedings of the IEEE Radio and Wireless Symposium (RWS), Orlando, FL, USA, 20–23 January 2019; pp. 1–3. [Google Scholar]

- Hu, Y.; Siriburanon, T.; Staszewski, R.B. A Low-Flicker-Noise 30-GHz Class-F23 Oscillator in 28-nm CMOS Using Implicit Resonance and Explicit Common-Mode Return Path. IEEE J. Solid-State Circuits 2018, 53, 1977–1987. [Google Scholar] [CrossRef] [Green Version]

- Vigilante, M.; Reynaert, P. A coupled-RTWO-based subharmonic receiver front-end for 5G E-Band backhaul links in 28 nm bulk CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 11–15 February 2018; pp. 412–414. [Google Scholar]

- Zhang, C.; Otto, M. A wide range 60 GHz VCO using back-gate controlled varactor in 22 nm FDSOI technology. In Proceedings of the IEEE International SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), San Francisco, CA, USA, 16–19 October 2017; pp. 1–3. [Google Scholar]

- Bai, J.; Lee, J.; Zhang, J.; Rohani, N. A 28-nm CMOS 40-GHz high-resolution digitally controlled oscillator for automotive radar applications. In Proceedings of the IEEE 17th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems (SiRF), Phoenix, AZ, USA, 15–18 January 2017; pp. 91–93. [Google Scholar]

- Mammei, E.; Monaco, E.; Mazzanti, A.; Svelto, F. A 33.6-to-46.2 GHz 32 nm CMOS VCO with 177.5 dBc/Hz minimum noise FOM using inductor splitting for tuning extension. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2013; pp. 350–351. [Google Scholar]

| Unit | This Work | RWS 2019 [16] | JSSC 2018 [17] | ISSCC 2018 [18] | SOI-3D 2017 [19] | SiRF 2017 [20] | ISSCC 2013 [21] | |

|---|---|---|---|---|---|---|---|---|

| Technology | 28 nm FD-SOI | 28 nm bulk | 28 nm bulk | 28 nm bulk | 22 nm FD-SOI | 28 nm bulk | 32 nm bulk | |

| Frequency | GHz | 40 | 18.7 | 29.3 | 18 | 60 | 40 | 40 |

| Tuning range | GHz | 3.5 | 2.2 | 3.9 | 3.7 | 21 | 3.6 | 12.6 |

| PN at 1 MHz | dBc/Hz | −94.3 | −113.8 | −106 | - | −84.3 | −99.5 (2) | - |

| PN at 10 MHz | dBc/Hz | −118 | −133 | - | −131.2 (3) | −108.6 | −115 (3) | −115.2/−118 |

| Supply voltage | V | 1.8 | 1.8 | 1 | 1.3 | 0.7 | 1 | 1 |

| Pwr consumption | mW | 18 | 90 | 12 | 82 (3) | 7.5 | 10.5 | 9.8 |

| FOM (1) | dBc/Hz | −177.5 | −179.7 | −184 | −176.7 | −175.8 | −176.7 | −177.3/−180 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Maiellaro, G.; Caruso, G.; Scaccianoce, S.; Giacomini, M.; Scuderi, A. 40 GHz VCO and Frequency Divider in 28 nm FD-SOI CMOS Technology for Automotive Radar Sensors. Electronics 2021, 10, 2114. https://doi.org/10.3390/electronics10172114

Maiellaro G, Caruso G, Scaccianoce S, Giacomini M, Scuderi A. 40 GHz VCO and Frequency Divider in 28 nm FD-SOI CMOS Technology for Automotive Radar Sensors. Electronics. 2021; 10(17):2114. https://doi.org/10.3390/electronics10172114

Chicago/Turabian StyleMaiellaro, Giorgio, Giovanni Caruso, Salvatore Scaccianoce, Mauro Giacomini, and Angelo Scuderi. 2021. "40 GHz VCO and Frequency Divider in 28 nm FD-SOI CMOS Technology for Automotive Radar Sensors" Electronics 10, no. 17: 2114. https://doi.org/10.3390/electronics10172114

APA StyleMaiellaro, G., Caruso, G., Scaccianoce, S., Giacomini, M., & Scuderi, A. (2021). 40 GHz VCO and Frequency Divider in 28 nm FD-SOI CMOS Technology for Automotive Radar Sensors. Electronics, 10(17), 2114. https://doi.org/10.3390/electronics10172114