Development of a Real-Time Magnetic Field Measurement System for Synchrotron Control

Abstract

:1. Introduction

2. Measurement Goals and Method

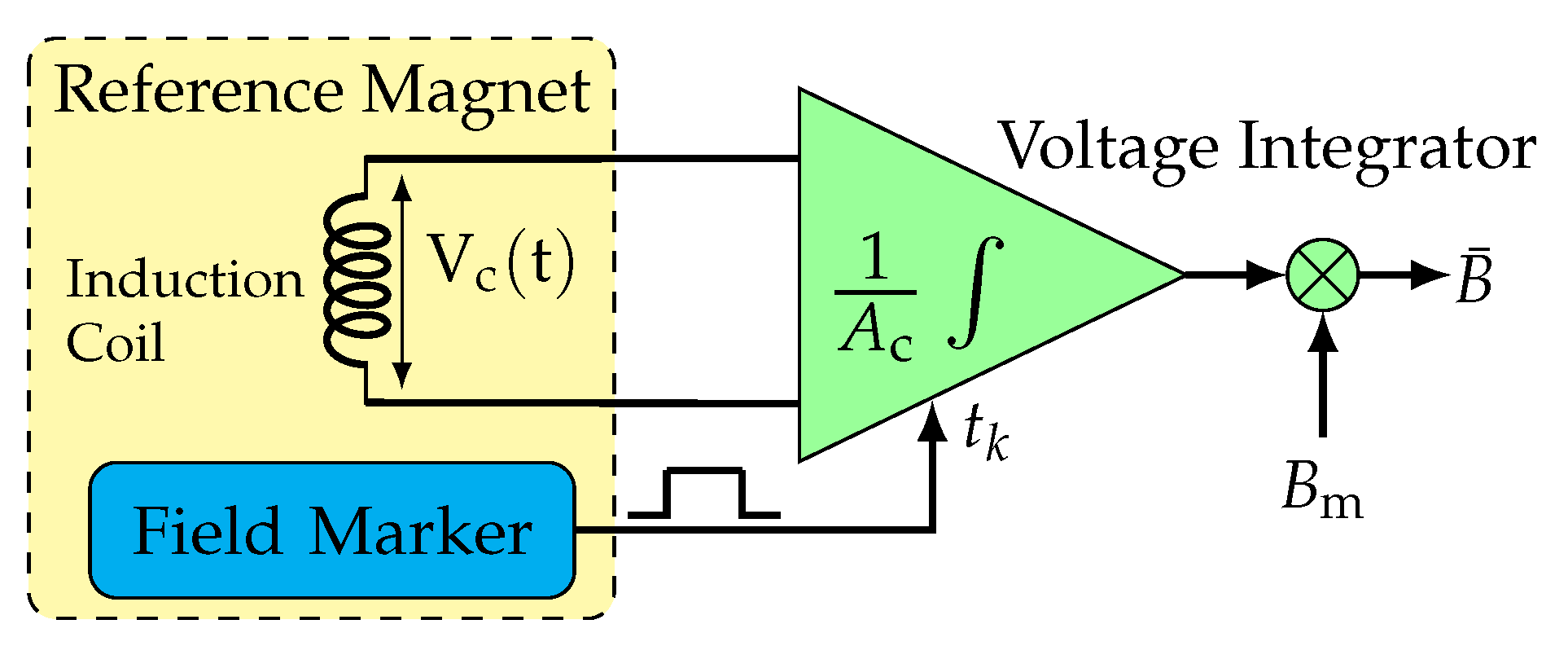

2.1. Measurement Model

2.2. Induction Coil

2.3. Field Marker

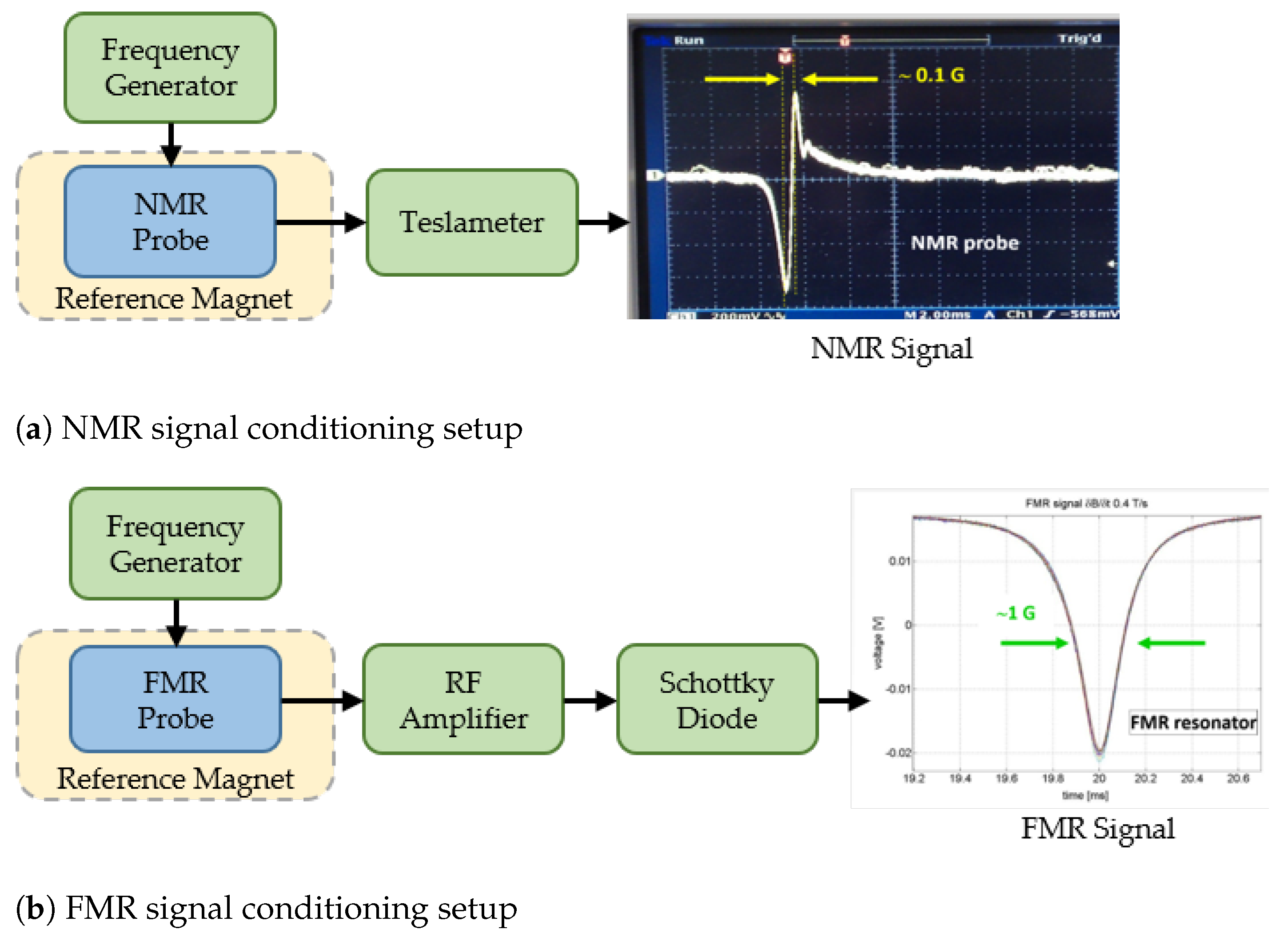

- The earliest solution is based on a commercially available instrument: the Nuclear Magnetic Resonance (NMR) teslameter Metrolab PT2025 [17,21,22]. The probe contains a cylindrical sample with a volume of 226 made of a hydrogen-rich substance, water or rubber, where resonance is induced in the hydrogen nuclei based on the gyromagnetic ratio of the proton, = 42.57747892(29) MHz/T. This instrument represents a reference standard in magnetometry, as it provides the modulus of the magnetic field with an absolute accuracy of about 5 ppm provided that the field is sufficiently uniform (tolerated relative gradient ) and stable. NMR probes have been used with success as markers in the PSB and SPS systems since the 1980s. In FIRESTORM, a stable excitation frequency is provided by an Aim-TTi Function/Pulse Generator [23], while the teslameter unit demodulates the probe’s RF output to obtain its amplitude envelope. Figure 4 depicts the output waveform from the teslameter, with the resonance point defined as the first negative peak [22]. Typically, the peak-to-peak amplitude of the signal ranges from 50 up to 1 , depending on probe type, field uniformity and field ramp rate. The measurement range covers magnetic field levels from 50 to well above 10 , with field ramp rates up to /. The effective reproducibility in operation, as derived from jitter measurements at a given field ramp rate under reproducible cycling conditions, is of the order of 5 .

- The most recent design is represented by Ferrimagnetic Resonance (FMR) devices, based on ⌀ Yittrium–Iron–Garnet (YIG) ferrite spheres (for a volume of ) as the resonating element [20]. FMR is a form of Electron Paramagnetic Resonance, implying that the precession frequency is three orders of magnitude higher than NMR, about 28 /. YIG has a narrow resonance peak even at field ramp-rates as high as 5 /, with typical quality factors ranging in the hundreds. Another advantage of FMR lies in the small size of the YIG sphere, which makes the resonator compatible with high-gradient fields such as those found in the PS combined-function magnets, where the poles are shaped to add a quadrupole field component with a relative gradient = −1 [24]. A prototype system based on a commercially available RF filter has been installed there since 2012, and a series of tests have shown that the resonance peak remains well defined for absolute gradients up to 12 /. On the downside, the anisotropy of conventional mono-crystalline YIG introduces a degree of dependence upon temperature and field direction, with equivalent errors up to 40 / and 20 /, respectively. These errors can be reduced by careful mechanical alignment of the YIG sphere and by thermalization of the resonator. Further reduction could be achieved using paramagnetic materials [25], which, however, have a lower Signal-to-Noise ratio. For FIRESTORM, lumped-element and waveguide resonators have been developed in-house and are now being implemented. The existing resonators cover a measurement range from 36 to 110 . Overall, the effective reproducibility of the marked field can be as low as 1 under optimal conditions [7]. Prototypes of single-chip integrated microwave oscillators [25] working up to 700 are currently being tested; such higher field levels, however, correspond to a frequency range about 20 , which requires complex electronics for the detection.

2.4. Field Marker Calibration

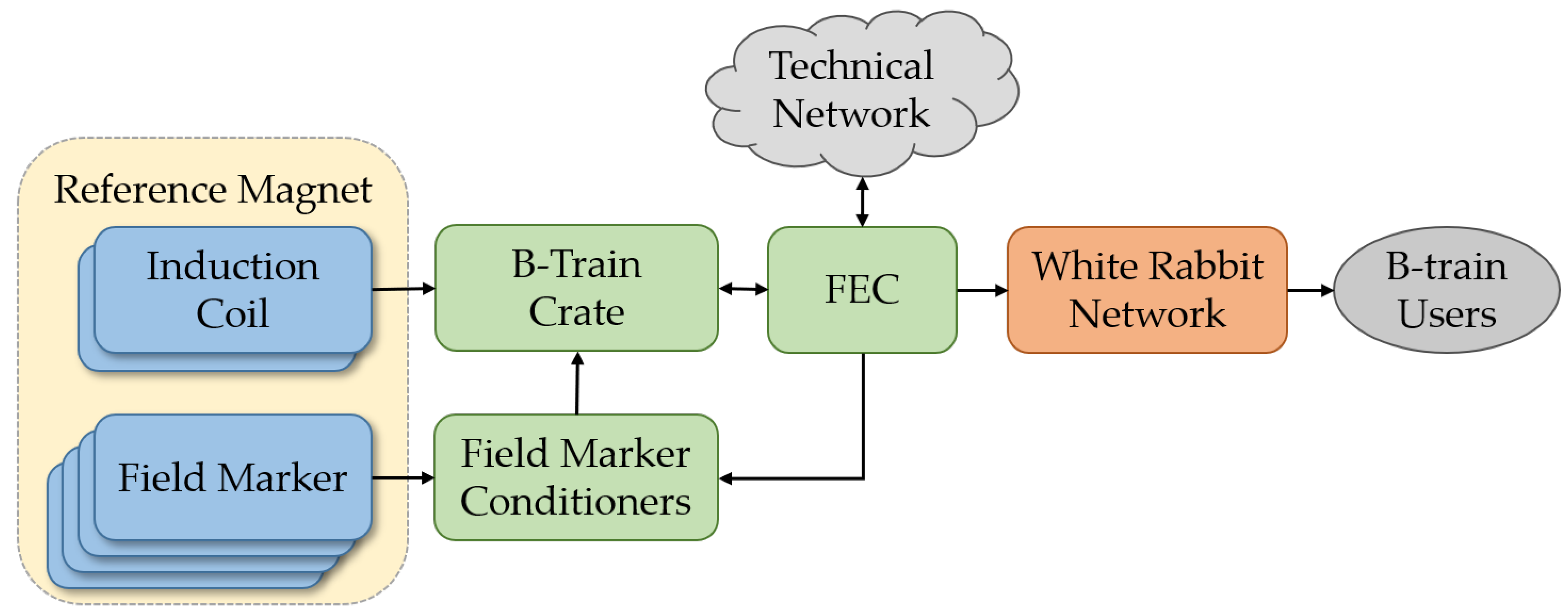

3. Hardware Architecture of the FIRESTORM System

3.1. Front End Computer and Software

3.2. SPEC—Simple PCIe Carriers

3.3. FMC—FPGA Mezzanine Cards

3.4. B-Train Crate

4. Functional SPEC Modules

4.1. Central Timing Receiver

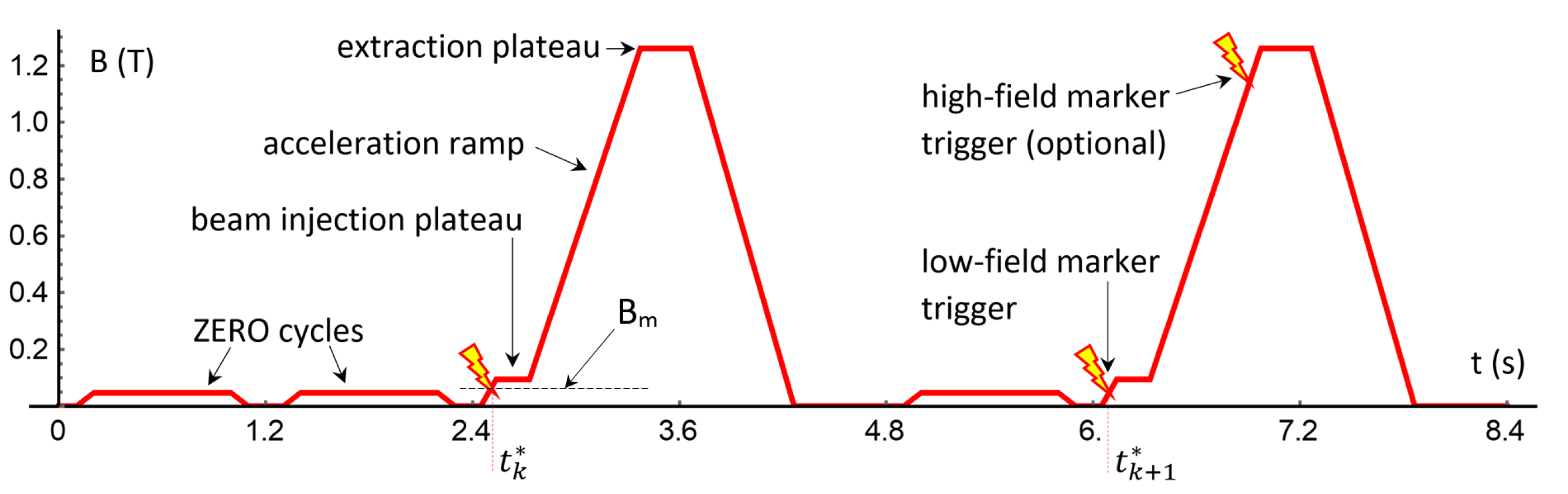

- the “C0” trigger, which signals the start of a new accelerator cycle and is used as an internal reference for various time-related functions, such as the integrator calibration procedures and the field marker gating function described below. Optionally, C0 can be used to enforce a restart of the flux integration process to a given preset value. This is useful, for example, when a field marker malfunction is suspected.

- the “ZERO” cycle trigger, which signals the start of special cycles where no beam is circulating, and the magnet excitation current is kept at a low (or zero) level. ZERO cycles are run from time to time in some (but not all) of CERN synchrotrons, either as low-power fillers in the machine schedule or to allow capacitive-discharge magnet power supplies time to recharge. Whenever available, ZERO cycles are used for self-calibration of the integrators, as described in Section 4.3.

4.2. Field Marker Trigger Generator Module

4.2.1. Field Marker FMC

4.2.2. Peak Detection Algorithm

4.3. B-Train Integrator Module

4.3.1. Integrator FMC

- A three-way selection switch with a 200 settling time for the auto-calibrating function, as explained below.

- An input buffer with a 27 bandwidth and a = impedance. The impedance stems from a compromise between the need to limit signal attenuation for high-resistance input loads and the need to limit the offset voltages arising due to input bias currents. For a typical measurement coil resistance on the order of = , the low-frequency attenuation can be easily calculated from and corrected in the post-processing stage. As the specified input signal bandwidth is just 100 , a more rigorous dynamic study of the parasitic capacitive effects was not considered a priority at this stage.

- A two-stage pre-amplifier that scales the nominal induction coil signal to the differential input range of the ADC. First, a voltage divider realized with high-precision discrete resistors attenuates the signal by a factor of ; then, a fully differential funnel amplifier AD8475 with the attenuation factor is and nominal passband 15 prepares the signal for the ADC while ensuring that the total attenuation factor is .

- An AD5291 digital potentiometer providing a programmable voltage source with 1 range and about 1 resolution, injected between the two attenuation stages and used for fine offset compensation.

- A simple first-order RC anti-aliasing filter with a 1 cutoff frequency, which gives a nominal 100 ppm maximum error at the upper end of the 100 signal bandwidth.

4.3.2. Integration Algorithm

4.3.3. Drift Correction

4.3.4. Gain Correction

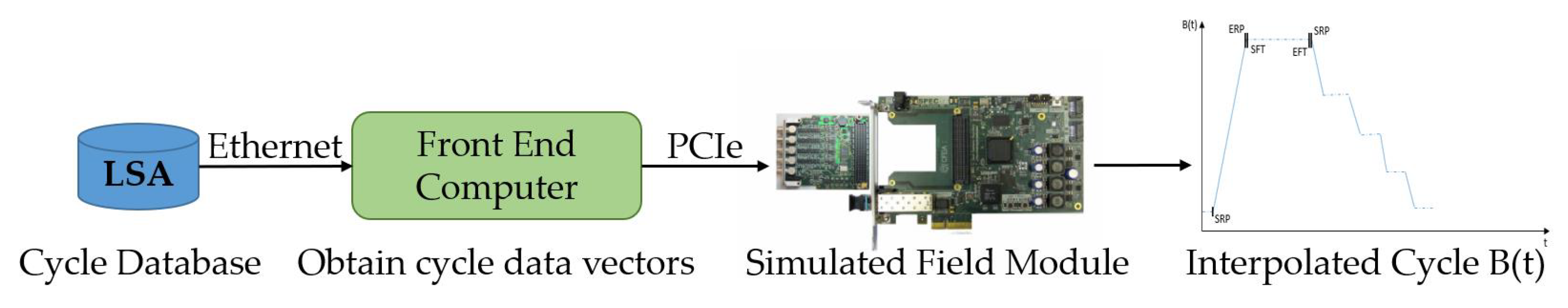

4.4. Simulated Field Module

- As a normal part of the accelerator restart sequence, when the accelerating RF cavity control system needs a realistic value of the field to be input via the B-train for its own frequency program, even when no beam is circulating yet and the magnets are not powered.

- Under certain special circumstances, when the magnetic field measurement feedback is not the best option. For instance, machine operators may want to replace the measured field temporarily with the simulated one as a beam diagnostic tool. As another example, in the case of a power converter trip, the value fed back to the RF cavities must switch automatically from the measured to the simulated field in order to avoid large, potentially harmful discontinuities. Even more crucially, in the specific case of the AD, the simulated field is always preferred because the machine is magnetically very reproducible, and the RF system is adversely affected by the noise inherent in the measured field.

4.4.1. Vector Cycle Representation

4.4.2. Magnetic Cycle Interpolation

4.4.3. Simulated/Predicted/WR FMC

4.5. Predicted Field Module

FMC

4.6. White Rabbit Module

- A 16-bit frame control header, consisting of an 8-bit frame type ID and various status and error flag bits, essential for remote diagnostics and calibration. In particular, there is a flag bit that signals if the current cycle is a ZERO cycle; and two additional flag bits, which are set to 1 to indicate the reception, respectively, of the C0 (cycle start) and field marker trigger pulses. Since the pulses have a nominal width of 1 , each one of these two flags will normally be set on 250 consecutive frames.

- The first part of the payload, comprising two 32-bit slots for the active and values. The active version of the magnetic field is selected among the four possibilities and is positioned in the first slot to ensure that all users read by default the same value. In signed fixed-point representation, the distributed field has a resolution ( 1 LSB) of 10 and a range of , which is more than enough for all foreseeable applications. The second slot contains the numerical time derivative of the first one, with a resolution of 1 / and a range of /, also exceeding all foreseeable demands.

- The second part of the payload, which includes four 32-bit slots for the measured, legacy, simulated and predicted field, with the same resolution as the active field slot. Repetition of the active field slot implies a redundancy of 4 bytes in the payload, which has negligible impact; in return, this guarantees that all users and diagnostic tools may conveniently access at any time the four versions of the field, at fixed slots within the frame.

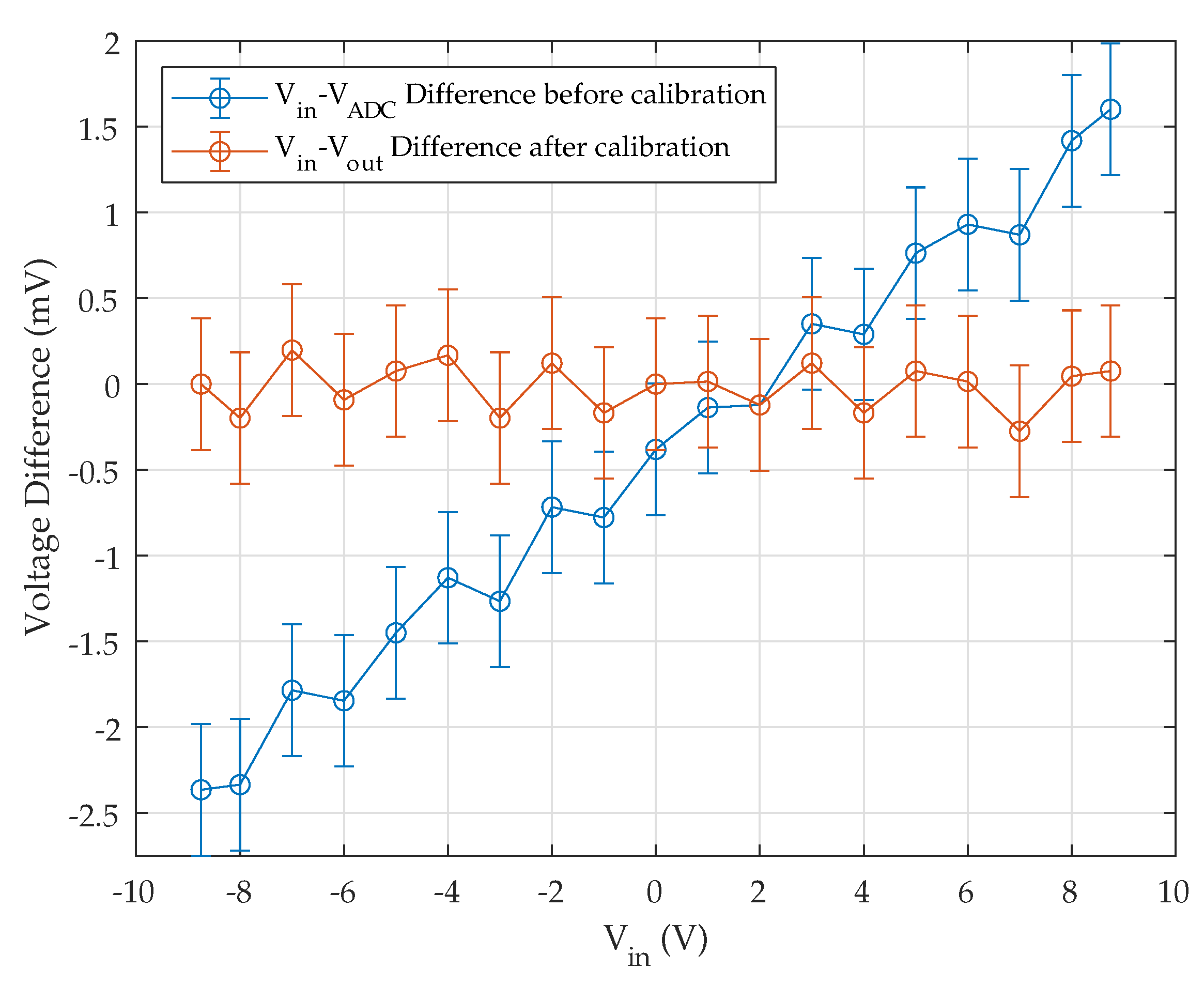

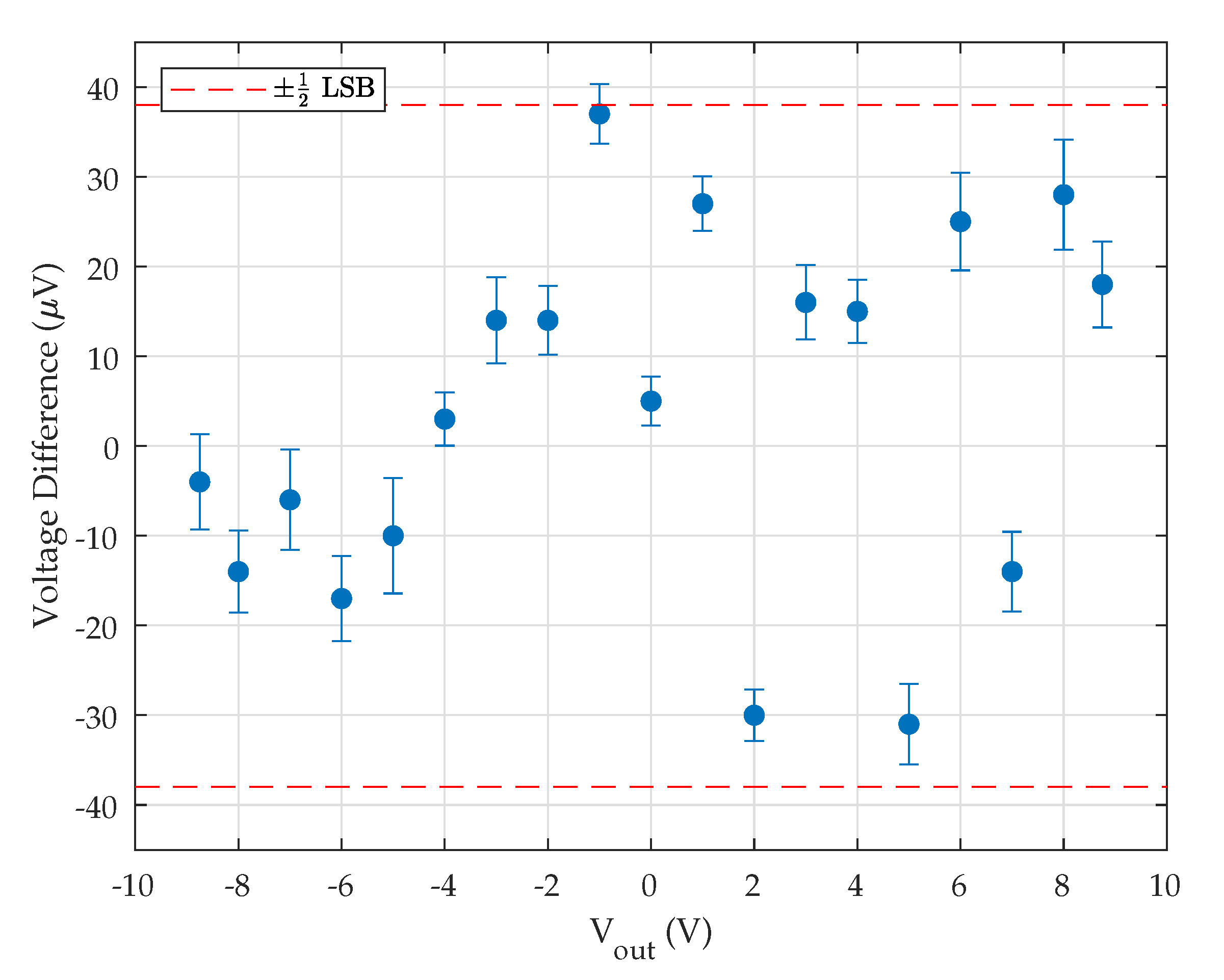

5. DC Performance

5.1. Voltage Measurement

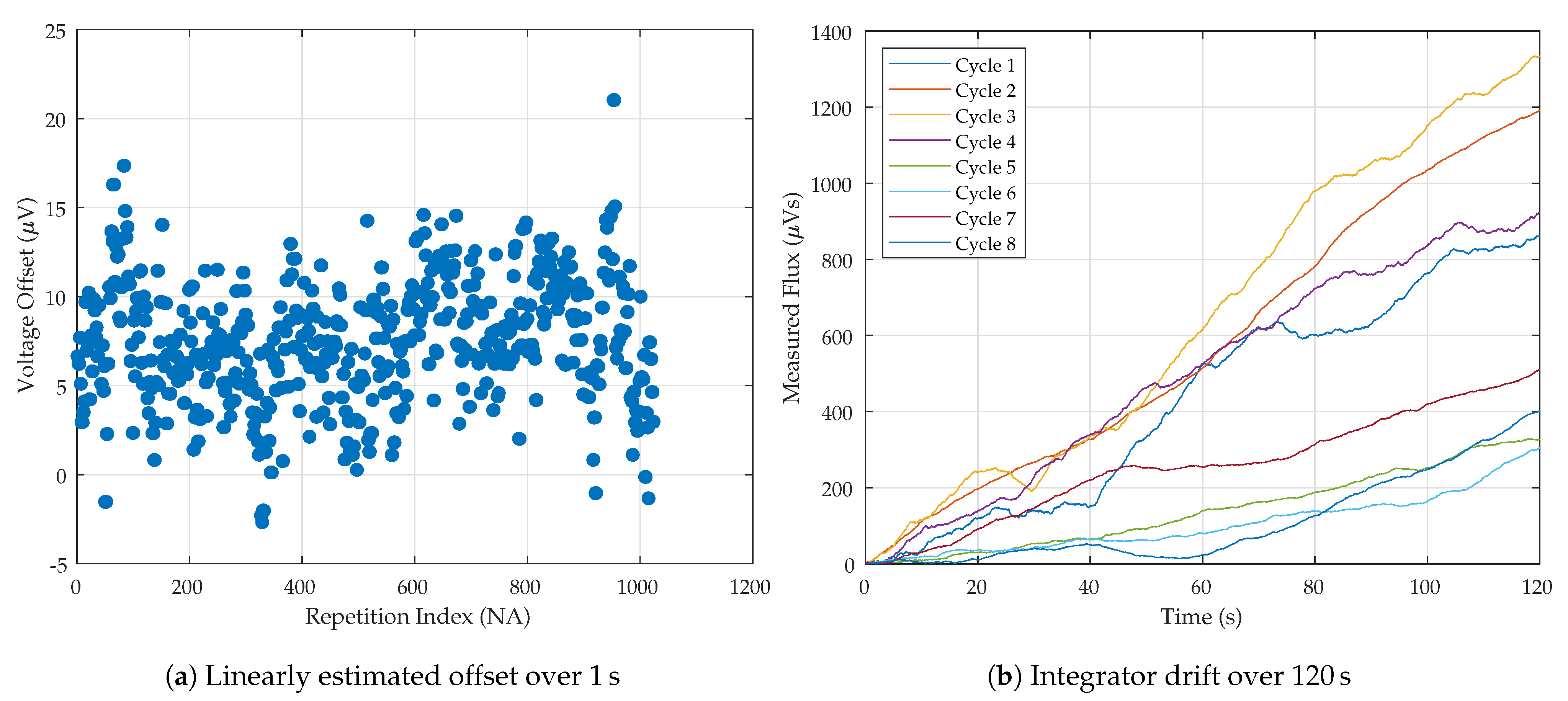

5.2. Flux Measurement

5.3. Integrator Drift

6. Dynamic Performance

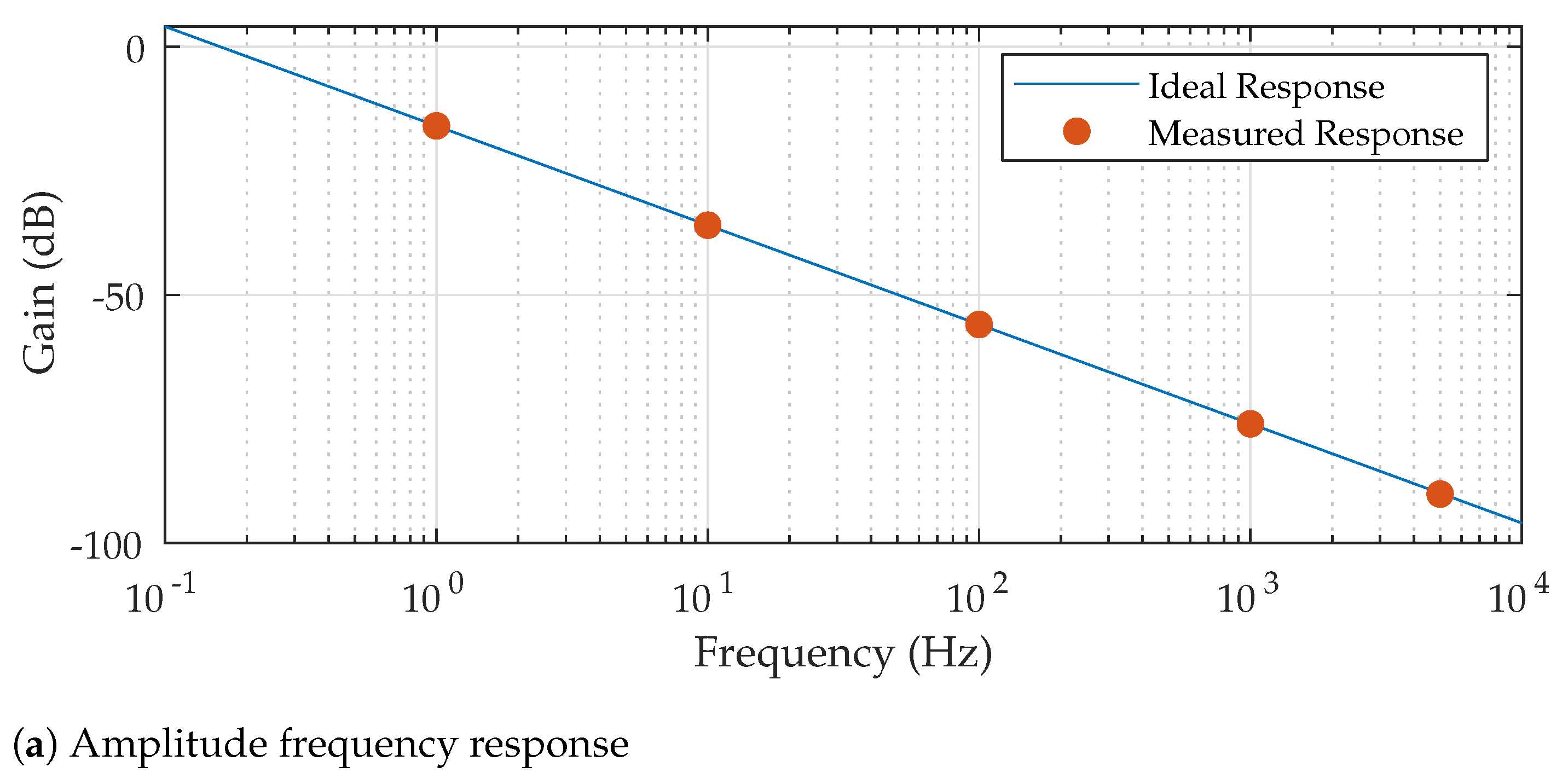

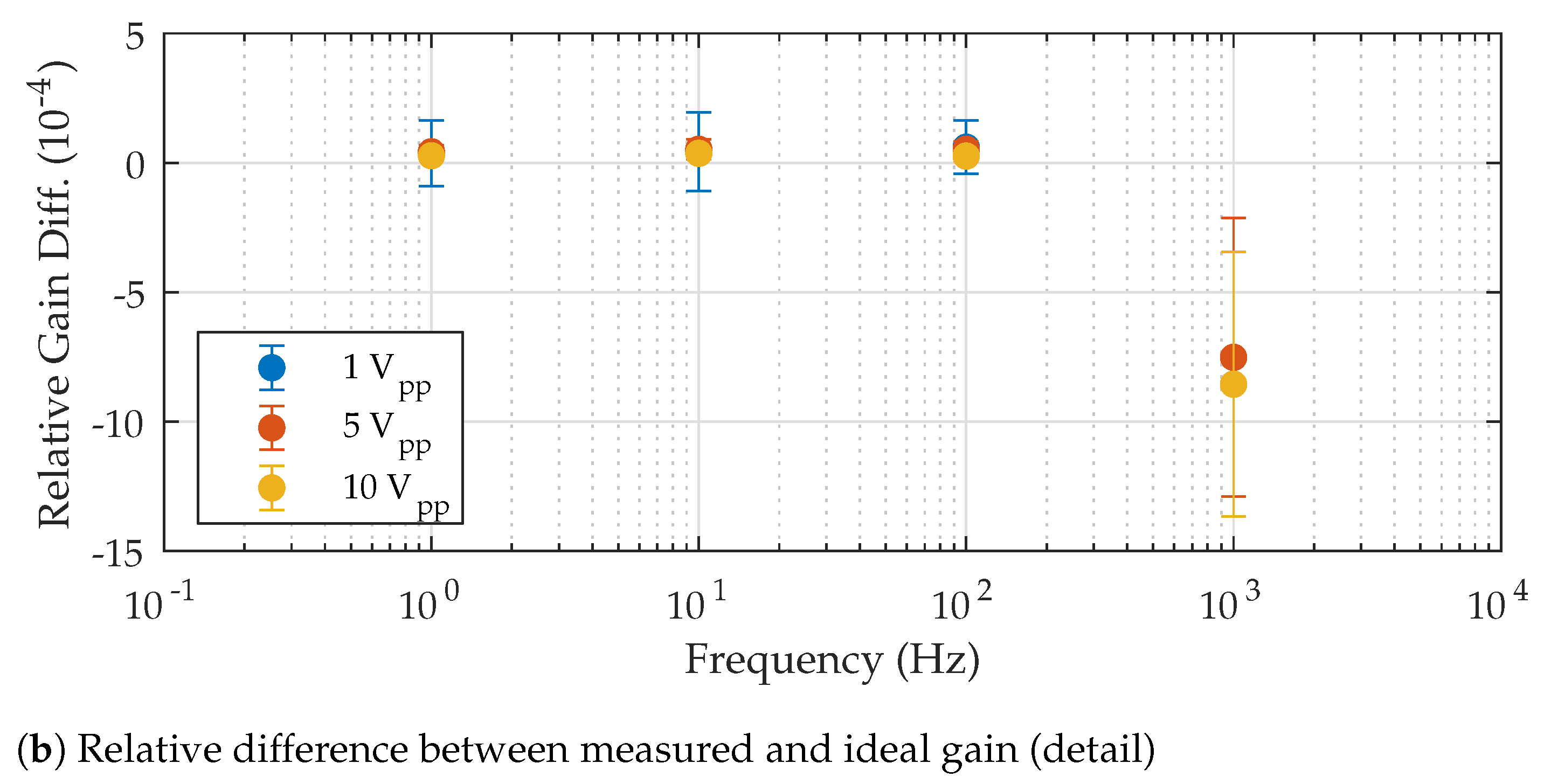

6.1. AC Amplitude Transfer Function

6.2. Latency Measurements

- The overall mean propagation delay, () at , was obtained from the time difference between C0 and a TTL trigger pulse emitted by the WR receiver as soon as it detected the field step change. The full statistics are reported in Table 3. This result is the most important, as it qualifies the whole acquisition chain. The accuracy of a single measurement is dominated by the frame period length in the WR stream, but due to the high number of repetitions, the uncertainty of the mean is as low as .

- The WR delay from transmitter to receiver was measured as the time difference between C0 and a second TTL trigger pulse emitted by the WR receiver. For this, we injected C0 directly in the WR module via one of the two DIO connections available. There, the WR core set to 1 the start cycle flag in the header of the frames transmitted throughout the duration of the pulse. At the other end, the WR receiver generated a pulse upon arrival of the first active flag. The average delay thus measured is @ (Table 3). The setup included a total fibre length of about 5 , which adds a negligible delay, taking into account a typical propagation speed of 5 /.

- The WR delay was also cross-checked by subtracting the high-resolution, GPS- synchronized timestamps injected in every frame by the WR transmitter from the timestamp available at the receiver end. Again, the specific frame used was the first one to have its field marker flag set in the Frame Control header, thereby representing the rising edge of the field marker trigger pulse. The result obtained with this method is @ (Table 4), which is significantly lower than the previous result. This difference can be ascribed to the functional sequence of the operations executed in the modules since timestamping is the last one before transmission and the first one upon reception. The uncertainty of each single timestamp difference is equal to the WR frame period, i.e., 4 .

- The delay due to the WR switch alone, i.e., @ , was measured by repeating the previous test while bypassing the switch.

- The details of the propagation through the FEC were measured by a different method based on generating an analog output image of the integrated field via the DAC built in the FMCs of the Integrator, the Simulated Field and the WR modules. (Since the Simulated Field module is by far the least computationally intensive of the three, its latency is very low, and the relative results were unstable, which is the reason why they are not reported here). The mean delays in the Integrator alone and in the whole chain up to the WR module are and , respectively, with a single-take uncertainty of 1 due to the sampling rate of the DAC.

Discussion

7. Summary and Outlook

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Bryant, P.; Johnsen, K. The Principles of Circular Accelerators and Storage Rings; Cambridge University Press: Cambridge, UK, 2005. [Google Scholar]

- Buzio, M.; Galbraith, P.; Gilardoni, S.; Giloteaux, D.; Golluccio, G.; Petrone, C.; Walckiers, L. Development of Upgraded Magnetic Instrumentation for CERN’s Real-time Reference Field Measurement Systems. In Proceedings of the 1st International Particle Accelerator Conference (IPAC’10), Kyoto, Japan, 23–28 May 2010; JACoW: Geneva, Switzerland, 2010; pp. 310–312. [Google Scholar]

- Franzini, G.; Coiro, O.; Pellegrini, D.; Serio, M.; Stella, A.; Pezzetta, M.; Pullia, M. Final Design and Features of the B-train System of CNAO. In Proceedings of the 1st International Particle Accelerator Conference (IPAC’10), Kyoto, Japan, 23–28 May 2010; JACoW: Geneva, Switzerland, 2010; pp. 2878–2880. [Google Scholar]

- Fraboulet, P.; Ambrosch, K.; Cesaris, I.D.; Beuret, A. The Current and Field Regulation System of the MedAustron Ion-Beam Accelerator. In Proceedings of the 39th Annual Conference of the IEEE Industrial Electronics Society (IECON 2013), Vienna, Austria, 10–13 November 2013; pp. 7103–7108. [Google Scholar] [CrossRef]

- Feldmeier, E.; Haberer, T.; Pters, A.; Schoemers, C.; Steiner, R. Magnetic Field Correction in Normal Conducting Synchrotrons. In Proceedings of the 1st International Particle Accelerator Conference (IPAC’10), Kyoto, Japan, 23–28 May 2010; JACoW: Geneva, Switzerland, 2010; pp. 675–677. [Google Scholar]

- Hanke, K.; Coupard, J.; Damerau, H.; Funken, A.; Goddard, B.; Lombardi, A.; Manglunki, D.; Mataguez, S.; Meddahi, M.; Mikulec, B.; et al. The LHC Injectors Upgrade (LIU) Project at CERN: Proton Injector Chain. In Proceedings of the 8th International Particle Accelerator Conference (IPAC’17), Copenhagen, Denmark, 14–19 May 2017; JACoW: Geneva, Switzerland, 2017; pp. 3335–3338. [Google Scholar] [CrossRef]

- Grech, C.; Amodeo, M.; Beaumont, A.; Buzio, M.; Di Capua, V.; Giloteaux, D.; Sammut, N.; Vella Wallbank, J. Error characterization and calibration of real-time magnetic field measurement systems. Nucl. Instrum. Methods Phys. Res. Sect. A Accel. Spectrom. Detect. Assoc. Equip. 2021, 990, 164979. [Google Scholar] [CrossRef]

- Burnet, J.P.; Giovannozzi, M.; Métral, E.; Michels, O.; Steerenberg, R.; Vandorpe, B. CERN Proton Synchrotron working point control using an improved version of the pole-face-windings and figure-of-eight loop powering. In Proceedings of the 10th European Particle Accelerator Conference (EPAC 2006), Edinburgh, UK, 26–30 June 2006; JACoW: Geneva, Switzerland, 2006; pp. 264–266. [Google Scholar]

- Benedikt, M.; Caspers, F.; Lindroos, M. Application of magnetic markers for precise measurement of magnetic fields in ramped accelerators. Part. Accel. 1999, 63, 57–73. [Google Scholar]

- Buzio, M. Fabrication and calibration of search coils. In Proceedings of the 2009 CAS-CERN Accelerator School: Specialised Course on Magnets, Bruges, Belgium, 16–25 June 2009; CERN: Geneva, Switzerland, 2009; pp. 387–421. [Google Scholar]

- Seo, S.H.; Werner, A.; Marquardt, M. Development of a digital integrator for the KSTAR device. Rev. Sci. Instrum. 2010, 81, 123507. [Google Scholar] [CrossRef] [PubMed]

- Feldmeier, E.; Haberer, T. Development of a High Precision Integrator for Analog Signals to Measure Magnetic Fields in Real-time. In Proceedings of the 4th International Particle Accelerator Conference (IPAC’13), Shanghai, China, 12–17 May 2013; JACoW: Geneva, Switzerland, 2013; pp. 661–663. [Google Scholar]

- Walckiers, L. Magnetic measurement with coils and wires. In Proceedings of the 2009 CAS-CERN Accelerator School: Specialised Course on Magnets, Bruges, Belgium, 16–25 June 2009; CERN: Geneva, Switzerland, 2009; pp. 357–385. [Google Scholar] [CrossRef]

- Grech, C.; Buzio, M.; Sammut, N. A Magnetic Measurement Model for Real-Time Control of Synchrotrons. IEEE Trans. Instrum. Meas. 2019, 69, 393–400. [Google Scholar] [CrossRef] [Green Version]

- Hancock, S. A Fit-Based Frequency Programme for the PS; Technical Report CERN-AB-Note-2007-036; CERN: Geneva, Switzerland, 2007. [Google Scholar]

- Pezzetta, M.; Bazzano, G.; Bressi, E.; Falbo, L.; Pullia, M.; Priano, C.; Coiro, O.; Franzini, G.; Pellegrini, D.; Serio, M.; et al. B-train Performances at CNAO. In Proceedings of the 2nd International Particle Accelerator Conference (IPAC’11), San Sebastian, Spain, 4–9 September 2011; JACoW: Geneva, Switzerland, 2011; pp. 568–570. [Google Scholar]

- Beaumont, A. NMR Magnetic Field Markers of the B-Train for the Proton Synchrotron Accelerator. Master’s Thesis, UTBM, Belfort, France, 2009. [Google Scholar]

- Benedikt, M.; Caspers, F.; Salvermoser, T. Absolute Calibration of the CERN PS-Booster Bending Field with Beam and NMR; Techreport PS-OP-Note-98-23; CERN: Geneva, Switzerland, 1998. [Google Scholar]

- Di Cesare, P.; Reymond, C.; Rottstock, H.; Sommer, P. SPS Magnetic Field Cycle Measurement System: Investigation on Nuclear Magnetic Resonnance (NMR) System to Get a Faster Reading of Field Values; Techreport CERN-SPS-PCO-Note 89-9; CERN: Geneva, Switzerland, 1989. [Google Scholar]

- Beaumont, A.; Buzio, M.; Boero, G. Ferrimagnetic Resonance Field Sensors for Particle Accelerators. Rev. Sci. Instrum. 2019, 90, 065005. [Google Scholar] [CrossRef] [PubMed]

- METROLAB. PT2025 NMR Teslameter User Manual, 2nd ed.; METROLAB Instruments SA: Geneva, Switzerland, 2003. [Google Scholar]

- Grech, C.; Beaumont, A.; Buzio, M.; Sammut, N. Performance comparison of Nuclear Magnetic Resonance and FerriMagnetic Resonance field markers for the control of low-energy Synchrotrons. J. Phys. Conf. Ser. 2018, 1065, 052022. [Google Scholar] [CrossRef]

- AimTTi. Aim-TTi TF930, 8th ed.; AIM & Thandar Thurlby Instruments: Cambridgeshire, UK; Available online: https://resources.aimtti.com/manuals/TF930_Instruction_Manual-English-Iss8.pdf (accessed on 8 July 2020).

- Gilardoni, S.; Manglunki, D.E. Fifty Years of the CERN Proton Synchrotron: Volume 1; Techreport CERN-2011-004; CERN: Geneva, Switzerland, 2011. [Google Scholar]

- Beaumont, A.; Giloteaux, D.; Matheoud, A.V.; Buzio, M.; Boero, G. Electron paramagnetic resonance magnetic field sensors for particle accelerators. Rev. Sci. Instrum. 2020, 91, 105001. [Google Scholar] [CrossRef] [PubMed]

- Open Hardware Repository. Available online: https://ohwr.org/ (accessed on 8 July 2020).

- Loschmidt, P.; Gaderer, G.; Simanic, N.; Hussain, A.; Moreira, P. White rabbit—Sensor/actuator protocol for the CERN LHC particle accelerator. In Proceedings of the 8th Annual IEEE Conference on Sensors (IEEE Sensors 2009), Christchurch, New Zealand, 25–28 October 2009; pp. 781–786. [Google Scholar] [CrossRef]

- Jansweijer, P.; Peek, H.; de Wolf, E. White Rabbit: Sub-nanosecond timing over Ethernet. Nucl. Instrum. Methods Phys. Res. A 2013, 725, 187–190. [Google Scholar] [CrossRef]

- Siemens. SIMATIC IPC847E, 1st ed.; A5E43920357-AA; Siemens AG: Nurnberg, Germany, 2018. [Google Scholar]

- About CentOS. Available online: https://centos.org/about/ (accessed on 8 July 2020).

- Arruat, M.; Fernandez, L.; Jackson, S.; Locci, F.; Nougaret, J.L.; Peryt, M.; Radeva, A.; Sobczak, M.; Vanden Eynden, M. Front-End Software Architecture. In Proceedings of the 11th International Conference on Accelerator and Large Experimental Physics Control Systems (ICALEPCS07), Knoxville, TN, USA, 15–19 October 2007; JACoW: Geneva, Switzerland, 2007; pp. 310–312. [Google Scholar]

- Alvarez-Sanchez, P.; Bau, J.C.; Domínguez, D.; Lewis, J.; Serrano, J. The Evolution of the CERN SPS Timing System for the LHC Era. In Proceedings of the 9th International Conference on Accelerator and Large Experimental Physics Control Systems (ICALEPCS2003), Gyeongju, Korea, 13–17 October 2003; JACoW: Geneva, Switzerland, 2003; pp. 125–127. [Google Scholar]

- Simple PCIe FMC Carrier (SPEC). Available online: https://www.ohwr.org/project/spec/wikis/home (accessed on 8 July 2020).

- Xilinx. Spartan 6 FPGA. Xilinx. 2011. Available online: https://www.xilinx.com/support/documentation/data_sheets/ds160.pdf (accessed on 8 July 2020).

- WISHBONE. Revision B.4 Specification, OpenCores. Available online: https://cdn.opencores.org/downloads/wbspec_b4.pdf (accessed on 8 July 2020).

- Wishbone Slave Generator. Wishbone Tool Developed by OHWR. Available online: https://ohwr.org/project/wishbone-gen/ (accessed on 8 July 2020).

- VITA. FPGA Mezzanine Card (FMC) Standard; Approved in 2008, Revised in 2010; VMEbus Internationa Trade Association: Fountain Hills, AZ, USA, 2008. [Google Scholar]

- Bojtar, L. OASIS User Manual. 2009. Available online: https://cds.cern.ch/record/1164782 (accessed on 8 July 2020).

- Alvarez, P. CTR User Guide; Technical Report; CERN: Geneva, Switzerland, 2007. [Google Scholar]

- Amodeo, M.; Arpaia, P.; Buzio, M. Integrator Drift Compensation of Magnetic Flux Transducers by Feed-Forward Correction. Sensors 2019, 19, 5455. [Google Scholar] [CrossRef] [Green Version]

- Arpaia, P.; Bottura, L.; Fiscarelli, L.; Walckiers, L. Performance of a fast digital integrator in on-field magnetic measurements for particle accelerators. Rev. Sci. Instrum. 2012, 83, 024702. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Keysight. Agilent Technologies 34401A Digital Multimeter Manual, 10th ed.; Keysight Technologies: Santa Rosa, CA, USA, 2014; Available online: https://www.keysight.com/zz/en/assets/9018-01063/user-manuals/9018-01063.pdf (accessed on 8 July 2020).

- Jacquet, D.; Gorbonosov, R.; Kruk, G. LSA—The High Level Application Software of the LHC—And Its Performance During the First Three Years of Operation. In Proceedings of the 14th International Conference on Accelerator and Large Experimental Physics Control Systems (ICALEPCS 2013), San Francisco, CA, USA, 6–11 October 2013; JACoW: Geneva, Switzerland, 2013; pp. 1201–1204. [Google Scholar]

- Argyropoulos, T.; Bohl, T.; Lasheen, A.; Papotti, G.; Quartullo, D.; Shaposhnikova, E. Momentum slip-stacking in CERN SPS for the ion beams. In Proceedings of the 10th International Particle Accelerator Conference (IPAC’19), Melbourne, Australia, 19–24 May 2019; JACoW: Geneva, Switzerland, 2019; pp. 3184–3187. [Google Scholar] [CrossRef]

- Todesco, E.; Aquilina, N.; Auchmann, B.; Bottura, L.; Buzio, M.; Chritin, R.; Deferne, G.; Deniau, L.; Fiscarelli, L.; Hagen, P.; et al. The Magnetic Model of the LHC in the Early Phase of Beam Commissioning; Technical Report CERN-ATS-2010-154; CERN: Geneva, Switzerland, 2010. [Google Scholar]

- Caspers, F.; Heinze, W.; Lewis, J.; Lindroos, M.; Salvermoser, T. An Alternative to Classical Real-time Magnetic Field Measurements using a Magnet Model. In Proceedings of the 6th International Conference on Accelerator and Large Experimental Physics Control Systems (ICALEPCS’97), Beijing, China, 3–7 November 1997; CERN: Geneva, Switzerland, 1997; pp. 581–584. [Google Scholar]

- Grech, C.; Buzio, M.; Pentella, M.; Sammut, N. Dynamic Ferromagnetic Hysteresis Modelling Using a Preisach-Recurrent Neural Network Model. Materials 2020, 13, 2561. [Google Scholar] [CrossRef]

- Perrelet, D.; Brischetto, Y.; Damerau, H.; Oberson, D.; Sundal, M.; Villanueva, A. White-Rabbit Based Revolution Frequency Program for the Longitudinal Beam Control of the CERN PS. In Proceedings of the 15th International Conference on Accelerator and Large Experimental Physics Control Systems (ICALEPCS 2015), Melbourne, Australia, 17–23 October 2015; JACoW: Geneva, Switzerland, 2015; pp. 286–290. [Google Scholar] [CrossRef]

- Lipinski, M.M. BTrain-over-WhiteRabbit Wiki. Available online: https://gitlab.cern.ch/BTrain-TEAM/Btrain-over-WhiteRabbit/wikis/home (accessed on 8 July 2020).

- Analogic. Data Precision 8200 User Manual. Available online: https://testequipment.center/Product_Documents/Data-Precision-8200-Specifications-0E813.pdf (accessed on 8 July 2020).

- Arpaia, P.; Di Capua, V.; Roda, M.; Buzio, M. Real-Time Magnetic Measurement Monitoring under cRIO-LabVIEW Based Platform; EasyChair Preprint No. 1335; EasyChair: Manchester, UK, 2019. [Google Scholar]

| Calibration Method | (V) | (ppm) |

|---|---|---|

| In-built Correction | 381 | 221 |

| Manual Linear Least-Squares Fit | 423 | 220 |

| Integration Period (s) | Mean (V) | (V) |

|---|---|---|

| 1 | 7.7 | 3.5 |

| 120 | 6.5 | 3.6 |

| Input to Output at 250 kHz (s) | Transmission at 250 kHz (s) | Input to Output at 100 kHz (s) | Transmission at 100 kHz (s) | |

|---|---|---|---|---|

| Average | 19.5 | 7.3 | 22.6 | 8.3 |

| Minimum | 15.6 | 4.9 | 15.7 | 5.0 |

| Maximum | 23.8 | 9.9 | 29.7 | 11.7 |

| 2.3 | 1.2 | 3.6 | 1.9 |

| Without Switch (s) | With Switch (s) | |

|---|---|---|

| Average | 1.53 | 3.93 |

| Minimum | 1.52 | 3.86 |

| Maximum | 4.32 | 7.2 |

| 0.13 | 0.13 |

| to Integrator DAC (s) | to WR DAC (s) | |

|---|---|---|

| Average | 4.4 | 10.9 |

| Minimum | 1.8 | 8.4 |

| Maximum | 6.8 | 13.3 |

| 1.2 | 1.7 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Vella Wallbank, J.; Amodeo, M.; Beaumont, A.; Buzio, M.; Di Capua, V.; Grech, C.; Sammut, N.; Giloteaux, D. Development of a Real-Time Magnetic Field Measurement System for Synchrotron Control. Electronics 2021, 10, 2140. https://doi.org/10.3390/electronics10172140

Vella Wallbank J, Amodeo M, Beaumont A, Buzio M, Di Capua V, Grech C, Sammut N, Giloteaux D. Development of a Real-Time Magnetic Field Measurement System for Synchrotron Control. Electronics. 2021; 10(17):2140. https://doi.org/10.3390/electronics10172140

Chicago/Turabian StyleVella Wallbank, Joseph, Maria Amodeo, Anthony Beaumont, Marco Buzio, Vincenzo Di Capua, Christian Grech, Nicholas Sammut, and David Giloteaux. 2021. "Development of a Real-Time Magnetic Field Measurement System for Synchrotron Control" Electronics 10, no. 17: 2140. https://doi.org/10.3390/electronics10172140