Remote Laboratory for E-Learning of Systems on Chip and Their Applications to Nuclear and Scientific Instrumentation

Abstract

:1. Introduction

Related Works

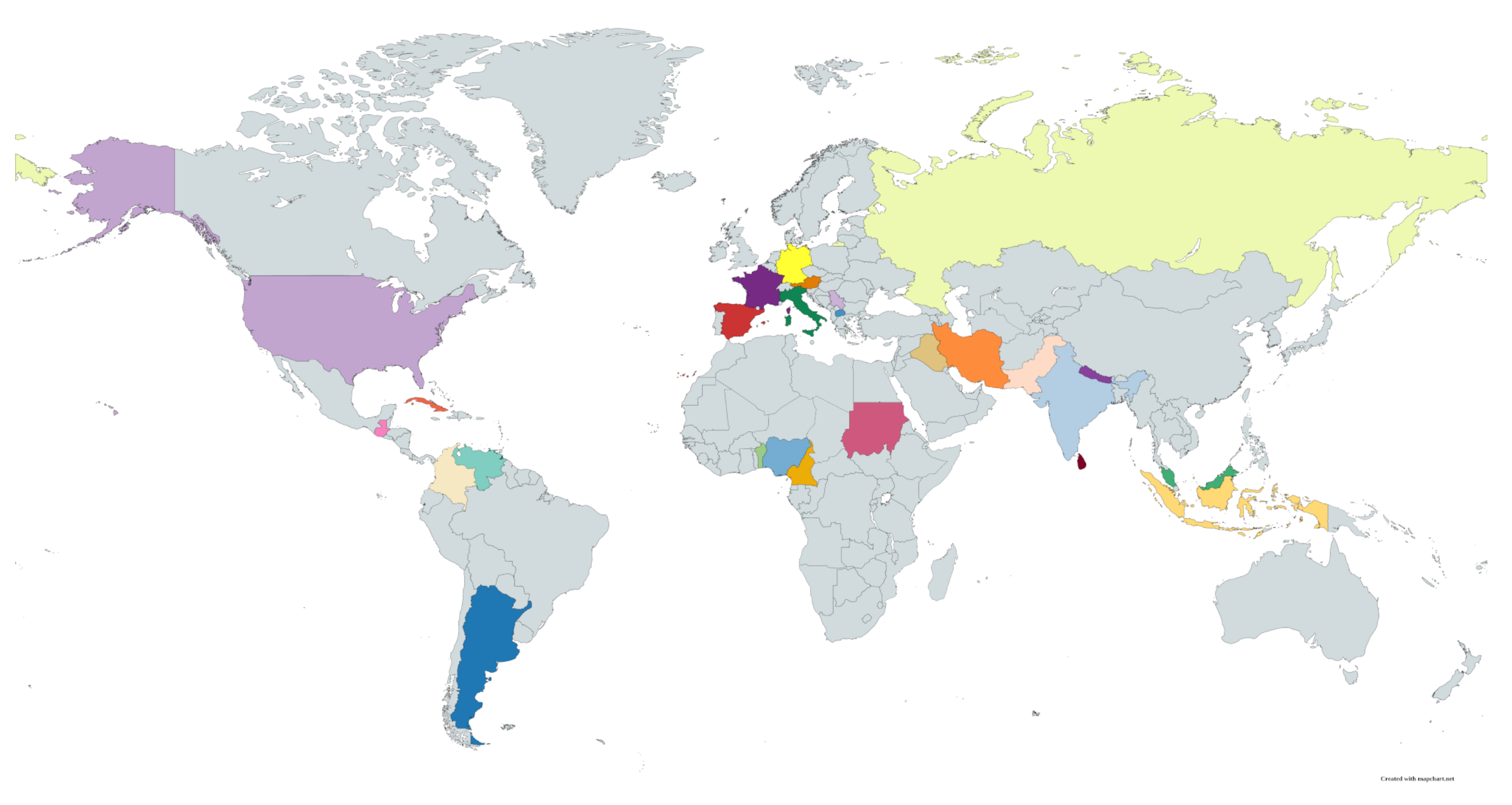

2. International School

School Program

3. Materials and Methods

3.1. Remote Laboratory

3.1.1. Hardware and Experimental Setup

- The ICTP hardware setup was based on a digital pulse processing system for X-Ray and nuclear spectroscopy, which was developed at MLab-ICTP. The system featured: a ZedBoard carrier card, an in-house high-speed data acquisition (DAQ) mezzanine card, a photo-multiplier tube (PMT) [30] with a scintillator crystal, a high voltage (HV) power supply, and a Dig-AD2 multi-function instrument. This setup is depicted in Figure 3.The DAQ card was designed at MLab-ICTP based on a commercial analog-to-digital converter that digitizes signals to 8 bits resolution at sampling rates up to 500 MHz (ADC500 [31]). It was connected to the SoC-FPGA carrier through an ANSI/VITA 57.1 FMC connector. The DAQ card [32] requires an external power supply provided by the Dig-AD2 instrument, which also generated signal stimuli for testing and calibration. The PMT was polarized using an Iseg BP40105n12 DC-HVDC converter [33] with programmable operation voltage. The output signal of the PMT was connected through a coaxial cable to the ADC500 input.For the evaluation of the final project, the participants tested their designs using synthetic pulses generated by the Dig-AD2 instrument and the PMT detector was connected to their remote hardware setup on request.

- The IAEA hardware setup was based on a radiation detection system for radiotracer applications in industry, which was developed at IAEA. The system consisted of multiple scintillator probes attached to a multi-port Power over Ethernet (PoE) switch. A single probe was used and attached to a single-port PoE switch to implement several identical training setups. Each probe consisted of a scintillator coupled to a PMT, a HV power supply board with a simple analog front-end (AFE) for converting anode pulse into voltage, and a digital pulse processing (DPP) board for data conversion and processing. The DPP board features a single-ended to differential amplifier, a 100 MHz ADC, an Artix-7 FPGA module (CMOD-A7 from Digilent [34]), a Wiznet W7500P processor [35] for Internet connectivity, and a PoE module. The DPP board can accept analog signals from the AFE or a detector simulator. The FPGA can communicate with the computer using USB to UART bridge, or via Ethernet through the processor.

3.1.2. Software Applications and Tools

3.1.3. Resources Sharing Services

3.2. In-House SoC-FPGA Development Framework

- The Communication Block (ComBlock) [41], which is an easy-to-use link layer between the microprocessor and the FPGA.

- The UDMA, a software application to encapsulate the interaction between the microprocessor and a personal computer.

- Hardware controllers that act as an interface between external devices and the user’s core FPGA design.

- (a)

- External Hardware Controller: Provides a simplified communication interface between the instrument-specific FPGA design (Core FPGA design) and the time-critical external hardware, like the high-speed ADC500 DAQ mezzanine card described in Section 3.1.1. This functional block takes care of all the details of the configuration and handling mechanism of the external hardware.

- (b)

- ComBlock: It is comprised of three different memory elements that can be asynchronously accessed from both parts, the microprocessor software/firmware and the core FPGA design. The ComBlock contains input and output registers, two First-In-First-Out (FIFO) memories, and a True Dual-Port Random Access Memory (TDPRAM). The memory elements are accessed from the side of the FPGA using native interfaces, and from the microprocessor side through the SoC AXI bus [43]. Utilizing these three types of memory elements, all data exchanges between the FPGA and the microprocessor are covered. From the microprocessor perspective, user instantiated cores in the FPGA become memory-mapped peripherals for reading and writing operations.

- (c)

- UDMA Microprocessor Firmware: It is a C library that provides functionality for a transparent communication channel between the ComBlock and a control computer. This firmware allows to exchange data, error messages, and configuration parameters between the computer and the core FPGA design or the application-specific software by means of predefined packets. It is implemented as an independent task in the underlying real-time microprocessor operating system (FreeRTOS), which supports running multiple tasks. TCP/IP over Ethernet was chosen to communicate with the computer either in a local area network or through the Internet.

- (d)

- UDMA CLI: This is a user-friendly Python-based CLI running on the control computer. It provides a set of commands to interact with the SoC-FPGA. These commands allow reading and writing the memory resources of the ComBlock for interaction with the FPGA design. Given that the CLI was built on Python, it has the advantage of multi-platform compatibility, which allows users to install the UDMA CLI on their personal computers with ease. Another advantage is that these commands can be written sequentially in a file to create automation scripts to simplify the communication with the SoC-FPGA.

3.3. Laboratories and Project Activities

3.3.1. Project 1: Digital Pulse Processor for X-ray and Nuclear Spectroscopy

- Data Acquisition: This laboratory was focused on high-speed data acquisition and signal conditioning using the DAQ card introduced in Section 3.1.1. The analog signal coming from the detector was digitized by the ADC500 of the DAQ card. Then, the resolution of the signal was enhanced through a decimation block to get it ready for the DPP module. To test the design, a periodic analog signal with known frequency was generated with the Dig-AD2 instrument. The digitized data was read through a serial connection to a plotter. The participants adjusted the ADC500 parameters and the decimation factor to condition the signal for the final step of the project.

- Digital Pulse Processing: The laboratory was centered on the implementation of a digital pulse processor on FPGA. The first part of the laboratory was dedicated to preparing a test environment by implementing a simple DPP to obtain the time of arrival and the amplitude of square pulses. The second part of the laboratory used the previous test environment to process typical PMT pulses from an experimental data set. The data were fed to the DPP by the microprocessor through the ComBlock.

- Data Transmission: This laboratory was concentrated on the exchange of data between the SoC-FPGA hardware and a control computer using the UDMA in-house tools described in Section 3.2. Specific logic blocks were implemented to interact with the FPGA design through the ComBlock from the UDMA microprocessor firmware and the UDMA CLI running on the computer. As a result, data moving experiments were performed using the CLI commands from the laboratory workstation over Ethernet. Moreover, the UDMA CLI also allowed the participants to directly interact with the experimental hardware setup from their personal computers over the Internet.

- Project Integration: This final laboratory integrated the previous three designs into a single project, completing the chain from the detector’s data acquisition to the readout of the processed data on a computer, where the amplitude of the pulses were organized into a histogram to obtain the energy spectrum. Because of the limited number of PMT detectors, the participants initially tested their designs using synthetic pulses generated by the Dig-AD2 instrument. The detector was connected by the tutors on-demand of the participants for final testing of the system and for taking measurements of the background radiation.

3.3.2. Project 2: Data Acquisition System for Radiotracer Techniques in Environmental Monitoring

- Embedded MicroBlaze processor core, which facilitated user access to design registers and data transfer to the computer.

- Oscilloscope core for capturing data streams at outputs of different design blocks.

- Signal conditioning core, which stabilized a possible slow varying DC level of the input signal, shaped exponential input signal with a finite rise and a fall time into a trapezoidal signal with predefined peaking time (with using a simple recursive algorithm) and stabilized a baseline that might fluctuate in case of a high counting rate (baseline restorer).

- Pulse Height Analysis (PHA) core, which included: a (a) PileUp Rejector (PUR) for rejecting pile-up events; (b) timers for triggering a series of measurements; a (c) Peak Detector (PKD) for detecting pulses and measuring their height; and a (d) Multi-Channel Analyzer (MCA) for sorting pulses by their height into a dual-port memory.

3.4. Remote Laboratory Implementation Costs

4. Results

4.1. Participants’ Presentations

4.2. Feedback Survey

- Q1:

- Level of difficulty of the laboratories and project activities.

- Q2:

- Presentations of the lecturers.

- Q3:

- Overall school activities.

- Q4:

- Quality of the guides and the material received during the school.

- Q5:

- Interaction with the laboratory tutors.

- Q6:

- Complexity of the tools provided to interact with remote hardware setups.

- Q7:

- Overall online experience during the school.

- Q8:

- The contents and selected topics of the school were appropriate.

- Q9:

- The proposed online modality was effective and efficient for the school.

- Q10:

- The newly acquired knowledge will be useful for their future research or teaching activities.

- Q11:

- Did not come across any disruption of services to the online experience.

- Q12:

- Would consider taking another similar school in remote mode if given the opportunity.

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Abbreviations

| AFE | Analog Front-End |

| CET | Central European Time |

| CLI | Command-Line Interpreter |

| DAQ | Data Acquisition |

| DHCP | Dynamic Host Configuration Protocol |

| DMA | Direct Memory Access |

| DNS | Domain Name System |

| DPP | Digital Pulse Processing |

| Dig-AD2 | Digilent Analog Discovery 2 |

| FIFO | First-In First-Out |

| FPGA | Field Programmable Gate Array |

| HDL | Hardware Description Language |

| HLS | High Level Synthesis |

| HV | High Voltage |

| IAEA | International Atomic Energy Agency |

| ICTP | International Centre for Theoretical Physics |

| IDE | Integrated Design Environment |

| IP | Intellectual Property |

| MCA | Multi-Channel Analyzer |

| MLab | Multidisciplinary Laboratory |

| NSIL | Nuclear Science and Instrumentation Laboratory |

| PHA | Pulse Height Analysis |

| PKD | Peak Detector |

| PMT | Photo-Multiplier Tube |

| PUR | Pile-Up Rejector |

| PoE | Power over Ethernet |

| RTL | Register Transfer Level |

| SDK | Software Development Kit |

| SSH | Secure Shell |

| SoC | System-on-Chip |

| TDPRAM | True Dual-Port Random Access Memory |

| UDMA | Universal Direct Memory Access |

| UNESCO | United Nations Educational, Scientific and Cultural Organization |

| VNC | Virtual Network Computing |

Appendix A

“It would have been useful to post the solutions to all projects and exercises.”

“Some preliminary online modality tests for self-checking could be very useful.”

“Some lectures were interesting but took too much time of the main aim which was the practical knowledge on the SoC-FPGA hardware boards.”

“This school was the best. Other events need to learn how to conduct lab activities.”

“My suggestion would be to multiply more activities like this and give the opportunity to as many people as possible to benefit from it despite the limited resources.”

“Conducting practical sessions online is a huge challenge. ICTP perfectly managed those things.”

“It was great to have a computer to work with remotely. I enjoyed the labs because they were practical. I enjoyed the lectures because they went beyond just information to give the “why” behind things.”

“Experience Gained: Developed my first SoC application. Started learning to use an OS on an embedded system. Built my first IP (IP-demystified: IPs are not written only by Martians). Got a better understanding of Git.”

“I applied for this school in order to learn and gain experience in SoC for instrumentation. I have gotten more experience than I desired. I am already planning exercises that I will use with my students next semester.”

“Most fruitful event attended in the pandemic. Best school with excellent lab activities with the best faculty.”

“The fact that this training was online made it possible to go beyond the planned objectives because, in addition to the knowledge related to FPGA and SoC, we were able to use different e-learning tools that further enrich the school’s program.”

“I learned so many new things. Using hardware remotely was an experience that needs to mention lab tutors’ wonderful expertise.”

“I really liked the possibility of remote access to the development hardware board.”

“Thank you so much to the organizers, all the amazing tutors, and incredible professors. I’m so grateful for being part of this school.”

References

- The Abdus Salam International Center for Theoretical Physics (ICTP). ICTP Home Page. Available online: https://www.ictp.it/ (accessed on 5 January 2021).

- International Atomic Energy Agency (IAEA). IAEA Home Page. Available online: https://www.iaea.org/ (accessed on 5 January 2021).

- Gazzano, J.; Crespo, M.; Cicuttin, A.; Calle, F. Field-Programmable Gate Array (FPGA) Technologies for High Performance Instrumentation; Advances in Computer and Electrical Engineering; IGI Global: Hershey, PA, USA, 2016. [Google Scholar]

- Crespo, M.L.; Cicuttin, A.; Gazzano, J.; Calle, F. Reconfigurable Virtual Instrumentation Based on FPGA for Science and High-Education. In Field-Programmable Gate Array (FPGA) Technologies for High Performance Instrumentation; Fagerberg, J., Mowery, D.C., Nelson, R.R., Eds.; IGI Global: Hershey, PA, USA, 2016; Chapter 5; pp. 99–123. [Google Scholar]

- ICTP. Scientific Calendar. Available online: https://www.ictp.it/scientific-calendar.aspx? (accessed on 3 January 2021).

- United Nations Educational, Scientific and Cultural Organization (UNESCO). UNESCO Home Page. Available online: https://en.unesco.org/ (accessed on 5 January 2021).

- Monzo, C.; Cobo, G.; Morán, J.A.; Santamaría, E.; García-Solórzano, D. Remote Laboratory for Online Engineering Education: The RLAB-UOC-FPGA Case Study. Electronics 2021, 10, 1072. [Google Scholar] [CrossRef]

- ICTP Multidisciplinary Laboratory (Mlab). Home Page of the ICTP-IAEA School. Available online: http://indico.ictp.it/event/9443/ (accessed on 5 January 2021).

- Mohsen, A.E.; Youssef GadAlrab, M.; elhaya Mahmoud, Z.; Alshaer, G.; Asy, M.; Mostafa, H. Remote FPGA Lab For ZYNQ and Virtex-7 Kits. In Proceedings of the 2019 IEEE 62nd International Midwest Symposium on Circuits and Systems (MWSCAS), Dallas, TX, USA, 4–7 August 2019; pp. 185–188. [Google Scholar] [CrossRef]

- Winzker, M.; Kiessling, R.; Schwandt, A.; Paez, C.S.; Shanab, S.A. Teaching Across the Ocean with Video Lectures and Remote-Lab. In Proceedings of the 2018 IEEE World Engineering Education Conference (EDUNINE), Buenos Aires, Argentina, 11–14 March 2018; pp. 1–4. [Google Scholar] [CrossRef]

- Oballe-Peinado, O.; Castellanos-Ramos, J.; Sánchez-Durán, J.A.; Navas-González, R.; Daza-Márquez, A.; Botín-Córdoba, J.A. FPGA-Based Remote Laboratory for Digital Electronics. In Proceedings of the 2020 XIV Technologies Applied to Electronics Teaching Conference (TAEE), Porto, Portugal, 8–10 July 2020; pp. 1–5. [Google Scholar] [CrossRef]

- Luković, V.; Krneta, R.; Damnjanović, Đ.; Peulić, A. The remote lab “Nexys 2 FPGA platform” aimed for learning design of digital circuits. In Proceedings of the 2017 4th Experiment@International Conference (exp.at’17), Faro, Portugal, 6–8 June 2017; pp. 101–102. [Google Scholar] [CrossRef]

- Torrensen, J.; Wold, A.; Hafting, Y.; Nygaard, T.; Skogstrom, R.; Norenda, J. Flexible teaching of reconfigurable logic design including a remote cloud lab. In Proceedings of the Sixth International Conference on E-Learning and E-Technologies in Education (ICEEE 2017), Lodz, Poland, 18–20 September 2017. [Google Scholar]

- Zhang, K.; Chang, Y.; Chen, M.; Bao, Y.; Xu, Z. Computer Organization and Design Course with FPGA Cloud. In Proceedings of the 50th ACM Technical Symposium on Computer Science Education, Minneapolis, MN, USA, 27 February–2 March 2019; pp. 927–933. [Google Scholar] [CrossRef]

- Mayoz, C.A.; da Silva Beraldo, A.L.; Villar-Martinez, A.; Rodriguez-Gil, L.; de Souza Seron, W.F.M.; Orduña, P. FPGA remote laboratory: Experience of a shared laboratory between UPNA and UNIFESP. In Proceedings of the 2020 XIV Technologies Applied to Electronics Teaching Conference (TAEE), Porto, Portugal, 8–10 July 2020; pp. 1–8. [Google Scholar] [CrossRef]

- Zoom Video. Zoom. Available online: https://zoom.us/ (accessed on 11 January 2021).

- The FreeRTOS™ Reference Manual. Rev. 2. Available online: https://www.freertos.org/Documentation/FreeRTOS_Reference_Manual_V9.0.0.pdf (accessed on 1 January 2021).

- Fahim, F.; Hawks, B.; Herwig, C.; Hirschauer, J.; Jindariani, S.; Tran, N.; Carloni, L.P.; Guglielmo, G.D.; Harris, P.C.; Krupa, J.D.; et al. hls4ml: An Open-Source Codesign Workflow to Empower Scientific Low-Power Machine Learning Devices. arXiv 2021, arXiv:2103.05579. [Google Scholar]

- de Dinechin, F.; Pasca, B. Designing Custom Arithmetic Data Paths with FloPoCo. IEEE Des. Test Comput. 2011, 28, 18–27. [Google Scholar] [CrossRef]

- ICTP Mlab. ICTP-IAEA School Program. Available online: http://indico.ictp.it/event/9443/other-view?view=ictptimetable (accessed on 5 January 2021).

- Foulon, F.; Ben Abdelouahed, H.; Bogovac, M.; Charisopoulos, S.; Matos, M.; Migliori, A.; Padilla-Alvarez, R.; Pessoa Barradas, N.; Ridikas, D.; Simon, A.; et al. IAEA Nuclear Science and Instrumentation Laboratory: Support to IAEA Member States and Recent Developments. EPJ Web Conf. 2020, 225, 7. [Google Scholar] [CrossRef] [Green Version]

- AVNET. ZedBoard. Available online: https://www.avnet.com/wps/portal/us/products/avnet-boards/avnet-board-families/zedboard/ (accessed on 3 January 2021).

- Zynq-7000 SoC Data Sheet: Overview. Available online: https://www.xilinx.com/support/documentation/data_sheets/ds190-Zynq-7000-Overview.pdf (accessed on 30 December 2020).

- Xilinx. Vivado 2019.1. Available online: https://www.xilinx.com/products/design-tools/vivado.html (accessed on 30 December 2020).

- Git. Git SCM System. Available online: https://git-scm.com/ (accessed on 5 February 2021).

- Slack. Slack. Available online: https://slack.com/intl/en-it/ (accessed on 5 January 2021).

- Digilent. Digilent Pmod™ Interface Specification. Available online: https://reference.digilentinc.com/_media/reference/pmod/pmod-interface-specification-1_3_1.pdf (accessed on 15 November 2020).

- FMC Community. Available online: https://www.vita.com/fmc (accessed on 5 January 2021).

- Dabacan, M. Analog Discovery 2: 100 MS/s USB Oscilloscope, Logic Analyzer and Variable Power Supply. Available online: https://reference.digilentinc.com/reference/instrumentation/analog-discovery-2/reference-manual (accessed on 17 November 2020).

- Thorn-EMI Electornics LTD. Photomultipliers Catalogue; Thorn-EMI Electornics LTD: London, UK, 1986. [Google Scholar]

- DC08500 High Performance, Low Power 8-Bit 500 MSPS A/D Converter. Rev. 3. Available online: https://www.ti.com/lit/ds/symlink/ads8505.pdf (accessed on 25 October 2020).

- Carrato, S.; Chatterjee, C.; Cicuttin, A.; Ciliberti, P.; Crespo, M.; Dalla Torre, S.; Dasgupta, S.; Florian, W.; Ordóñez, L.G.; Gobbo, B.; et al. A scalable High Voltage Power Supply System with system on chip control for Micro Pattern Gaseous Detectors. Nucl. Instrum. Methods Phys. Res. Sect. A Accel. Spectrometers Detect. Assoc. Equip. 2020, 963, 163763. [Google Scholar] [CrossRef]

- Iseg. BPS High Voltage Power Supply Series. Available online: https://iseg-hv.com/download/DC_DC/BPS/iseg_datasheet_BPS_en.pdf (accessed on 30 September 2020).

- Digilent. Cmod A7 Reference Manual. Available online: https://reference.digilentinc.com/programmable-logic/cmod-a7/reference-manual (accessed on 30 October 2020).

- Wiznet. W7500x Data Sheet. Available online: https://wizwiki.net/wiki/lib/exe/fetch.php?media=products:w7500:w7500x_ds_v106_20180205_2.pdf (accessed on 15 November 2020).

- Canonical. Ubuntu 20.04 LTS. Available online: https://ubuntu.com/ (accessed on 5 January 2021).

- ICTP Mlab. Universal Direct Memory Access-UDMA. Available online: https://gitlab.com/brunovali/udma (accessed on 5 January 2021).

- Gitlab. Gitlab Repository. Available online: https://docs.gitlab.com/ee/user/project/repository/ (accessed on 10 November 2020).

- ICTP MLab. Wiki home Page of the School Repository. Available online: https://gitlab.com/smr3562/labs/-/wikis/home (accessed on 5 January 2021).

- Wu, J. Using Vivado Design Suite with Version Control Systems-XAPP1165. Available online: https://www.xilinx.com/support/documentation/application_notes/xapp1165.pdf (accessed on 12 January 2021).

- ICTP Mlab and INTI CMNT. The Core Comblock. Available online: https://gitlab.com/rodrigomelo9/core-comblock (accessed on 5 January 2021).

- Mannatunga, K.S.; Ordóñez, L.G.; Amador, M.B.; Crespo, M.L.; Cicuttin, A.; Levorato, S.; Melo, R.; Valinoti, B. Design for Portability of Reconfigurable Virtual Instrumentation. In Proceedings of the 2019 X Southern Conference on Programmable Logic (SPL), Buenos Aires, Argentina, 10–12 April 2019; pp. 45–52. [Google Scholar] [CrossRef]

- AXI Reference Guide. Rev. 3. Available online: https://www.xilinx.com/support/documentation/ip_documentation/axi_ref_guide/latest/ug761_axi_reference_guide.pdf (accessed on 22 December 2020).

- Cicuttin, A.; Crespo, M.L.; Mannatunga, K.S.; Garcia, V.V.; Baldazzi, G.; Rignanese, L.P.; Ahangarianabhari, M.; Bertuccio, G.; Fabiani, S.; Rachevski, A.; et al. A programmable System-on-Chip based digital pulse processing for high resolution X-ray spectroscopy. In Proceedings of the 2016 International Conference on Advances in Electrical, Electronic and Systems Engineering (ICAEES), Putrajaya, Malaysia, 14–16 November 2016; pp. 520–525. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Crespo, M.L.; Foulon, F.; Cicuttin, A.; Bogovac, M.; Onime, C.; Sisterna, C.; Melo, R.; Florian Samayoa, W.; García Ordóñez, L.G.; Molina, R.; et al. Remote Laboratory for E-Learning of Systems on Chip and Their Applications to Nuclear and Scientific Instrumentation. Electronics 2021, 10, 2191. https://doi.org/10.3390/electronics10182191

Crespo ML, Foulon F, Cicuttin A, Bogovac M, Onime C, Sisterna C, Melo R, Florian Samayoa W, García Ordóñez LG, Molina R, et al. Remote Laboratory for E-Learning of Systems on Chip and Their Applications to Nuclear and Scientific Instrumentation. Electronics. 2021; 10(18):2191. https://doi.org/10.3390/electronics10182191

Chicago/Turabian StyleCrespo, Maria Liz, François Foulon, Andres Cicuttin, Mladen Bogovac, Clement Onime, Cristian Sisterna, Rodrigo Melo, Werner Florian Samayoa, Luis Guillermo García Ordóñez, Romina Molina, and et al. 2021. "Remote Laboratory for E-Learning of Systems on Chip and Their Applications to Nuclear and Scientific Instrumentation" Electronics 10, no. 18: 2191. https://doi.org/10.3390/electronics10182191

APA StyleCrespo, M. L., Foulon, F., Cicuttin, A., Bogovac, M., Onime, C., Sisterna, C., Melo, R., Florian Samayoa, W., García Ordóñez, L. G., Molina, R., & Valinoti, B. (2021). Remote Laboratory for E-Learning of Systems on Chip and Their Applications to Nuclear and Scientific Instrumentation. Electronics, 10(18), 2191. https://doi.org/10.3390/electronics10182191