A Systematic Assessment of W-Doped CoFeB Single Free Layers for Low Power STT-MRAM Applications

Abstract

:1. Introduction

2. Materials and Methods

3. Results and Discussion

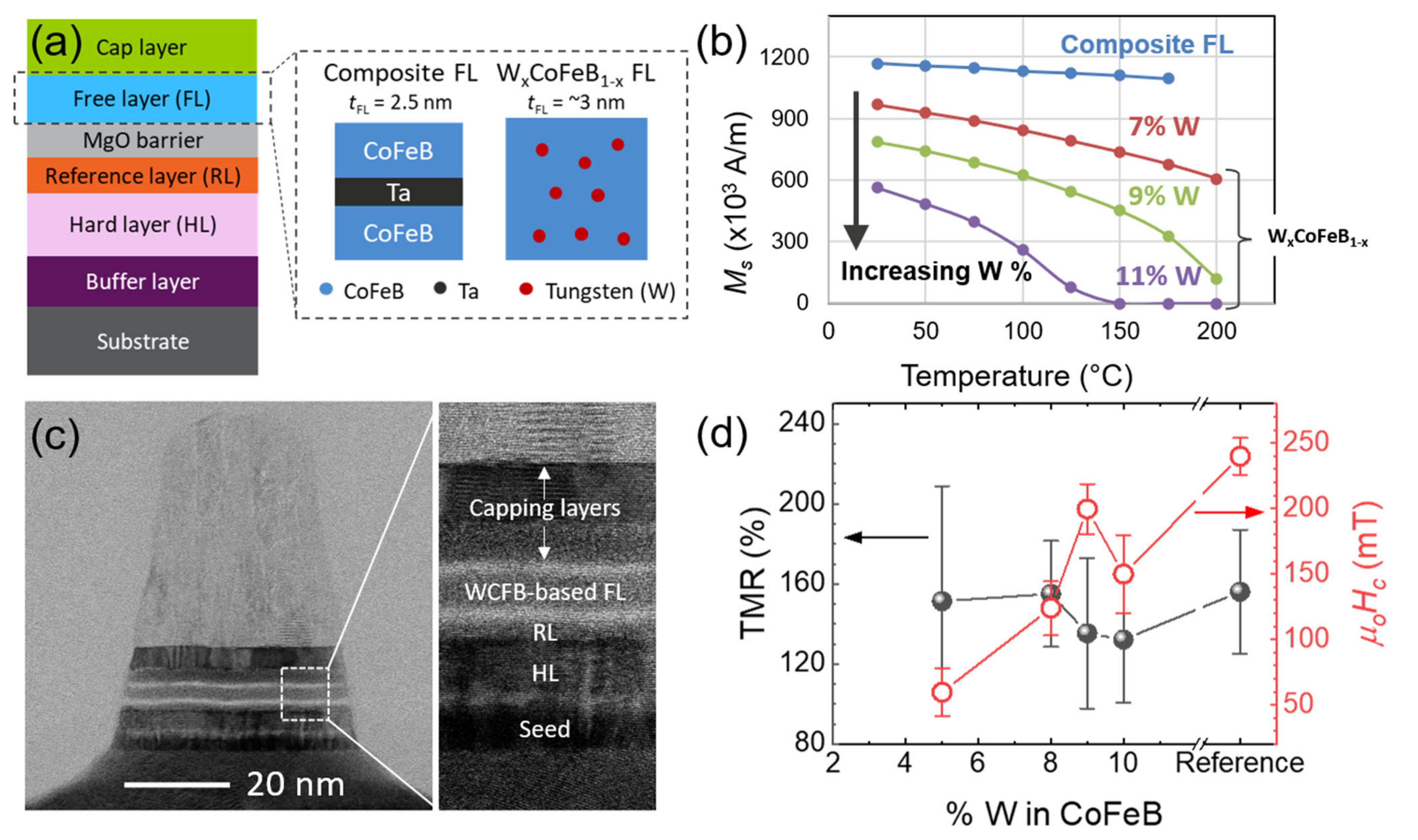

3.1. Stack Development and Fundamental MTJ Properties

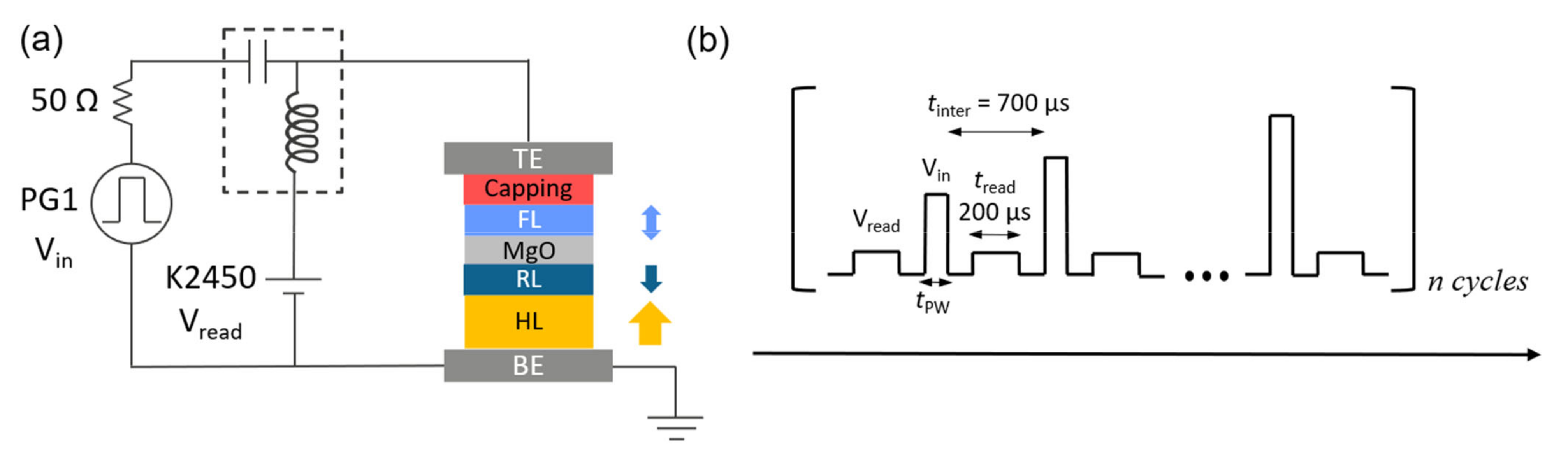

3.2. STT Write Performance

3.3. Reliability

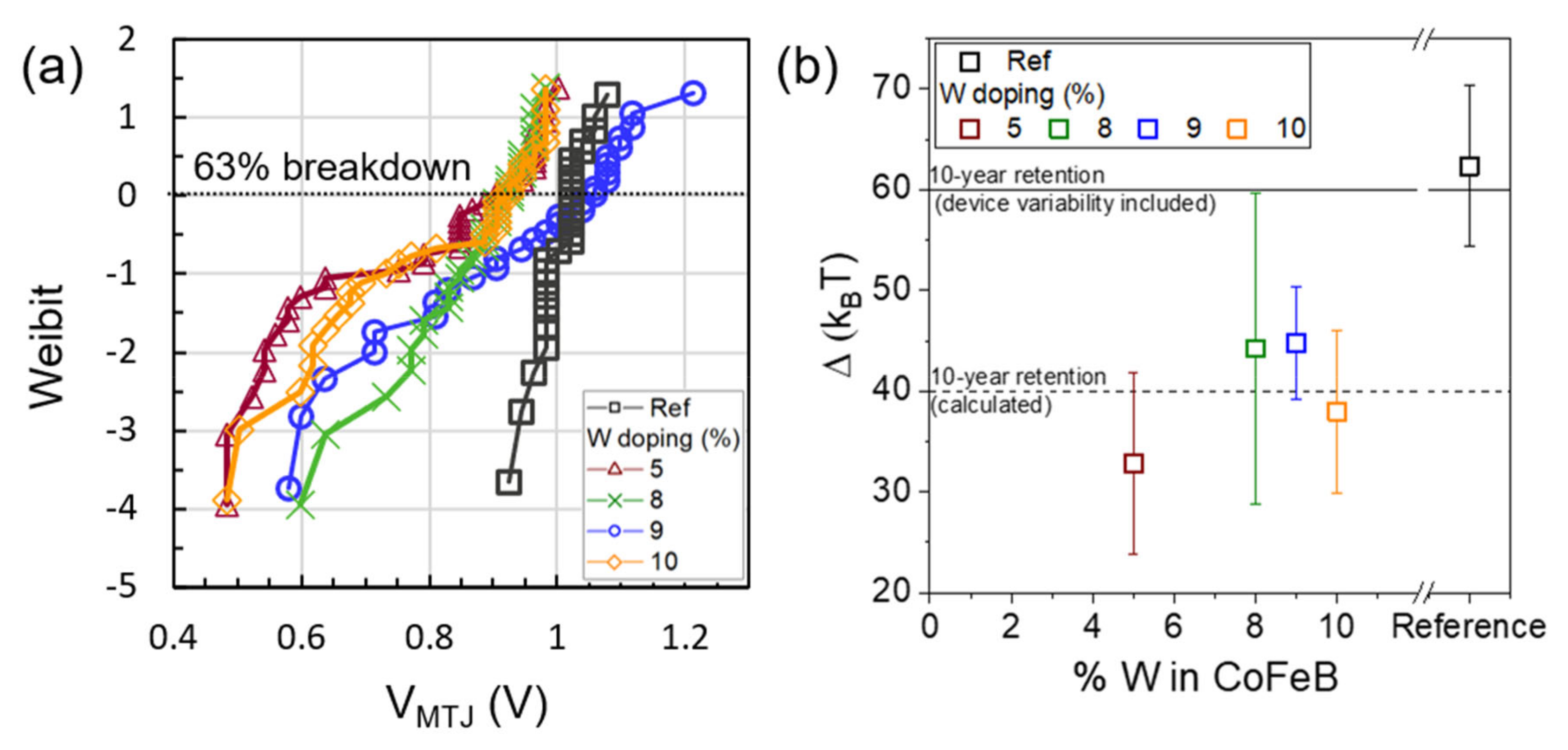

3.3.1. Breakdown Characteristics

3.3.2. Thermal Stability and Retention

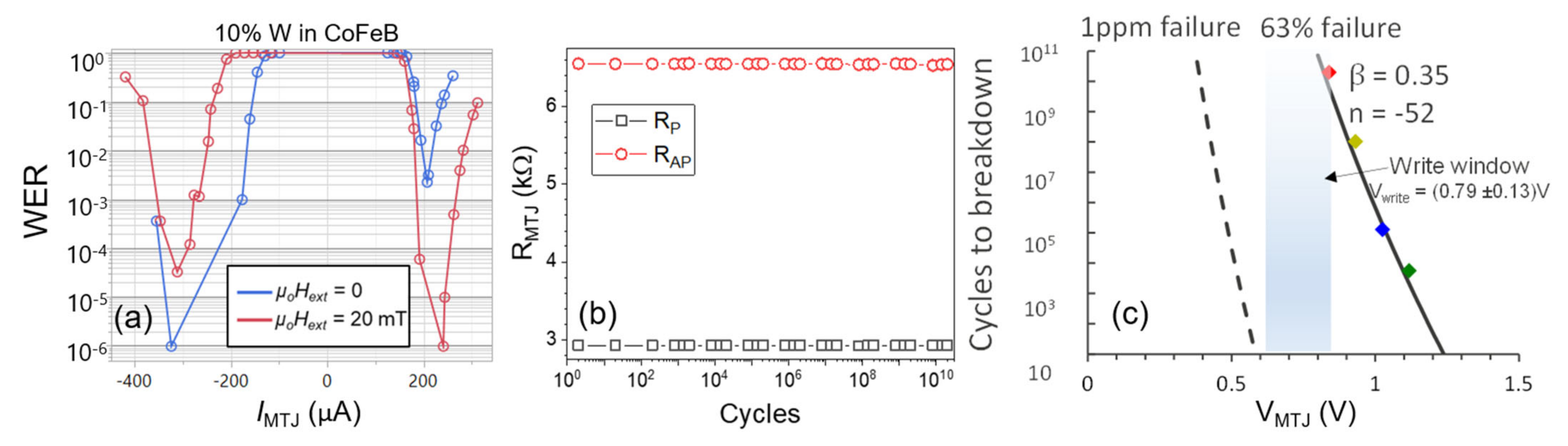

3.3.3. Write Error Rates (WER) and Endurance

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Ikeda, S.; Miura, K.; Yamamoto, H.; Mizunuma, K.; Gan, H.D.; Endo, M.; Kanai, S.; Hayakawa, J.; Matsukura, F.; Ohno, H. A Perpendicular-Anisotropy CoFeB–MgO Magnetic Tunnel Junction. Nat. Mater. 2010, 9, 721–724. [Google Scholar] [CrossRef] [PubMed]

- Kang, S.H. Embedded STT-MRAM for Energy-Efficient and Cost-Effective Mobile Systems. In Proceedings of the 2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers, Honolulu, HI, USA, 9–12 June 2014; pp. 1–2. [Google Scholar]

- Slaughter, J.M.; Rizzo, N.D.; Janesky, J.; Whig, R.; Mancoff, F.B.; Houssameddine, D.; Sun, J.J.; Aggarwal, S.; Nagel, K.; Deshpande, S.; et al. High Density ST-MRAM Technology (Invited). In Proceedings of the 2012 International Electron Devices Meeting, San Francisco, CA, USA, 10–13 December 2012; pp. 29.3.1–29.3.4. [Google Scholar]

- Lee, T.Y.; Yamane, K.; Otani, Y.; Zeng, D.; Kwon, J.; Lim, J.H.; Naik, V.B.; Hau, L.Y.; Chao, R.; Chung, N.L.; et al. Advanced MTJ Stack Engineering of STT-MRAM to Realize High Speed Applications. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12–18 December 2020; pp. 11.6.1–11.6.4. [Google Scholar]

- Lee, Y.K.; Song, Y.; Kim, J.; Oh, S.; Bae, B.-J.; Lee, S.; Lee, J.; Pi, U.; Seo, B.; Jung, H.; et al. Embedded STT-MRAM in 28-Nm FDSOI Logic Process for Industrial MCU/IoT Application. In Proceedings of the 2018 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 18–22 June 2018; pp. 181–182. [Google Scholar]

- Jan, G.; Thomas, L.; Le, S.; Lee, Y.-J.; Liu, H.; Zhu, J.; Iwata-Harms, J.; Patel, S.; Tong, R.-Y.; Sundar, V.; et al. Demonstration of Ultra-Low Voltage and Ultra Low Power STT-MRAM Designed for Compatibility with 0x Node Embedded LLC Applications. In Proceedings of the 2018 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 18–12 June 2018; pp. 65–66. [Google Scholar]

- Naik, V.B.; Yamane, K.; Lee, T.Y.; Kwon, J.; Chao, R.; Lim, J.H.; Chung, N.L.; Behin-Aein, B.; Hau, L.Y.; Zeng, D.; et al. JEDEC-Qualified Highly Reliable 22nm FD-SOI Embedded MRAM For Low-Power Industrial-Grade, and Extended Performance Towards Automotive-Grade-1 Applications. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12–18 December 2020; pp. 11.3.1–11.3.4. [Google Scholar]

- Dixit, H.; Naik, V.B.; Yamane, K.; Lee, T.; Kwon, J.-H.; Behin-Aein, B.; Soss, S.; Taylor, W.J. TCAD Device Technology Co-Optimization Workflow for Manufacturable MRAM Technology. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12–18 December 2020; pp. 13.5.1–13.5.4. [Google Scholar]

- Golonzka, O.; Alzate, J.-G.; Arslan, U.; Bohr, M.; Bai, P.; Brockman, J.; Buford, B.; Connor, C.; Das, N.; Doyle, B.; et al. MRAM as Embedded Non-Volatile Memory Solution for 22FFL FinFET Technology. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 18.1.1–18.1.4. [Google Scholar]

- Kan, J.J.; Park, C.; Ching, C.; Ahn, J.; Xue, L.; Wang, R.; Kontos, A.; Liang, S.; Bangar, M.; Chen, H.; et al. Systematic Validation of 2x Nm Diameter Perpendicular MTJ Arrays and MgO Barrier for Sub-10 Nm Embedded STT-MRAM with Practically Unlimited Endurance. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 27.4.1–27.4.4. [Google Scholar]

- Rao, S.; Kim, W.; van Beek, S.; Kundu, S.; Perumkunnil, M.; Cosemans, S.; Yasin, F.; Couet, S.; Carpenter, R.; O’Sullivan, B.J.; et al. STT-MRAM Array Performance Improvement through Optimization of Ion Beam Etch and MTJ for Last-Level Cache Application. In Proceedings of the 2021 IEEE International Memory Workshop (IMW), Dresden, Germany, 16–19 May 2021; pp. 1–4. [Google Scholar]

- Xue, L.; Ching, C.; Kontos, A.; Ahn, J.; Wang, X.; Whig, R.; Tseng, H.; Howarth, J.; Hassan, S.; Chen, H.; et al. Process Optimization of Perpendicular Magnetic Tunnel Junction Arrays for Last-Level Cache beyond 7 Nm Node. In Proceedings of the 2018 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 18–12 June 2018; pp. 117–118. [Google Scholar]

- Khvalkovskiy, A.V.; Apalkov, D.; Watts, S.; Chepulskii, R.; Beach, R.S.; Ong, A.; Tang, X.; Driskill-Smith, A.; Butler, W.H.; Visscher, P.B.; et al. Basic Principles of STT-MRAM Cell Operation in Memory Arrays. J. Phys. D Appl. Phys. 2013, 46, 074001. [Google Scholar] [CrossRef]

- Liu, H.; Bedau, D.; Sun, J.Z.; Mangin, S.; Fullerton, E.E.; Katine, J.A.; Kent, A.D. Dynamics of Spin Torque Switching in All-Perpendicular Spin Valve Nanopillars. J. Mag. Mag. Mater. 2014, 358–359, 233–258. [Google Scholar] [CrossRef]

- Iwata-Harms, J.M.; Jan, G.; Serrano-Guisan, S.; Thomas, L.; Liu, H.; Zhu, J.; Lee, Y.-J.; Le, S.; Tong, R.-Y.; Patel, S.; et al. Ultrathin Perpendicular Magnetic Anisotropy CoFeB Free Layers for Highly Efficient, High Speed Writing in Spin-Transfer-Torque Magnetic Random Access Memory. Sci. Rep. 2019, 9, 19407. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Santos, T.S.; Mihajlović, G.; Smith, N.; Li, J.-L.; Carey, M.; Katine, J.A.; Terris, B.D. Ultrathin Perpendicular Free Layers for Lowering the Switching Current in STT-MRAM. J. Appl. Phys. 2020, 128, 113904. [Google Scholar] [CrossRef]

- Chatterjee, J.; Sousa, R.C.; Perrissin, N.; Auffret, S.; Ducruet, C.; Dieny, B. Enhanced Annealing Stability and Perpendicular Magnetic Anisotropy in Perpendicular Magnetic Tunnel Junctions Using W Layer. Appl. Phys. Lett. 2017, 110, 202401. [Google Scholar] [CrossRef] [Green Version]

- Hu, G.; Gottwald, M.G.; He, Q.; Park, J.H.; Lauer, G.; Nowak, J.J.; Brown, S.L.; Doris, B.; Edelstein, D.; Evarts, E.R.; et al. Key Parameters Affecting STT-MRAM Switching Efficiency and Improved Device Performance of 400 °C-Compatible p-MTJs. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 38.3.1–38.3.4. [Google Scholar]

- Kan, J.J.; Gottwald, M.; Park, C.; Zhu, X.; Kang, S.H. Thermally Robust Perpendicular STT-MRAM Free Layer Films Through Capping Layer Engineering. IEEE Trans. Magn. 2015, 51, 1–5. [Google Scholar] [CrossRef]

- Iwata-Harms, J.M.; Jan, G.; Liu, H.; Serrano-Guisan, S.; Zhu, J.; Thomas, L.; Tong, R.-Y.; Sundar, V.; Wang, P.-K. High-Temperature Thermal Stability Driven by Magnetization Dilution in CoFeB Free Layers for Spin-Transfer-Torque Magnetic Random Access Memory. Sci. Rep. 2018, 8, 14409. [Google Scholar] [CrossRef] [PubMed]

- O’Sullivan, B.J.; Van Beek, S.; Roussel, P.J.; Rao, S.; Kim, W.; Couet, S.; Swerts, J.; Yasin, F.; Crotti, D.; Linten, D.; et al. Extended RVS Characterisation of STT-MRAM Devices: Enabling Detection of AP/P Switching and Breakdown. In Proceedings of the 2018 IEEE International Reliability Physics Symposium (IRPS), Burlingame, CA, USA, 11–15 March 2018; pp. P-MY.5-1–P-MY.5-6. [Google Scholar]

- Van Beek, S.; Rousse, P.; O’Sullivan, B.; Degraeve, R.; Cosemans, S.; Linten, D.; Kar, G.S. Study of Breakdown in STT-MRAM Using Ramped Voltage Stress and All-in-One Maximum Likelihood Fit. In Proceedings of the 2018 48th European Solid-State Device Research Conference (ESSDERC), Dresden, Germany, 3–6 September 2018; pp. 146–149. [Google Scholar]

- Couet, S.; Devolder, T.; Swerts, J.; Lin, T.; Liu, E.; Van Elshoct, S.; Kar, G.S. Impact of Ta and W-based spacers in double MgO STT-MRAM free layers on perpendicular anisotropy and damping. Appl. Phys. Lett. 2017, 107, 152406. [Google Scholar] [CrossRef]

- Van Beek, S.; O’Sullivan, B.J.; Roussel, P.J.; Degraeve, R.; Bury, E.; Swerts, J.; Couet, S.; Souriau, L.; Kundu, S.; Rao, S.; et al. Impact of Self-Heating on Reliability Predictions in STT-MRAM. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 25.2.1–25.2.4. [Google Scholar]

- Endoh, T.; Honjo, H. A Recent Progress of Spintronics Devices for Integrated Circuit Applications. J. Low Power Electron. Appl. 2018, 8, 44. [Google Scholar] [CrossRef] [Green Version]

- Pellegren, J.P.; Furuta, M.; Sundar, V.; Liu, Y.; Zhu, J.-G.; Sokalski, V. Increased Boron Content for Wider Process Tolerance in Perpendicular MTJs. AIP Adv. 2017, 7, 055901. [Google Scholar] [CrossRef] [Green Version]

- Bedau, D.; Liu, H.; Sun, J.Z.; Katine, J.A.; Fullerton, E.E.; Mangin, S.; Kent, A.D. Spin-Transfer Pulse Switching: From the Dynamic to the Thermally Activated Regime. Appl. Phys. Lett. 2010, 97, 262502. [Google Scholar] [CrossRef] [Green Version]

- Hu, G.; Nowak, J.J.; Gottwald, M.G.; Sun, J.Z.; Houssameddine, D.; Bak, J.; Brown, S.L.; Hashemi, P.; He, Q.; Kim, J.; et al. Reliable Five-Nanosecond Writing of Spin-Transfer Torque Magnetic Random-Access Memory. IEEE Magn. Lett. 2019, 10, 1–4. [Google Scholar] [CrossRef]

- Kim, W.; Couet, S.; Swerts, J.; Lin, T.; Tomczak, Y.; Souriau, L.; Tsvetanova, D.; Sankaran, K.; Donadio, G.L.; Crotti, D.; et al. Experimental Observation of Back-Hopping With Reference Layer Flipping by High-Voltage Pulse in Perpendicular Magnetic Tunnel Junctions. IEEE Trans. Magn. 2016, 52, 1–4. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Rao, S.; Couet, S.; Van Beek, S.; Kundu, S.; Sharifi, S.H.; Jossart, N.; Kar, G.S. A Systematic Assessment of W-Doped CoFeB Single Free Layers for Low Power STT-MRAM Applications. Electronics 2021, 10, 2384. https://doi.org/10.3390/electronics10192384

Rao S, Couet S, Van Beek S, Kundu S, Sharifi SH, Jossart N, Kar GS. A Systematic Assessment of W-Doped CoFeB Single Free Layers for Low Power STT-MRAM Applications. Electronics. 2021; 10(19):2384. https://doi.org/10.3390/electronics10192384

Chicago/Turabian StyleRao, Siddharth, Sebastien Couet, Simon Van Beek, Shreya Kundu, Shamin Houshmand Sharifi, Nico Jossart, and Gouri Sankar Kar. 2021. "A Systematic Assessment of W-Doped CoFeB Single Free Layers for Low Power STT-MRAM Applications" Electronics 10, no. 19: 2384. https://doi.org/10.3390/electronics10192384

APA StyleRao, S., Couet, S., Van Beek, S., Kundu, S., Sharifi, S. H., Jossart, N., & Kar, G. S. (2021). A Systematic Assessment of W-Doped CoFeB Single Free Layers for Low Power STT-MRAM Applications. Electronics, 10(19), 2384. https://doi.org/10.3390/electronics10192384