A Novel MOS-Channel Diode Embedded in a SiC Superjunction MOSFET for Enhanced Switching Performance and Superior Short Circuit Ruggedness

Abstract

:1. Introduction

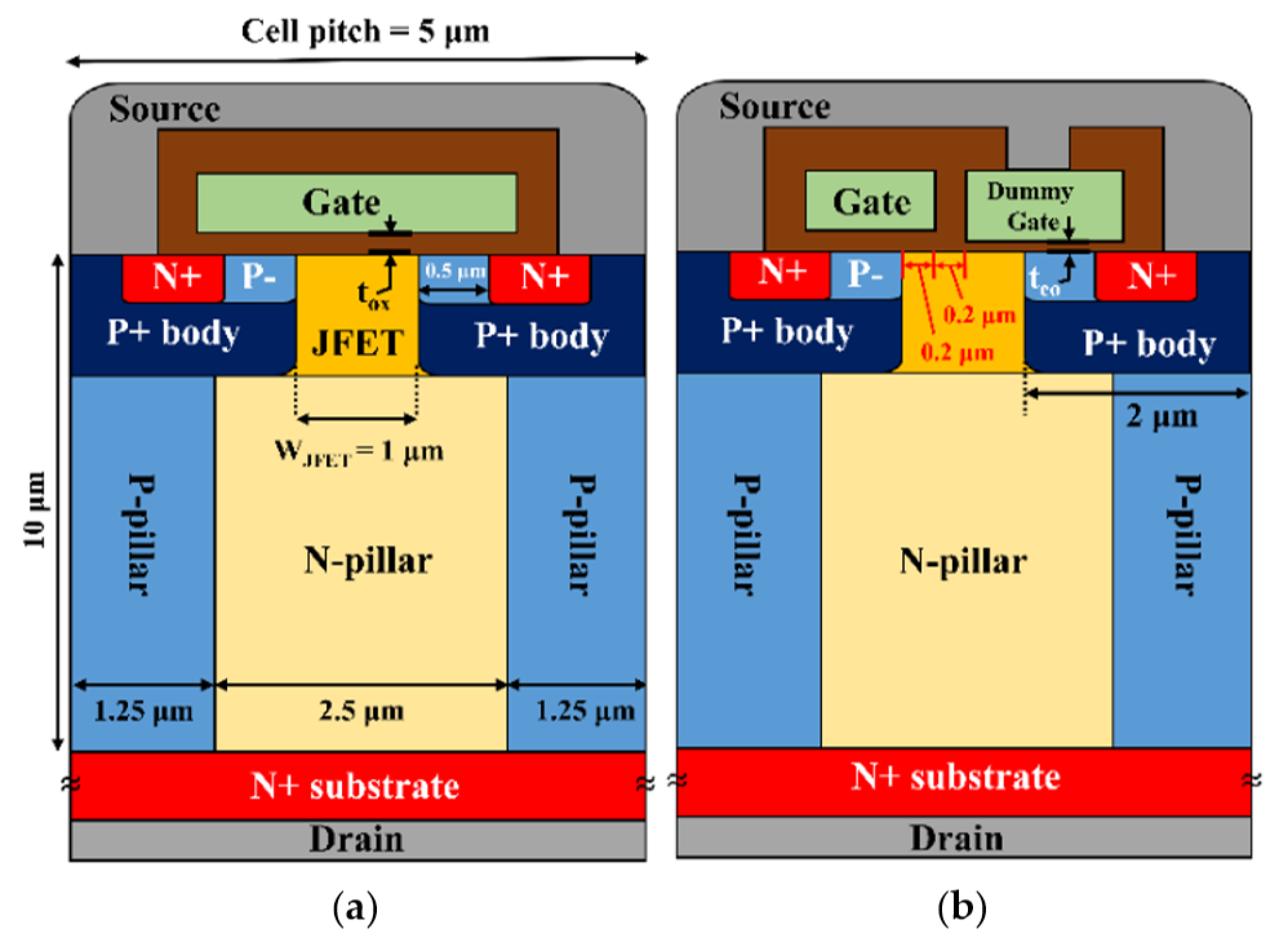

2. Device Structures and Simulation Background

3. Results and Discussion

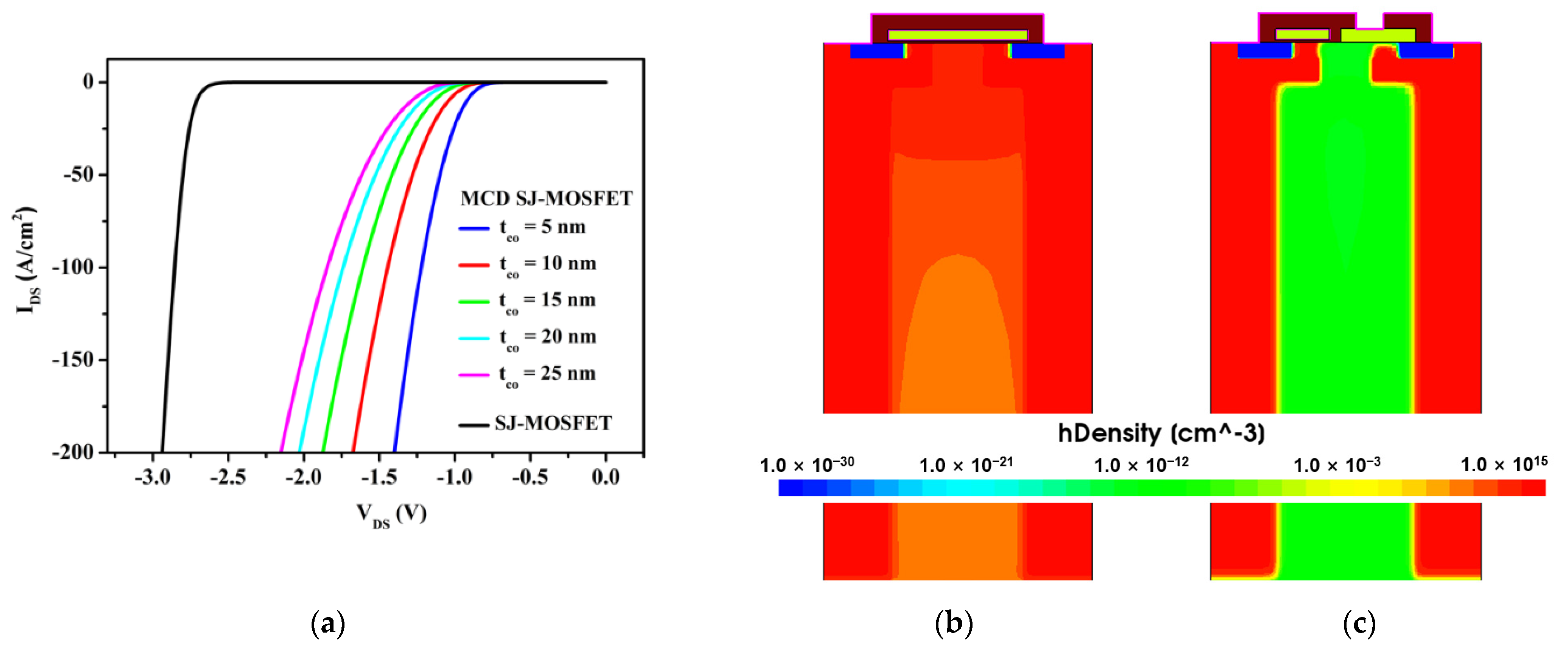

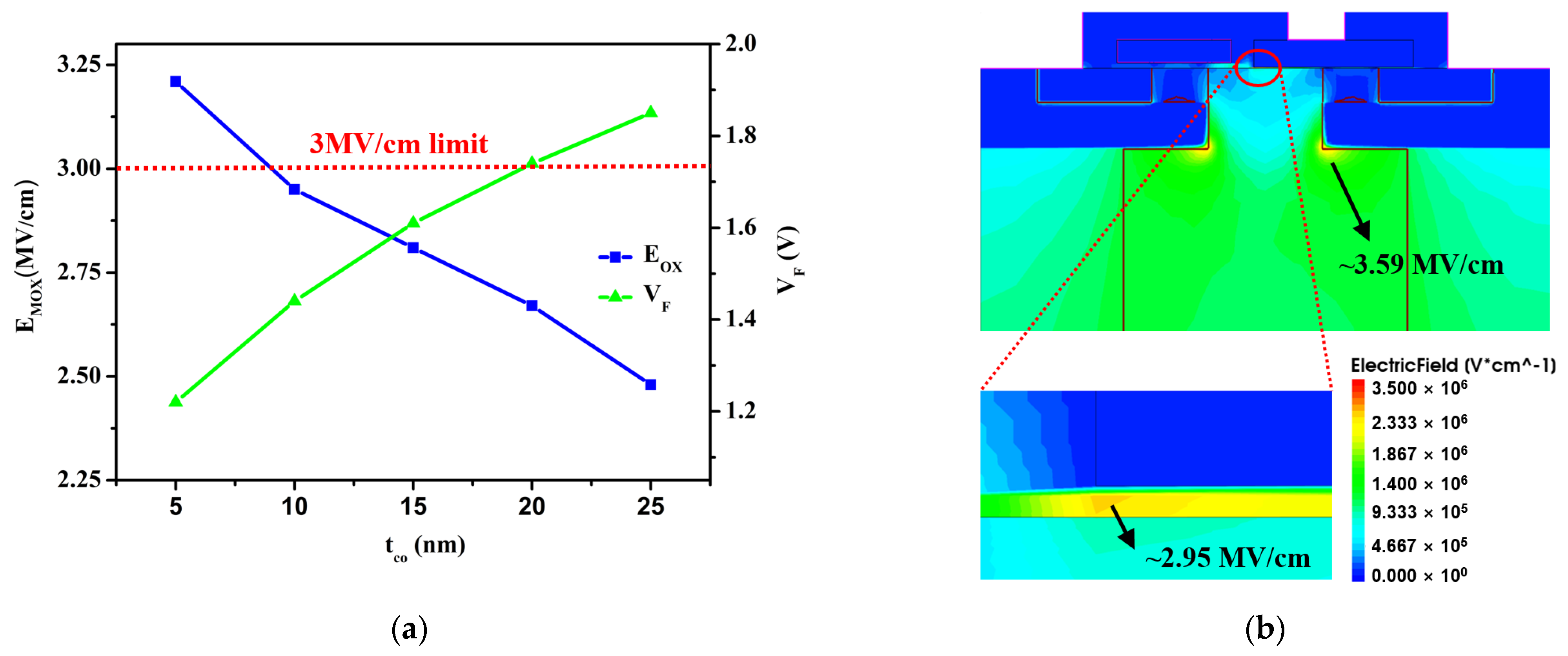

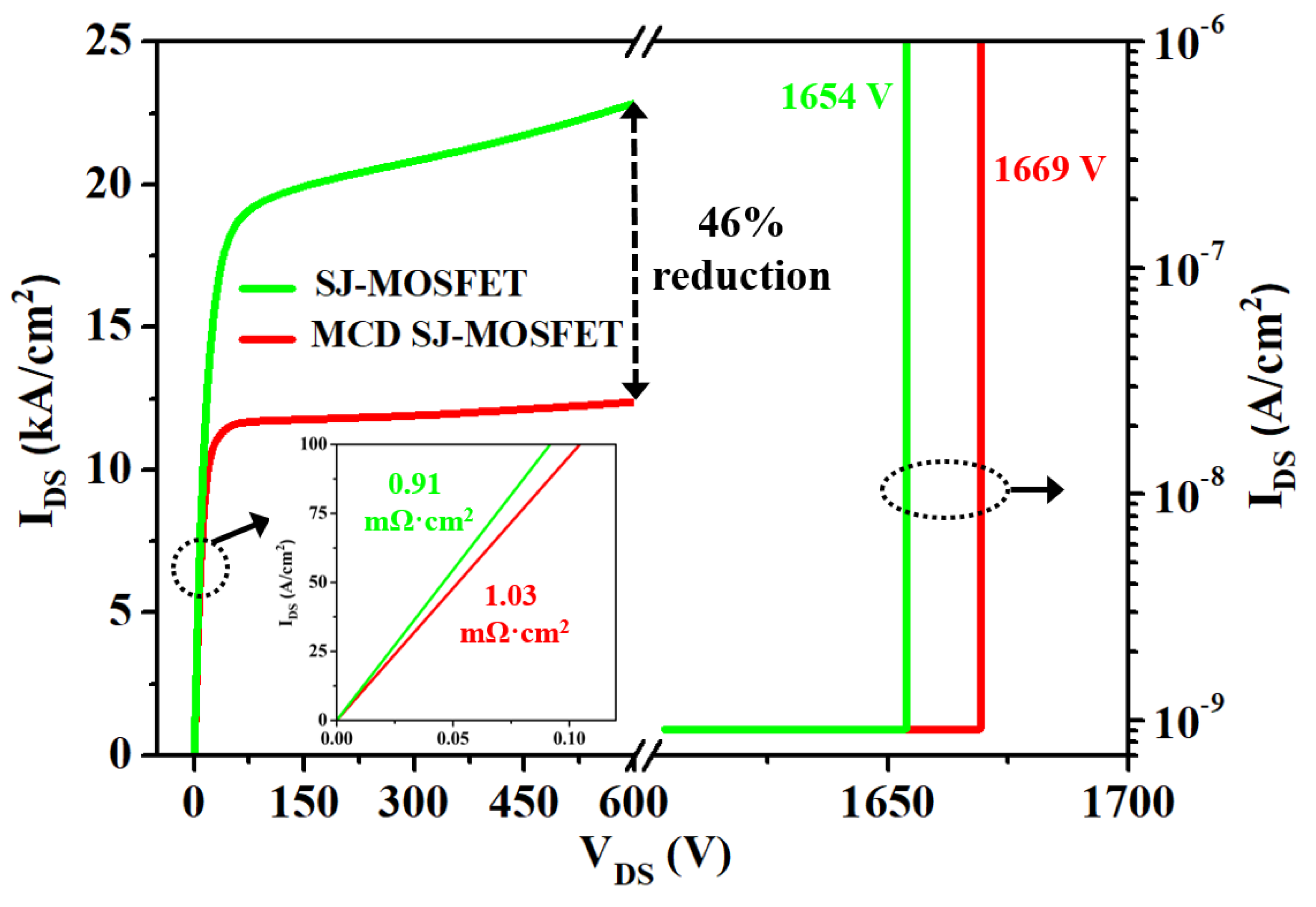

3.1. Electrical Characteristics

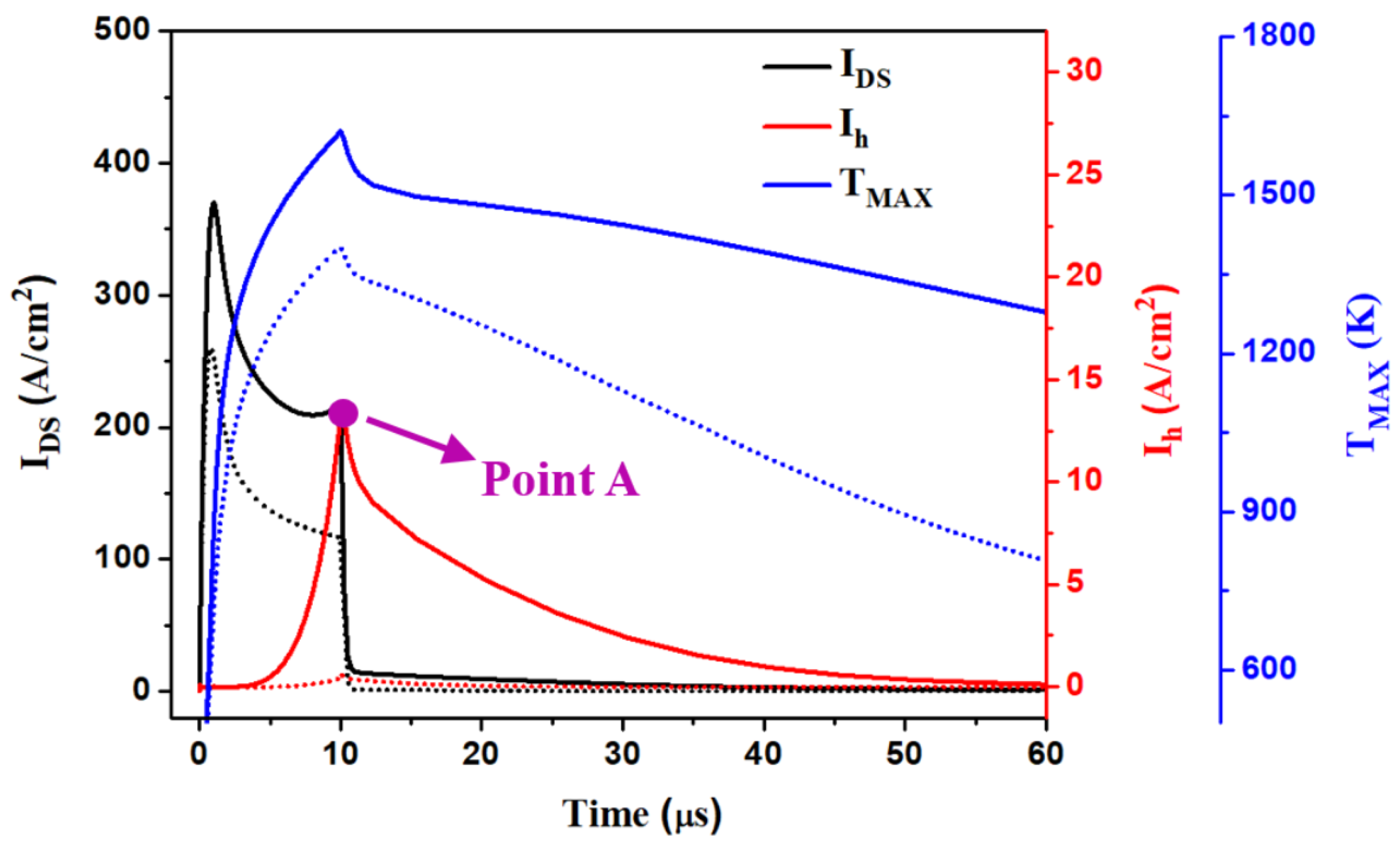

3.2. Short Circuit Characteristics

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Deboy, G.; Marz, N.; Stengl, J.P.; Strack, H.A.S.H.; Tihanyi, J.A.T.J.; Weber, H.A.W.H. A new generation of high voltage MOSFETs breaks the limit line of silicon. In IEDM Tech; IEEE: San Francisco, CA, USA, 1998; pp. 683–685. [Google Scholar]

- Udrea, F.; Deboy, G.; Fujihira, T. Superjunction Power Devices, History, Development, and Future Prospects. IEEE Trans. Electron Devices 2017, 64, 713–727. [Google Scholar] [CrossRef]

- Masuda, T.; Saito, Y.; Kumazawa, T.; Hatayama, T.; Harada, S. 0.63 mΩ∙cm2/1170 V 4H-SiC Super Junction V-Groove Trench MOSFET; IEDM: San Francisco, CA, USA, 2018; pp. 8.1.1–8.1.4. [Google Scholar]

- Kosugi, R.; Sakuma, Y.; Kojima, K.; Itoh, S.; Nagata, A.; Yatsuo, T.; Tanaka, Y.; Okumura, H. First experimental demonstration of SiC super-junction (SJ) structure by multi-epitaxial growth method. In Proceedings of the IEEE 26th International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Waikoloa, HI, USA, 15–19 June 2014; pp. 346–349. [Google Scholar]

- Zhong, X.; Wang, B.; Sheng, K. Design and experimental demonstration of 1.35 kV SiC super junction Schottky diode. In Proceedings of the 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Prague, Czech Republic, 12–16 June 2016; pp. 231–234. [Google Scholar]

- Kosugi, R.; Ji, S.; Mochizuki, K.; Adachi, K.; Segawa, S.; Kawada, Y.; Yonezawa, Y.; Okumura, H. Breaking the Theoretical Limit of 6.5 kV-Class 4H-SiC Super-Junction (SJ) MOSFETs by Trench-Filling Epitaxial Growth. In Proceedings of the 31st International Symposium on Power Semiconductor Devices and ICs (ISPSD), Shanghai, China, 19–23 May 2019; pp. 39–42. [Google Scholar]

- Wang, H.; Wang, C.; Wang, B.; Ren, N.; Sheng, K. 4H-SiC Super-Junction JFET: Design and Experimental Demonstration. IEEE Electron Device Lett. 2020, 41, 445–448. [Google Scholar] [CrossRef]

- Matsui, R.; Suzuki, D.; Tanimoto, Y.; Kitamura, M.; Kikuchihara, H.; Mattausch, H.J.; Miura-Mattausch, M. Modeling of reverse recovery effect for embedded diode in SJ MOSFET. In Proceedings of the IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), Singapore, 1–4 June 2015; pp. 375–378. [Google Scholar]

- Conrad, M.; DeDoncker, R.W. Avoiding reverse recovery effects in super junction MOSFET based half-bridges. In Proceedings of the IEEE 6th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Aachen, Germany, 22–25 June 2015; pp. 1–5. [Google Scholar]

- Yamashita, N.; Murakami, N.; Yachi, T. Conduction power loss in MOSFET synchronous rectifier with parallel-connected Schottky barrier diode. IEEE Trans. Power Electron. 1998, 13, 667–673. [Google Scholar] [CrossRef]

- Vudumula, P.; Kotamraju, S. The reverse recovery characteristics of an SiC superjunction MOSFET with a p-type Schottky diode embedded at the drain side for improved reliability. J. Comput. Electron. 2021, 20, 1187–1195. [Google Scholar] [CrossRef]

- Kotamraju, S.; Vudumula, P. Improved reverse recovery characteristics obtained in 4H-SiC double-trench superjunction MOSFET with an integrated p-type Schottky diode. IET Circuits Devices Syst. 2020, 14, 1283–1288. [Google Scholar] [CrossRef]

- Zhang, Y.; Yang, X.; Chen, H.; Li, K.; Zhong, W.; Luo, M.; Luo, J.; Zhang, B.; Bai, S. Investigating the Failure Mechanism of Short-Circuit Tests in 1.2-kV SiC JBS-Integrated MOSFETs. IEEE Trans. Electron Devices 2020, 67, 4027–4032. [Google Scholar] [CrossRef]

- Okawa, M.; Aiba, R.; Kanamori, T.; Kobayashi, Y.; Harada, S.; Yano, H.; Iwamuro, N. First Demonstration of Short-Circuit Capability for a 1.2 kV SiC SWITCH-MOS. IEEE J. Electron Devices Soc. 2019, 7, 613–620. [Google Scholar] [CrossRef]

- Aiba, R.; Matsui, K.; Baba, M.; Harada, S.; Yano, H.; Iwamuro, N. Demonstration of Superior Electrical Characteristics for 1.2 kV SiC Schottky Barrier Diode-Wall Integrated Trench MOSFET with Higher Schottky Barrier Height Metal. IEEE Electron Device Lett. 2020, 41, 1810–1813. [Google Scholar] [CrossRef]

- Okawa, M.; Kanamori, T.; Aiba, R.; Yano, H.; Iwamuro, N.; Harada, S. Analysis of 1.2 kV SiC SWITCH-MOS after Short-circuit Stress. In Proceedings of the 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Vienna, Austria, 13–18 September 2020; pp. 74–77. [Google Scholar]

- Zhang, M.; Wei, J.; Zhou, X.; Jiang, H.; Li, B.; Chen, K.J. Simulation Study of a Power MOSFET with Built-in Channel Diode for Enhanced Reverse Recovery Performance. IEEE Electron Device Lett. 2019, 40, 79–82. [Google Scholar] [CrossRef]

- Li, P.; Guo, J.; Lin, Z.; Hu, S. A Power MOSFET with P-Base Schottky Diode and Built-In Channel Diode for Fast Reverse Recovery. IEEE J. Electron Devices Soc. 2021, 9, 300–305. [Google Scholar]

- Zhou, X.; Pang, H.; Jia, Y.; Hu, D.; Wu, Y.; Tang, Y.; Xia, T.; Gong, H.; Zhao, Y. SiC Double-Trench MOSFETs with Embedded MOS-Channel Diode. IEEE Trans. Electron Devices 2020, 67, 582–587. [Google Scholar] [CrossRef]

- Zhou, X.; Gong, H.; Jia, Y.; Hu, D.; Wu, Y.; Xia, T.; Pang, H.; Zhao, Y. SiC Planar MOSFETs With Built-In Reverse MOS-Channel Diode for Enhanced Performance. IEEE J. Electron Devices Soc. 2020, 8, 619–625. [Google Scholar] [CrossRef]

- Krishnaswami, S.; Das, M.; Hull, B.; Ryu, S.H.; Scofield, J.; Agarwal, A.; Palmour, J. Gate oxide reliability of 4H-SiC MOS devices, IEEE International Reliability Physics Symposium. In Proceedings of the 43rd Annual, San Jose, CA, USA, 17–21 April 2005; pp. 592–593. [Google Scholar]

- Ye, Z.Y.; Liu, L.; Yao, Y.; Lin, M.Z.; Wang, P.F. Fabrication of a 650V Superjunction MOSFET with Built-in MOS-Channel Diode for Fast Reverse Recovery. IEEE Electron Device Lett. 2019, 40, 1159–1162. [Google Scholar] [CrossRef]

- Synopsys Inc. Sentaurus Device Manual, User Manual, Version O-2016.06; Synopsys Inc.: Mountain View, CA, USA, 2016. [Google Scholar]

- Han, Z.; Bai, Y.; Chen, H.; Li, C.; Lu, J.; Song, G.; Liu, X. A trench/planar SiC MOSFET integrated with SBD (TPSBD) for low reverse recovery charge and low switching loss. Semicond. Sci. Technol. 2020, 35, 10. [Google Scholar] [CrossRef]

- Chen, X.; Chen, H.; Shi, B.; Wang, Y.; Li, X.; Zhou, C.; Li, C.; Deng, X.; Luo, H.; Wu, Y.; et al. Investigation on Short-Circuit Characterization and Optimization of 3.3-kV SiC MOSFETs. IEEE Trans. Electron Devices 2021, 68, 184–191. [Google Scholar] [CrossRef]

- Ni, W.; Wang, X.; Xu, M.; Li, M.; Feng, C.; Xiao, H.; Jiang, L.; Li, W.; Wang, Q. Comparative Study of SiC Planar MOSFETs with Different p-Body Designs. IEEE Trans. Electron Devices 2020, 67, 1071–1076. [Google Scholar] [CrossRef]

- Baliga, B.J. Advanced High Voltage Power Device Concepts, 1st ed.; Springer: Cham, Switzerland, 2011; pp. 481–489. [Google Scholar]

- Reigosa, P.D.; Schulz, N.; Minamisawa, R. Short-circuit robustness of retrograde channel doping 1.2 kV SiC MOSFETs. Microelectron. Reliab. 2021, 120, 114117. [Google Scholar] [CrossRef]

- Sung, W.; Baliga, B.J. On Developing One-Chip Integration of 1.2 kV SiC MOSFET and JBS Diode (JBSFET). IEEE Trans. Ind. Electron. 2017, 64, 8206–8212. [Google Scholar] [CrossRef]

- Ishigaki, T.; Hayakawa, S.; Murata, T.; Masuda, T.; Oda, T.; Takayanagi, Y. Diode-Less SiC Power Module with Countermeasures Against Bipolar Degradation to Achieve Ultrahigh Power Density. IEEE Trans. Electron Devices 2020, 67, 2035–2043. [Google Scholar] [CrossRef]

- Sampath, M.; Morisette, D.T.; Cooper, J.A. Constant-Gate-Charge Scaling for Increased Short-Circuit Withstand Time in SiC Power Devices. In Proceedings of the IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 28 April–30 May 2020; pp. 1–4. [Google Scholar]

- Vudumula, P.; Kotamraju, S. Design and Optimization of 1.2-kV SiC Planar Inversion MOSFET Using Split Dummy Gate Concept for High-Frequency Applications. IEEE Trans. Electron Devices 2019, 66, 5266–5271. [Google Scholar] [CrossRef]

- Wei, J.; Liu, S.; Tong, J.; Zhang, X.; Sun, W.; Huang, A.Q. Understanding Short-Circuit Failure Mechanism of Double-Trench SiC Power MOSFETs. IEEE Trans. Electron Devices 2020, 67, 5593–5599. [Google Scholar] [CrossRef]

- Qin, H.; Dong, Y.; Xu, K.; Xu, H.; Fu, D.; Wang, S.; Zhao, C. A comprehensive study of the short-circuit characteristics of SiC MOSFETs. In Proceedings of the 12th IEEE Conference on Industrial Electronics and Applications (ICIEA), Siem Reap, Cambodia, 18–20 June 2017; pp. 332–336. [Google Scholar]

- Romano, G.; Fayyaz, A.; Riccio, M.; Maresca, L.; Breglio, G.; Castellazzi, A.; Irace, A. A Comprehensive Study of Short-Circuit Ruggedness of Silicon Carbide Power MOSFETs. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 978–987. [Google Scholar] [CrossRef]

- Castellazzi, A.; Fayyaz, A.; Yang, L.; Riccio, M.; Irace, A. Short-circuit robustness of SiC Power MOSFETs: Experimental analysis. In Proceedings of the IEEE 26th International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Waikoloa, HI, USA, 15–19 June 2014; pp. 71–74. [Google Scholar]

- Kakarla, B.; Tsibizov, A.; Stark, R.; Badstübner, I.K.; Grossner, U. Short Circuit Robustness and Carrier Lifetime in Silicon Carbide MOSFETs. In Proceedings of the 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Vienna, Austria, 13–18 September 2020; pp. 234–237. [Google Scholar]

- Aikio, A.T.; Selkälä, A. Statistical properties of Joule heating rate, electric field and conductances at high latitudes. Ann. Geophys. 2009, 27, 2661–2673. [Google Scholar] [CrossRef] [Green Version]

- Okada, M.; Kyogoku, S.; Kumazawa, T.; Saito, J.; Morimoto, T.; Takei, M.; Harada, S. Superior Short-Circuit Performance of SiC Superjunction MOSFET. In Proceedings of the 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Vienna, Austria, 13–18 September 2020; pp. 70–73. [Google Scholar]

- Namai, M.; An, J.; Yano, H.; Iwamuro, N. Investigation of shoet-circuit failure mechanisms of SiC MOSFETs by varying DC bus voltage. Jpn. J. Appl. Phys. 2018, 57, 7. [Google Scholar] [CrossRef]

| Parameter | SJ- | MCD- |

|---|---|---|

| Drift layer thickness (μm) | 10 | 10 |

| N-pillar/P-pillar doping (cm−3) | 3.75 × 1016 | 3.75 × 1016 |

| JFET doping (cm−3) | 1 × 1017 | 1 × 1017 |

| Channel length (μm) | 0.5 | 0.5 |

| N+ substrate thickness (μm) | 100 | 100 |

| N+ substrate doping (cm−3) | 1 × 1019 | 1 × 1019 |

| Channel doping (cm−3) | 1 × 1017 | 1 × 1017 |

| P+ body doping (cm−3) | 5 × 1018 | 5 × 1018 |

| N+ source doping (cm−3) | 1 × 1019 | 1 × 1019 |

| EFP region doping (cm−3) | 5 × 1018 | 5 × 1018 |

| Width of P-pillar (μm) | 1.25 | 1.25 |

| Cell pitch (μm) | 5 | 5 |

| Width of JFET (μm) | 1 | 1 |

| tox (nm) | 50 | 50 |

| tco (nm) | - | 10 |

| Distance of the active gate extend over the channel (μm) | - | 0.2 |

| SJ- | MCD- | Unit | |

|---|---|---|---|

| VF | 2.86 | 1.43 | V |

| 1 BV | 1654 | 1669 | V |

| 2 RON | 0.91 | 1.03 | mΩ·cm2 |

| BFOM | 3006 | 2704 | MW/cm2 |

| 3 CISS | 27.1 | 14.5 | nF/cm2 |

| 3 CGD | 21.2 | 4.4 | pF/cm2 |

| RON × CGD | 19.3 | 4.5 | mΩ∙pF |

| IRRM | 324 | 206 | A/cm2 |

| trr | 44 | 25 | ns |

| Qrr | 7270 | 2999 | nC/cm2 |

| SJ- | MCD- | Unit | |

|---|---|---|---|

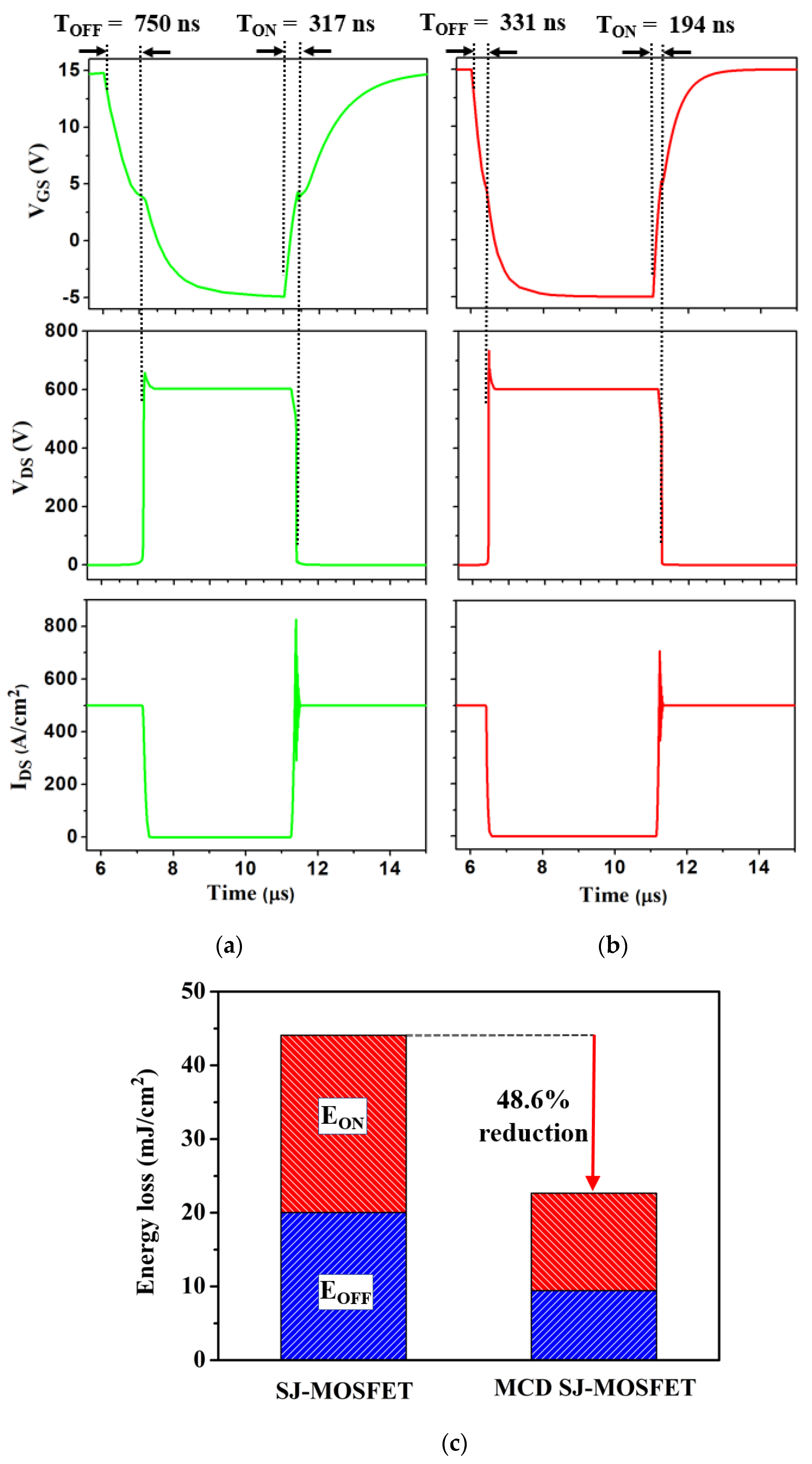

| TOFF | 750 | 331 | ns |

| TON | 317 | 194 | ns |

| EOFF | 20.03 | 9.43 | mJ/cm2 |

| EON | 24.05 | 13.24 | mJ/cm2 |

| ESW | 44.08 | 22.67 | mJ/cm2 |

| SJ- | MCD- | Unit | |

|---|---|---|---|

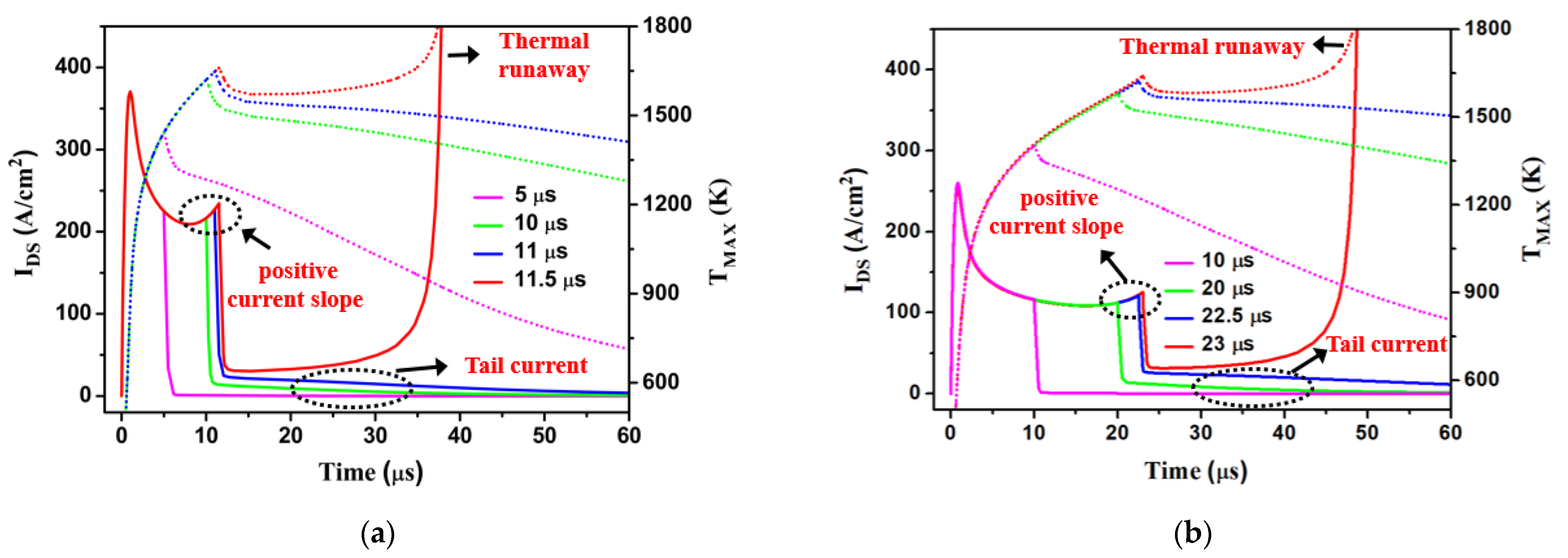

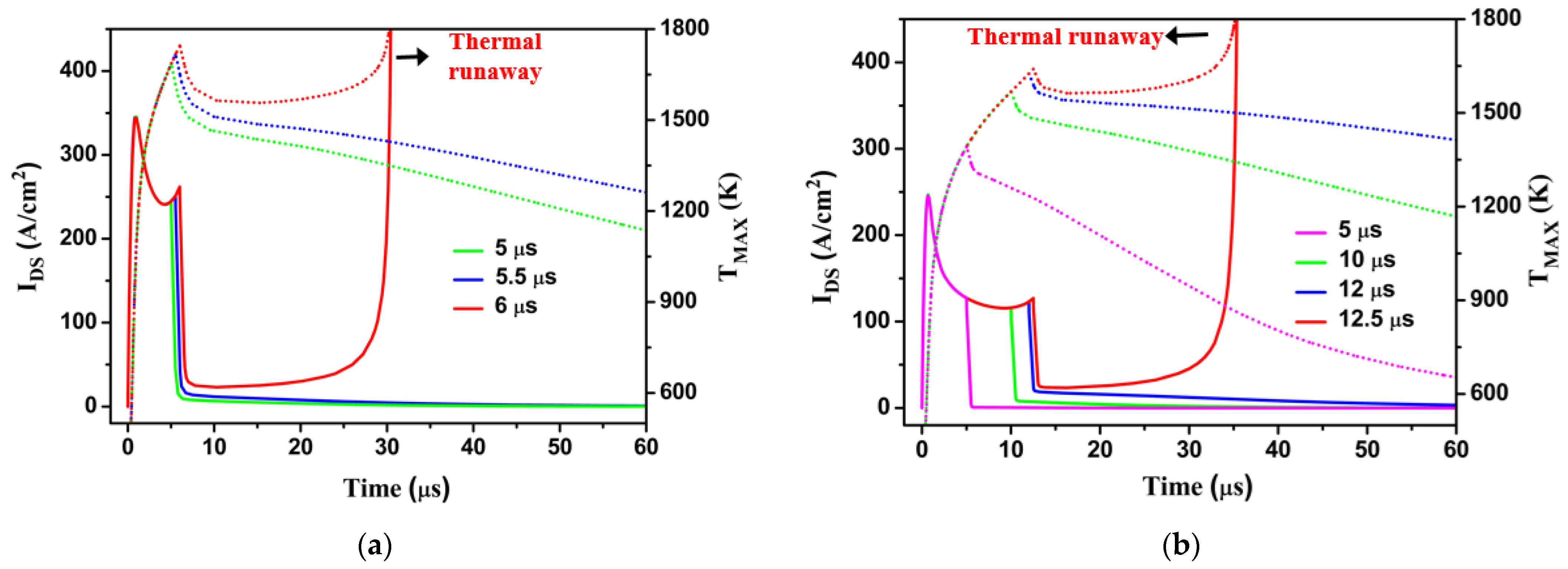

| tSC (@VDD = 400 V) | 11 | 22.5 | μs |

| tSC (@VDD = 600 V) | 5.5 | 12 | μs |

| ESC (@VDD = 400 V) | 1.05 | 1.16 | J/cm2 |

| ESC (@VDD = 600 V) | 0.86 | 0.98 | J/cm2 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yoon, J.; Kim, K. A Novel MOS-Channel Diode Embedded in a SiC Superjunction MOSFET for Enhanced Switching Performance and Superior Short Circuit Ruggedness. Electronics 2021, 10, 2619. https://doi.org/10.3390/electronics10212619

Yoon J, Kim K. A Novel MOS-Channel Diode Embedded in a SiC Superjunction MOSFET for Enhanced Switching Performance and Superior Short Circuit Ruggedness. Electronics. 2021; 10(21):2619. https://doi.org/10.3390/electronics10212619

Chicago/Turabian StyleYoon, Jongwoon, and Kwangsoo Kim. 2021. "A Novel MOS-Channel Diode Embedded in a SiC Superjunction MOSFET for Enhanced Switching Performance and Superior Short Circuit Ruggedness" Electronics 10, no. 21: 2619. https://doi.org/10.3390/electronics10212619