Improved Cascaded H-Bridge Multilevel Inverters with Voltage-Boosting Capability

Abstract

:1. Introduction

2. Proposed ICHB Multilevel Inverters

2.1. ICHB (3L)

2.2. ICHB (5L)

2.3. Cascaded Extension

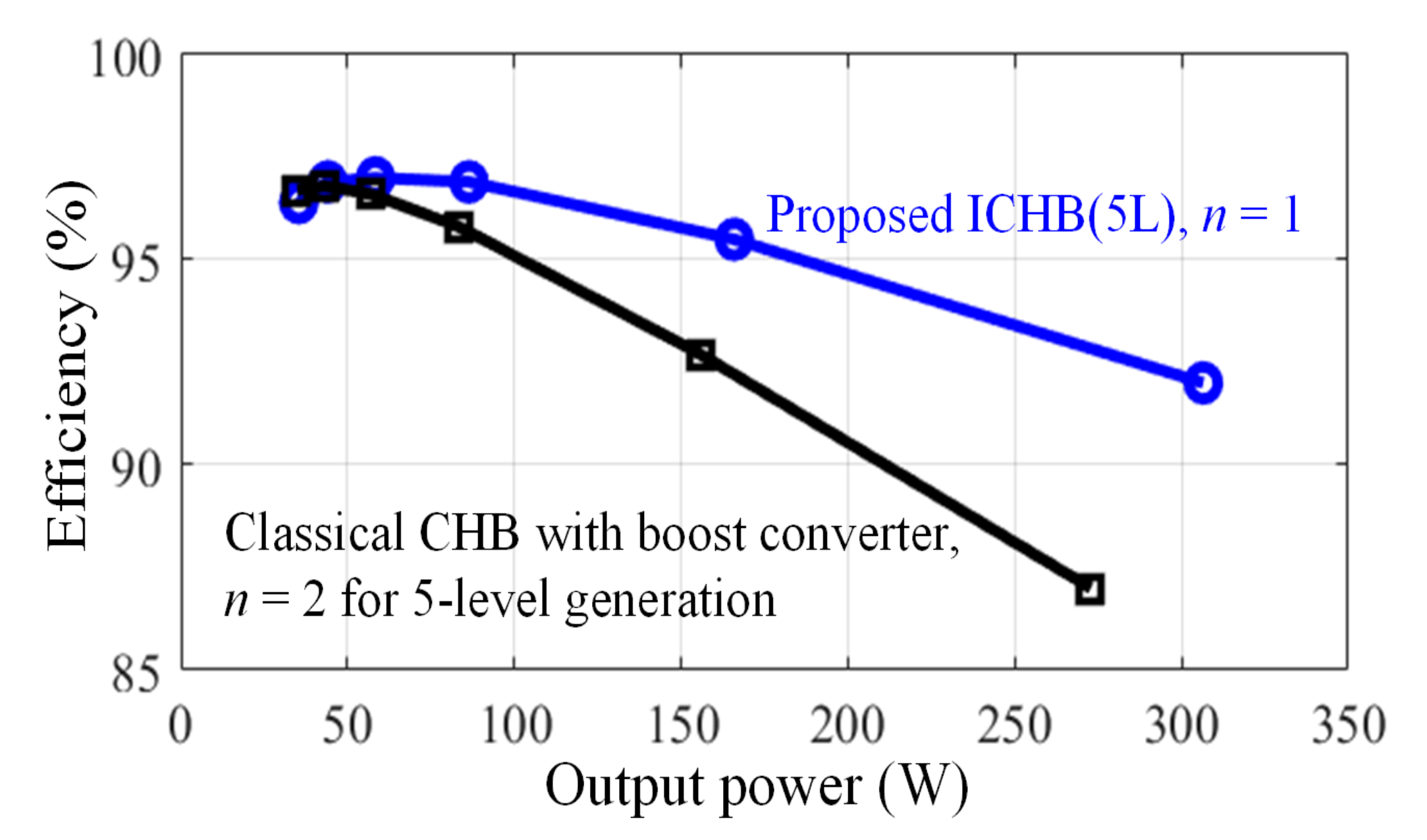

3. Comparison with CHB Multilevel Inverter

- (1)

- Reduced switch count from 6 to 5.

- (2)

- Reduced capacitor voltage stress from Vmax to DVmax.

- (3)

- Reduced total standing voltage (TSV) of the inverter from 6Vmax to 5Vmax.

- (1)

- Reduced switch count by 42%, i.e., from 12 to 7.

- (2)

- Reduced number of isolated dc sources from 2 to 1.

- (3)

- Reduced inductor count from 2 to 1.

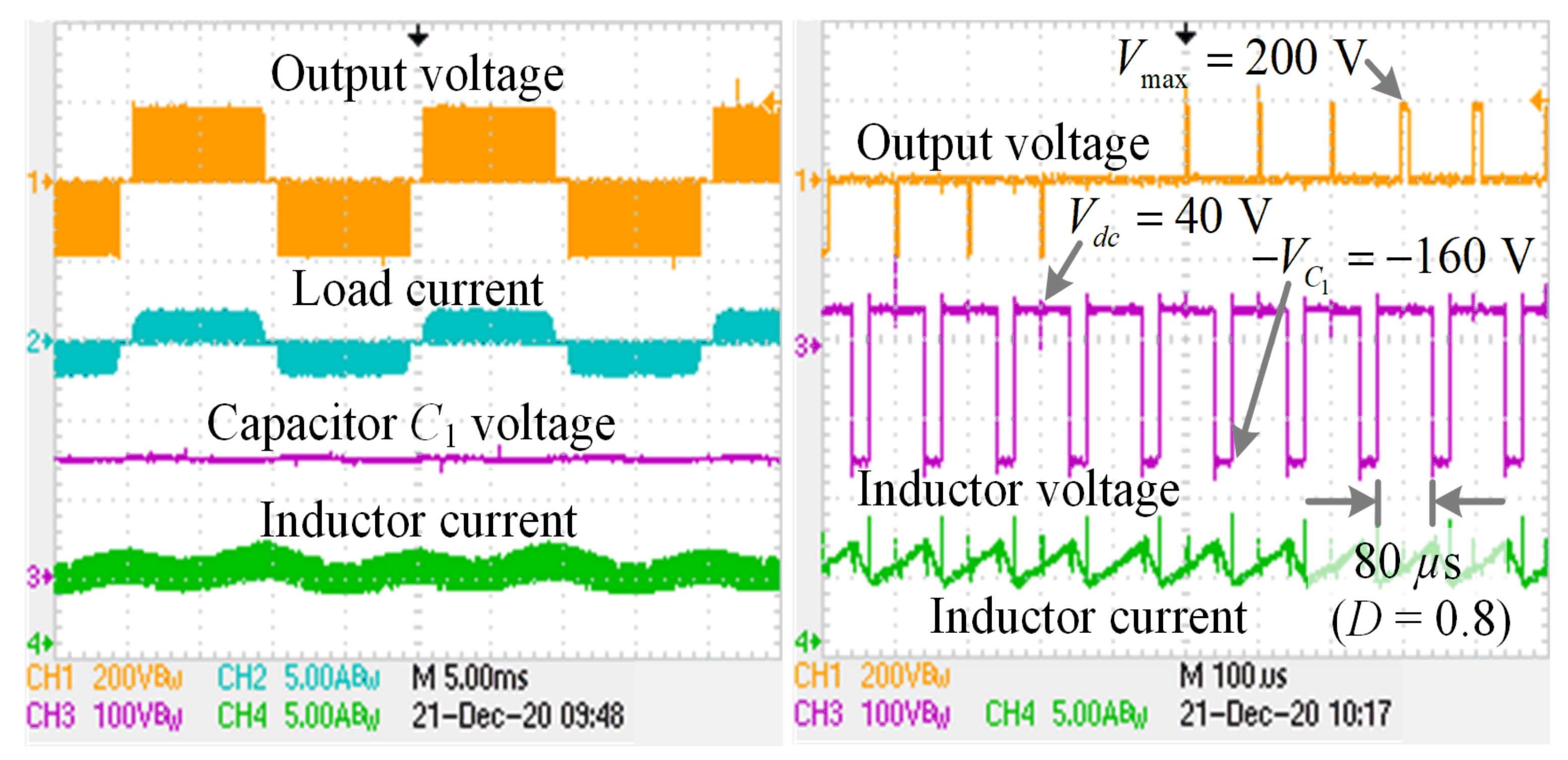

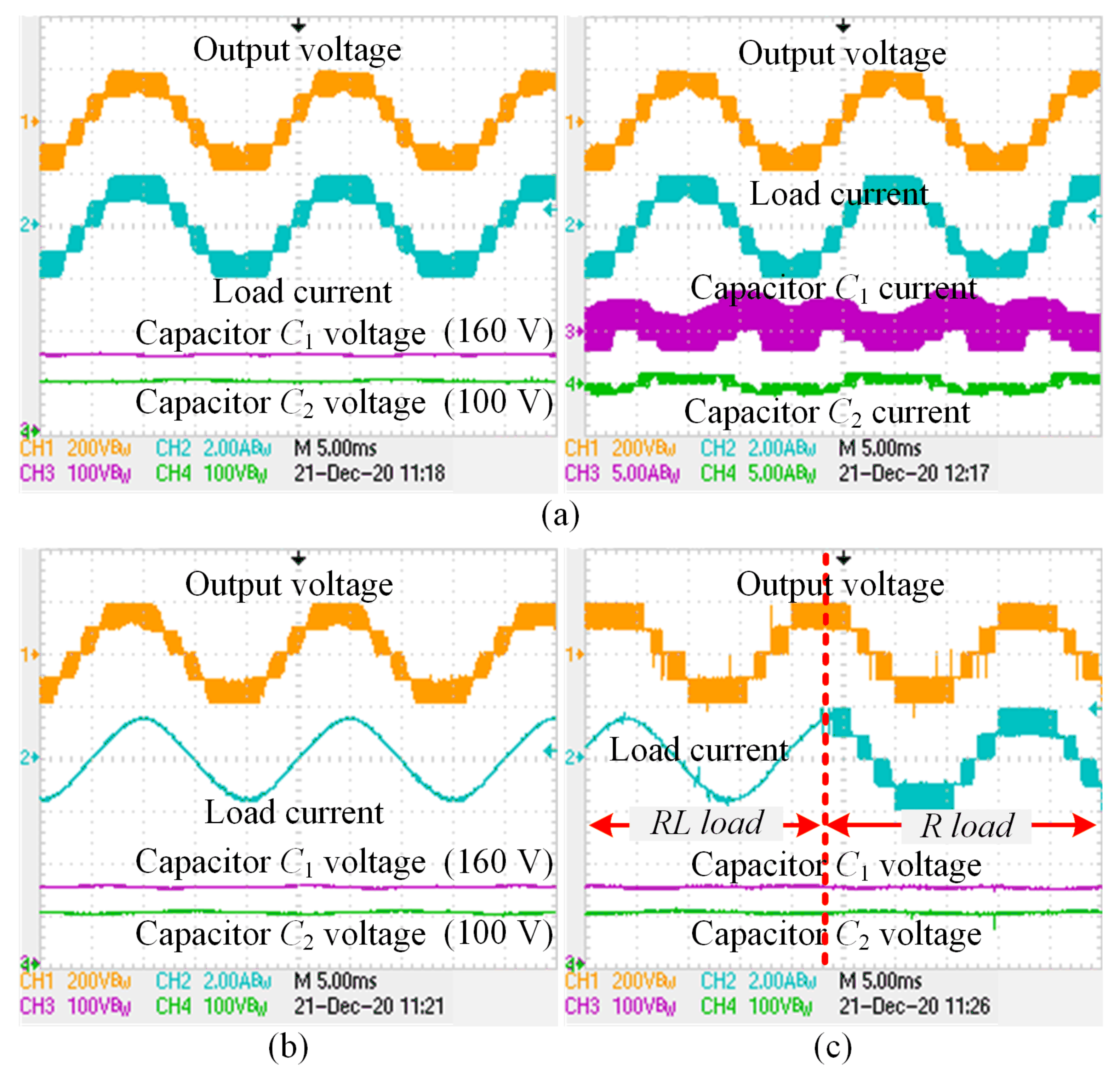

4. Simulation and Experimental Results

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- McMurray, W. Fast response stepped-wave switching power converter circuit. U.S. Patent 3581212, 25 May 1971. [Google Scholar]

- Akagi, H. Multilevel Converters: Fundamental Circuits and Systems. Proc. IEEE 2017, 105, 2048–2065. [Google Scholar] [CrossRef]

- Malinowski, M.; Gopakumar, K.; Rodriguez, J.; Pérez, M.A. A Survey on Cascaded Multilevel Inverters. IEEE Trans. Ind. Electron. 2010, 57, 2197–2206. [Google Scholar] [CrossRef]

- Cecati, C.; Ciancetta, F.; Siano, P. A Multilevel Inverter for Photovoltaic Systems with Fuzzy Logic Control. IEEE Trans. Ind. Electron. 2010, 57, 4115–4125. [Google Scholar] [CrossRef]

- Rana, R.A.; Patel, S.A.; Muthusamy, A.; Lee, C.w.; Kim, H.-J. Review of Multilevel Voltage Source Inverter Topologies and Analysis of Harmonics Distortions in FC-MLI. Electronics 2019, 8, 1329. [Google Scholar] [CrossRef] [Green Version]

- Ye, M.; Ren, W.; Wei, Q.; Song, G.; Miao, Z. Research on Modified Hybrid Frequency Modulation Technology of Type-III Asymmetric CHB Multilevel Inverters. Electronics 2020, 9, 263. [Google Scholar] [CrossRef] [Green Version]

- Tayyab, M.; Sarwar, A.; Khan, I.; Tariq, M.; Hussan, M.R.; Murshid, S.; Alhosaini, W. A Single Source Switched-Capacitor 13-Level Inverter with Triple Voltage Boosting and Reduced Component Count. Electronics 2021, 10, 2321. [Google Scholar] [CrossRef]

- Vijeh, M.; Rezanejad, M.; Samadaei, E.; Bertilsson, K. A General Review of Multilevel Inverters Based on Main Submodules: Structural Point of View. IEEE Trans. Power Electron. 2019, 34, 9479–9502. [Google Scholar] [CrossRef]

- Su, G.J. Multilevel DC-link inverter. IEEE Trans. Ind. Appl. 2005, 41, 848–854. [Google Scholar] [CrossRef]

- Hosseinzadeh, M.A.; Sarebanzadeh, M.; Rivera, M.; Babaei, E.; Wheeler, P. A Reduced Single-Phase Switched-Diode Cascaded Multilevel Inverter. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 9, 3556–3569. [Google Scholar] [CrossRef]

- Samadaei, E.; Gholamian, S.A.; Sheikholeslami, A.; Adabi, J. An Envelope Type (E-Type) Module: Asymmetric Multilevel Inverters with Reduced Components. IEEE Trans. Ind. Electron. 2016, 63, 7148–7156. [Google Scholar] [CrossRef]

- Samadaei, E.; Sheikholeslami, A.; Gholamian, S.A.; Adabi, J. A Square T-Type (ST-Type) Module for Asymmetrical Multilevel Inverters. IEEE Trans. Power Electron. 2018, 33, 987–996. [Google Scholar] [CrossRef]

- Alishah, R.S.; Hosseini, S.H.; Babaei, E.; Sabahi, M. Optimal Design of New Cascaded Switch-Ladder Multilevel Inverter Structure. IEEE Trans. Ind. Electron. 2017, 64, 2072–2080. [Google Scholar] [CrossRef]

- Lee, S.S.; Lim, C.S.; Siwakoti, Y.P.; Lee, K.B. Dual-T-Type 5-Level Cascaded Multilevel Inverter (DTT-5L-CMI) with Double Voltage Boosting Gain. IEEE Trans. Power Electron. 2020, 35, 9522–9529. [Google Scholar] [CrossRef]

- Tran, V.-T.; Nguyen, M.-K.; Ngo, C.-C.; Choi, Y.-O. Three-Phase Five-Level Cascade Quasi-Switched Boost Inverter. Electronics 2019, 8, 296. [Google Scholar] [CrossRef] [Green Version]

- Lee, S.S.; Yang, Y.; Siwakoti, Y.P.; Lee, K.B. A Novel Boost Cascaded Multilevel Inverter. IEEE Trans. Ind. Electron. 2021, 68, 8072–8080. [Google Scholar] [CrossRef]

| 3-Level | 5-Level | |||

|---|---|---|---|---|

| CHB (Figure 1a, n = 1) | Proposed ICHB (3L) | CHB (Figure 1a, n = 2) | Proposed ICHB (5L) | |

| Switch | 6 | 5 | 12 | 7 |

| DC source | 1 | 1 | 2 | 1 |

| Inductor | 1 | 1 | 2 | 1 |

| Capacitor | 1 | 1 | 2 | 2 |

| Gain | M/(1 − D) | M/(1 − D) | M/(1 − D) | M/(1 − D) |

| 1 | D | 0.5 | D | |

| − | − | 0.5 | 0.5 | |

| 6 | 5 | 6 | 6 | |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, S.S.; Yang, Y.; Siwakoti, Y.P.; Barzegarkhoo, R. Improved Cascaded H-Bridge Multilevel Inverters with Voltage-Boosting Capability. Electronics 2021, 10, 2801. https://doi.org/10.3390/electronics10222801

Lee SS, Yang Y, Siwakoti YP, Barzegarkhoo R. Improved Cascaded H-Bridge Multilevel Inverters with Voltage-Boosting Capability. Electronics. 2021; 10(22):2801. https://doi.org/10.3390/electronics10222801

Chicago/Turabian StyleLee, Sze Sing, Yongheng Yang, Yam P. Siwakoti, and Reza Barzegarkhoo. 2021. "Improved Cascaded H-Bridge Multilevel Inverters with Voltage-Boosting Capability" Electronics 10, no. 22: 2801. https://doi.org/10.3390/electronics10222801

APA StyleLee, S. S., Yang, Y., Siwakoti, Y. P., & Barzegarkhoo, R. (2021). Improved Cascaded H-Bridge Multilevel Inverters with Voltage-Boosting Capability. Electronics, 10(22), 2801. https://doi.org/10.3390/electronics10222801