CDM Protection Test Structure for I/O Cells in a Submicronic Technology

Abstract

:1. Introduction

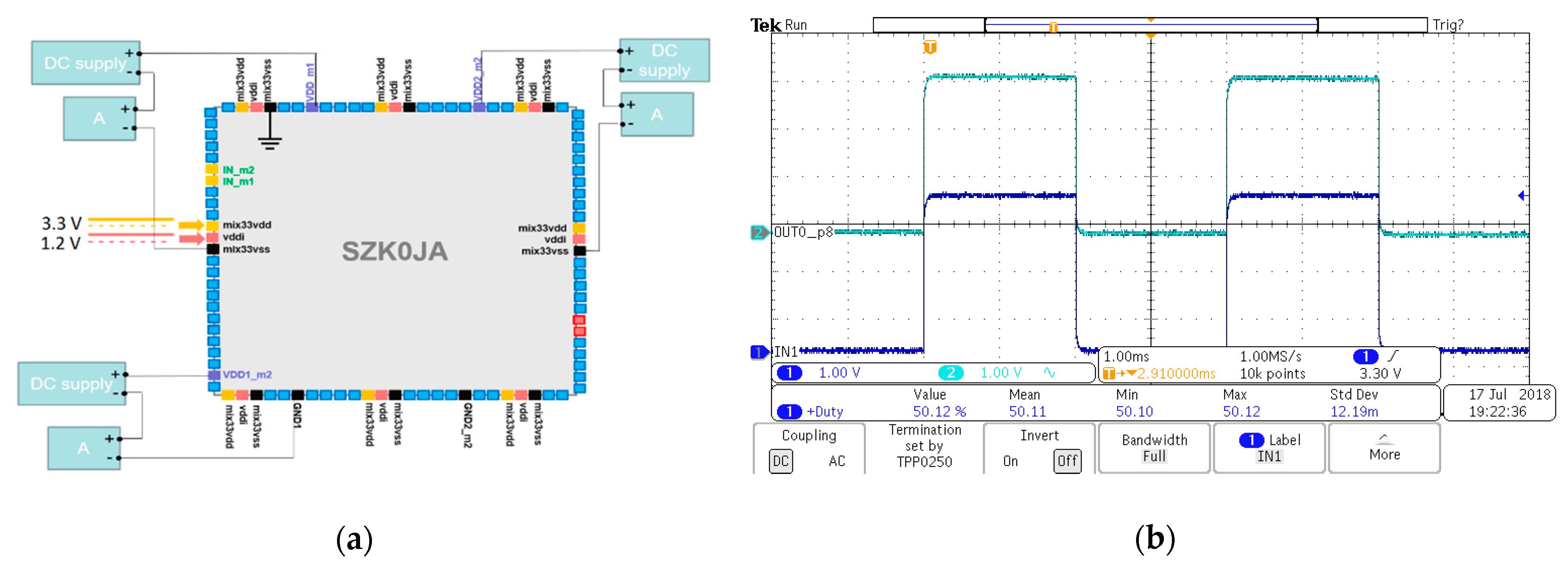

2. Proposed Structure and Implementation

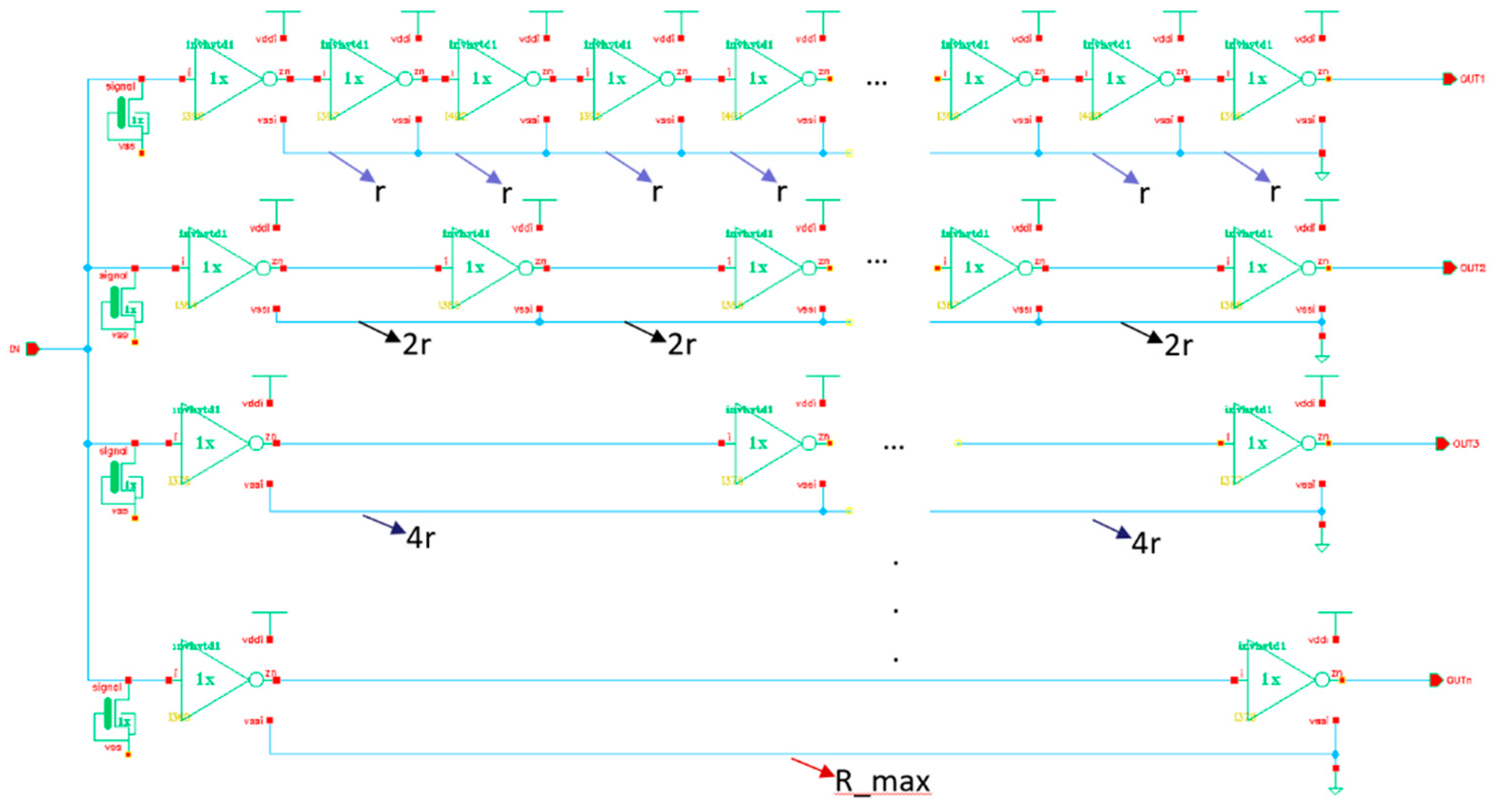

2.1. Proposed Structure

- CDM is our major ESD concern and the focus of the proposed structure. The design of the proposed test-chip will permit to have a quantifiable ground resistor value in relationship with different CDM stress voltages according to JEDEC (Joint Electron Device Engineering Council) [11].

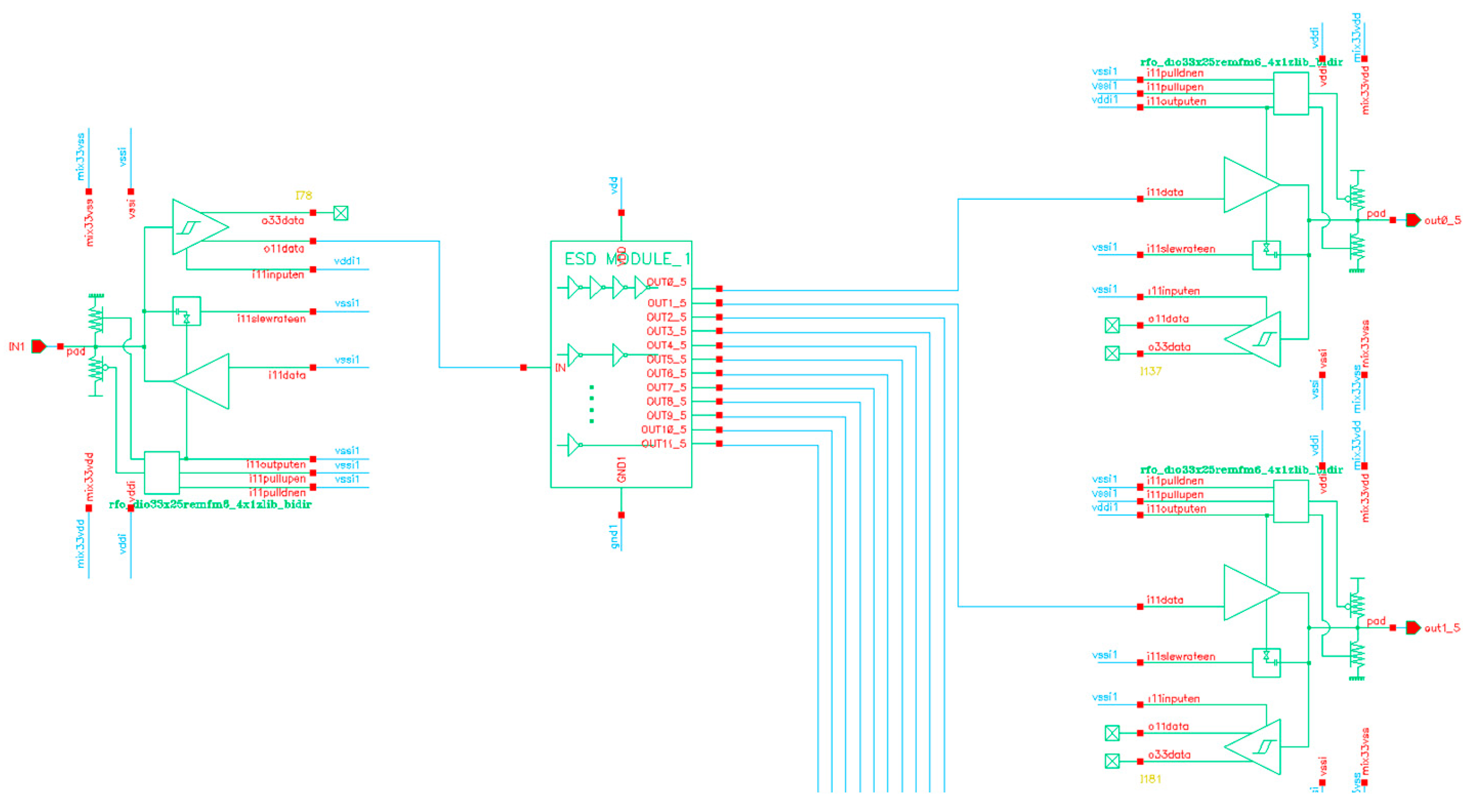

- The I/O structures that will be used to connect the defined structure from the core to the package’s pins were previously designed and CDM tested and validated with a high CDM stress level. Hence the I/O structures do not constitute a threat for the present discussion.

- Extra CDM protections such as GGNMOS (grounded gate NMOS) devices will be used to protect the gate oxide of the driver. The receiver in the structures that will be shortly defined are the object of our investigation.

- (a)

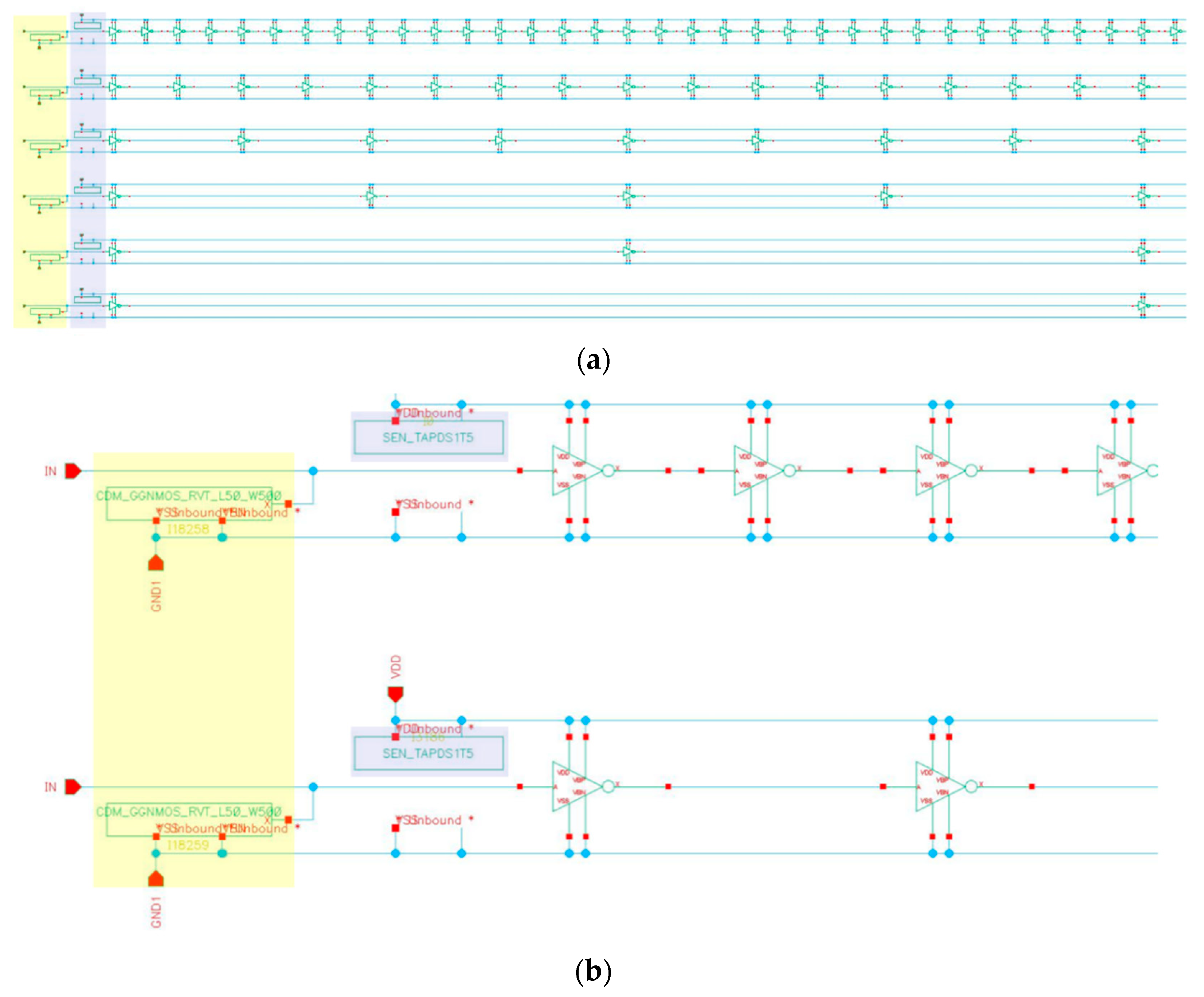

- Input GGNMOS protection structure was added at the beginning of each row to protect the gates of the first inverter in case of ESD stress. Because the aim of the proposed structure is to see which is the maximum wire resistance where CDM stress does no harm, it was mandatory for the added input GGNMOS so that the eventual CDM faults in the output would be due to the length of the wires and not because of unprotected input signals. The input protection GGNMOS was highlighted in Figure 5b with semi-transparent yellow boxes.

- (b)

- Tap cells were added in order to correctly connect the bulk from the inverters from GGNMOS to corresponding potentials. Tap cells provide the nwell and substrate contacts, connecting pmos bulk (VBP) and nmos bulk (VBN) to the specified supply potentials. The purpose of this tap cell is for normal usage without bias or retention. Key characteristics are: VBP internally connected to the supply (VDD) and VBN internally connected to the ground (VSS). Tap cells were also highlighted in Figure 5b.

- (c)

- Filler cells were added in the layout to overcome design rule checking (DRC) errors. If a block has a halo/placement keepout region around it when it is placed on a chip, then the NOPG (fille cell without power/ground rails) end caps can be placed in the halo. Halos around blocks are used to provide room for routing power/ground supply rings, and for routing signal nets connecting to the block’s input/output pins. The use of NOPG cells in the halo does not consume any routing tracks the way fillers with VDD/VSS rails.

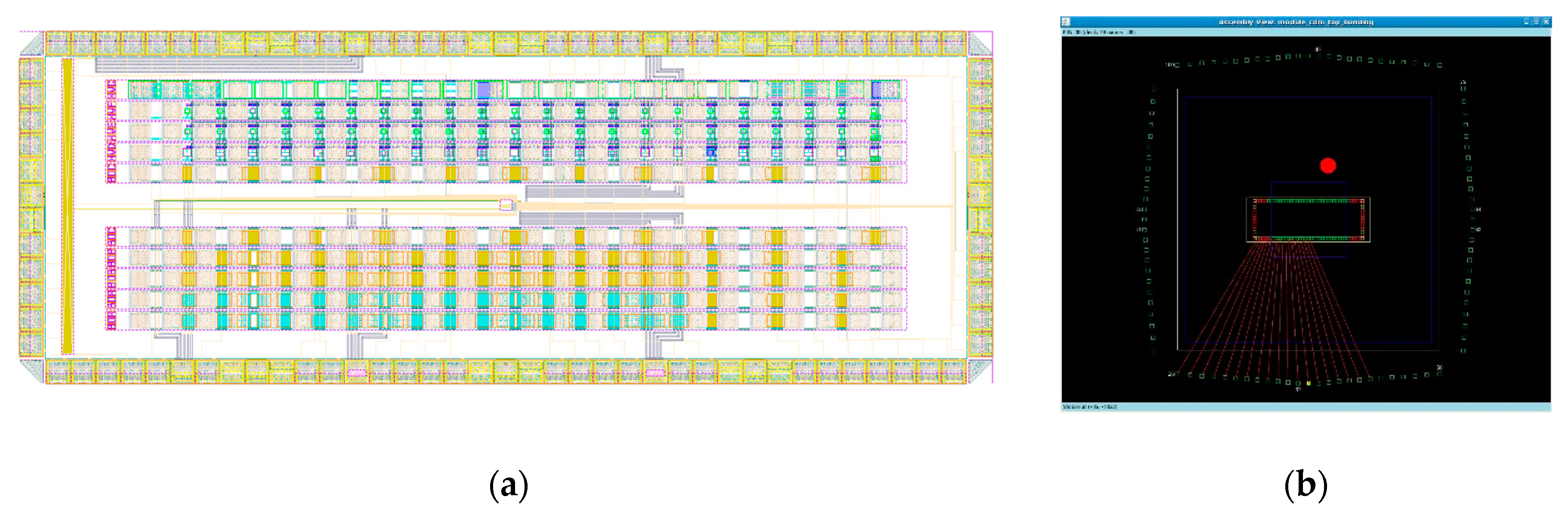

2.2. Test-Chip Implementation

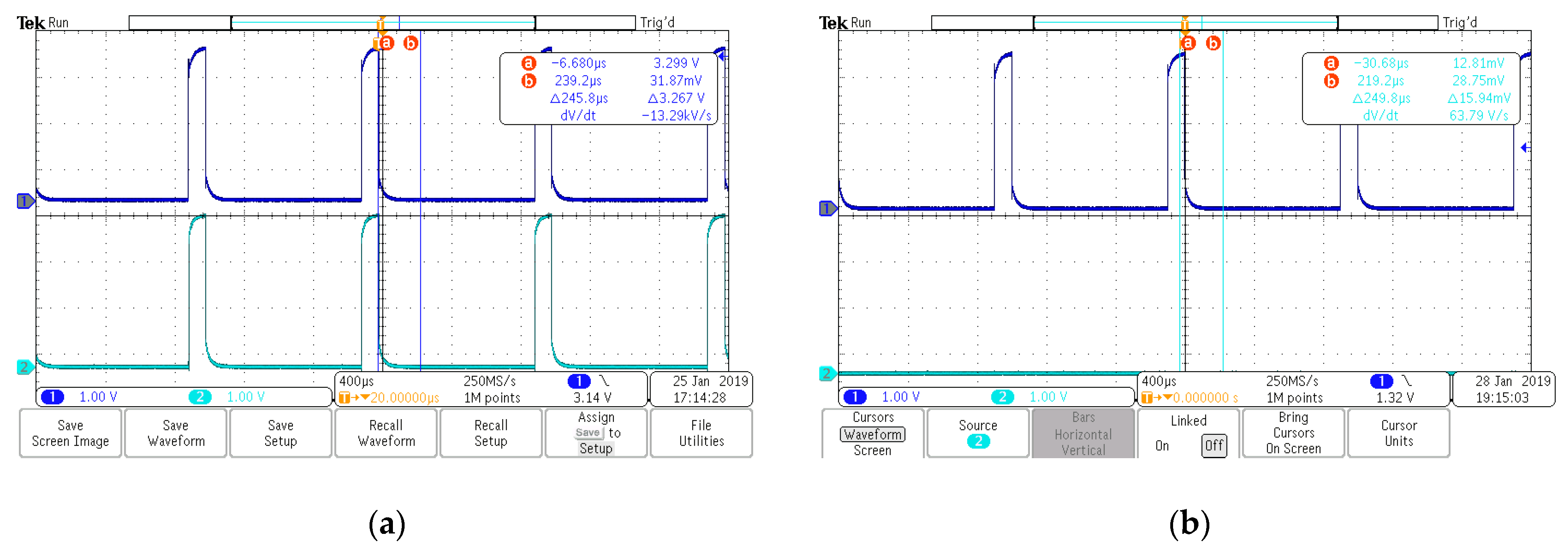

3. Testing the Implemented Structures

3.1. Functionality Testing

3.2. Electrostatic Discharge–Charge Device Model (ESD–CDM) Stress

- Only the module’s ground and supplies to be stressed.

- Only positive zaps per each supply/ground pin.

- To be used three consecutive zaps per each pin.

- To be used three samples per identical stress level.

3.3. Functionality Testing Post ESD–CDM Stress

- All samples have good functionality after being stressed at 500 V and 1 kV. Therefore, for 500 V CDM stress all implemented ground wire resistors are safe to be used for the considered submicron technology. According to the latest research [13,14], CDM stress voltage at 500 V is enough to assure CDM protection for integrated circuits.

- For 1.5 kV stress voltage, there are two situations: one sample failed for the row corresponding to 1.14 Ohm per ground length and two samples failed for the row with the maximum resistance of 1.38 kohm. We can conclude that for ground track resistance of 1.38 kohm, the part will fail when stressed at 1 kV CDM stress since 2 out of 3 samples failed. Regarding the second row corresponding to 1.14 ohm that had one sample failed, it can be considered a singular situation given the fact that the other two samples had good behavior at the same CDM voltage stress and all other rows with resistance higher than that passed the test.

- For 2 kV stress voltage, there is only one sample that failed for the row corresponding to 1.14 ohm and it can be considered a non-repetitive pattern with no conclusion to be drawn, especially because on the next other cases with higher track resistivity there is no fail on neither of the samples. On the other hand, for the last row of the module corresponding to the maximum resistance of 1.38 kohm all three samples failed after performing the functionality test. The conclusion here is clear: the resistance of the supply tracks cannot exceed 1.38 kohm if CDM stress is above 1 kV.

4. Discussion

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- ESD Association. Fundamentals of Electrostatic Discharge, Part Five—Device Sensitivity and Testing; ESD Association: Rome, NY, USA, 2010; p. 2. [Google Scholar]

- ESD Association. Fundamentals of Electrostatic Discharge, Part 1—An Introduction to ESD; ESD Association: Rome, NY, USA, 2010. [Google Scholar]

- Duvvury, C.; Amerasekera, A. Advanced CMOS protection device trigger mechanisms during CDM. IEEE Trans. Compon. Packag. Manuf. Technol. Part C 1996, 19, 169–177. [Google Scholar] [CrossRef]

- Neil, D.M.H.; Weste, H.E. CMOS VLSI Design, a Circuits and Systems Perspective, 4th ed.; Pearson Education Inc.: London, UK, 2011; pp. 593–594. [Google Scholar]

- Ker, M.D.; Hsiao, Y.W. CDM ESD protection in CMOS integrated circuits. In Proceedings of the 2008 Argentine School of Micro-Nanoelectronics, Technology and Applications, Buenos Aires, Argentina, 18–19 September 2008; pp. 61–66. [Google Scholar]

- Aharoni, E.; Parvin, A.; Vaserman, Y.; Grund, E. Empirical ESD simulation flow for ESD protection circuits based on snapback devices. In Proceedings of the 2016 38th Electrical Overstress/Electrostatic Discharge Symposium (EOS/ESD), Garden Grove, CA, USA, 11–16 September 2016; pp. 1–10. [Google Scholar] [CrossRef]

- Okushima, M. ESD protection design for mixed-power domains in 90 nm CMOS with new efficient power clamp and GND current trigger (GCT) technique. In Proceedings of the 2006 Electrical Overstress/Electrostatic Discharge Symposium, Anaheim, CA, USA, 10–15 September 2006; pp. 205–213. [Google Scholar]

- Chen, S.; Ker, M.; Hung, H. Active ESD Protection Design for Interface Circuits between Separated Power Domains against Cross-Power-Domain ESD Stresses. IEEE Trans. Device Mater. Reliab. 2008, 8, 549–560. [Google Scholar] [CrossRef]

- Watanabe, K.; Hiraoka, T.; Sato, K.; Sei, T.; Numata, K. New protection techniques and test chip design for achieving high CDM robustness. In Proceedings of the EOS/ESD 2008—2008 30th Electrical Overstress/Electrostatic Discharge Symposium, Tucson, AZ, USA, 7–11 September 2008; pp. 332–338. [Google Scholar]

- Etherton, M.; Ruth, S.; Miller, J.W.; Agarwal, R.; Bhooshan, R.; Ershov, M.; Cadjan, M.; Feinberg, Y.; Srinivasan, K.; Chang, N.; et al. A new full-chip verification methodology to prevent CDM oxide failures. In Proceedings of the 2015 37th Electrical Overstress/Electrostatic Discharge Symposium (EOS/ESD), Reno, NV, USA, 27 September–2 October 2015; pp. 1–10. [Google Scholar] [CrossRef]

- Recommended ESD-CDM Target Levels; JEDEC Publication JEP157; JEDEC Solid State Technology Association: Arlington County, VA, USA, 2009; p. 11.

- Charged Device Model (CDM) Electrostatic Discharge Test. AEC—Q100-011 Rev-C1. 12 March 2013. Available online: http://www.aecouncil.com/Documents/AEC_Q100-011C1.pdf (accessed on 12 May 2017).

- Kim, S.; Sithanandam, R.; Seo, W.; Lee, M.; Cho, S.; Park, J.; Kwon, H.; Kim, N.; Jeon, C. Technology Scaling of ESD Devices in State-of-the-ArtFinFET Technologies. In Proceedings of the 2020 IEEE Custom Integrated Circuits Conference (CICC), Boston, MA, USA, 22–25 March 2020; pp. 1–6. [Google Scholar] [CrossRef]

- White Paper 1: A Case for Lowering Component Level HBM/MM ESD Specifications and Requirements; Industry Council on ESD Target Levels, June 2018; Available online: https://www.esdindustrycouncil.org/ic/docs/industry%20council_esd_target_levels_whitepaper1_rev4.0_june2018%20final.pdf (accessed on 28 December 2020).

- Shukla, V.; Jack, N.; Rosenbaum, E. Predictive simulation of CDM events to study effects of package, substrate resistivity and placement of ESD protection circuits on reliability of integrated circuits. In Proceedings of the 2010 IEEE International Reliability Physics Symposium, Anaheim, CA, USA, 2–6 May 2010; pp. 485–493. [Google Scholar] [CrossRef]

- Ershov, M.; Feinberg, Y.; Cadjan, M.; Klein, D.; Etherton, M. EDA software for verification of metal interconnects in ESD protection networks at chip, block, and cell level. In Proceedings of the 2013 35th Electrical Overstress/Electrostatic Discharge Symposium, Las Vegas, NV, USA, 10–12 September 2013; pp. 1–7. [Google Scholar]

- Abessolo-Bidzo, D.; Smedes, T.; Huitsing, A.J. CDM Simulation Based on Tester, Package and Full Integrated Circuit Modeling: Case Study. IEEE Trans. Electron Devices 2012, 59, 2869–2875. [Google Scholar] [CrossRef]

- Shukla, V.; Boselli, G.; Dissegna, M.; Duvvury, C.; Sankaralingam, R.; Rosenbaum, E. Prediction of Charged Device Model Peak Discharge Current for Microelectronic Components. IEEE Trans. Device Mater. Reliab. 2014, 14, 801–809. [Google Scholar] [CrossRef]

- Olson, N.; Shukla, V.; Rosenbaum, E. Test Chip design for study of CDM related failures in SoC designs. In Proceedings of the 2011 International Reliability Physics Symposium, Monterey, CA, USA, 10–14 April 2011; pp. EL.3.1–EL.3.6. [Google Scholar] [CrossRef]

- Abessolo-Bidzo, D.; Smedes, T.; de Jong, P.C. A study of the effect of remote CDM clamps in integrated circuits. In Proceedings of the 2015 37th Electrical Overstress/Electrostatic Discharge Symposium (EOS/ESD), Reno, NV, USA, 27 September–2 October 2015; pp. 1–8. [Google Scholar] [CrossRef]

- Troussier, C.; Bourgeat, J.; Simeu, E.; Arnould, J.-D.; Jimenez, J.; Jacquier, B. Study of Inter-Power Domain Failures during a CDM Event. In Proceedings of the 2020 42nd Annual EOS/ESD Symposium (EOS/ESD), Reno, NV, USA, 13–18 September 2020; pp. 1–5. [Google Scholar]

- Brennan, C.J.; Sloan, J.; Picozzi, D. CDM failure modes in a 130 nm ASIC technology. In Proceedings of the 2004 Electrical Overstress/Electrostatic Discharge Symposium, Grapevine, TX, USA, 19–23 September 2004; pp. 1–5. [Google Scholar] [CrossRef]

- Di Biccari, L.; Boroni, A.; Castelnovo, A.; Zullino, L.; Cerati, L.; Wolf, H.; Weber, J.; Andreini, A. Impact of Alternative CDM Methods on HV ESD Protections Behavior. In Proceedings of the 2020 42nd Annual EOS/ESD Symposium (EOS/ESD), Reno, NV, USA, 13–18 September 2020; pp. 1–10. [Google Scholar]

- Dumalkina, E.; Semenov, O. Optimization of Metal Interconnects in I/O Cells and Banks to Improve Robustness of ESD Protection Network in 16 nm FinFet Technology. In Proceedings of the 2020 International Semiconductor Conference (CAS), Sinaia, Romania, 7–9 October 2020; pp. 69–72. [Google Scholar] [CrossRef]

- Zhou, Y.; Hajjar, J. CDM ESD failure modes and VFTLP testing for protection evaluation. In Proceedings of the 2008 9th International Conference on Solid-State and Integrated-Circuit Technology, Beijing, China, 20–23 October 2008; pp. 333–336. [Google Scholar] [CrossRef]

- Brennan, C.J.; Kozhaya, J.N.; Proctor, R.A.; Sloan, J.; Chang, S.; Sundquist, J.; Lowe, T. ESD design automation for a 90nm ASIC design system. In Proceedings of the 2004 Electrical Overstress/Electrostatic Discharge Symposium, Grapevine, TX, USA, 19–23 September 2004; pp. 1–8. [Google Scholar] [CrossRef]

- Brodbeck, T.; Esmark, K.; Stadler, W. CDM tests on interface test chips for the verification of ESD protection concepts. In Proceedings of the 2007 29th Electrical Overstress/Electrostatic Discharge Symposium (EOS/ESD), Anaheim, CA, USA, 16–21 September 2007; pp. 1A.1-1–1A.1-8. [Google Scholar] [CrossRef]

- Alvarez, D.; Kupfer, C.; Kruppa, J.; Trivedi, N.J.; Chakravarthy, S.N. CDM single power domain failures in 90 nm. In Proceedings of the 2013 35th Electrical Overstress/Electrostatic Discharge Symposium, Las Vegas, NV, USA, 10–12 September 2013; pp. 1–8. [Google Scholar]

| Row Number | No. of Inverters | Resistance [ohm] |

|---|---|---|

| 1 | 2346 | 0.57 |

| 2 | 1172 | 1.14 |

| 3 | 587 | 2.28 |

| 4 | 306 | 4.56 |

| 5 | 153 | 9.12 |

| 6 | 77 | 18.24 |

| 7 | 39 | 36.58 |

| 8 | 20 | 72.65 |

| 9 | 10 | 155.44 |

| 10 | 5 | 344.78 |

| 11 | 3 | 690.55 |

| 12 | 2 | 1387.17 |

| Wire Resistance [ohm] | CDM Stress Applied | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 V | 500 V | 500 V | 500 V | 1000 V | 1000 V | 1000 V | 1500 V | 1500 V | 1500 V | 2000 V | 2000 V | 2000 V | |

| 0.57 | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass | fail | pass |

| 1.14 | pass | pass | pass | pass | pass | pass | pass | fail | pass | pass | pass | pass | pass |

| 2.28 | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass |

| 4.56 | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass |

| 9.12 | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass |

| 18.24 | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass |

| 36.58 | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass |

| 72.65 | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass |

| 155.44 | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass |

| 344.78 | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass |

| 690.55 | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass | pass |

| 1387.17 | pass | pass | pass | pass | pass | pass | pass | fail | pass | fail | fail | fail | fail |

| Other Relevant Papers | Technology Node | Package Used | Different Power Domains | CDM Stress Method | CDM Stress Voltage | Maximum Ground Wire Resistance |

|---|---|---|---|---|---|---|

| [20] | 250 nm | LQFP64 (Low Profile Quad Flat Package) | yes | vf-TLP (very fast TLP) | 750 V | 1 kohm |

| [21] | - | CDIP (Ceramic Dual Inline Package) | yes | vf-TLP | 750 V | 5.8 kohm (GGNMOS added) |

| [22] | 130 m | Flip-chip | no | - | 500 V | 1.5 ohm |

| [28] | 90 nm | BGA (Ball Grid Array) | no | - | 600 V | 600 ohm |

| This paper | 40 nm | LQFP100 | no | FICDM (Field-Induced CDM) | 1 kV | 1.3 kohm |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Dobre, M.-D.; Coll, P.; Brezeanu, G. CDM Protection Test Structure for I/O Cells in a Submicronic Technology. Electronics 2021, 10, 443. https://doi.org/10.3390/electronics10040443

Dobre M-D, Coll P, Brezeanu G. CDM Protection Test Structure for I/O Cells in a Submicronic Technology. Electronics. 2021; 10(4):443. https://doi.org/10.3390/electronics10040443

Chicago/Turabian StyleDobre, Mihaela-Daniela, Philippe Coll, and Gheorghe Brezeanu. 2021. "CDM Protection Test Structure for I/O Cells in a Submicronic Technology" Electronics 10, no. 4: 443. https://doi.org/10.3390/electronics10040443