Analysis of a Wide Voltage Hybrid Soft Switching Converter

Abstract

1. Introduction

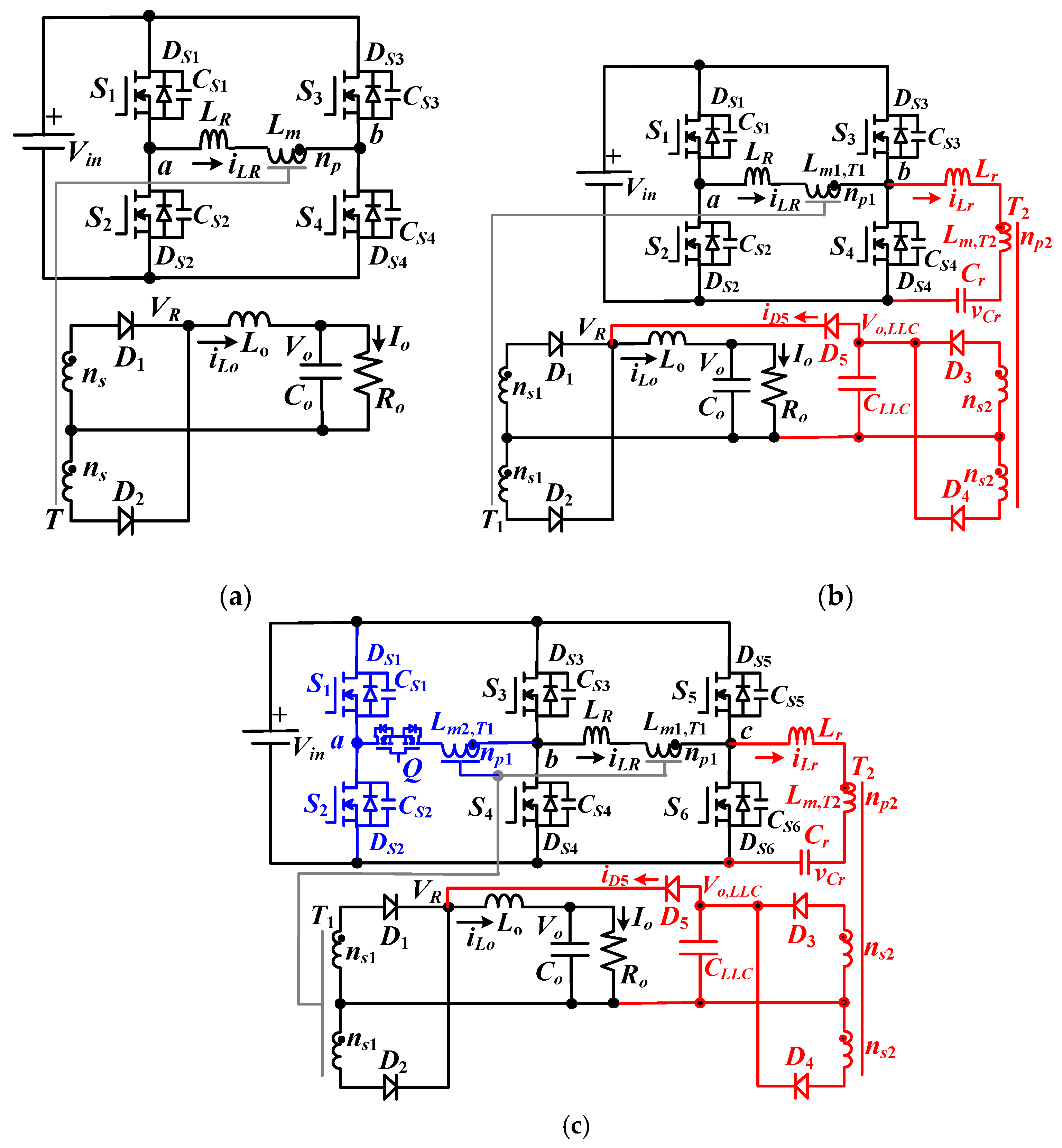

2. Structure of the Proposed Converter

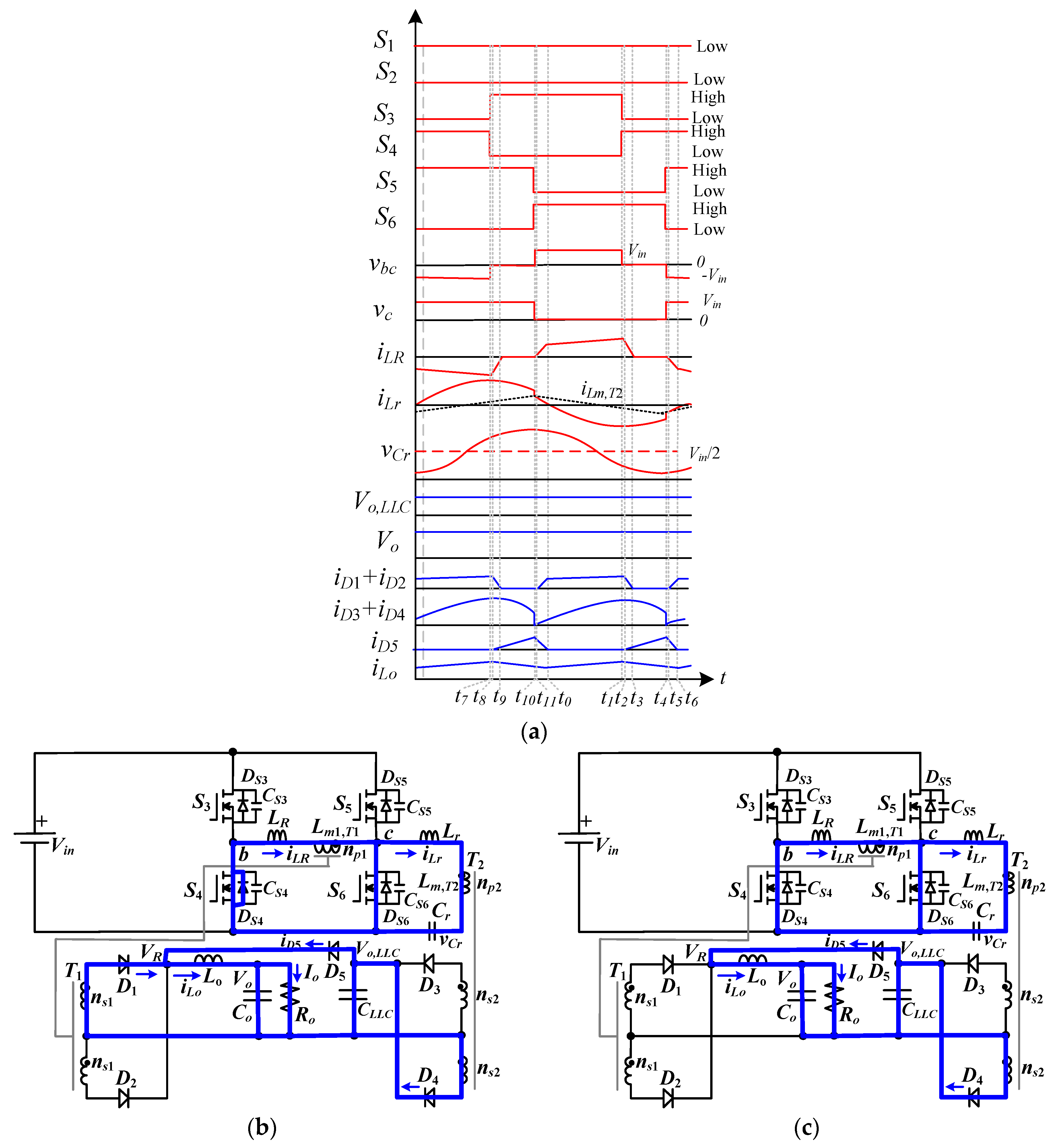

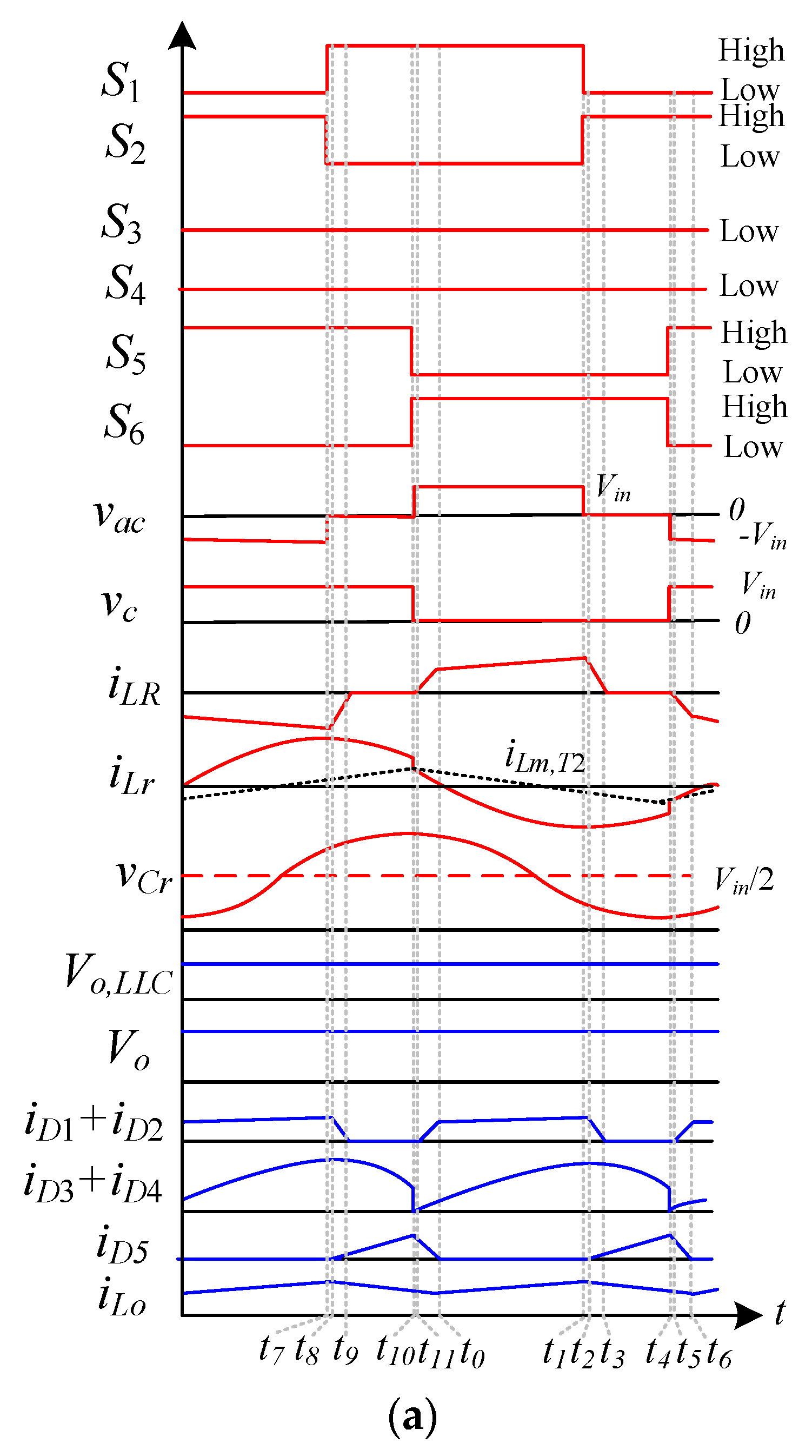

3. Principle of Operation

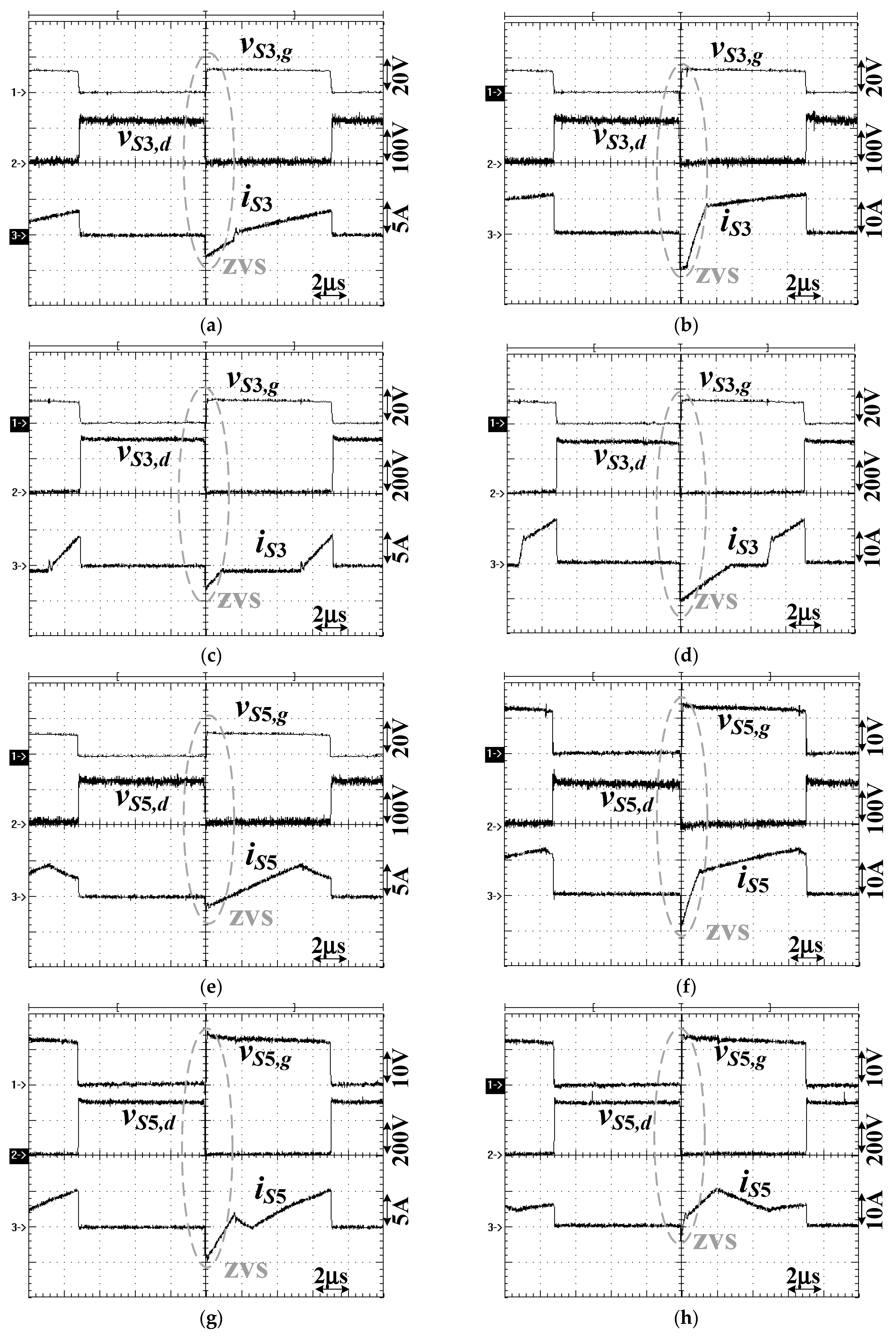

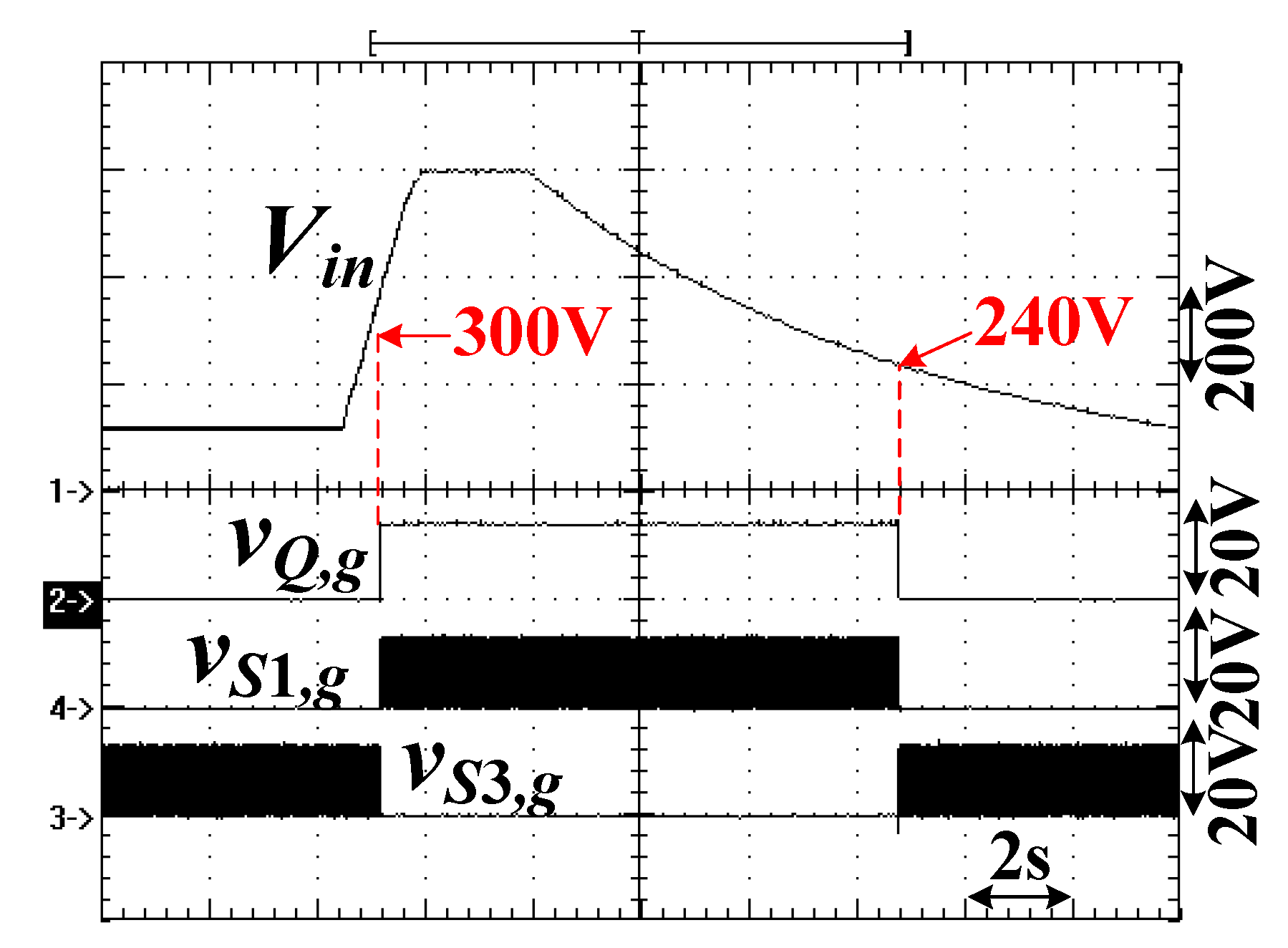

4. Circuit Characteristics

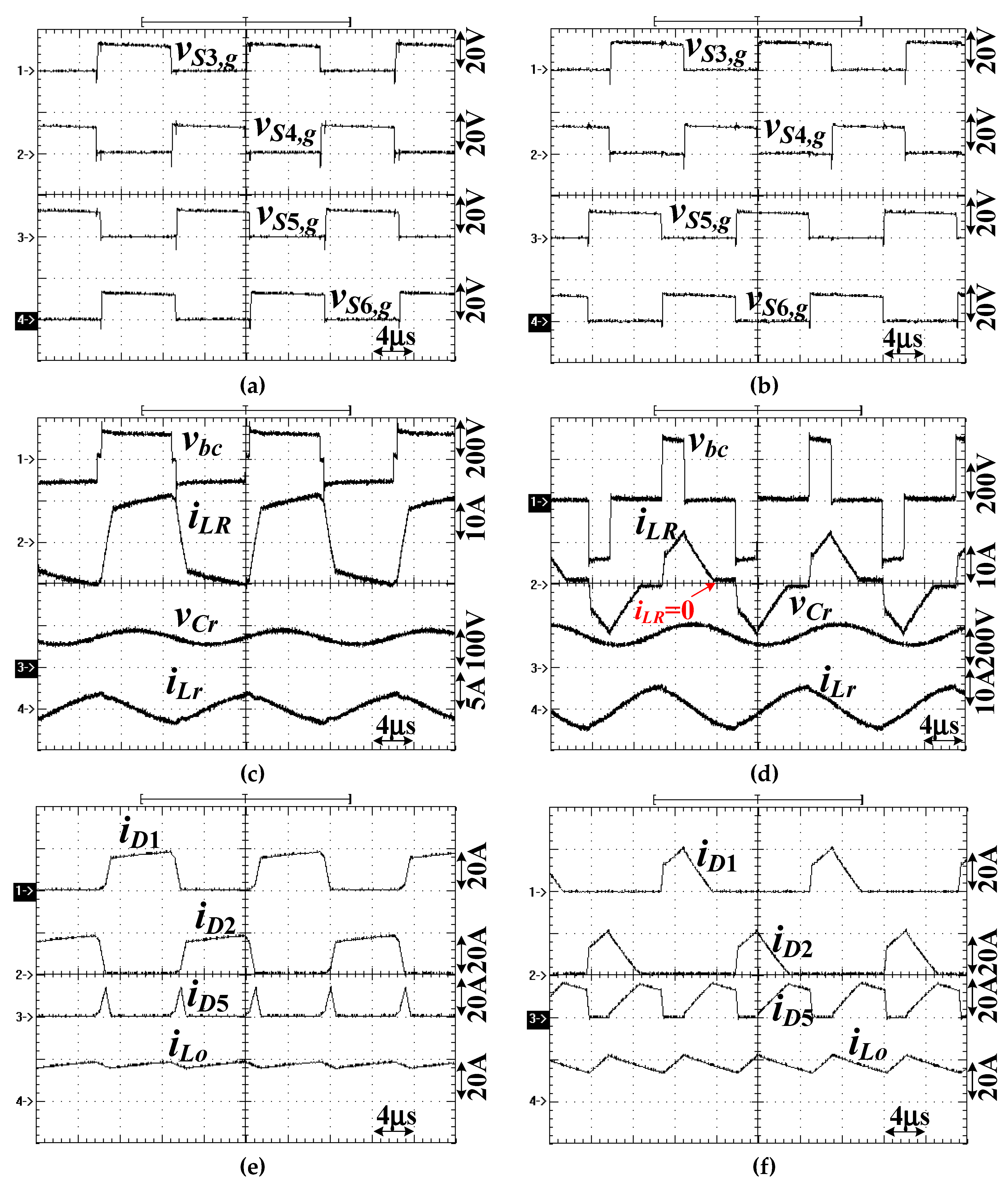

5. Experimental Results

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Tahir, S.; Wang, J.; Baloch, M.H.; Kaloi, G.S. Digital Control Techniques Based on Voltage Source Inverters in Renewable Energy Applications: A Review. Electronics 2018, 7, 18. [Google Scholar] [CrossRef]

- Almalaq, Y.; Matin, M. Three topologies of a non-isolated high gian switched-capacitor step-up cuk converter for renewable energy applications. Electronics 2018, 7, 94. [Google Scholar] [CrossRef]

- Blaabjerg, F.; Dragicevic, T.; Davari, P. Applications of Power Electronics. Electronics 2019, 8, 465. [Google Scholar] [CrossRef]

- Kim, J.-Y.; Kim, H.-S.; Baek, J.-W.; Jeong, D.-K. Analysis of Effective Three-Level Neutral Point Clamped Converter System for the Bipolar LVDC Distribution. Electronics 2019, 8, 691. [Google Scholar] [CrossRef]

- Steigerwald, R.L. A comparison of half-bridge resonant converter topologies. IEEE Trans. Power Electron. 1988, 3, 174–182. [Google Scholar] [CrossRef]

- Lin, B.-R.; Dai, C.-X. Wide Voltage Resonant Converter Using a Variable Winding Turns Ratio. Electronics 2020, 9, 370. [Google Scholar] [CrossRef]

- Ren, R.; Liu, B.; Jones, E.A.; Wang, F.F.; Zhang, Z.; Costinett, D. Capacitor-clamped, three-level Gan-based dc-dc converter with dual voltage outputs for battery charger applications. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 841–853. [Google Scholar] [CrossRef]

- Safaee, A.; Jain, P.; Bakhshai, A. A ZVS Pulsewidth Modulation Full-Bridge Converter with a Low-RMS-Current Resonant Auxiliary Circuit. IEEE Trans. Power Electron. 2015, 31, 4031–4047. [Google Scholar] [CrossRef]

- Wang, X.; Tian, F.; Batarseh, I. High Efficiency Parallel Post Regulator for Wide Range Input DC–DC Converter. IEEE Trans. Power Electron. 2008, 23, 852–858. [Google Scholar] [CrossRef]

- Wu, H.; Wan, C.; Sun, K.; Xing, Y. A High Step-Down Multiple Output Converter with Wide Input Voltage Range Based on Quasi Two-Stage Architecture and Dual-Output LLC Resonant Converter. IEEE Trans. Power Electron. 2015, 30, 1793–1796. [Google Scholar] [CrossRef]

- Lin, B.-R.; Hsieh, F.-Y. Soft-Switching Zeta–Flyback Converter with a Buck–Boost Type of Active Clamp. IEEE Trans. Ind. Electron. 2007, 54, 2813–2822. [Google Scholar] [CrossRef]

- Jeong, Y.; Park, J.D.; Moon, G.-W. An Interleaved Active-Clamp Forward Converter Modified for Reduced Primary Conduction Loss Without Additional Components. IEEE Trans. Power Electron. 2019, 35, 121–130. [Google Scholar] [CrossRef]

- Lin, B.-R.; Chao, C.-H. A New ZVS DC/DC Converter with Three APWM Circuits. IEEE Trans. Ind. Electron. 2012, 60, 4351–4358. [Google Scholar] [CrossRef]

- Pont, N.C.D.; Bandeira, D.; Lazzarin, T.B.; Barbi, I. A ZVS APWM half-bridge parallel resonant DC–DC converter with ca-pacitive output. IEEE Trans. Ind. Electron. 2019, 66, 5231–5241. [Google Scholar] [CrossRef]

- Lin, B. Resonant converter with wide input voltage range and input current ripple-free. Electron. Lett. 2018, 54, 1086–1088. [Google Scholar] [CrossRef]

- Wang, P.; Zhou, L.; Zhang, Y.; Li, J.; Sumner, M. Input-Parallel Output-Series DC-DC Boost Converter with a Wide Input Voltage Range, For Fuel Cell Vehicles. IEEE Trans. Veh. Technol. 2017, 66, 7771–7781. [Google Scholar] [CrossRef]

- Hu, H.; Fang, X.; Chen, F.; Shen, Z.J.; Batarseh, I. A Modified High-Efficiency LLC Converter with Two Transformers for Wide Input-Voltage Range Applications. IEEE Trans. Power Electron. 2013, 28, 1946–1960. [Google Scholar] [CrossRef]

| Items | Parameter | Items | Parameter |

|---|---|---|---|

| Vin | 120–600 V | Lo | 30 μH |

| Vo | 48 V | S1~S6, Q | STF15N95K5 |

| Po | 800 W | D1~D4 | MBR40500PT |

| fsw | 70 kHz | D5 | STTH2003CT |

| Co | 640 μF/100 V | np1:ns1 | 16:10 |

| Co,LLC | 240 μF/100 V | np2:ns2 | 22:2 |

| Cr | 205 nF | Lm1,T1, Lm2,T1 | 259 μH |

| Lr | 27 μH | Lm,T2 | 135 μH |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lin, B.-R.; Liu, Y.-C. Analysis of a Wide Voltage Hybrid Soft Switching Converter. Electronics 2021, 10, 473. https://doi.org/10.3390/electronics10040473

Lin B-R, Liu Y-C. Analysis of a Wide Voltage Hybrid Soft Switching Converter. Electronics. 2021; 10(4):473. https://doi.org/10.3390/electronics10040473

Chicago/Turabian StyleLin, Bor-Ren, and Yen-Chun Liu. 2021. "Analysis of a Wide Voltage Hybrid Soft Switching Converter" Electronics 10, no. 4: 473. https://doi.org/10.3390/electronics10040473

APA StyleLin, B.-R., & Liu, Y.-C. (2021). Analysis of a Wide Voltage Hybrid Soft Switching Converter. Electronics, 10(4), 473. https://doi.org/10.3390/electronics10040473