An Ultra-Low-Power K-Band 22.2 GHz-to-26.9 GHz Current-Reuse VCO Using Dynamic Back-Gate-Biasing Technique

Abstract

1. Introduction

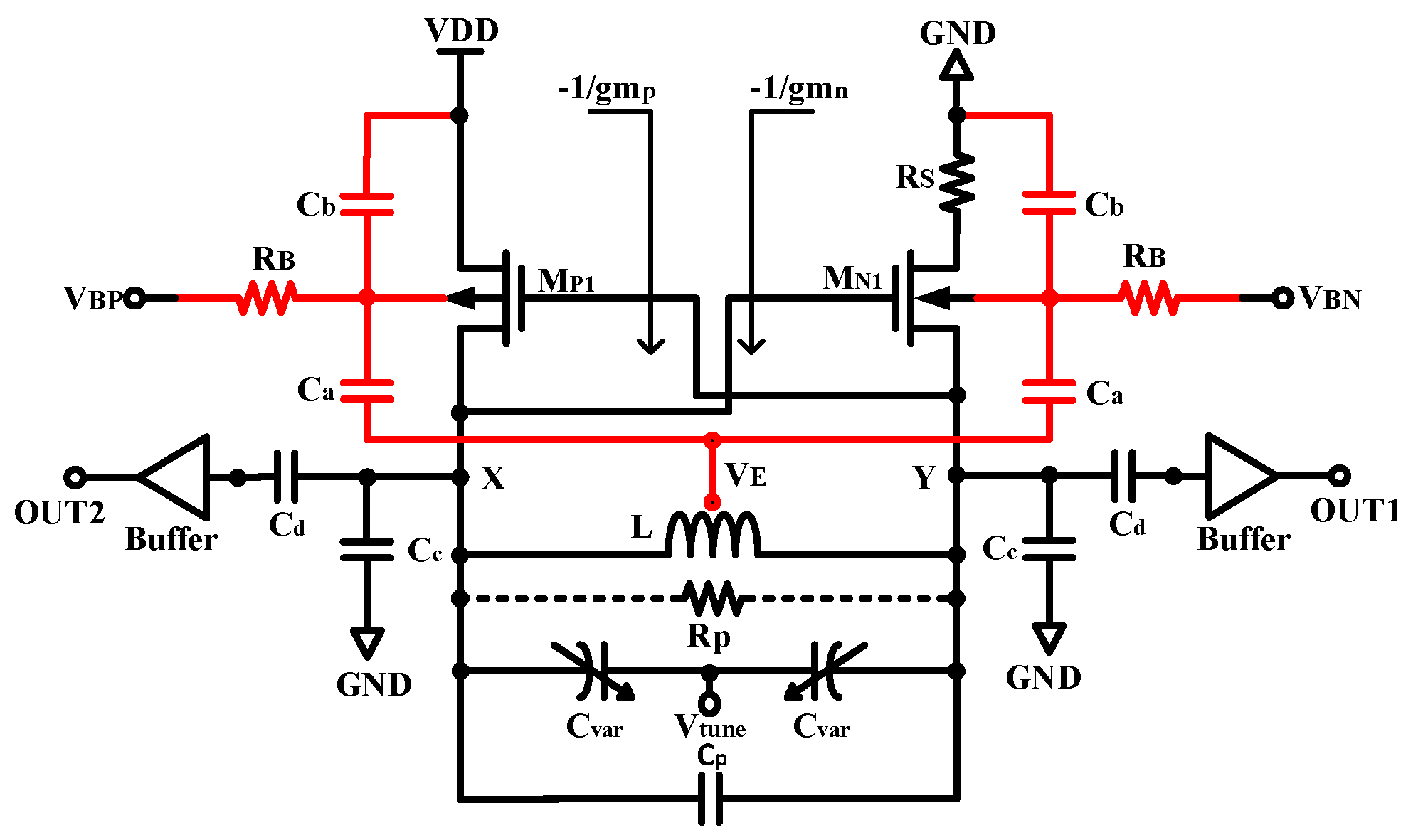

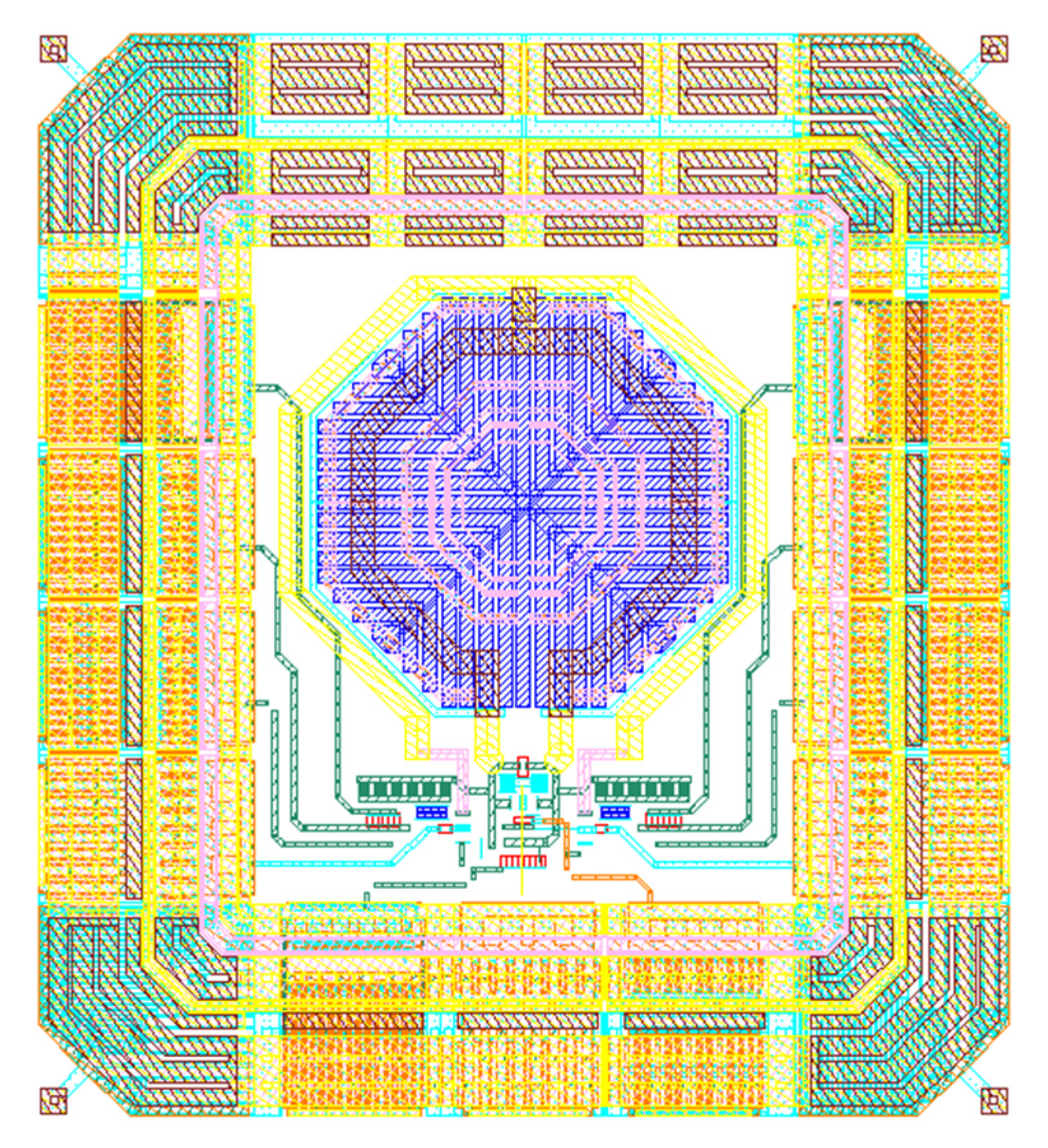

2. Design and Analysis of CR_VCO

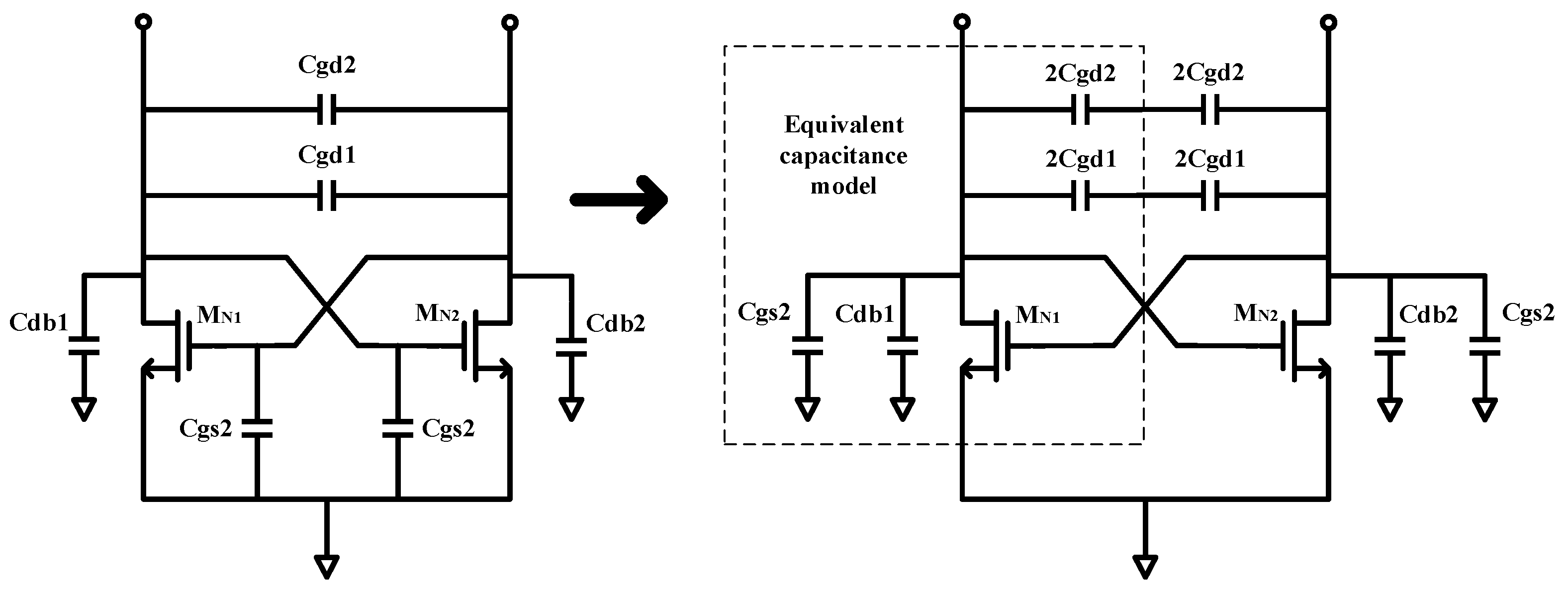

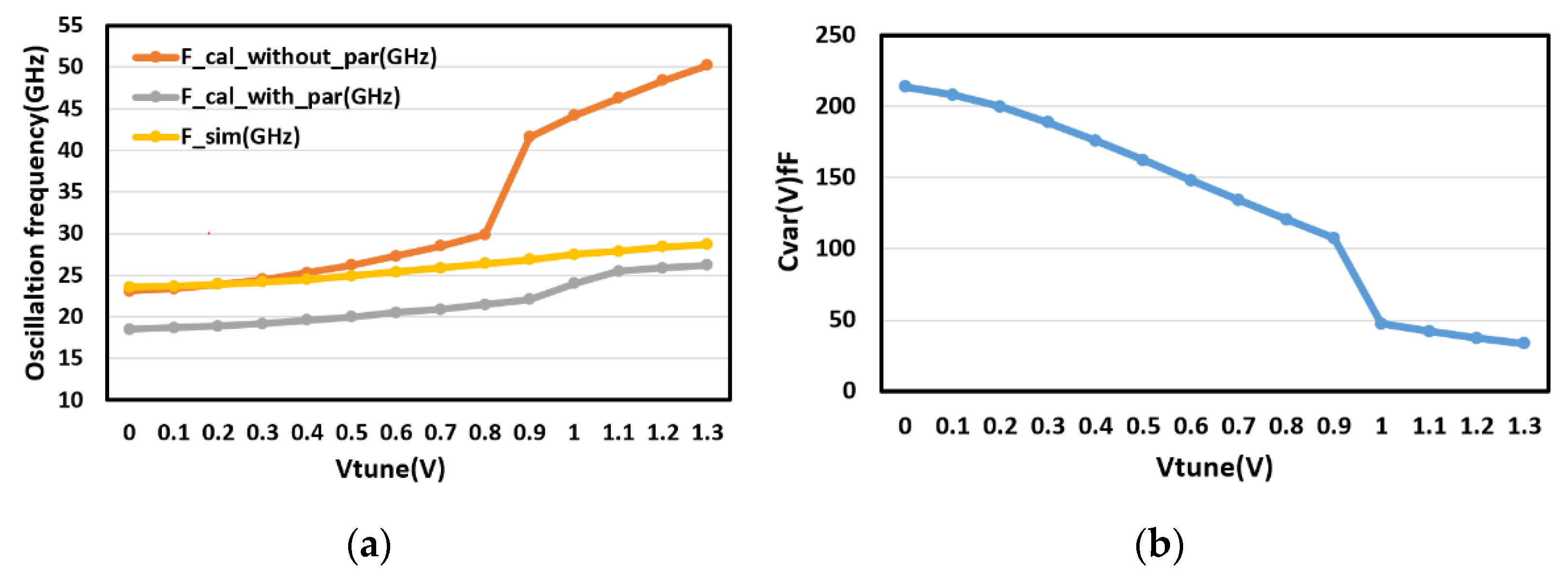

2.1. Schematic and Its Small Signal Model

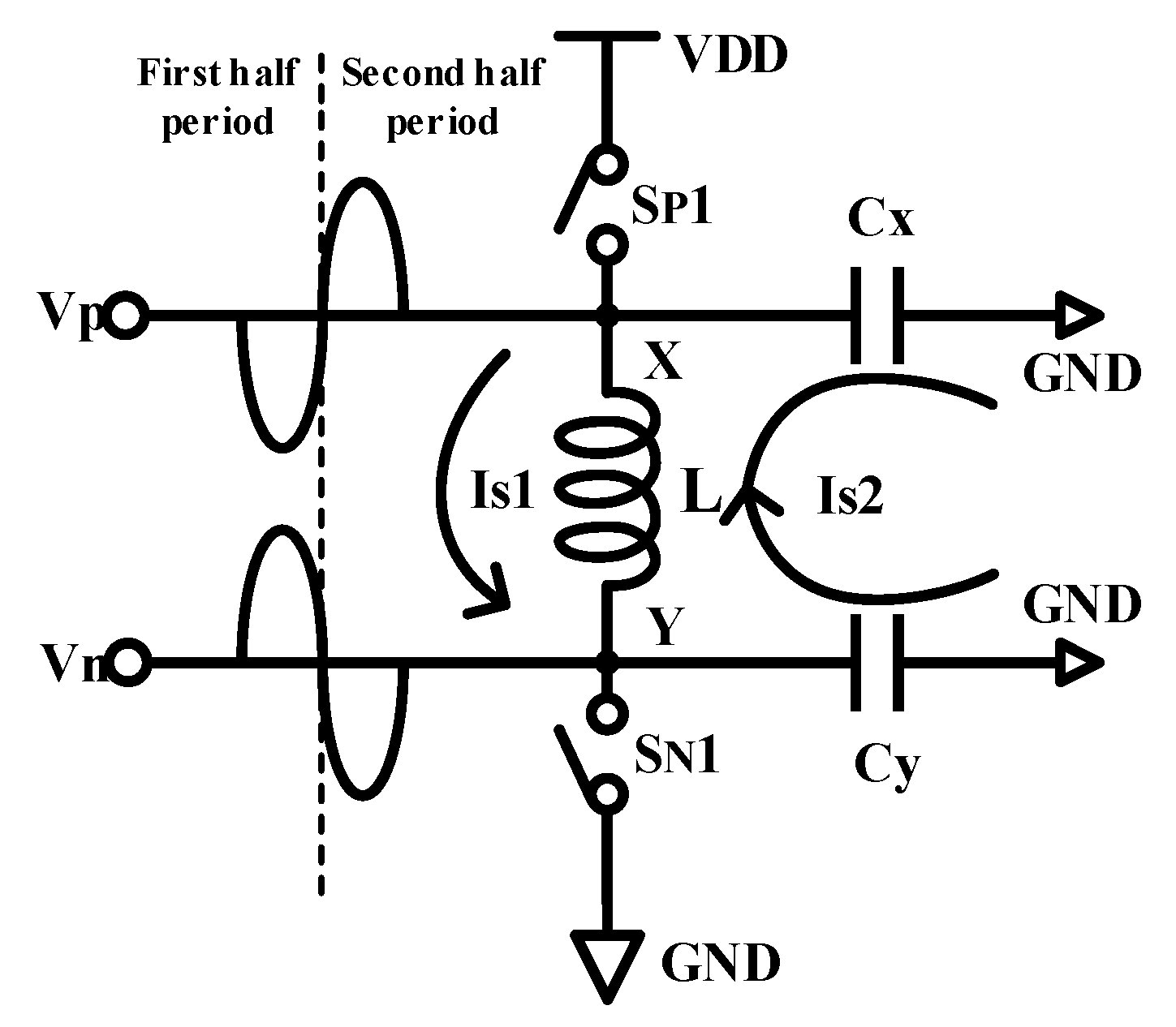

2.2. Dynamic Back-Gate-Biasing Technique

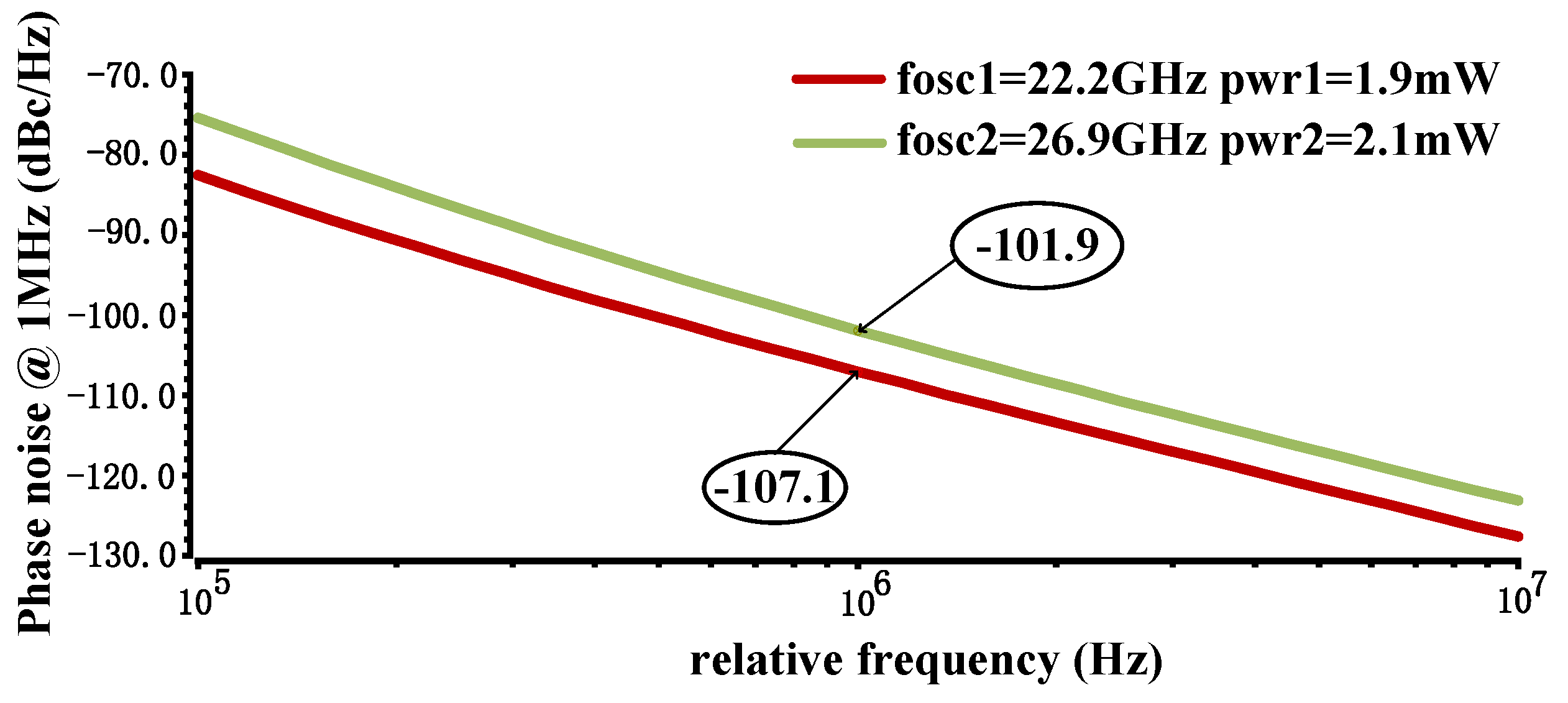

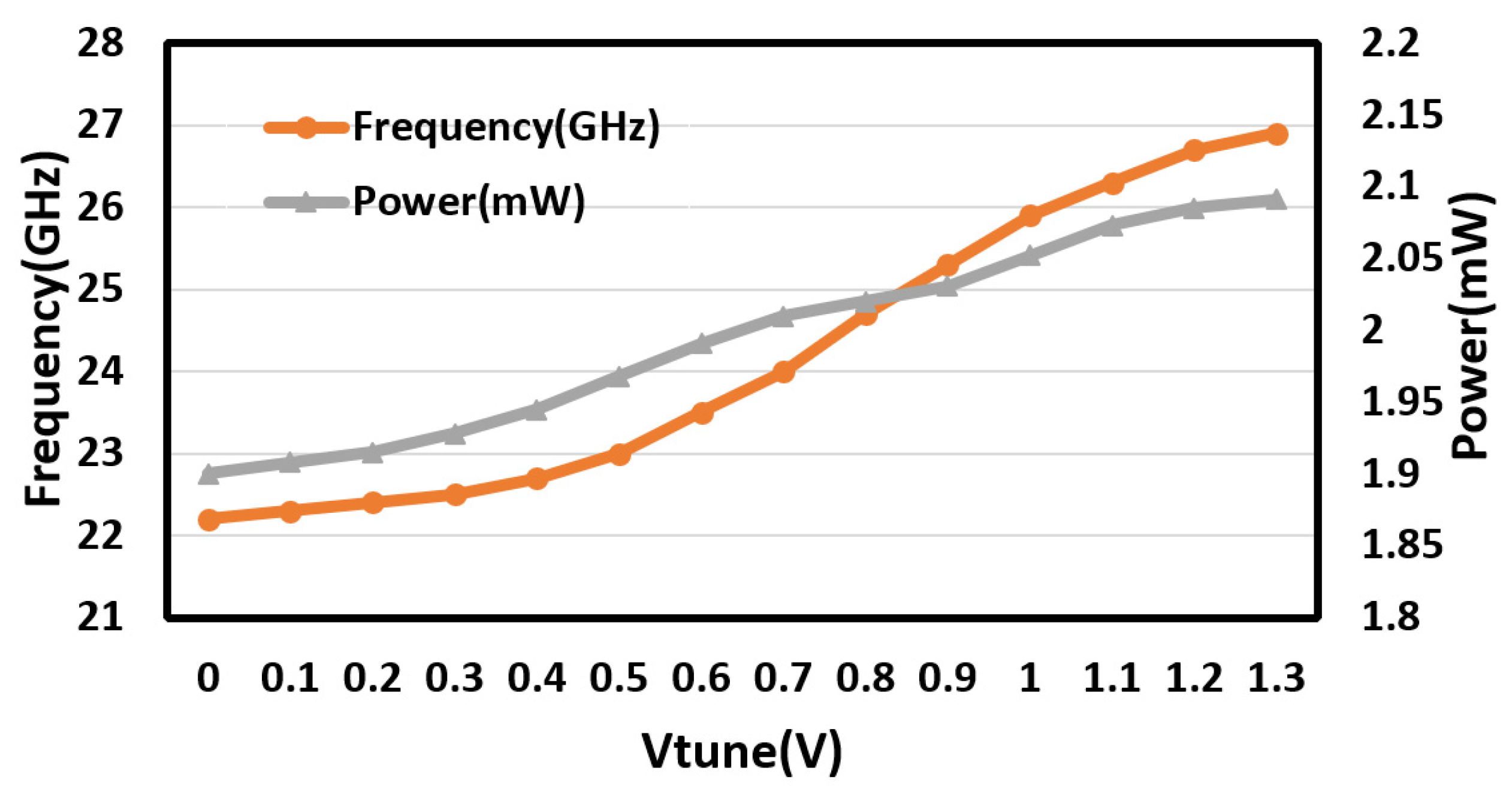

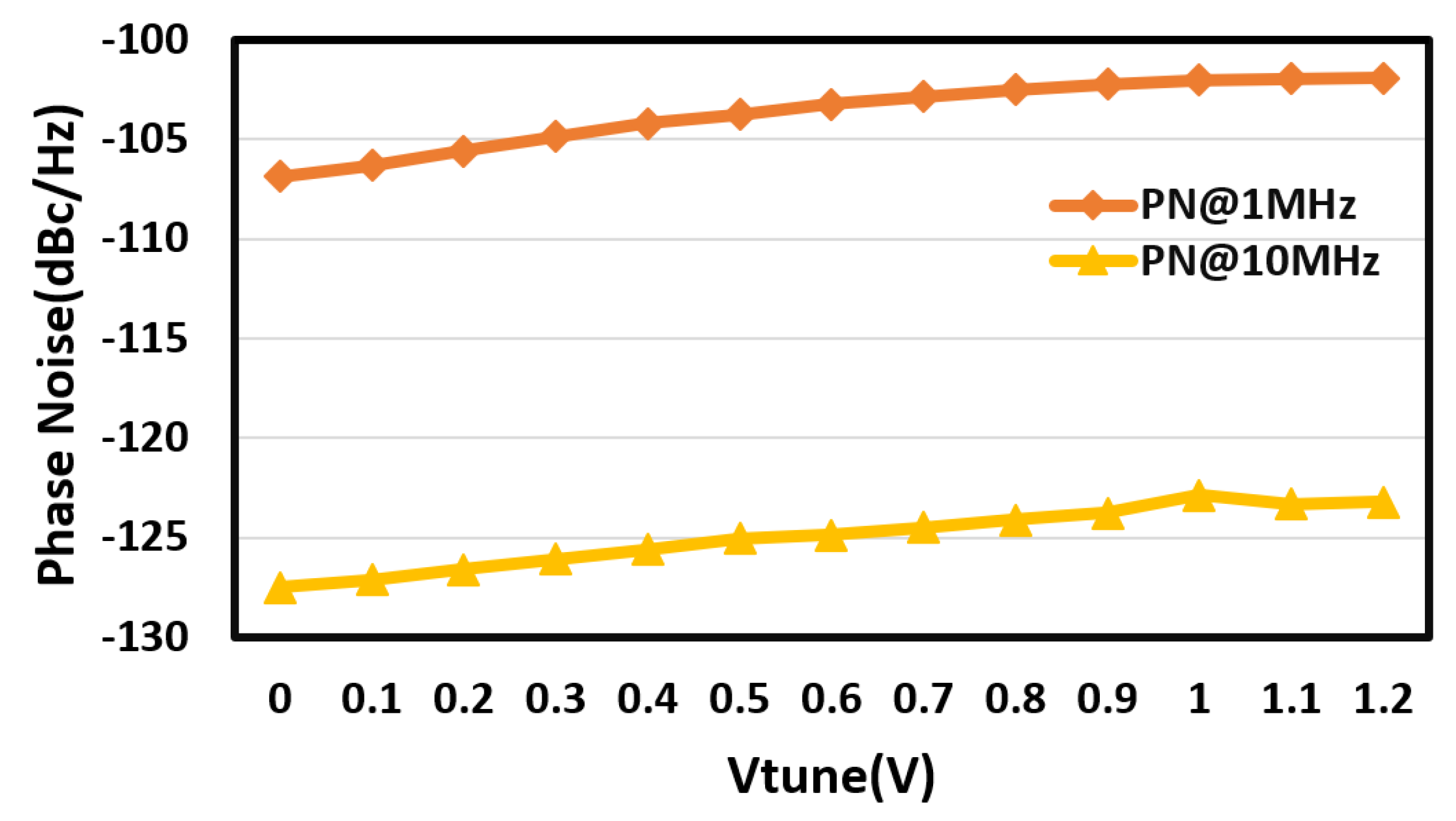

3. Post-Layout Simulation Results

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Jahan, N.; Baichuan, C.; Pokharel, R.K.; Barakat, A. A K-Band VCO Employing High Active Q-factor Defected Ground Structure Resonator in 0.18 um CMOS Technology. In Proceedings of the 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018; pp. 1–5. [Google Scholar] [CrossRef]

- Andreani, P.; Mattisson, S. On the use of MOS varactors in RF VCOs. IEEE J. Solid-State Circuits 2000, 35, 905–910. [Google Scholar] [CrossRef]

- Mazzanti, A.; Andreani, P. A Push–Pull Class-C CMOS VCO. IEEE J. Solid-State Circuits 2013, 48, 724–732. [Google Scholar] [CrossRef]

- Guo, H.; Chen, Y.; Mak, P.; Martins, R.P. A 0.083-mm2 25.2-to-29.5 GHz Multi-LC-Tank Class-F234 VCO with a 189.6-dBc/Hz FOM. IEEE Solid-State Circuits Lett. 2018, 1, 86–89. [Google Scholar] [CrossRef]

- Huang, Y.; Chen, Y.; Guo, H.; Mak, P.-I.; Martins, R.P. A 3.3-mW 25.2-to-29.4-GHz Current-Reuse VCO Using a Single-Turn Multi-Tap Inductor and Differential-Only Switched-Capacitor Arrays with a 187.6-dBc/Hz FOM. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 3704–3717. [Google Scholar] [CrossRef]

- Hu, Y.; Siriburanon, T.; Staszewski, R.B. A Low-Flicker-Noise 30-GHz Class-F23 Oscillator in 28-nm CMOS Using Implicit Resonance and Explicit Common-Mode Return Path. IEEE J. Solid-State Circuits 2018, 53, 1977–1987. [Google Scholar] [CrossRef]

- Yun, S.-J.; Shin, S.-B.; Choi, H.-C.; Lee, S.-G. A 1mW current-reuse CMOS differential LC-VCO with low phase noise. In Proceedings of the ISSCC, 2005 IEEE International Digest of Technical Papers, Solid-State Circuits Conference, San Francisco, CA, USA, 10 February 2005; Volume 1, pp. 540–616. [Google Scholar] [CrossRef]

- Guo, S.; Gui, P.; Liu, T.; Zhang, T.; Xi, T.; Wu, G.; Fan, Y.; Morgan, M. A Low-Voltage Low-Phase-Noise 25-GHz Two-Tank Transformer-Feedback VCO. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 3162–3173. [Google Scholar] [CrossRef]

- Fu, Y.; Li, L.; Wang, D.; Wang, X.; He, L. 28-GHz CMOS VCO With Capacitive Splitting and Transformer Feedback Techniques for 5G Communication. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2019, 27, 2088–2095. [Google Scholar] [CrossRef]

- MKashani, H.; Molavi, R.; Mirabbasi, S. A 2.3-mW 26.3-GHz Gm-Boosted Differential Colpitts VCO with 20% Tuning Range in 65-nm CMOS. IEEE Trans. Microw. Theory Tech. 2019, 67, 1556–1565. [Google Scholar] [CrossRef]

- Murphy, D.; Darabi, H. A 27-GHz Quad-Core CMOS Oscillator with No Mode Ambiguity. IEEE J. Solid-State Circuits 2018, 53, 3208–3216. [Google Scholar] [CrossRef]

- Shu, Y.; Qian, H.J.; Luo, X. 17.4 A 18.6-to-40.1GHz 201.7dBc/Hz FoMT Multi-Core Oscillator Using E-M Mixed-Coupling Resonance Boosting. In Proceedings of the 2020 IEEE International Solid-State Circuits Conference-(ISSCC), San Francisco, CA, USA, 16–20 February 2020; pp. 272–274. [Google Scholar] [CrossRef]

- Wei, M.; Chang, S.; Huang, S.; Yang, Y.; Negra, R. Investigation of Sub-Milliwatt Current-Reuse VCOs with Mono-Spontaneous Transconductance Match Technique. IEEE Trans. Microw. Theory Tech. 2014, 62, 332–340. [Google Scholar] [CrossRef]

- Razavi, B. RF Microelectronics. Prentice Hall Communications Engineering Emerging Technologies; Pearson: London, UK, 1998. [Google Scholar]

- Bunch, R.L.; Raman, S. Large-signal analysis of MOS varactors in CMOS-Gm LC VCOs. IEEE J. Solid-State Circuits 2003, 38, 1325–1332. [Google Scholar] [CrossRef]

- Toso, S.D.; Bevilacqua, A.; Gerosa, A.; Neviani, A. A thorough analysis of the tank quality factor in LC oscillators with switched capacitor banks. In Proceedings of the 2010 IEEE International Symposium on Circuits and Systems, Paris, France, 30 May–2 June 2010; pp. 1903–1906. [Google Scholar] [CrossRef]

- Sadhu, B.; Kim, J.; Harjani, R. A CMOS 3.3-8.4 GHz wide tuning range, low phase noise LC VCO. In Proceedings of the 2009 IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 13–16 September 2009; pp. 559–562. [Google Scholar] [CrossRef]

| This Work * | [5] | [6] | [9] | [10] | [11] | |

|---|---|---|---|---|---|---|

| Process (nm) | 55 | 65 | 28 | 65 | 65 | 40 |

| Supply (V) | 1.2 | 1.1 | 1 | 0.9 | 1 | 0.95 |

| Tuning range | 22.2~26.9 | 25.2~29.38 | 27.3~31.2 | 26.5 | 26.3 | 23~29.9 |

| TR (%) | 19.1 | 15.3 | NA | 14 | 20.1 | 26.1 |

| Area (mm2) | 0.043 | 0.116 | 0.15 | 0.22 | 0.22 | 0.1 |

| Power (mW) | 1.9~2.1 | 3.03~3.44 | 22~23 | 10.8 | 2.3 | 16 |

| PNoise@1 MHz (dBc/Hz) | −107~−101 | −104~−103.9 | −106~−104 | −105.8 | −121 | −110 |

| PNoise@10 MHz (dBc/Hz) | −127.7~−122.9 | −123.5~−122.5 | −125~−126 | −130 | NA | NA |

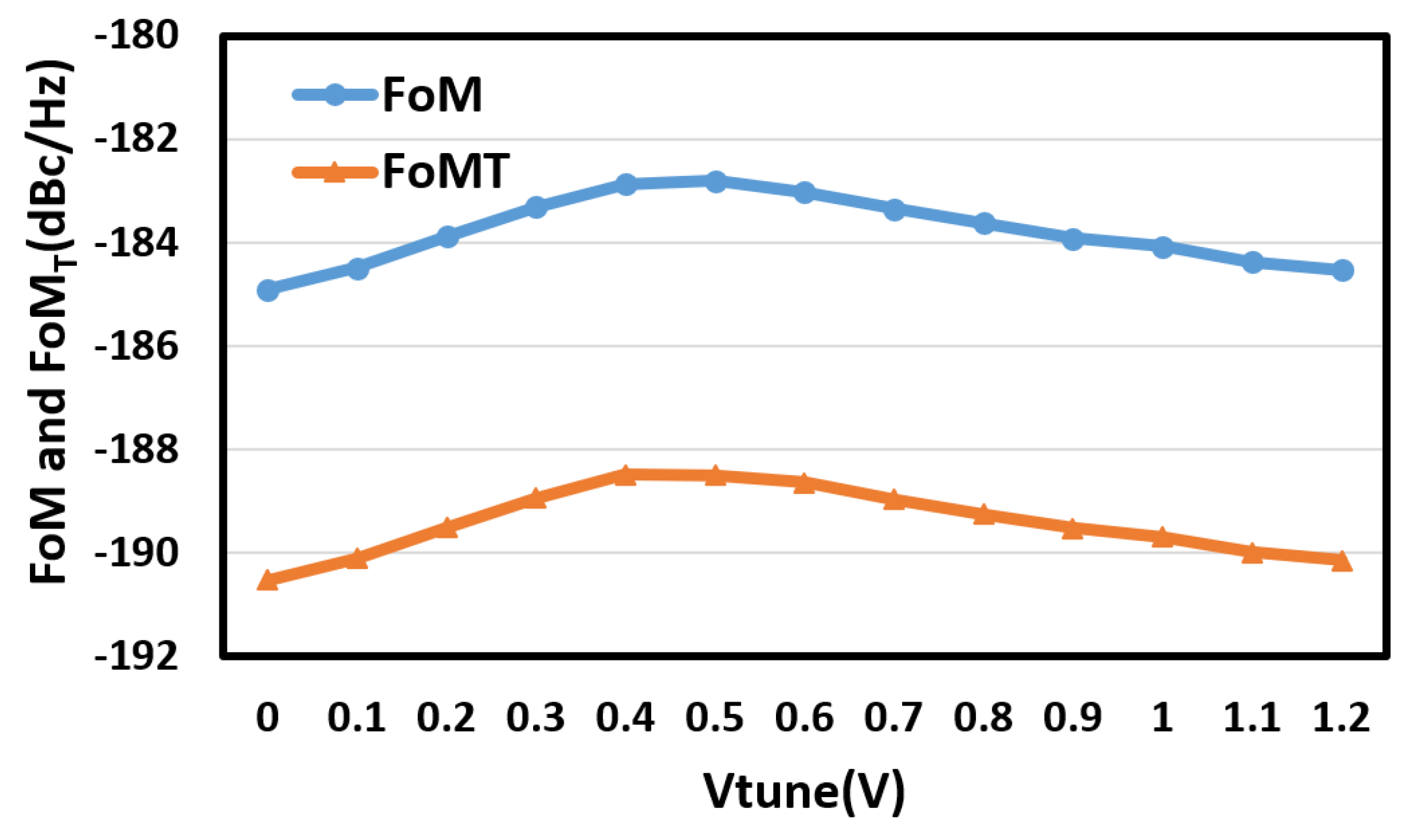

| FoM@1 MHz (dBc/Hz) 1 | −182.8~−185.1 | −187.3~−187.6 | −184~−183 | −184 | −191.8 | −187~−186.5 |

| FoMT@1 MHz (dBc/Hz) 2 | −188.4~−190.7 | −191.3~−190.9 | −184 | NA | NA | −195.3~−194.8 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Deng, X.; Tan, P. An Ultra-Low-Power K-Band 22.2 GHz-to-26.9 GHz Current-Reuse VCO Using Dynamic Back-Gate-Biasing Technique. Electronics 2021, 10, 889. https://doi.org/10.3390/electronics10080889

Deng X, Tan P. An Ultra-Low-Power K-Band 22.2 GHz-to-26.9 GHz Current-Reuse VCO Using Dynamic Back-Gate-Biasing Technique. Electronics. 2021; 10(8):889. https://doi.org/10.3390/electronics10080889

Chicago/Turabian StyleDeng, Xiaoying, and Peiqi Tan. 2021. "An Ultra-Low-Power K-Band 22.2 GHz-to-26.9 GHz Current-Reuse VCO Using Dynamic Back-Gate-Biasing Technique" Electronics 10, no. 8: 889. https://doi.org/10.3390/electronics10080889

APA StyleDeng, X., & Tan, P. (2021). An Ultra-Low-Power K-Band 22.2 GHz-to-26.9 GHz Current-Reuse VCO Using Dynamic Back-Gate-Biasing Technique. Electronics, 10(8), 889. https://doi.org/10.3390/electronics10080889