K-Band Hetero-Stacked Differential Cascode Power Amplifier with High Psat and Efficiency in 65 nm LP CMOS Technology

Abstract

:1. Introduction

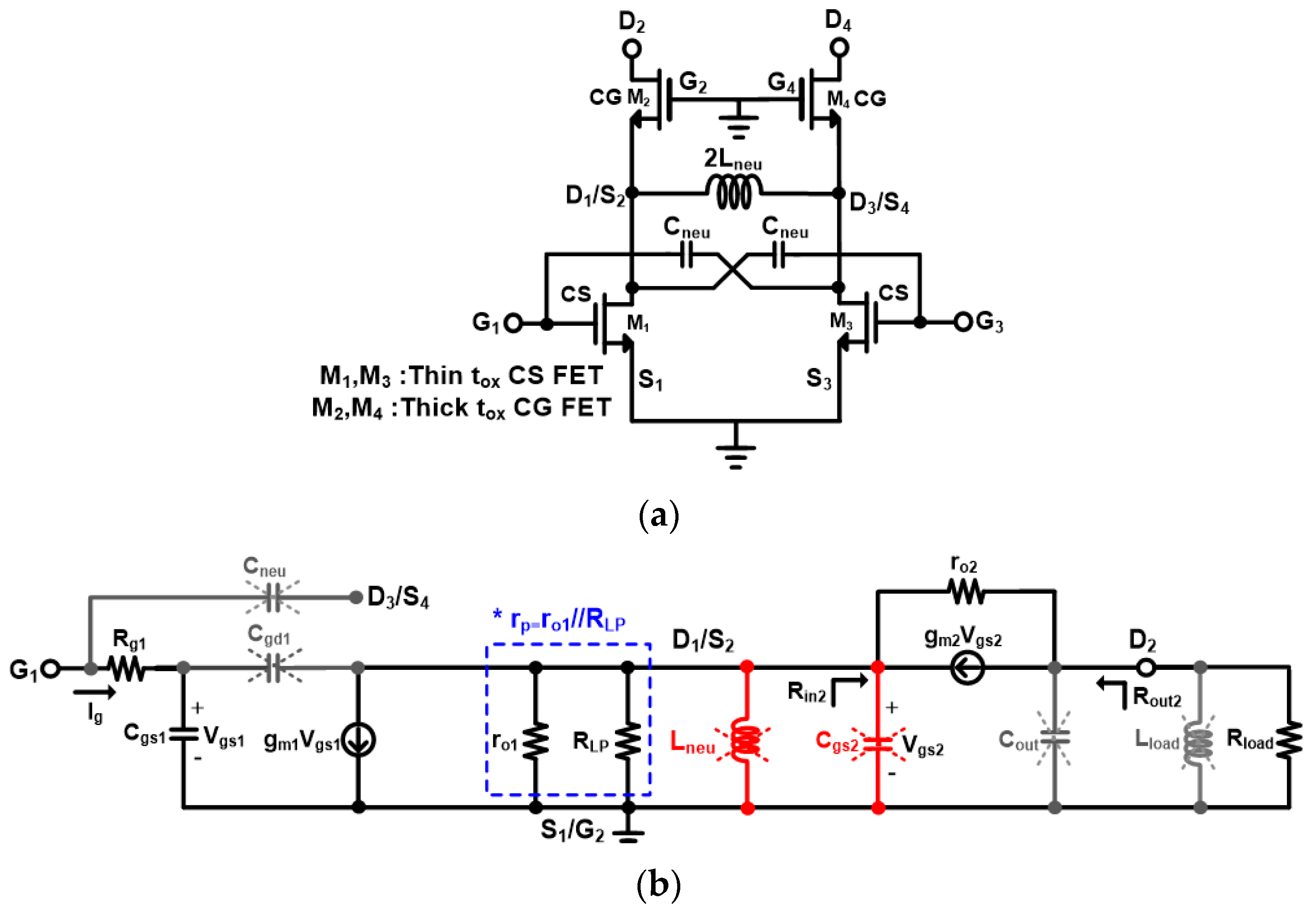

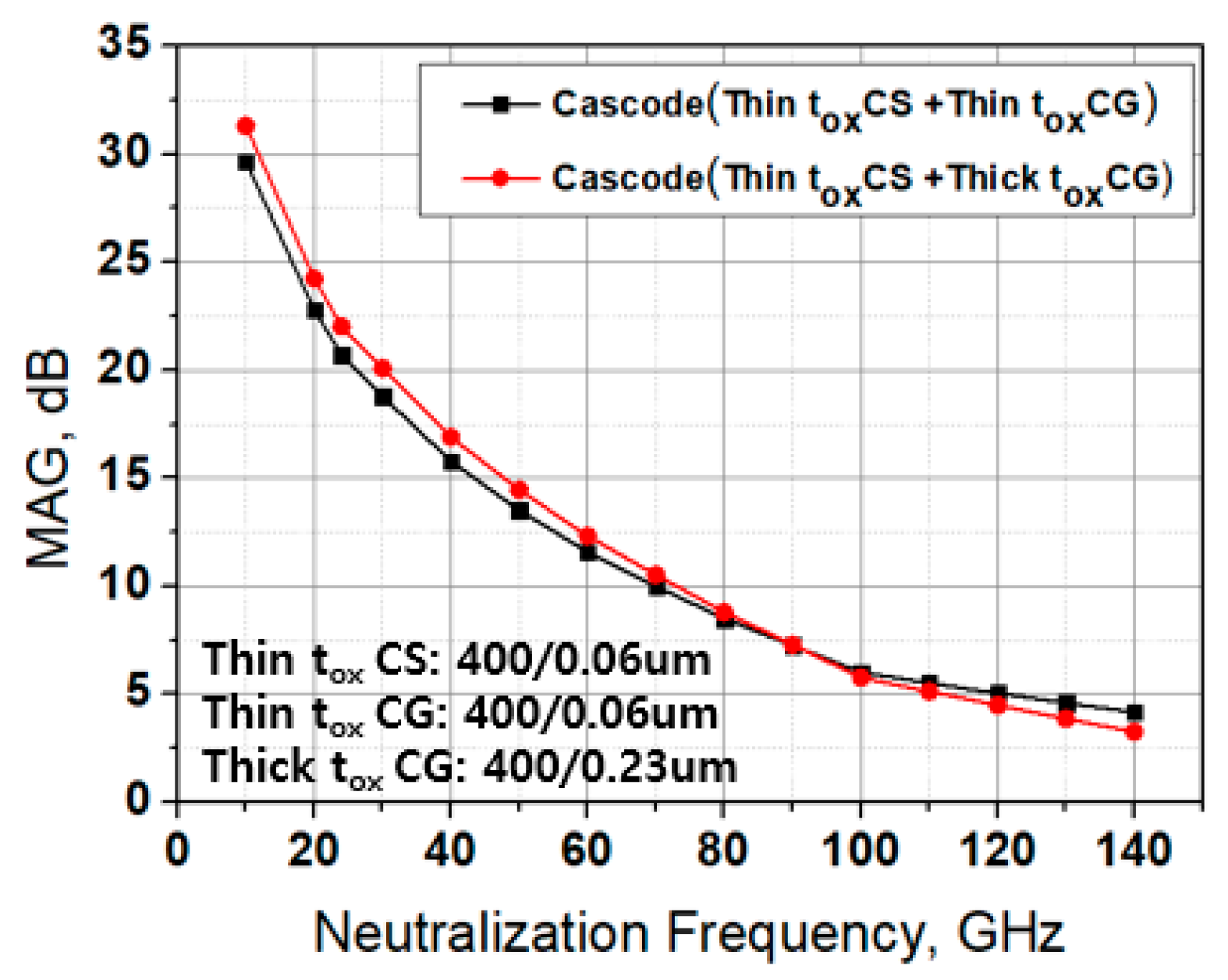

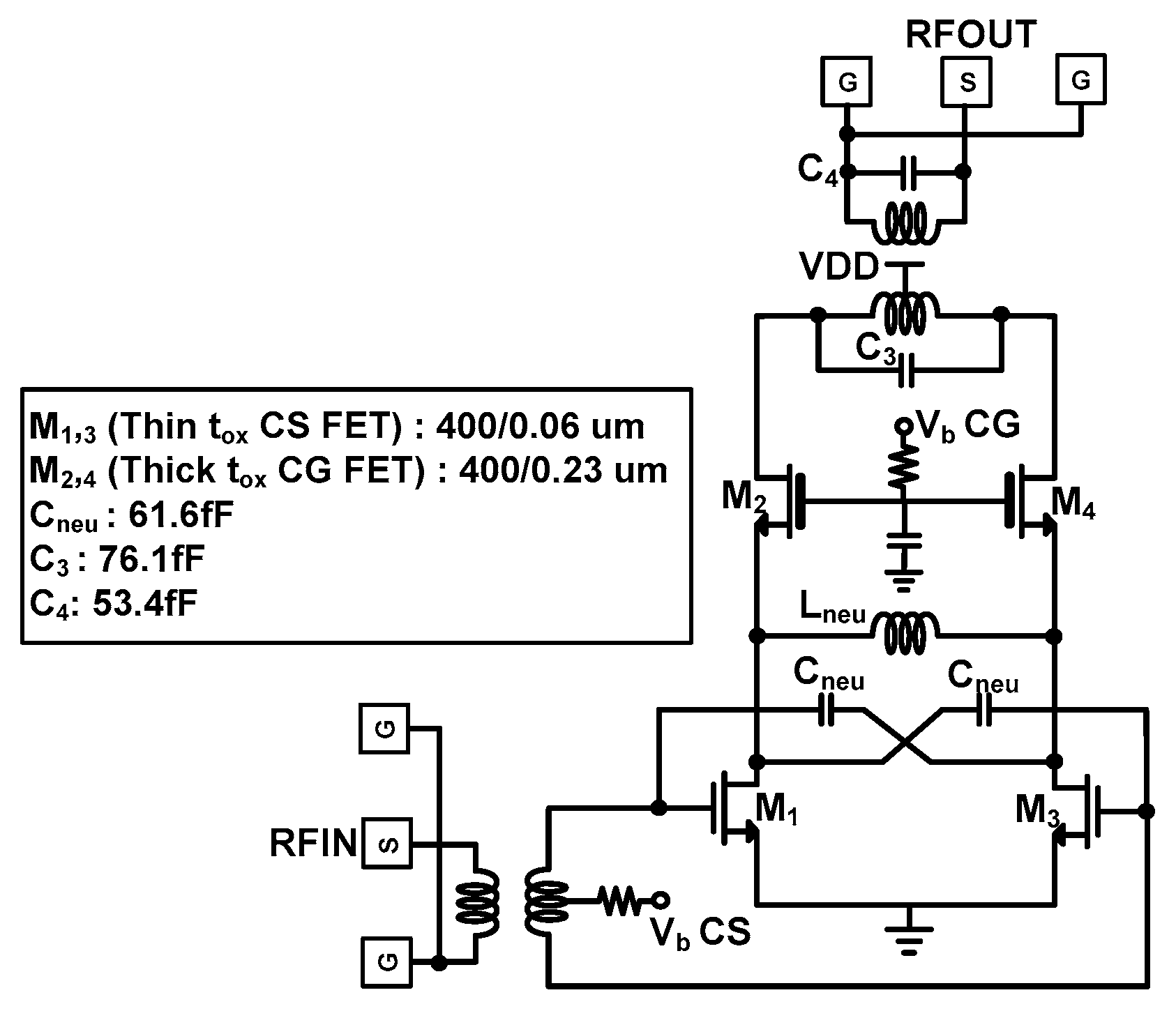

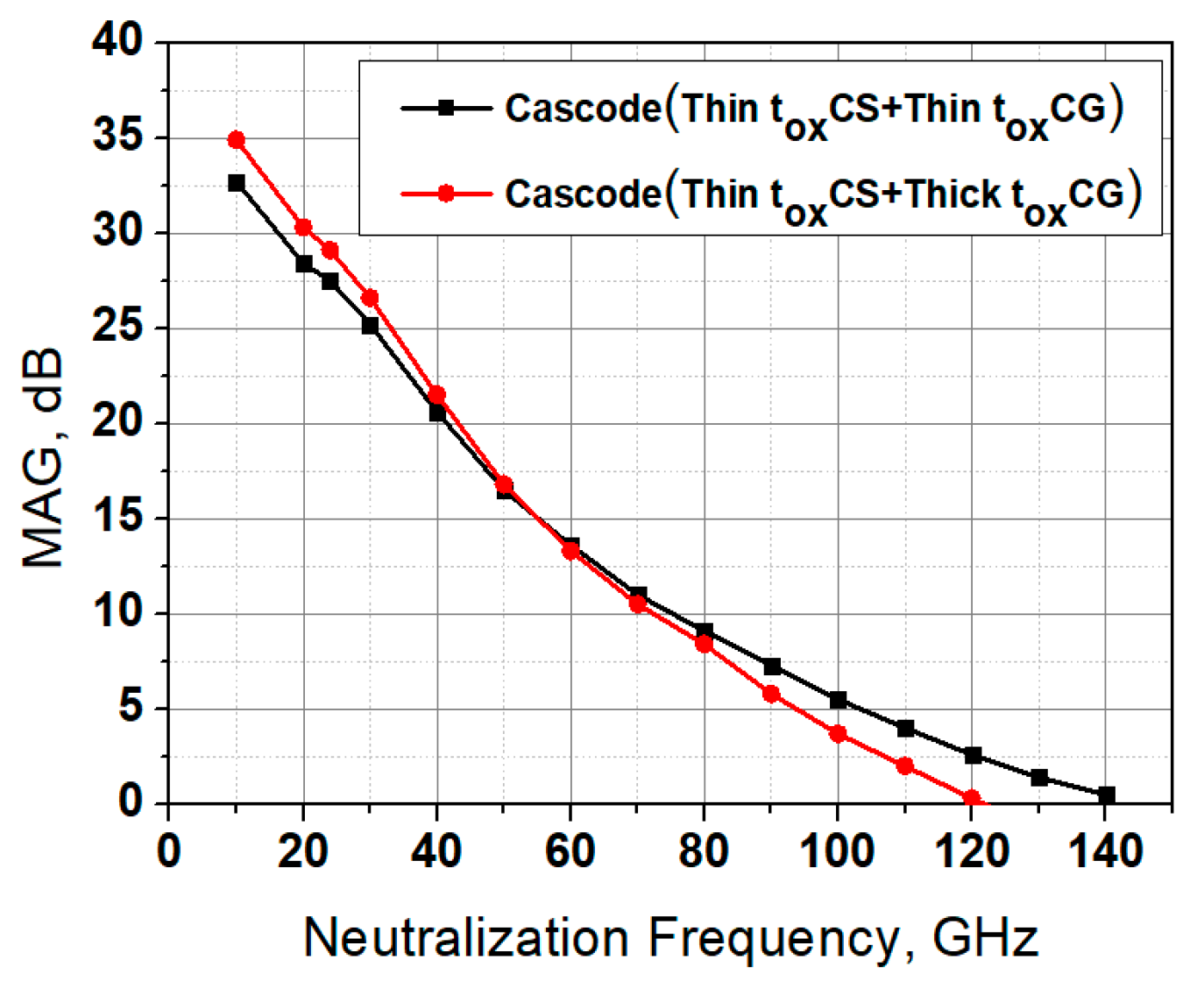

2. High Frequency Gain of the Neutralized Hetero-Stacked Cascode Amplifier

3. MAG Simulation Verification

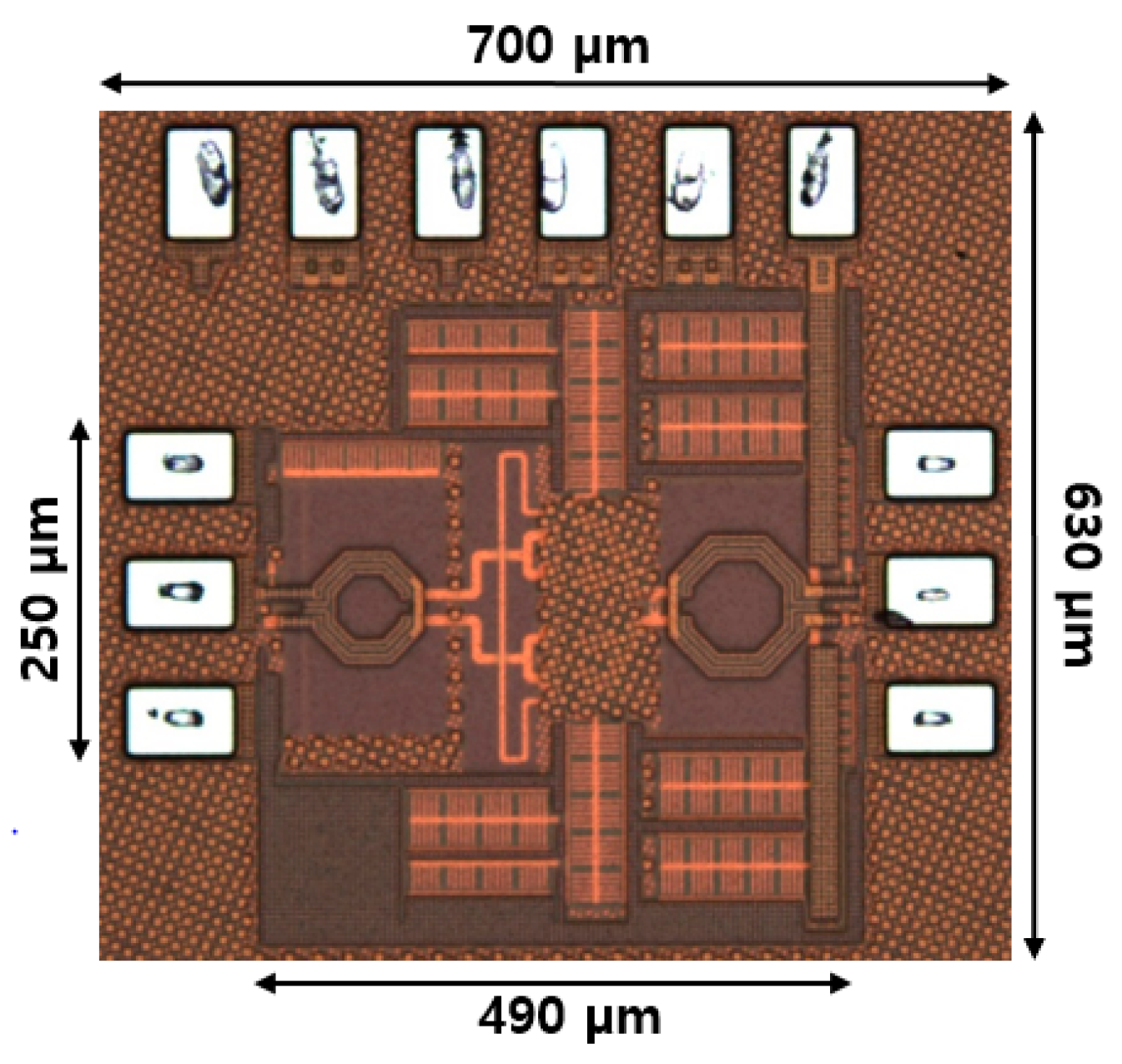

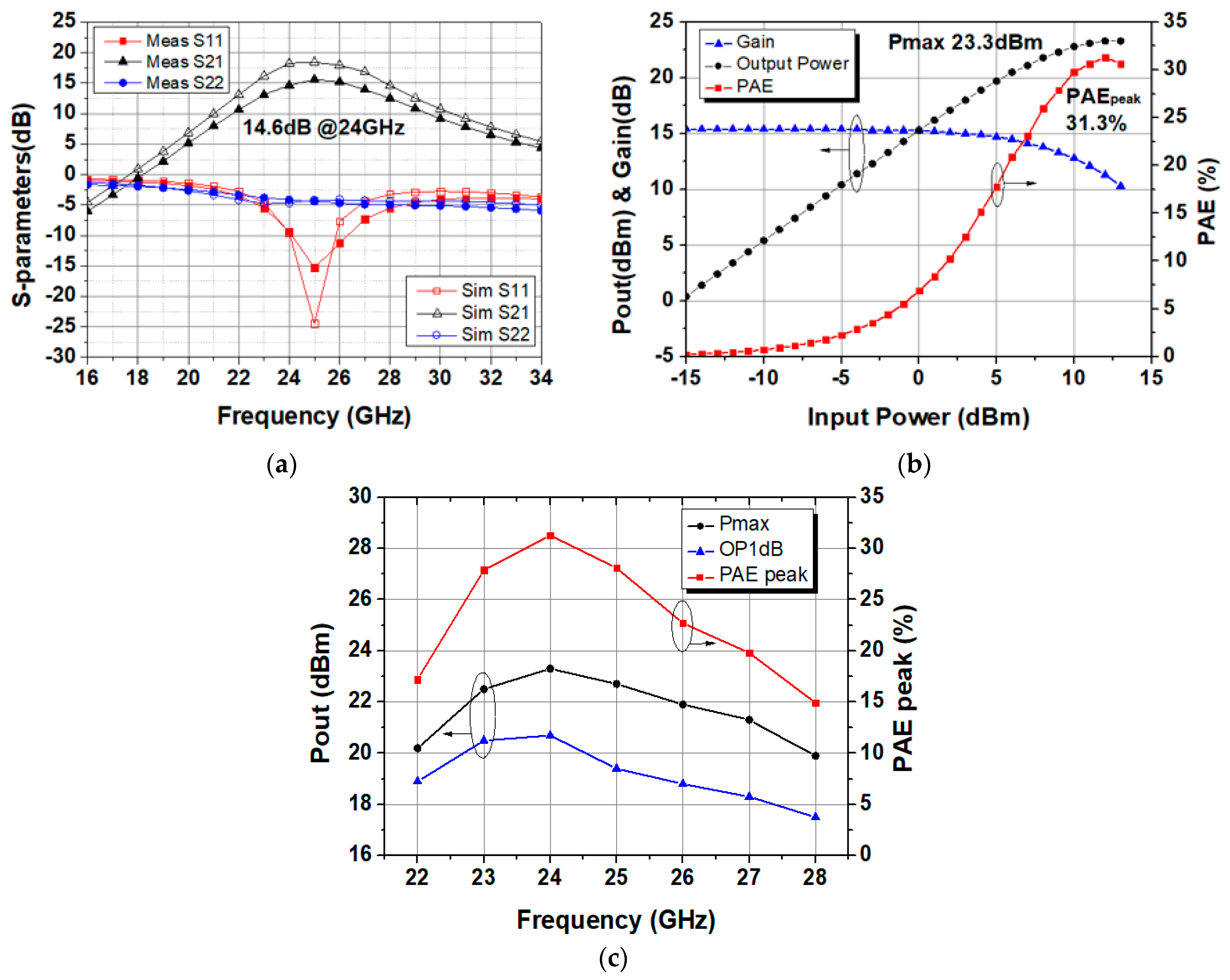

4. Measurement Results

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Lei, M.F.; Tsai, Z.M.; Lin, K.Y.; Wang, H. Design and analysis of stacked power amplifier in series-input and series-output configuration. IEEE Trans. Microw. Theory Tech. 2007, 55, 2802–2812. [Google Scholar] [CrossRef]

- Chen, J.H.; Helmi, S.R.; Azadegan, R.; Aryanfar, F.; Mohammadi, S. A broadband stacked power amplifier in 45-nm CMOS SOI technology. IEEE J. Solid State Circuits. 2013, 48, 2775–2784. [Google Scholar] [CrossRef]

- Apostolidou, M.; van der Heijden, M.P.; Leenaerts, D.M.W.; Sonsky, J.; Heringa, A.; Volokhine, I. A 65 nm CMOS 30 dBm class-E RF power amplifier with 60% power added efficiency. In Proceedings of the 2008 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Atlanta, GA, USA, 15–17 June 2008; pp. 141–144. [Google Scholar]

- Chan, W.L.; Long, J.R. A 58–65 GHz neutralized CMOS power amplifier with PAE above 10% at 1-V supply. IEEE J. Solid State Circuits. 2010, 45, 554–564. [Google Scholar] [CrossRef]

- Razavi, B. Design of Analog CMOS Integrated Circuits; McGraw-Hill Series in Electrical and Computer Engineering; McGraw-Hill: New York, NY, USA, 2001; pp. 80–85. [Google Scholar]

- Huang, W.C.; Lin, J.L.; Lin, Y.H.; Wang, H. A K-band power amplifier with 26-dBm output power and 34% PAE with novel inductance-based neutralization in 90-nm CMOS. In Proceedings of the 2018 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Philadelphia, PA, USA, 10–12 June 2018; pp. 228–231. [Google Scholar]

- Shakib, S.; Elkholy, M.; Dunworth, J.; Aparin, V.; Entesari, K. A wideband 28GHz power amplifier supporting 8 × 100MHz carrier aggregation for 5G in 40nm CMOS. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 44–45. [Google Scholar]

- Liu, J.Y.C.; Chan, C.T.; Hsu, S.S.H. A K-band power amplifier with adaptive bias in 90-nm CMOS. In Proceedings of the 2014 European Microwave Integrated Circuit Conference (EuMIC), Rome, Italy, 6–7 October 2014; pp. 1376–1379. [Google Scholar]

- Yeh, J.F.; Hsiao, Y.F.; Tsai, J.H.; Huang, T.W. MMW ultra-compact N-way transformer PAs using bowtie-radial architecture in 65-nm CMOS. IEEE Microw. Wirel. Compon. Lett. 2015, 25, 460–462. [Google Scholar] [CrossRef]

- Lin, J.L.; Lin, Y.H.; Hsiao, Y.H.; Wang, H. A K-band transformer based power amplifier with 24.4-dBm output power and 28% PAE in 90-nm CMOS technology. In Proceedings of the 2017 IEEE MTT-S International Microwave Symposium (IMS), Honololu, HI, USA, 4–9 June 2017; pp. 31–34. [Google Scholar]

- Alsuraisry, H.; Cheng, J.H.; Luo, S.J.; Lin, W.J.; Tsai, J.H.; Huang, T.W. A 24-GHz transformer-based stacked-FET power amplifier in 90-nm CMOS technology. In Proceedings of the 2015 IEEE Asia Pacific Microwave Conference (APMC), Nanjing, China, 6–9 December 2015; pp. 1–3. [Google Scholar]

- Ali, S.N.; Agarwal, P.; Renaud, L.; Molavi, R.; Mirabbasi, S.; Pande, P.P.; Heo, D. A 40% PAE frequency-reconfigurable CMOS power amplifier with tunable gate–drain neutralization for 28-GHz 5G radios. IEEE Trans. Microw. Theory Tech. 2018, 66, 2231–2245. [Google Scholar] [CrossRef]

| Ref | Process | Freq. (GHz) | Gain (dB) | Psat (dBm) | PAEpeak (%) | OP1dB (dBm) | Structure | Power Combining | P.D. * (mW/mm2) |

|---|---|---|---|---|---|---|---|---|---|

| [6] | 90 nm CMOS | 24 | 17.4 | 25.6 | 32.8 | 23.6 | 1-stage Cascode | 2-way | 905.4 ** |

| [7] | 40 nm CMOS | 27 | 22.4 | 15.1 | 33.7 | 13.7 | 3-stage (Cascode + CS) | 1 | 140.7 |

| [8] | 90 nm CMOS | 21 | 26.9 | 20.4 | 17.3 | 18.5 | 2-stage Cascode | 1 | 148.2 ** |

| [9] | 65 nm CMOS | 23.5 | 10.2 | 26.1 | 19.3 | 23.9 | 1-stage Cascode | 4-way | 636.5 ** |

| [10] | 90 nm CMOS | 24 | 14.1 | 24.4 | 28 | 21.7 | 1-stage Cascode | 2-way | 523.6 ** |

| [11] | 90 nm CMOS | 24 | 11.5 | 21.7 | 16.7 | 18.9 | 1-stage Stacked | 2-way | 547.8 ** |

| [12] | 65 nm CMOS | 24 | 9.1 | 14.7 | 42.6 | 13.9 | 1-Stage CS | 1 | 268.3 |

| This work | 65 nm LP CMOS | 24 | 15.4 | 23.3 | 31.3 | 20.8 | 1-stage Cascode | 1 | 1745.3 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Choi, K.-J.; Park, J.-H.; Kim, S.-K.; Kim, B.-S. K-Band Hetero-Stacked Differential Cascode Power Amplifier with High Psat and Efficiency in 65 nm LP CMOS Technology. Electronics 2021, 10, 890. https://doi.org/10.3390/electronics10080890

Choi K-J, Park J-H, Kim S-K, Kim B-S. K-Band Hetero-Stacked Differential Cascode Power Amplifier with High Psat and Efficiency in 65 nm LP CMOS Technology. Electronics. 2021; 10(8):890. https://doi.org/10.3390/electronics10080890

Chicago/Turabian StyleChoi, Kyu-Jin, Jae-Hyun Park, Seong-Kyun Kim, and Byung-Sung Kim. 2021. "K-Band Hetero-Stacked Differential Cascode Power Amplifier with High Psat and Efficiency in 65 nm LP CMOS Technology" Electronics 10, no. 8: 890. https://doi.org/10.3390/electronics10080890