Analysis and Design of a Fully-Integrated High-Power Differential CMOS T/R Switch and Power Amplifier Using Multi-Section Impedance Transformation Technique

Abstract

:1. Introduction

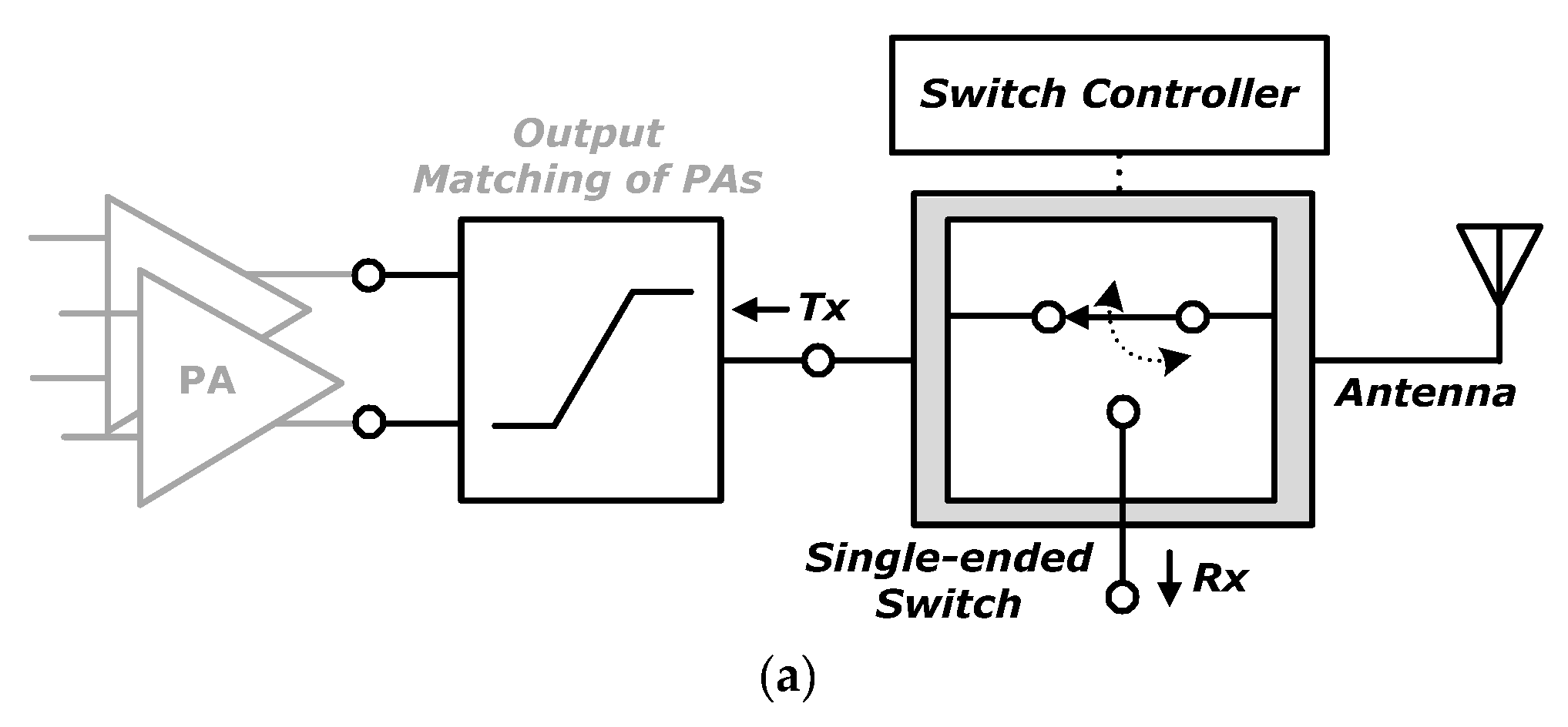

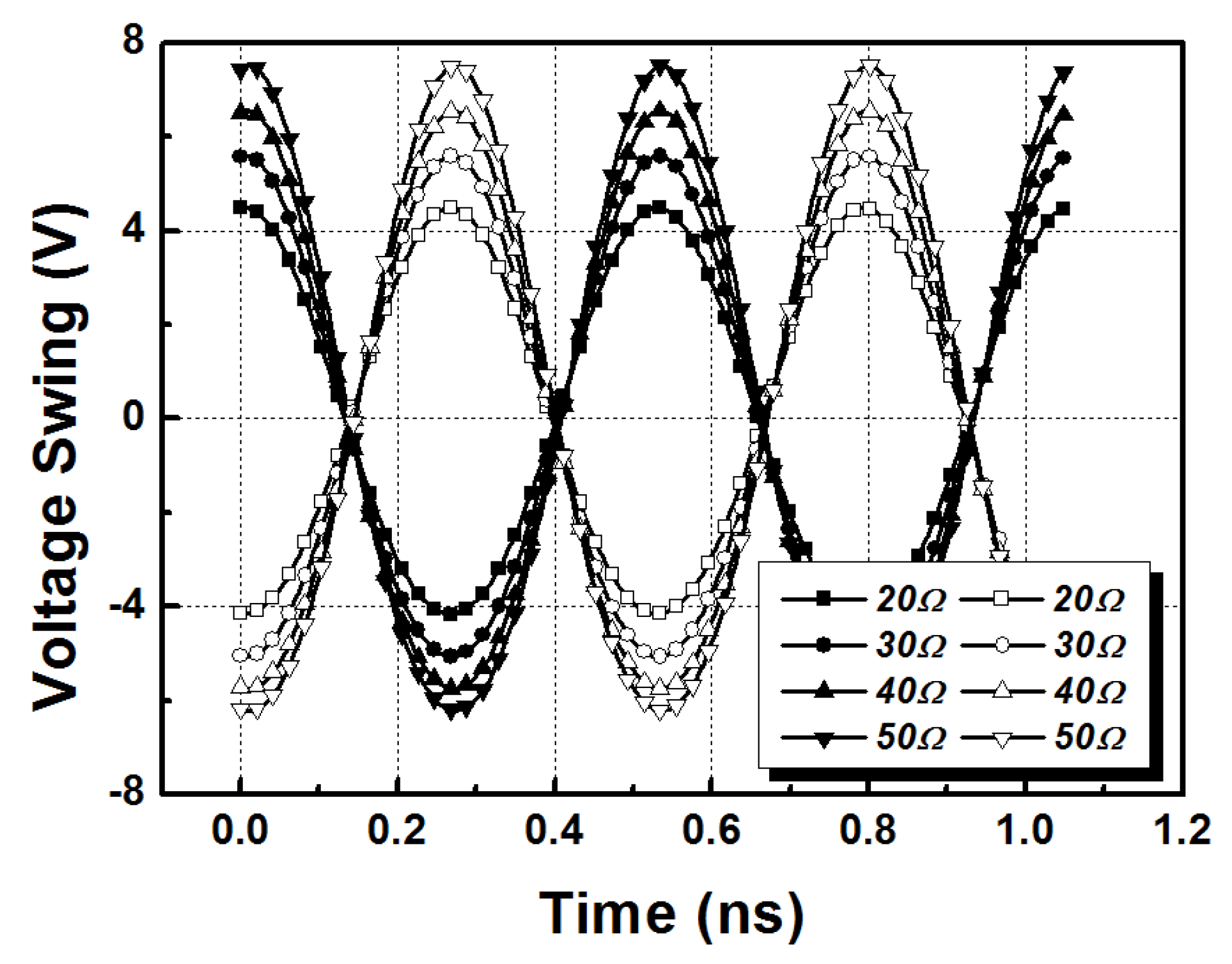

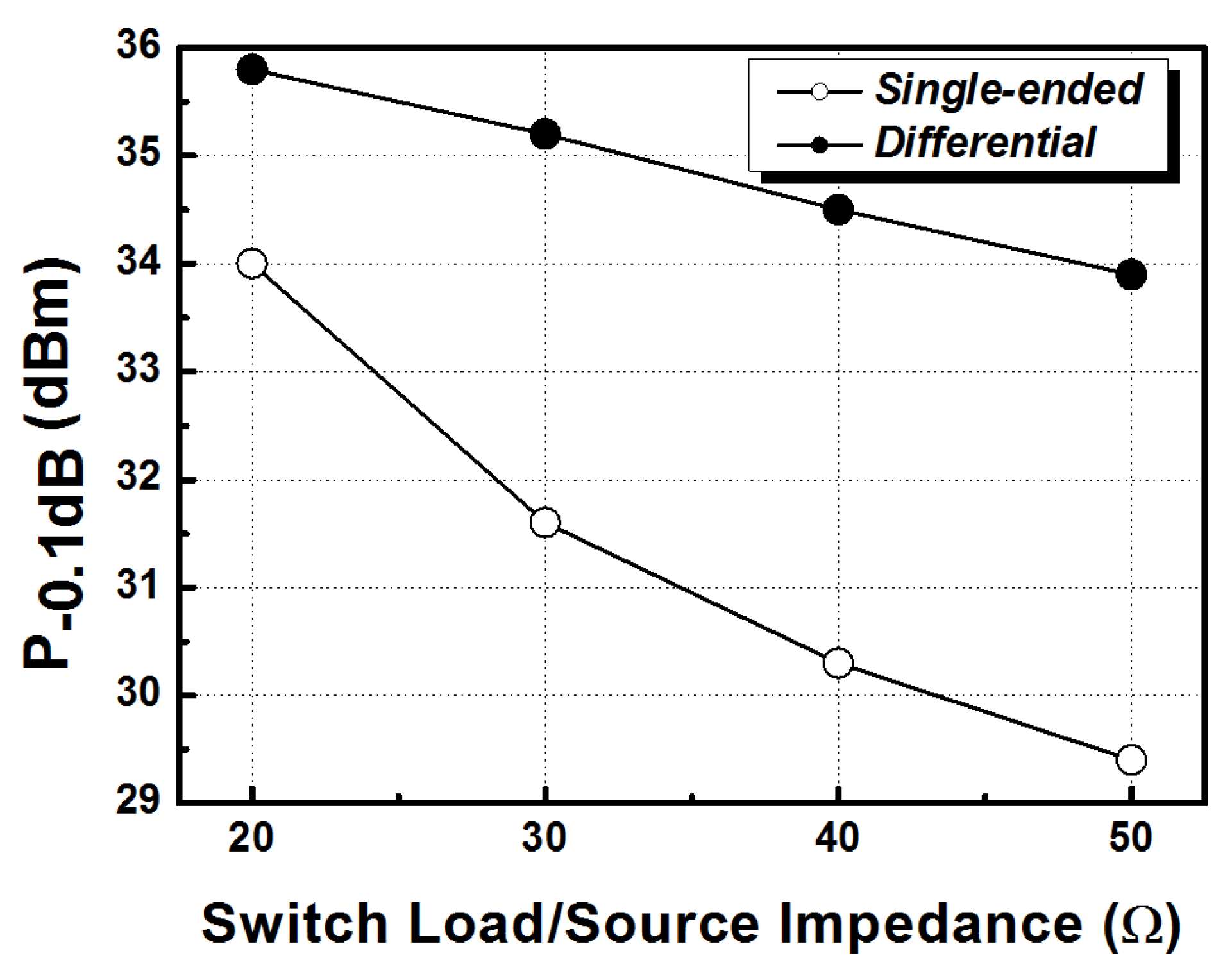

2. Proposed High-Power CMOS T/R Switch Structure

3. Loss Analysis

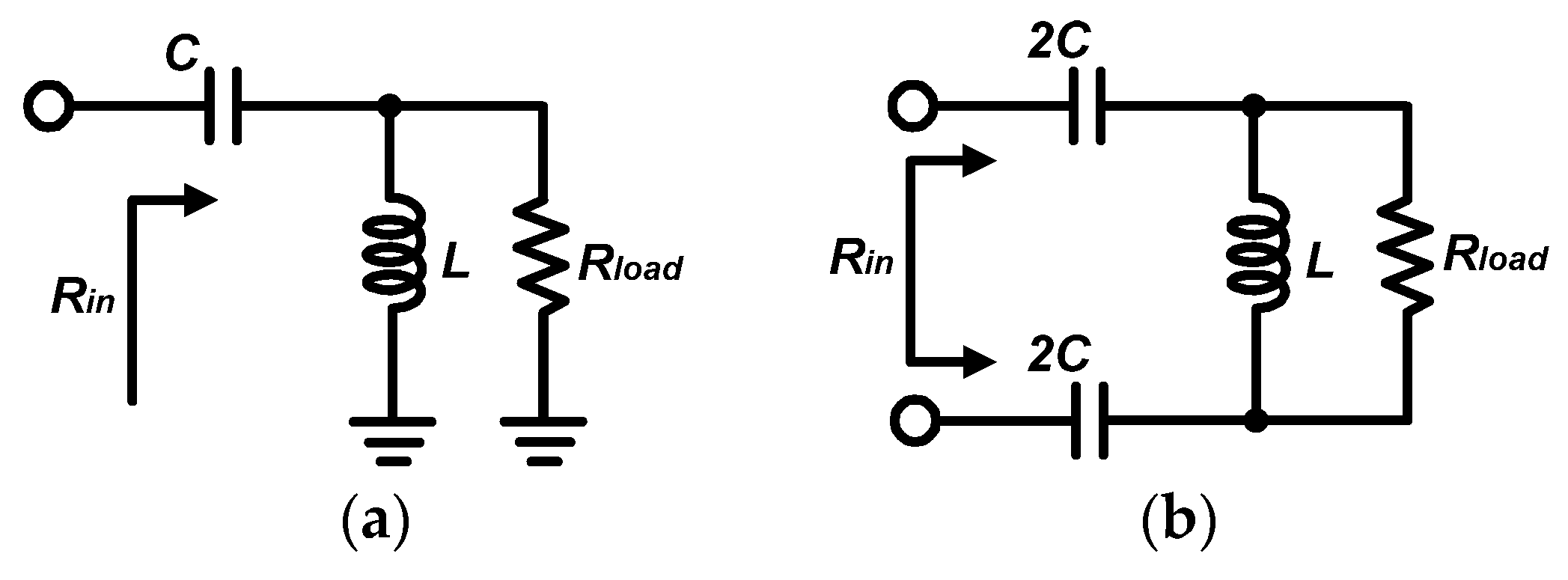

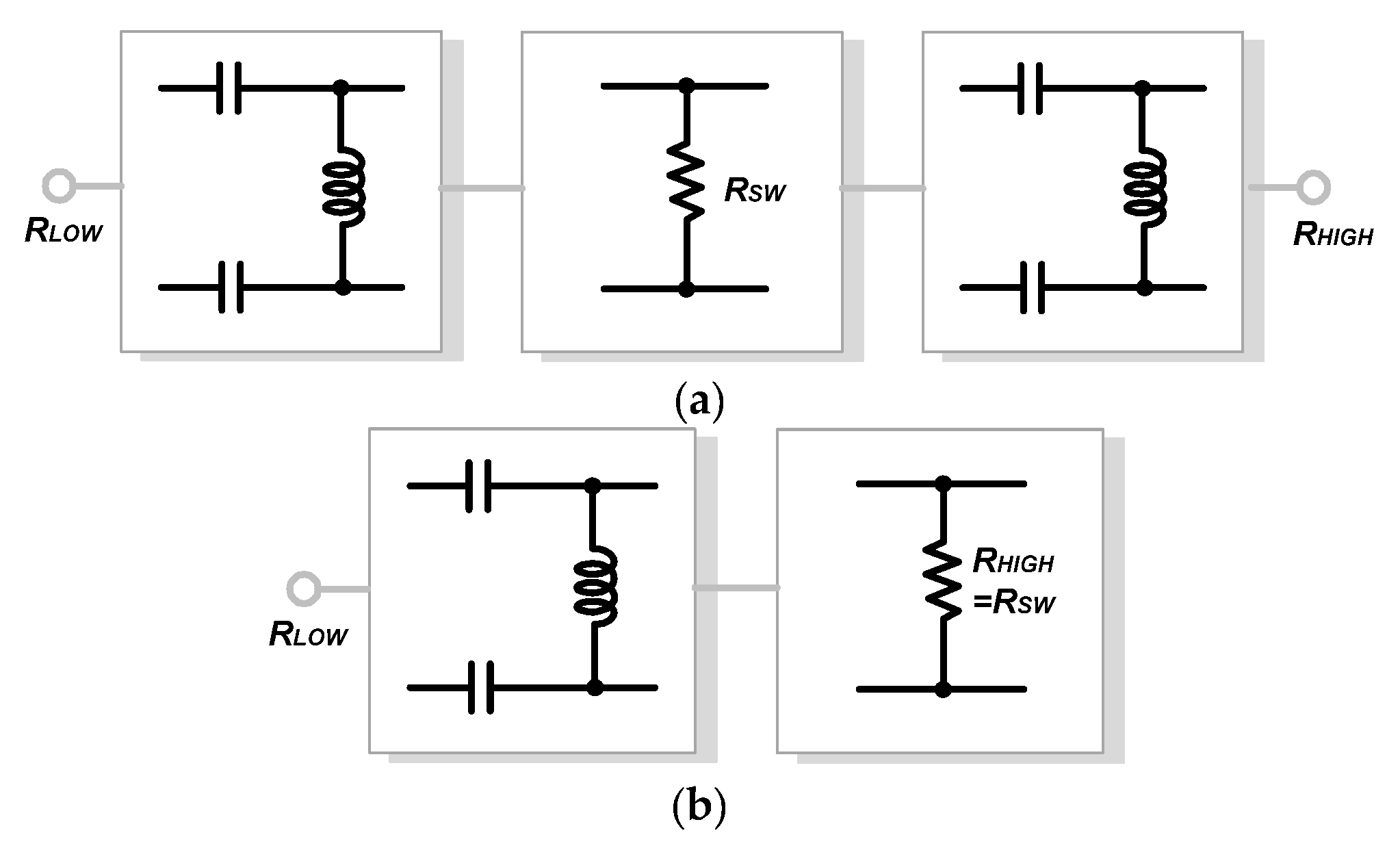

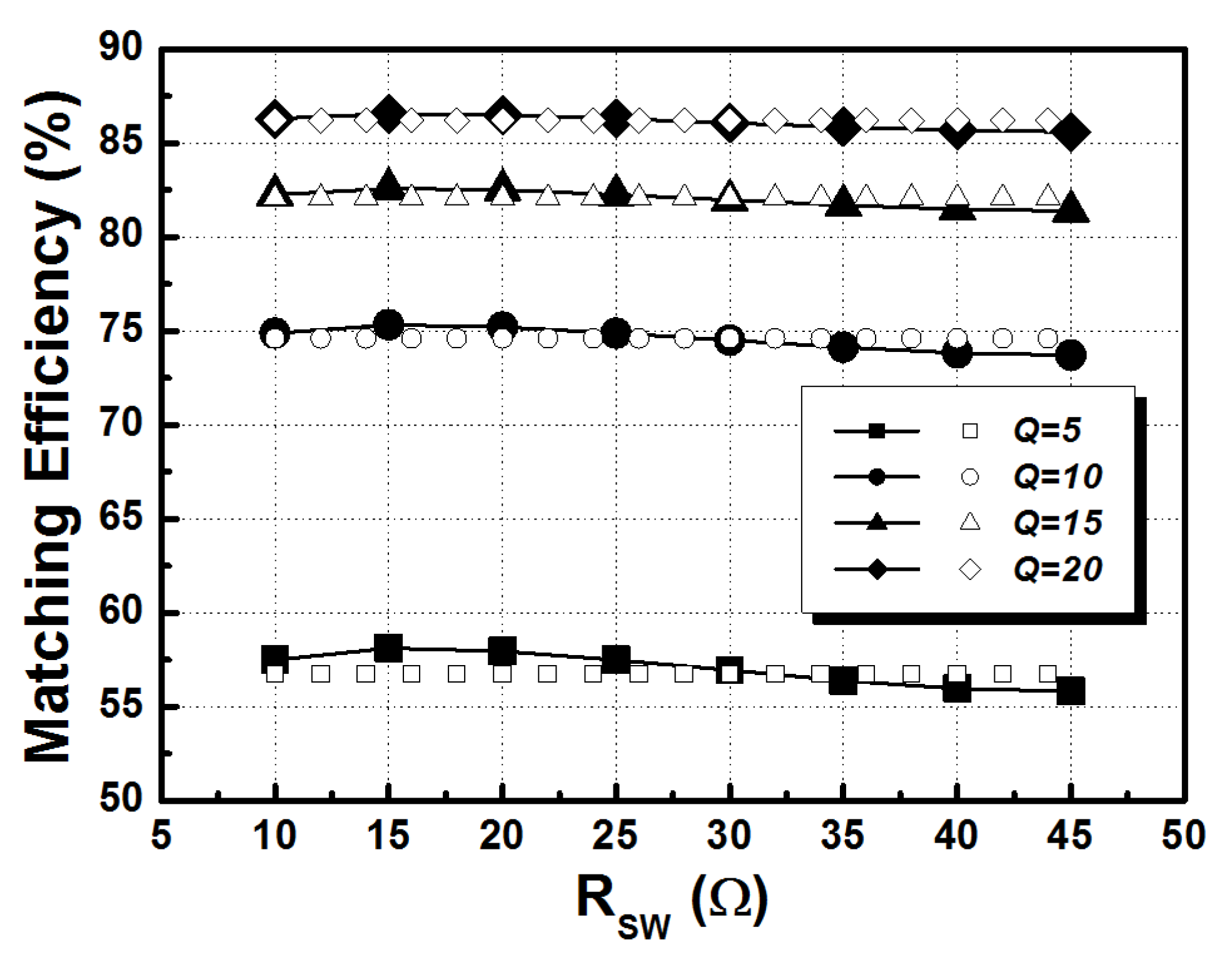

3.1. Multi-Section Impedance Transformation

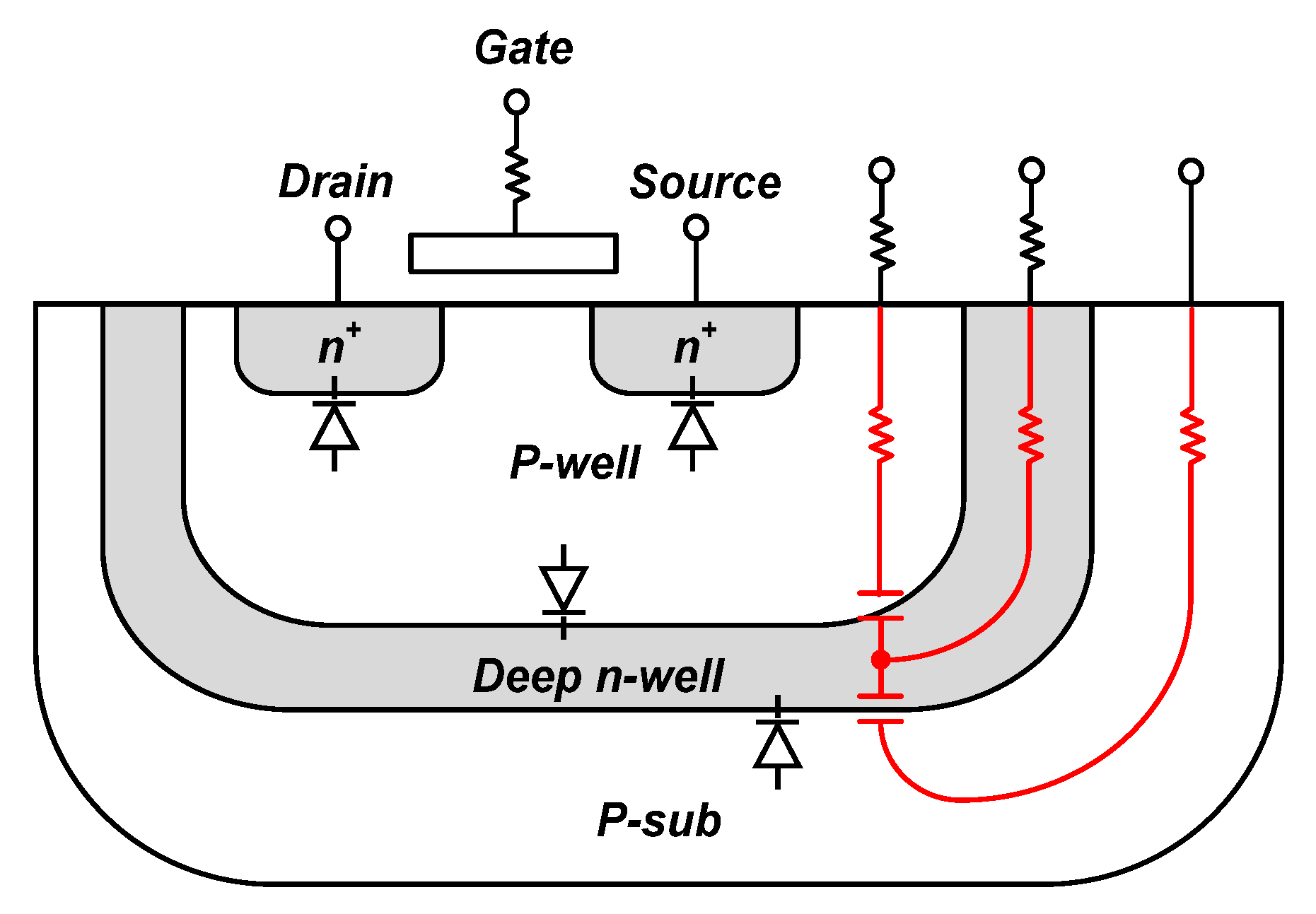

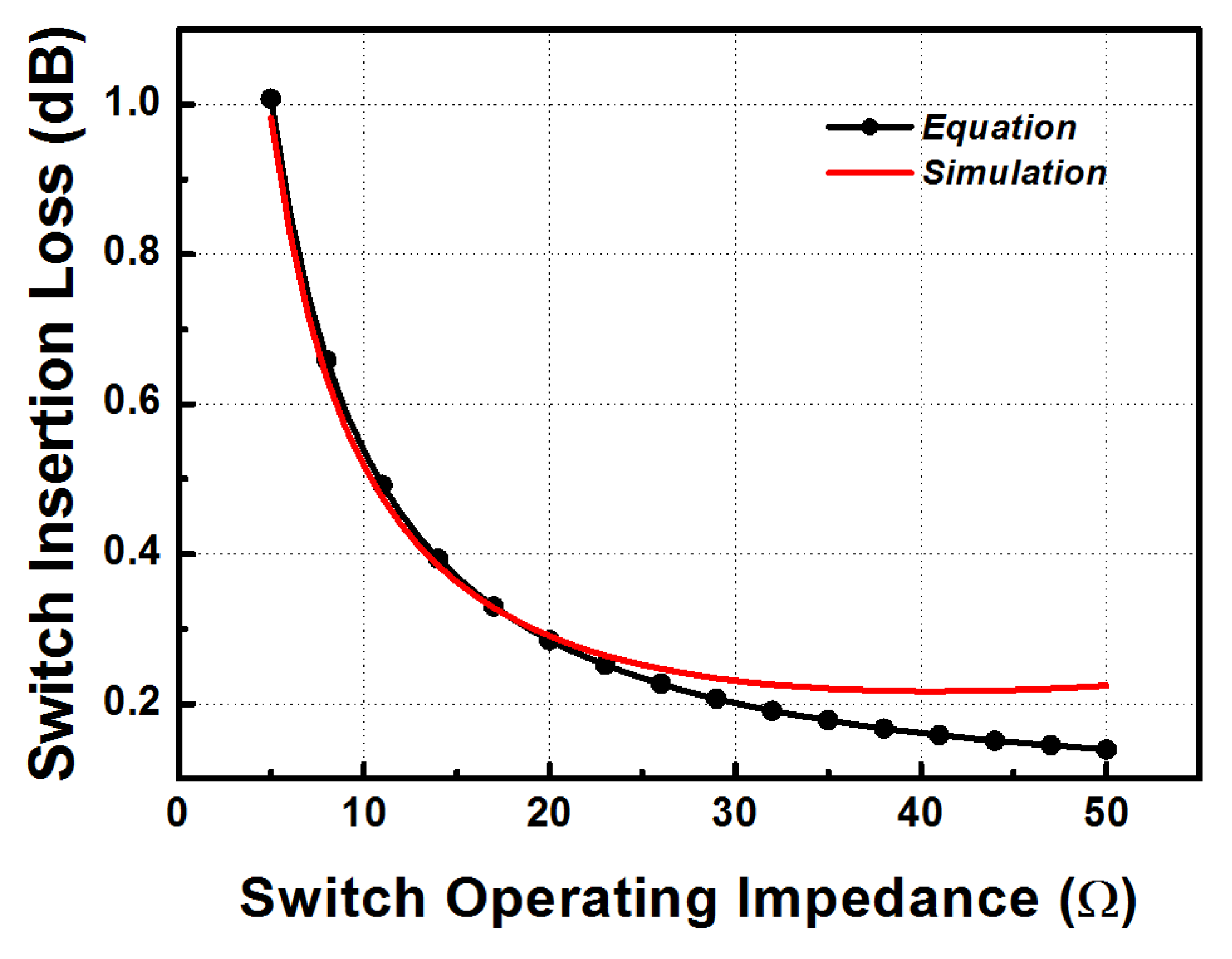

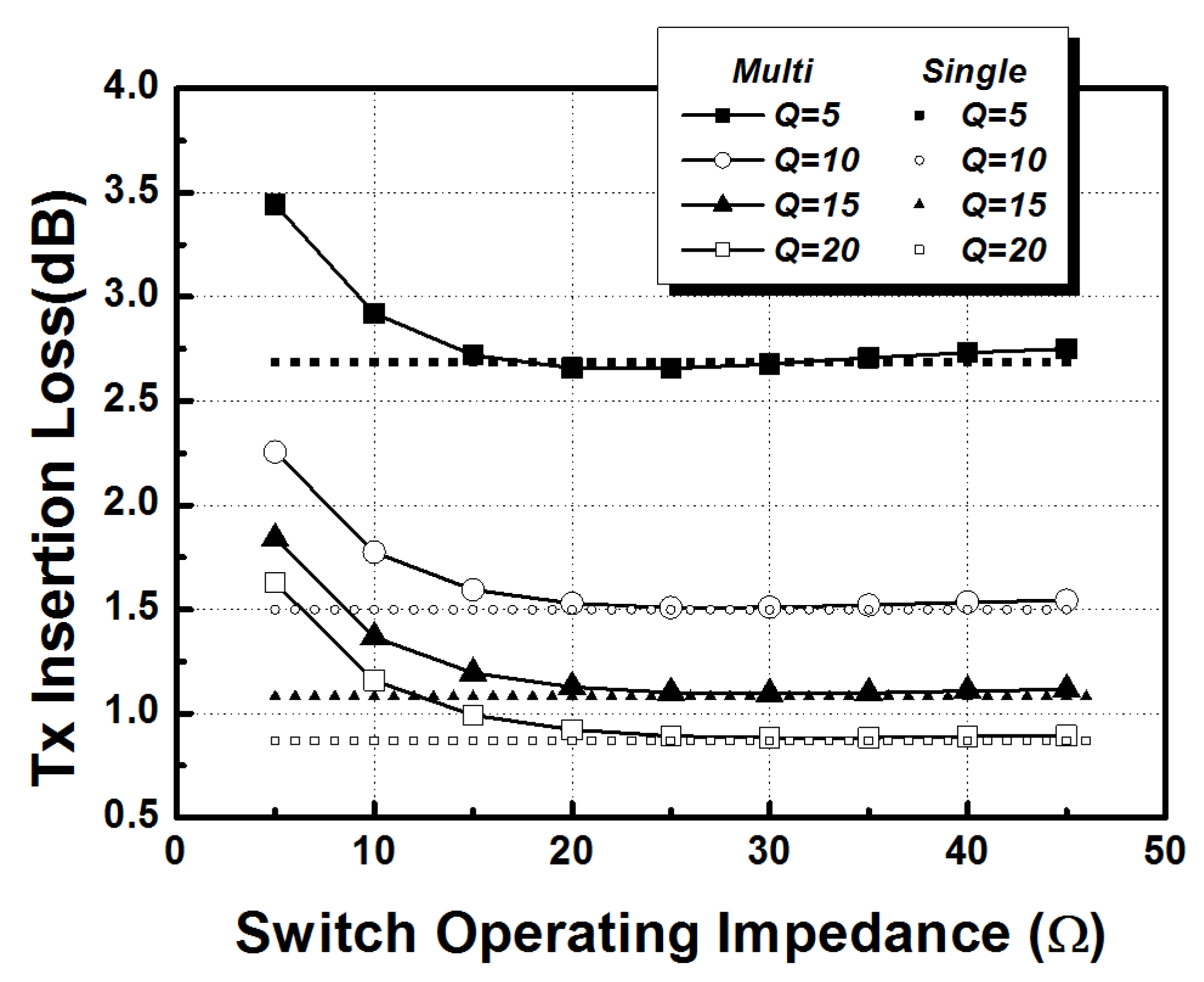

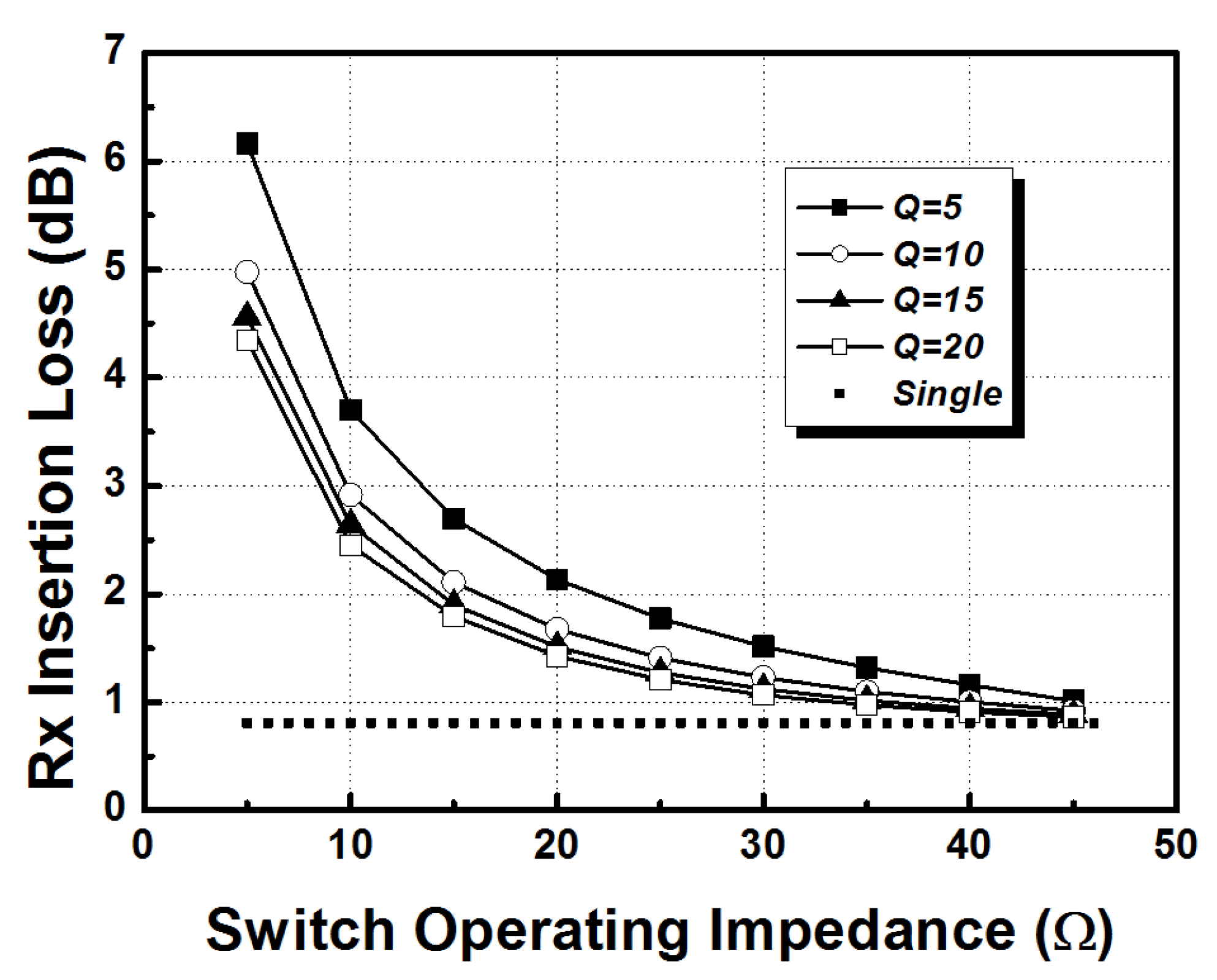

3.2. Switch Insertion Loss

3.3. Total Loss

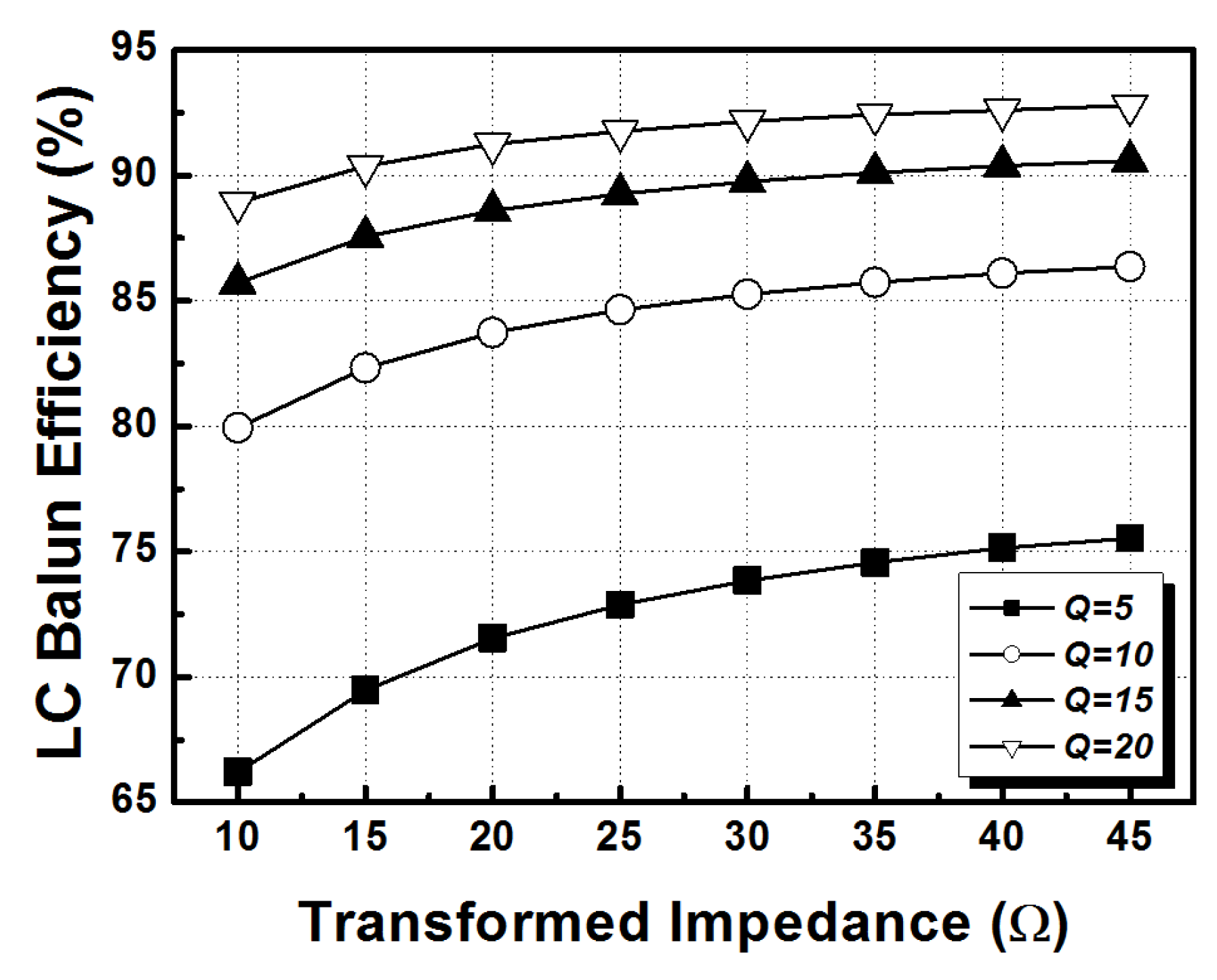

3.4. LC Balun Efficiency

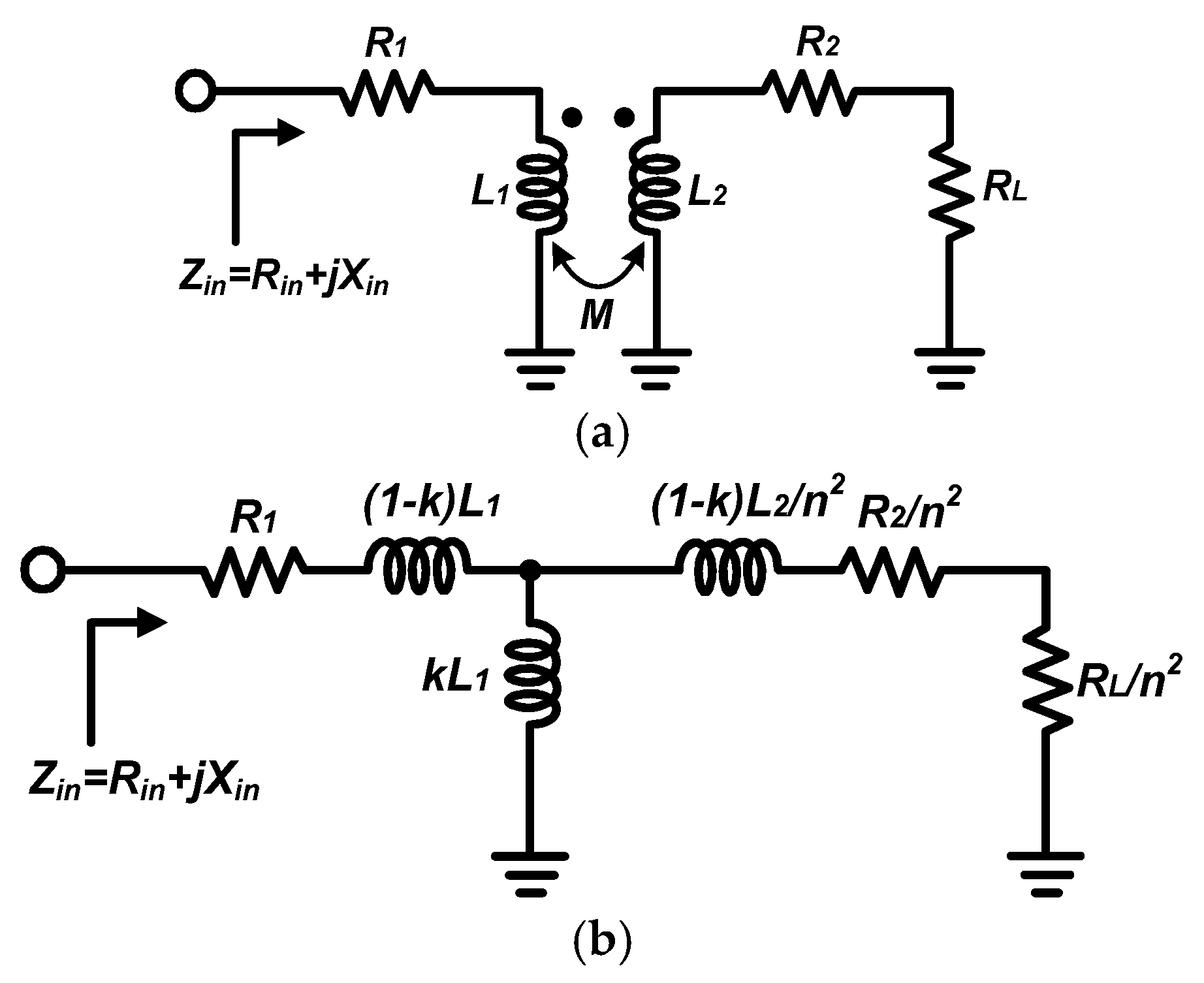

3.5. Transformer Efficiency

4. Design and Implementations

5. Measurement Results

6. Discussion

Author Contributions

Funding

Conflicts of Interest

References

- Abidi, A.A. RF CMOS comes of age. IEEE J. Solid-State Circuits 2004, 39, 549–561. [Google Scholar] [CrossRef]

- Ohnakado, T.; Yamakawa, S.; Murakami, T.; Furukawa, A.; Taniguchi, E.; Ueda, H.; Suematsu, N.; Oomori, T. 21.5-dBm power-handling 5-GHz transmit/receive CMOS switch realized by voltage division effect of stacked transistor configuration with depletion-layer-extended transistors (DETs). IEEE J. Solid-State Circuits 2004, 39, 577–584. [Google Scholar] [CrossRef]

- Talwalkar, N.A.; Yue, C.P.; Gan, H.; Wong, S.S. Integrated CMOS transmit-receive switch using LC-tuned substrate bias for 2.4-GHz and 5.2-GHz applications. IEEE J. Solid-State Circuits 2004, 39, 863–8702004. [Google Scholar] [CrossRef]

- Yeh, M.-C.; Tsai, Z.-M.; Liu, R.-C.; Lin, K.-Y.; Chang, Y.-T.; Wang, H. Design and analysis for a miniature CMOS SPDT switch using body-floating technique to improve power performance. IEEE Trans. Microw. Theory Tech. 2006, 54, 31–39. [Google Scholar]

- Huang, F.-J.; Kenneth, K.O. Single-pole double-throw CMOS switches for 900-MHz and 2.4-GHz applications on p-silicon substrates. IEEE J. Solid-State Circuits 2004, 39, 35–41. [Google Scholar] [CrossRef]

- Li, Q.; Zhang, Y.P. CMOS T/R switch design: Towards ultra-wideband and high frequency. IEEE J. Solid-State Circuits 2007, 42, 563–570. [Google Scholar] [CrossRef]

- Kidwai, A.A.; Fu, C.-T.; Jenson, J.C.; Taylor, S.S. A fully integrated ultra-low insertion loss T/R switch for 802.11b/g/n application in 90nm CMOS process. IEEE J. Solid-State Circuits 2009, 44, 1352–1360. [Google Scholar] [CrossRef]

- Xu, H.; Kenneth, K.O. A 31.3-dBm bulk CMOS T/R switch using stacked transistors with sub-design-rule channel length in floated p-wells. IEEE J. Solid-State Circuits 2007, 42, 2528–2534. [Google Scholar] [CrossRef]

- Costa, J.; Carroll, M.; Jorgenson, J.; Mckay, T.; Ivanov, T.; Dinh, T.; Kozuch, D.; Remoundos, G.; Kerr, D.; Tombak, A.; et al. A silicon RFCMOS SOI technology for integrated cellular/WLAN RF TX modules. In Proceedings of the IEEE MTT-S International Microwave Symposium, Honolulu, HI, USA, 3–8 June 2007; pp. 445–448. [Google Scholar]

- Carroll, M.; Kerr, D.; Iversen, C.; Tombak, A.; Pierres, J.-B.; Mason, P.; Costa, J. High-resistivity SOI CMOS cellular antenna switches. In Proceedings of the IEEE Compound Semiconductor Integrated Circuit Symposium, Greensboro, NC, USA, 11–14 October 2009; pp. 1–4. [Google Scholar]

- Miyatsuji, K.; Ueda, D. A GaAs high power RF single-pole dual throw switch IC for digital-mobile communication system. IEEE J. Solid-State Circuits 1995, 30, 979–983. [Google Scholar] [CrossRef]

- Numata, K.; Takahashi, Y.; Maeda, T.; Hida, H. A +2.4/0V controlled high power GaAs SPDT antenna switch IC for GSM application. In Proceedings of the 2002 IEEE Radio Frequency Integrated Circuits (RFIC) Symposium. Digest of Papers (Cat. No.02CH37280), Seattle, WA, USA, 3–4 June 2002; pp. 141–144. [Google Scholar]

- Aoki, I.; Kee, S.D.; Rutledge, D.B.; Hajimiri, A. Fully integrated CMOS power amplifier design using the distributed active-transformer architecture. IEEE J. Solid-State Circuits 2002, 37, 371–383. [Google Scholar] [CrossRef] [Green Version]

- An, K.H.; Lee, O.; Kim, H.; Lee, D.H.; Han, J.; Yang, K.S.; Kim, Y.; Chang, J.J.; Woo, W.; Lee, C.-H.; et al. Power-combining transformer techniques for fully-integrated CMOS power amplifiers. IEEE J. Solid-State Circuits 2008, 43, 1064–1075. [Google Scholar] [CrossRef]

- Kim, H.-W.; Ahn, M.; Lee, O.; Kim, H.; Kim, Y.Y.H.S.; Lee, C.-H.; Laskar, J. Design and Analysis of CMOS T/R Switches with the Impedance Transformation Technique. IEEE Microw. Wirel. Compon. Lett. 2017, 27, 1137–1139. [Google Scholar] [CrossRef]

- Kim, H.-W.; Ahn, M.; Lee, O.; Lee, C.-H.; Laskar, J. A high power CMOS differential T/R switch using multi-section impedance transformation technique. In Proceedings of the 2010 IEEE Radio Frequency Integrated Circuits Symposium, Anaheim, CA, USA, 23–25 May 2010; pp. 483–486. [Google Scholar]

- Aoki, I.; Kee, S.D.; Rutledge, D.B.; Hajimiri, A. Distributed active transformer—A new power-combining and impedance-transformation technique. IEEE Trans. Microw. Theory Tech. 2002, 50, 316–331. [Google Scholar] [CrossRef] [Green Version]

- Huang, F.-J.; Kenneth, K.O. A 0.5-µm CMOS T/R switch for 900-MHz wireless applications. IEEE J. Solid-State Circuits 2001, 36, 486–492. [Google Scholar] [CrossRef]

- Ahn, M.; Kim, H.-W.; Lee, C.-H.; Laskar, J. A 1.8-GHz 33-dBm P0.1-dB CMOS T/R switch using stacked FETs witch feed-forward capacitors in a floated well structure. IEEE Trans. Microw. Theory Tech. 2009, 57, 2261–2670. [Google Scholar]

- Reynaert, P.; Steyaert, M. A 2.45-GHz 0.13-µm CMOS PA with parallel amplification. IEEE J. Solid-State Circuits 2007, 42, 551–562. [Google Scholar] [CrossRef]

- Lee, O.; An, K.H.; Kim, H.; Lee, D.H.; Han, J.; Yang, K.S.; Lee, C.-H.; Kim, H.; Laskar, J. Analysis and design of fully integrated high-power parallel-circuit class-E CMOS power amplifiers. IEEE Trans. Circuits Syst. I Reg. Papers 2010, 57, 725–734. [Google Scholar] [CrossRef]

- DiCarlo, P.; Boerman, S.; Burton, R.; Chung, H.-C.; Evans, D.; Gerard, M.; Gering, J.; Khayo, I.; Lagrandier, L.; Lalicevic, I.; et al. A highly integrated quad-band GSM TX-front-end-module. In Proceedings of the 25th Annual Technical Digest 2003. IEEE Gallium Arsenide Integrated Circuit (GaAs IC) Symposium, 2003, San Diego, CA, USA, 9–12 November 2003; pp. 280–283. [Google Scholar]

- De Graauw, A.J.M.; van Bezooijen, A.; Chanlo, C.; den Dekker, A.; Dijkhuis, J.; Pramm, S.; ten Dolle, H.K.J. Miniaturized quad-band front-end module for GSM using Si BiCMOS and passive integration technologies. In Proceedings of the IEEE Bipolar/BiCMOS Circuits and Technology Meeting (BCTM), Maastricht, The Netherlands, 8–10 October 2006; pp. 1–4. [Google Scholar]

- Jeon, J.; Kuhn, W.B. A UHF CMOS transceiver front-end with a resonant TR switch. In Proceedings of the IEEE Radio and Wireless Symposium (RWS), Long Beach, CA, USA, 9–11 January 2007; pp. 71–74. [Google Scholar]

- Ahn, M.; An, K.H.; Lee, C.; Laskar, J.; Kim, H. Fully integrated high-power RF front-end circuits in 2 GHz using 0.18μm standard CMOS process. In Proceedings of the IEEE Asia-Pacific Microwave Conference (APMC), Hong Kong, China, 16–20 December 2008; pp. 1–4. [Google Scholar]

| Process | Freq. | Features | Supply Volt. | Pout (dBm)/ PAE | |

|---|---|---|---|---|---|

| [22] | GaAs/ pHEMT | 900 MHz | pHEMT switch | 5 V | POUT: 34 PAE: 45% |

| [23] | BiCMOS | 870 MHz | pHEMT switch | 3.5 V | POUT: 32 PAE: 35% |

| [24] | CMOS SOI | 400 MHz | Resonant switch UHF application | 3.3 V | POUT: 29 PAE: 29% |

| [25] | 0.18 µm CMOS | 2 GHz | Transistor stacking LNA design included | 3.3 V | POUT: 29.7 PAE: 35% |

| This work | 0.18 µm CMOS | 1.9 GHz | Diff. topology Multi-sect. Impedance matching | 3.3 V | POUT: 32.1 PAE: 38.3% |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, H.-W.; Ahn, M.; Lee, O.; Kim, H.; Kim, H.; Lee, C.-H. Analysis and Design of a Fully-Integrated High-Power Differential CMOS T/R Switch and Power Amplifier Using Multi-Section Impedance Transformation Technique. Electronics 2021, 10, 1028. https://doi.org/10.3390/electronics10091028

Kim H-W, Ahn M, Lee O, Kim H, Kim H, Lee C-H. Analysis and Design of a Fully-Integrated High-Power Differential CMOS T/R Switch and Power Amplifier Using Multi-Section Impedance Transformation Technique. Electronics. 2021; 10(9):1028. https://doi.org/10.3390/electronics10091028

Chicago/Turabian StyleKim, Hyun-Woong, Minsik Ahn, Ockgoo Lee, Hyoungsoo Kim, Hyungwook Kim, and Chang-Ho Lee. 2021. "Analysis and Design of a Fully-Integrated High-Power Differential CMOS T/R Switch and Power Amplifier Using Multi-Section Impedance Transformation Technique" Electronics 10, no. 9: 1028. https://doi.org/10.3390/electronics10091028