Hunting Energy Bugs in Embedded Systems: A Software-Model-In-The-Loop Approach

Abstract

:1. Introduction

- RQ1:

- How can energy bugs, as the energy-related misbehavior of embedded systems, be described and classified, and which constraints should be considered?

- RQ2:

- How can software application models be extended to consider functionalities and energy-related characteristics of the hardware platform so that an energy model is created along with the software model to make interactions visible and traceable?

- RQ3:

- How can the energy-related impact of software application models be determined and energy bugs identified if the hardware platform is not or only partially defined?

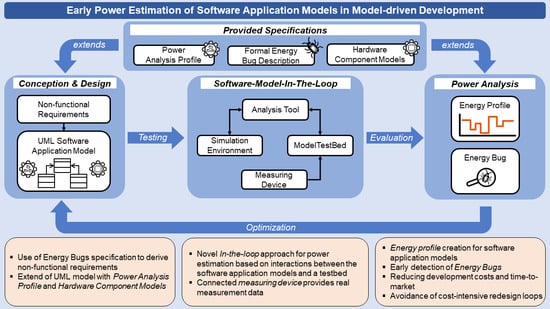

- A formal description and classification of energy-related bugs to specify energy-related NFRs. The concept of energy bugs is integrated into the automatic power analysis and evaluation of NFRs in early phases to optimize the software application model.

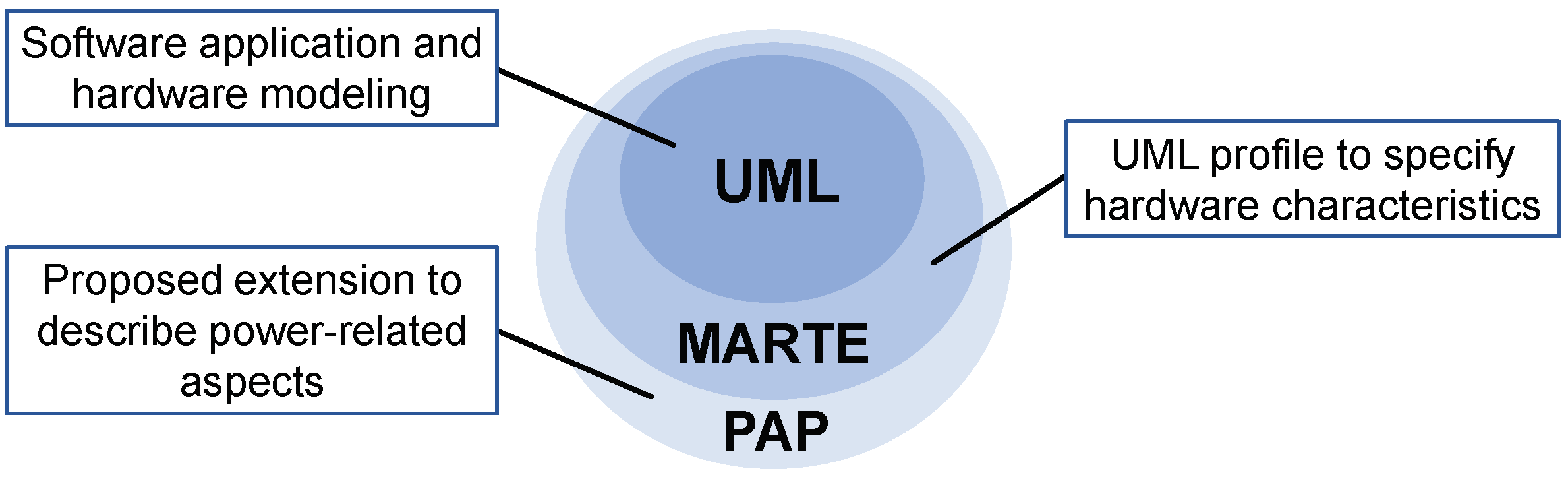

- A UML-based description of hardware components extended with a UML profile to model power-related aspects. The provided descriptions can be linked with the software application and provide interfaces for their utilization. Our approach can take the microcontroller unit (MCU) and connected peripheral devices into account, thus enabling a system-wide power estimation.

- Two methods for power estimation of software application models in MDD which are applied in different development stages. The indirect power analysis method provides a simulation-based rapid power analysis without needing an existing hardware platform. The direct power analysis method is based on a novel in-the-loop testing approach and uses a testbed for the estimation process. Additionally, the software application model can interact with the testbed, e.g., to obtain real measurement data from sensors during simulation.

2. Background

2.1. Energy Model of Hardware Components

2.2. Energy Bugs

2.2.1. Definition

2.2.2. Classification

- Type A: An incorrect hardware design or faulty hardware component leads to increased power consumption during runtime. The cause of such an error can be, for example, in the layout and become visible due to changed environmental conditions.

- Type B: Unknown or unconsidered consumers, which can be hardware or software components, lead to an increased power demand. For example, additional LEDs in the layout indicating a correct operation increase the power requirement.

- Type C: Energy bugs in this category are mainly caused by the software application itself. Flaws in the software design, incorrect utilization, or inappropriate design patterns [14] may lead to higher power consumption. Hardware components may also have a fixed energy offset described as ramp and tail energies [20,24] before and after the execution of tasks. The offset substantially affects the overall consumption if these operations are executed at a high frequency. Examples of avoidable additional power consumption are unnecessarily high sampling rates of sensors.

- Type D: Components such as MCUs and peripheral devices realize a sleep mode that is activated when the component is not accessed. Unintentional accesses can thus prevent these components from switching to a sleep mode (no-sleep bug [25]). Peripheral devices can also be bound too early or too long in specific parts of the software workflow. As a result, they may persist in a high-power state longer than necessary.

2.3. X-in-the-Loop Testing

3. Related Work

4. IoT Application Example

5. The Proposed Power Analysis Concepts and Developer Workflow

5.1. Power Analysis Concepts

5.2. Developer Workflow

6. The Proposed Hardware Component Model and Power Analysis Profile Specification

6.1. Hardware Component Model Specification

6.2. Overview: Power Analysis UML Profile

6.2.1. Hardware Abstraction Model with Energy-related Elements

6.2.2. Hardware Behavior Model with Energy-related Elements

- hasDynamicConsumption: Defines if the consumption of the state or transition is variable or static.

- hasDynamicExecutionTime: Defines if the execution time of the state or transition is variable or static.

- current: Contains the electric current consumption of a state or transition.

- executionTime: Contains the execution time of the state or transition.

6.3. Managing Dynamic Power-Related Behavior

| Listing 1. Selected parts of the value specification language specification for variables described in extended Backus–Naur form. A definition of the nonterminal symbol 〈init-expression〉 can be found in [13]. Adaptations are highlighted in bold. | ||

| 〈variable-call-expr〉 | ⊨ | 〈variable-name〉 |

| 〈variable-declaration〉 | ⊨ | [〈variable-direction〉] ‘$’ 〈variable-name〉 |

| [‘:’ 〈typename〉] [‘=’ 〈init-expression〉] | ||

| 〈variable-direction〉 | ⊨ | ‘in’ | ‘out’ ‘ | inout’ |

| 〈variable-name〉 | ⊨ | [〈namespace〉 ‘.’] | 〈body-text〉 |

| 〈namespace〉 | ⊨ | 〈pap-prefix〉 [ ‘.’ 〈pap-postfix〉 ] 〈body-text〉 |

| 〈pap-prefix〉 | ⊨ | ‘PAP’ |

| 〈pap-postfix〉 | ⊨ | ‘SM’ | ‘ATTR’ |

| 〈body-text〉 | ⊨ | terminal symbol consisting of string of characters |

- If a variable for PAP is defined, the namespace has to start with a specific prefix, while the use of the postfix is optional and depends on the type of reference.

- For the prefix, the term PAP has to be used.

- The postfix can be one of the two terms SM or ATTR.

7. Implementation of the Power Analysis Process and IoT Application

7.1. Unit for Central Control and Estimation

7.2. Hardware-Based ModelTestBed

| Listing 2.ModelRPC example: client enables an LED connected to GPIO 33. | |

| { | |

| "modelrpc" | : "2.0", |

| "method" | : "pin.set", |

| "params" | : { "device" : { "gpio" : 33 }} |

| } | |

7.3. Example Application

7.3.1. Hardware Component Models of the Beehive Microclimate Sensor Node Example

7.3.2. Software Application Model of the Beehive Microclimate Sensor Node Example

8. Experimental Setup and Results

- Accuracy of the estimation process for the IoT application example (Section 8.2).

- Time delays of the DPA (Section 8.3).

- Power overhead of the DPA (Section 8.4).

- Identification of energy bugs (Section 8.5).

8.1. Research Methodology and Setup

8.2. Power Consumption Estimation of the IoT Application Example

8.3. Time Delay of the Direct Power Analysis

8.4. Power and Time Overhead of the Presented Approach

8.5. Identifying Energy Bugs

- NFR1

- The LoRa module (rak811) shall not consume more than 16 µA when the device is operating in a low-power mode.

- NFR2

- The total energy of the LoRa module (rak811) during a single sleep phase period of 10 min shall not exceed J.

9. Discussion

10. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Morrish, J.; Arnott, M. Global IoT Forecast Report, 2020–2030. Available online: https://transformainsights.com/research/reports/global-iot-forecast-report-2020-2030 (accessed on 31 March 2022).

- Friedli, M.; Kaufmann, L.; Paganini, F.; Kyburz, R. Energy efficiency of the Internet of Things. In Technology and Energy Assessment Report Prepared for IEA 4E EDNA; Lucerne University of Applied Sciences: Luzern, Switzerland, 2016. [Google Scholar]

- World Bank Group. Commodity Markets Outlook: Causes and Consequences of Metal Price Shocks. Available online: https://openknowledge.worldbank.org/handle/10986/35458 (accessed on 1 March 2022).

- Grunwald, A.; Schaarschmidt, M.; Westerkamp, C. LoRaWAN in a rural context: Use cases and opportunities for agricultural businesses. In Proceedings of the Mobile Communication-Technologies and Applications, 24. ITG-Symposium, Osnabrück, Germany, 15–16 May 2019; pp. 1–6. [Google Scholar]

- Fonseca, A.; Kazman, R.; Lago, P. A Manifesto for Energy-Aware Software. IEEE Softw. 2019, 36, 79–82. [Google Scholar] [CrossRef]

- Pinto, G.; Castor, F.; Liu, Y.D. Mining Questions about Software Energy Consumption. In Proceedings of the 11th Working Conference on Mining Software Repositories, Hyderabad, India, 31 May–1 June 2014; pp. 22–31. [Google Scholar] [CrossRef] [Green Version]

- Pang, C.; Hindle, A.; Adams, B.; Hassan, A.E. What Do Programmers Know about Software Energy Consumption? IEEE Softw. 2016, 33, 83–89. [Google Scholar] [CrossRef]

- Hansson, J.; Helton, S.; Feiler, P. ROI Analysis of the System Architecture Virtual Integration Initiative; Technical report; Carnegie-Mellon Univerity Software Engineering Institute Pittsburgh United States: Pittsburgh, PA, USA, 2018. [Google Scholar]

- Deichmann, J.; Georg, D.; Klein, B.; Mühlreiter, B.; Stein, J.P. Cracking the Complexity Code in Embedded Systems Development: How to Manage—and Eventually Master—Complexity in Embedded Systems Development. Available online: https://www.mckinsey.com/industries/advanced-electronics/our-insights/cracking-the-complexity-code-in-embedded-systems-development (accessed on 1 April 2022).

- Object Management Group. Unified Modeling Language, Version 2.5.1. OMG Document Number Formal/17-12-05. Available online: https://www.omg.org/spec/UML/2.5.1/ (accessed on 31 March 2022).

- Evans, E.; Evans, E.J. Domain-Driven Design: Tackling Complexity in the Heart of Software; Addison-Wesley Professional: Boston, MA, USA, 2004. [Google Scholar]

- Akdur, D.; Garousi, V.; Demirörs, O. A survey on modeling and model-driven engineering practices in the embedded software industry. J. Syst. Archit. 2018, 91, 62–82. [Google Scholar] [CrossRef] [Green Version]

- Object Management Group. A UML Profile for MARTE: Modeling and Analysis of Real-Time and Embedded Systems, Version 1.2. OMG Document Number formal/19-04-01. 2019. Available online: https://www.omg.org/spec/MARTE/1.2/ (accessed on 31 March 2022).

- Schaarschmidt, M.; Uelschen, M.; Pulvermüller, E.; Westerkamp, C. Framework of Software Design Patterns for Energy-Aware Embedded Systems. In Proceedings of the 15th International Conference on Evaluation of Novel Approaches to Software Engineering—Volume 1: ENASE, Prague, Czech Republic, 5–6 May 2020; pp. 62–73. [Google Scholar] [CrossRef]

- Schaarschmidt, M.; Uelschen, M.; Pulvermüller, E. Power Consumption Estimation in Model Driven Software Development for Embedded Systems. In Proceedings of the 16th International Conference on Software Technologies (ICSOFT), INSTICC, Online Streaming, 6–8 July 2021; pp. 47–58. [Google Scholar] [CrossRef]

- Uelschen, M.; Schaarschmidt, M. Software Design of Energy-Aware Peripheral Control for Sustainable Internet-of-Things Devices. In Proceedings of the 55th Hawaii International Conference on System Sciences, Maui, HI, USA, 4–7 January 2022. [Google Scholar]

- Li, D.; Hao, S.; Gui, J.; Halfond, W.G. An Empirical Study of the Energy Consumption of Android Applications. In Proceedings of the 2014 IEEE International Conference on Software Maintenance and Evolution, Victoria, BC, Canada, 29 September–3 October 2014; pp. 121–130. [Google Scholar] [CrossRef]

- Duan, L.T.; Guo, B.; Shen, Y.; Wang, Y.; Zhang, W.L. Energy analysis and prediction for applications on smartphones. J. Syst. Archit. 2013, 59, 1375–1382. [Google Scholar] [CrossRef]

- Corral, L.; Georgiev, A.B.; Sillitti, A.; Succi, G. A method for characterizing energy consumption in Android smartphones. In Proceedings of the 2nd International Workshop on Green and Sustainable Software (GREENS), San Francisco, CA, USA, 20 May 2013; pp. 38–45. [Google Scholar] [CrossRef]

- Banerjee, A.; Chong, L.K.; Chattopadhyay, S.; Roychoudhury, A. Detecting Energy Bugs and Hotspots in Mobile Apps. In Proceedings of the 22nd ACM SIGSOFT International Symposium on Foundations of Software Engineering, Hong Kong, China, 16–21 November 2014; pp. 588–598. [Google Scholar] [CrossRef]

- Pathak, A.; Hu, Y.C.; Zhang, M. Where is the Energy Spent inside My App? Fine Grained Energy Accounting on Smartphones with Eprof. In Proceedings of the 7th ACM European Conference on Computer Systems, Bern, Switzerland, 10–13 April 2012; pp. 29–42. [Google Scholar] [CrossRef]

- Pathak, A.; Hu, Y.C.; Zhang, M. Bootstrapping Energy Debugging on Smartphones: A First Look at Energy Bugs in Mobile Devices. In Proceedings of the 10th ACM Workshop on Hot Topics in Networks, Cambridge, MA, USA, 14–15 November 2011. [Google Scholar] [CrossRef]

- Zhang, L.; Tiwana, B.; Dick, R.P.; Qian, Z.; Mao, Z.M.; Wang, Z.; Yang, L. Accurate online power estimation and automatic battery behavior based power model generation for smartphones. In Proceedings of the 2010 IEEE/ACM/IFIP International Conference on Hardware/Software Codesign and System Synthesis (CODES+ISSS), Scottsdale, AZ, USA, 24–29 October 2010; pp. 105–114. [Google Scholar]

- Balasubramanian, N.; Balasubramanian, A.; Venkataramani, A. Energy Consumption in Mobile Phones: A Measurement Study and Implications for Network Applications. In Proceedings of the 9th ACM SIGCOMM Conference on Internet Measurement, Chicago, IL, USA, 4–6 November 2009; pp. 280–293. [Google Scholar] [CrossRef]

- Pathak, A.; Jindal, A.; Hu, Y.C.; Midkiff, S.P. What is Keeping My Phone Awake? Characterizing and Detecting No-Sleep Energy Bugs in Smartphone Apps. In Proceedings of the 10th International Conference on Mobile Systems, Applications, and Services, Low Wood Bay, Lake District, UK, 25–29 June 2012; pp. 267–280. [Google Scholar] [CrossRef]

- Broekman, B.; Notenboom, E. Testing Embedded Software; Pearson Education: London, UK, 2003. [Google Scholar]

- Shokry, H.; Hinchey, M. Model-Based Verification of Embedded Software. IEEE Comput. 2009, 42, 53–59. [Google Scholar] [CrossRef]

- Marculescu, D.; Marculescu, R.; Pedram, M. Information Theoretic Measures of Energy Consumption at Register Transfer Level. In Proceedings of the International Symposium on Low Power Design, Dana Point, CA, USA, 23–26 April 1995; pp. 81–86. [Google Scholar] [CrossRef]

- Raghunathan, A.; Dey, S.; Jha, N. Register-transfer level estimation techniques for switching activity and power consumption. In Proceedings of the International Conference on Computer Aided Design, San Jose, CA, USA, 10–14 November 1996; pp. 158–165. [Google Scholar] [CrossRef]

- Durrani, Y.; Riesgo, T.; Machado, F. Statistical Power Estimation For Register Transfer Level. In Proceedings of the International Conference Mixed Design of Integrated Circuits and System, MIXDES 2006, Gdynia, Poland, 22–24 June 2006; pp. 522–527. [Google Scholar] [CrossRef]

- Tiwari, V.; Malik, S.; Wolfe, A.; Lee, M.C. Instruction level power analysis and optimization of software. In Proceedings of the 9th International Conference on VLSI Design, Bangalore, India, 3–6 January 1996; pp. 326–328. [Google Scholar] [CrossRef]

- Choi, K.w.; Chatterjee, A. Efficient Instruction-Level Optimization Methodology for Low-Power Embedded Systems. In Proceedings of the 14th International Symposium on Systems Synthesis, Montreal, PQ, Canada, 30 September–3 October 2001; pp. 147–152. [Google Scholar] [CrossRef]

- Steinke, S.; Knauer, M.; Wehmeyer, L.; Marwedel, P. An Accurate and Fine Grain Instruction-Level Energy Model supporting Software Optimizations. In Proceedings of the International Workshop on Power And Timing Modeling, Optimization and Simulation, Yverdon-les-Bains, Switzerland, 26–28 September 2001. [Google Scholar]

- Stattelmann, S.; Ottlik, S.; Viehl, A.; Bringmann, O.; Rosenstiel, W. Combining instruction set simulation and wcet analysis for embedded software performance estimation. In Proceedings of the 7th IEEE International Symposium on Industrial Embedded Systems (SIES’12), Karlsruhe, Germany, 20–22 June 2012; pp. 295–298. [Google Scholar]

- Qu, G.; Kawabe, N.; Usami, K.; Potkonjak, M. Function-level power estimation methodology for microprocessors. In Proceedings of the 37th Annual Design Automation Conference, Los Angeles, CA, USA, 5–9 June 2000; pp. 810–813. [Google Scholar]

- Julien, N.; Laurent, J.; Senn, E.; Martin, E. Power estimation of a C algorithm based on the functional-level power analysis of a digital signal processor. In Proceedings of the International Symposium on High Performance Computing, Kansai Science City, Japan, 15–17 May 2002; pp. 354–360. [Google Scholar]

- Laurent, J.; Senn, E.; Julien, N.; Martin, E. High level energy estimation for DSP systems. In Proceedings of the International Workshop on Power and Timing Modeling, Optimization and Simulation, Yverdon-les-Bains, Switzerland, 26–28 September 2001; pp. 311–316. [Google Scholar]

- Schneider, M.; Blume, H.; Noll, T.G. Power estimation on functional level for programmable processors. Adv. Radio Sci. 2004, 2, 215–219. [Google Scholar] [CrossRef] [Green Version]

- Hönig, T.; Janker, H.; Eibel, C.; Schröder-Preikschat, W.; Mihelic, O.; Kapitza, R. Proactive Energy-Aware Programming with PEEK. In Proceedings of the 2014 International Conference on Timely Results in Operating Systems, USENIX Association, Broomfield, CO, USA, 5 October 2014; pp. 1–14. [Google Scholar]

- Martinez, B.; Monton, M.; Vilajosana, I.; Prades, J.D. The Power of Models: Modeling Power Consumption for IoT Devices. IEEE Sensors J. 2015, 15, 5777–5789. [Google Scholar] [CrossRef] [Green Version]

- Bouguera, T.; Diouris, J.F.; Chaillout, J.J.; Jaouadi, R.; Andrieux, G. Energy Consumption Model for Sensor Nodes Based on LoRa and LoRaWAN. Sensors 2018, 18, 2104. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Benini, L.; Bogliolo, A.; de Micheli, G. A survey of design techniques for system-level dynamic power management. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2000, 8, 299–316. [Google Scholar] [CrossRef]

- Atitallah, Y.B.; Mottin, J.; Hili, N.; Ducroux, T.; Godet-Bar, G. A Power Consumption Estimation Approach for Embedded Software Design Using Trace Analysis. In Proceedings of the 41st Euromicro Conference on Software Engineering and Advanced Applications, Madeira, Portugal, 26–28 August 2015; pp. 61–68. [Google Scholar] [CrossRef] [Green Version]

- Zhu, Z.; Olutunde Oyadiji, S.; He, H. Energy awareness workflow model for wireless sensor nodes. Wirel. Commun. Mob. Comput. 2014, 14, 1583–1600. [Google Scholar] [CrossRef]

- Trabelsi, C.; Ben Atitallah, R.; Meftali, S.; Dekeyser, J.L.; Jemai, A. A Model-Driven Approach for Hybrid Power Estimation in Embedded Systems Design. EURASIP J. Embed. Syst. 2011, 2011. [Google Scholar] [CrossRef] [Green Version]

- Institute of Electrical and Electronics Engineers, Inc. IEEE Standard for Standard SystemC Language Reference Manual; Technical report; Institute of Electrical and Electronics Engineers: Piscataway, NJ, USA, 2012. [Google Scholar] [CrossRef]

- Menghin, M.; Druml, N.; Steger, C.; Weiss, R.; Bock, H.; Haid, J. Development Framework for Model Driven Architecture to Accomplish Power-Aware Embedded Systems. In Proceedings of the 2014 17th Euromicro Conference on Digital System Design, Verona, Italy, 27–29 August 2014; pp. 122–128. [Google Scholar] [CrossRef]

- Senn, E.; Laurent, J.; Juin, E.; Diguet, J.P. Refining power consumption estimations in the component based AADL design flow. In Proceedings of the 2008 Forum on Specification, Verification and Design Languages, Stuttgart, Germany, 23–25 September 2008; pp. 173–178. [Google Scholar]

- Dhouib, S.; Senn, E.; Diguet, J.P.; Laurent, J.; Blouin, D. Model Driven High-Level Power Estimation of Embedded Operating Systems Communication Services. In Proceedings of the 2009 International Conference on Embedded Software and Systems, Hangzhou, China, 25–27 May 2009; pp. 475–481. [Google Scholar] [CrossRef]

- Dhouib, S.; Diguet, J.P.; Senn, E.; Laurent, J. Energy models of real time operating systems on FPGA. In Proceedings of the 4th International Workshop on Operating Systems Platforms for Embedded Real-Time Applications (OSPERT), Prague, Czech Republic, 1 July 2008. [Google Scholar]

- Faugere, M.; Bourbeau, T.; Simone, R.d.; Gerard, S. MARTE: Also an UML Profile for Modeling AADL Applications. In Proceedings of the 12th IEEE International Conference on Engineering Complex Computer Systems (ICECCS 2007), Auckland, New Zealand, 11–14 July 2007; pp. 359–364. [Google Scholar] [CrossRef]

- Abdallah, F.B.; Apvrille, L. Fast evaluation of power consumption of embedded systems using diplodocus. In Proceedings of the 2013 39th Euromicro Conference on Software Engineering and Advanced Applications, Santander, Spain, 4–6 September 2013; pp. 138–144. [Google Scholar]

- Schaumont, P.R. A Practical Introduction to Hardware/Software Codesign; Springer Science & Business Media: Berlin/Heidelberg, Germany, 2012. [Google Scholar]

- Iyenghar, P.; Noyer, A.; Pulvermüller, E. Early model-driven timing validation of IoT-compliant use cases. In Proceedings of the 2017 IEEE 15th International Conference on Industrial Informatics (INDIN), Emden, Germany, 24–26 July 2017; pp. 19–25. [Google Scholar] [CrossRef]

- Iyenghar, P.; Pulvermüller, E. A Model-Driven Workflow for Energy-Aware Scheduling Analysis of IoT-Enabled Use Cases. IEEE Internet Things J. 2018, 5, 4914–4925. [Google Scholar] [CrossRef]

- Hagner, M.; Aniculaesei, A.; Goltz, U. UML-Based Analysis of Power Consumption for Real-Time Embedded Systems. In Proceedings of the 2011 10th International Conference on Trust, Security and Privacy in Computing and Communications, Changsha, China, 16–18 November 2011; pp. 1196–1201. [Google Scholar] [CrossRef]

- Arpinen, T.; Salminen, E.; Hämäläinen, T.D.; Hännikäinen, M. Extension to MARTE profile for modeling dynamic power management of embedded systems. In Proceedings of the M-BED 1st Workshop on Model Based Engineering for Embedded Systems Design, Workhop co-Located with DATE 2010, Dresden, Germany, 12 March 2010; pp. 1–6. [Google Scholar]

- Arpinen, T.; Salminen, E.; Hämäläinen, T.D.; Hännikäinen, M. MARTE Profile Extension for Modeling Dynamic Power Management of Embedded Systems. J. Syst. Archit. 2012, 58, 209–219. [Google Scholar] [CrossRef]

- Eouzan, I.; Garnery, L.; Pinto, M.A.; Delalande, D.; Neves, C.J.; Fabre, F.; Lesobre, J.; Houte, S.; Estonba, A.; Montes, I.; et al. Hygroregulation, a key ability for eusocial insects: Native Western European honeybees as a case study. PLoS ONE 2019, 14, 1–15. [Google Scholar] [CrossRef] [PubMed]

- Espressif Systems. ESP32 Series. Datasheet: V3.9. Available online: https://www.espressif.com/sites/default/files/documentation/esp32_datasheet_en.pdf (accessed on 31 March 2022).

- Bosch Sensortec GmbH. BME280—Data sheet, Version 2.2. Document Number BST-BME280-DS001-22. Available online: https://www.bosch-sensortec.com/media/boschsensortec/downloads/datasheets/bst-bme280-ds002.pdf (accessed on 31 March 2022).

- Lora Alliance. LoRaWAN™ 1.1 Specification. Available online: https://lora-alliance.org/wp-content/uploads/2020/11/lorawantm_specification_-v1.1.pdf (accessed on 1 March 2022).

- The Things Industries B.V. The Things Network. Available online: https://www.thethingsnetwork.org/ (accessed on 1 April 2022).

- RAKwireless Technology Co. RAK811-Module: Datasheet. Available online: https://docs.rakwireless.com/Product-Categories/WisDuo/RAK811-Module/Datasheet/ (accessed on 1 March 2022).

- Semtech Corporation. SX1276/77/78/79 Datasheet Rev. 7 May 2020. Technical Report. Available online: https://www.semtech.com/products/wireless-rf/lora-core/sx1276#datasheets (accessed on 31 March 2022).

- Semtech Corporation. An In-depth Look at LoRaWAN™ Class A Devices. Technical Report. Available online: https://lora-developers.semtech.com/uploads/documents/files/LoRaWAN_Class_A_Devices_In_Depth_Downloadable.pdf (accessed on 31 March 2022).

- The MathWorks, Inc. MATLAB. Available online: https://www.mathworks.com/products/matlab (accessed on 1 March 2022).

- IBM. IBM Engineering Systems Design Rhapsody—Developer. Available online: https://www.ibm.com/products/uml-tools (accessed on 12 January 2022).

- IVI Foundation. Standard Commands for Programmable Instruments (SCPI); Technical report, European SCPI Consortium. 1999. Available online: https://www.ivifoundation.org/docs/scpi-99.pdf (accessed on 31 March 2022).

- IVI Foundation. VISA Specifications. Available online: https://www.ivifoundation.org/specifications/default.aspx (accessed on 12 January 2022).

- Cheij, D. A software architecture for building interchangeable test systems. In Proceedings of the 2001 IEEE Autotestcon Proceedings. IEEE Systems Readiness Technology Conference, Valley Forge, PA, USA, 20–23 August 2001; pp. 16–22. [Google Scholar] [CrossRef]

- Douglass, B.P. Design Patterns for Embedded Systems in C: An Embedded Software Engineering Toolkit; Newnes/Elsevier: Oxford, UK; Burlington, MA, USA, 2011. [Google Scholar]

- Danese, A.; Pravadelli, G.; Zandonà, I. Automatic generation of power state machines through dynamic mining of temporal assertions. In Proceedings of the 2016 Design, Automation Test in Europe Conference Exhibition (DATE), Dresden, Germany, 14–18 March 2016; pp. 606–611. [Google Scholar]

- Huning, L.; Pulvermüller, E. Automatic Code Generation of Safety Mechanisms in Model-Driven Development. Electronics 2021, 10, 3150. [Google Scholar] [CrossRef]

- Selic, B.; Gérard, S. Modeling and Analysis of Real-time and Embedded Systems with UML and MARTE: Developing Cyber-Physical Systems; Morgan Kaufmann: Waltham, MA, USA, 2014. [Google Scholar]

- Valmari, A. The state explosion problem. In Lectures on Petri Nets I: Basic Models: Advances in Petri Nets; Springer: Berlin/Heidelberg, Germany, 1998; pp. 429–528. [Google Scholar] [CrossRef]

- Qoitech AB. Otii Arc. Available online: https://www.qoitech.com/otii/ (accessed on 1 March 2022).

- Object Management Group. OMG System Modeling Language Specification, Version 1.6. OMG Document Number Formal/19-11-01. 2019. Available online: https://www.omg.org/spec/SysML/1.6/ (accessed on 1 April 2022).

- Google LLC. Protocol Buffers Version 3 Language Specification. Available online: https://developers.google.com/protocol-buffers/docs/reference/proto3-spec (accessed on 27 January 2022).

- Google LLC. gRPC: A High-Performance, Open Source Universal RPC Framework. Available online: https://grpc.io/ (accessed on 1 April 2022).

- JSON-RPC Working Group. JSON-RPC 2.0 Specification. Available online: https://www.jsonrpc.org/specification (accessed on 31 March 2022).

- Bray, T. The JavaScript Object Notation (JSON) Data Interchange Format. Technical Report RFC 7159, RFC Editor. 2017. Available online: https://datatracker.ietf.org/doc/html/rfc8259 (accessed on 1 April 2022).

- Qoitech AB. The Otii Server. Available online: https://www.qoitech.com/help/tcpserver/ (accessed on 1 March 2022).

- Buschhoff, M.; Friesel, D.; Spinczyk, O. Energy Models in the Loop. In Proceedings of the 8th International Sumposium on Internet of Ubiquitous and Pervasive Things (IUPT 2018), Porto, Portugal, 8–11 May 2018; Volume 130, pp. 1063–1068. [Google Scholar] [CrossRef]

| Device | State | Electric Current | Execution Time | ||||

|---|---|---|---|---|---|---|---|

| Value | Static | Source | Value | Static | Source | ||

| Espressif ESP32 | Off | 1 µA | Y | O | - | - | - |

| DeepSleep | 10 µA | Y | O | - | - | - | |

| Active | 28 mA | Y | M | - | - | - | |

| Bosch BME280 | Sleep | 13.4 µA | Y | M | - | - | - |

| Forced | 467.2 µA | Y | M | 18.08 ms | Y | M | |

| RAK Wireless RAK811 | Sleep | 13.4 µA | Y | M | - | - | - |

| Idle | 6.14 mA | Y | M | - | - | - | |

| Join | 19.9 mA | Y | M | - | - | - | |

| RX | 22.2 mA | Y | M | 1300 ms | Y | E | |

| TX | 63.9 mA | Y | M | D | N | C | |

| Parameter | Configured Value |

|---|---|

| Bandwidth | 125 kHz |

| Spreading Factor | 12 |

| Preamble Length | 23 symbols |

| Header Mode | Explicit (0) |

| Low Data Rate Optimization | Off (0) |

| CRC Check | Off (0) |

| Coding Rate | 4/5 (1) |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Schaarschmidt, M.; Uelschen, M.; Pulvermüller, E. Hunting Energy Bugs in Embedded Systems: A Software-Model-In-The-Loop Approach. Electronics 2022, 11, 1937. https://doi.org/10.3390/electronics11131937

Schaarschmidt M, Uelschen M, Pulvermüller E. Hunting Energy Bugs in Embedded Systems: A Software-Model-In-The-Loop Approach. Electronics. 2022; 11(13):1937. https://doi.org/10.3390/electronics11131937

Chicago/Turabian StyleSchaarschmidt, Marco, Michael Uelschen, and Elke Pulvermüller. 2022. "Hunting Energy Bugs in Embedded Systems: A Software-Model-In-The-Loop Approach" Electronics 11, no. 13: 1937. https://doi.org/10.3390/electronics11131937