A 5 V-to-32 V Input PVT-Robust Charge-Pump Circuit with Adjustable Output in a 0.18 μm BCD Process

Abstract

:1. Introduction

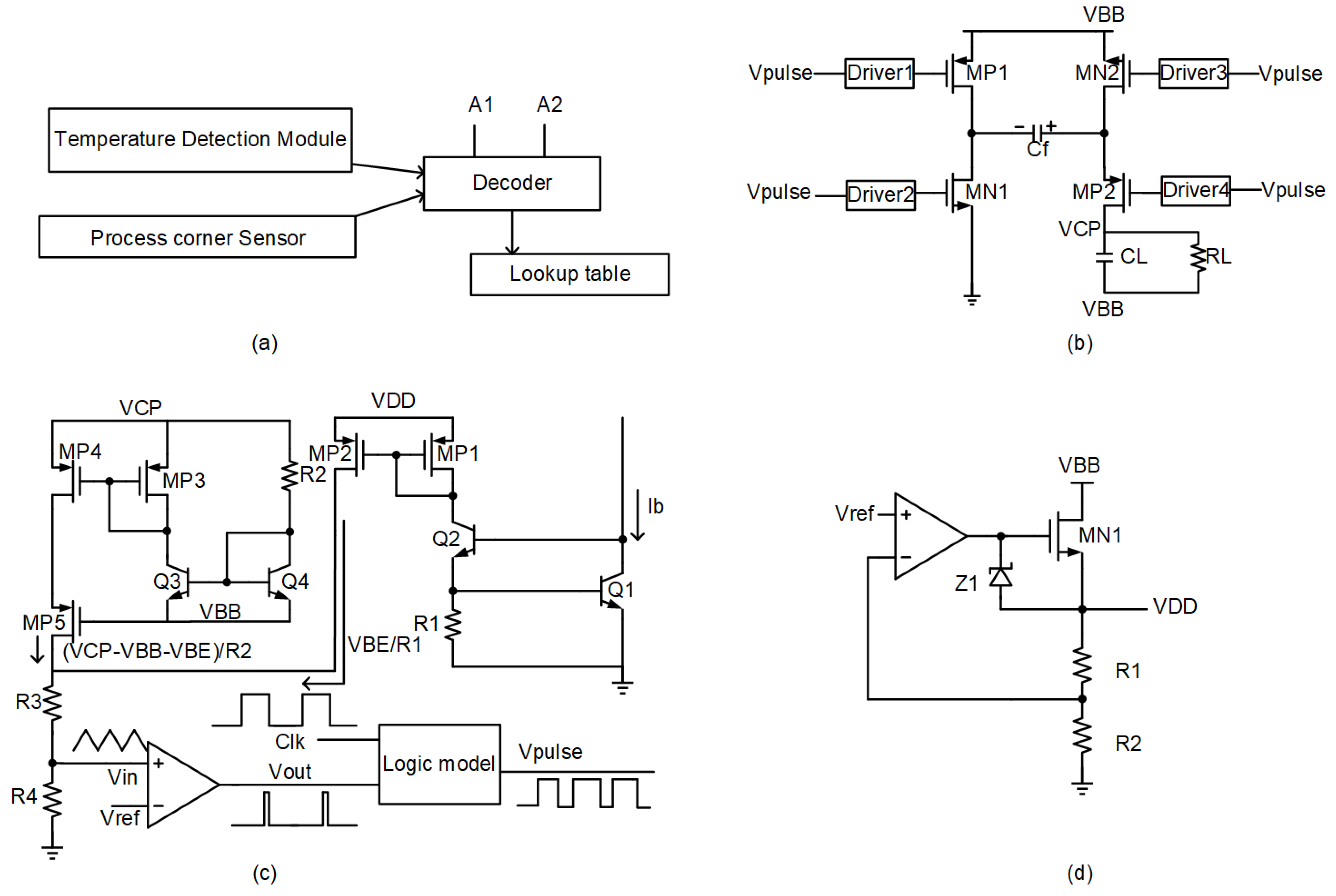

2. System Design

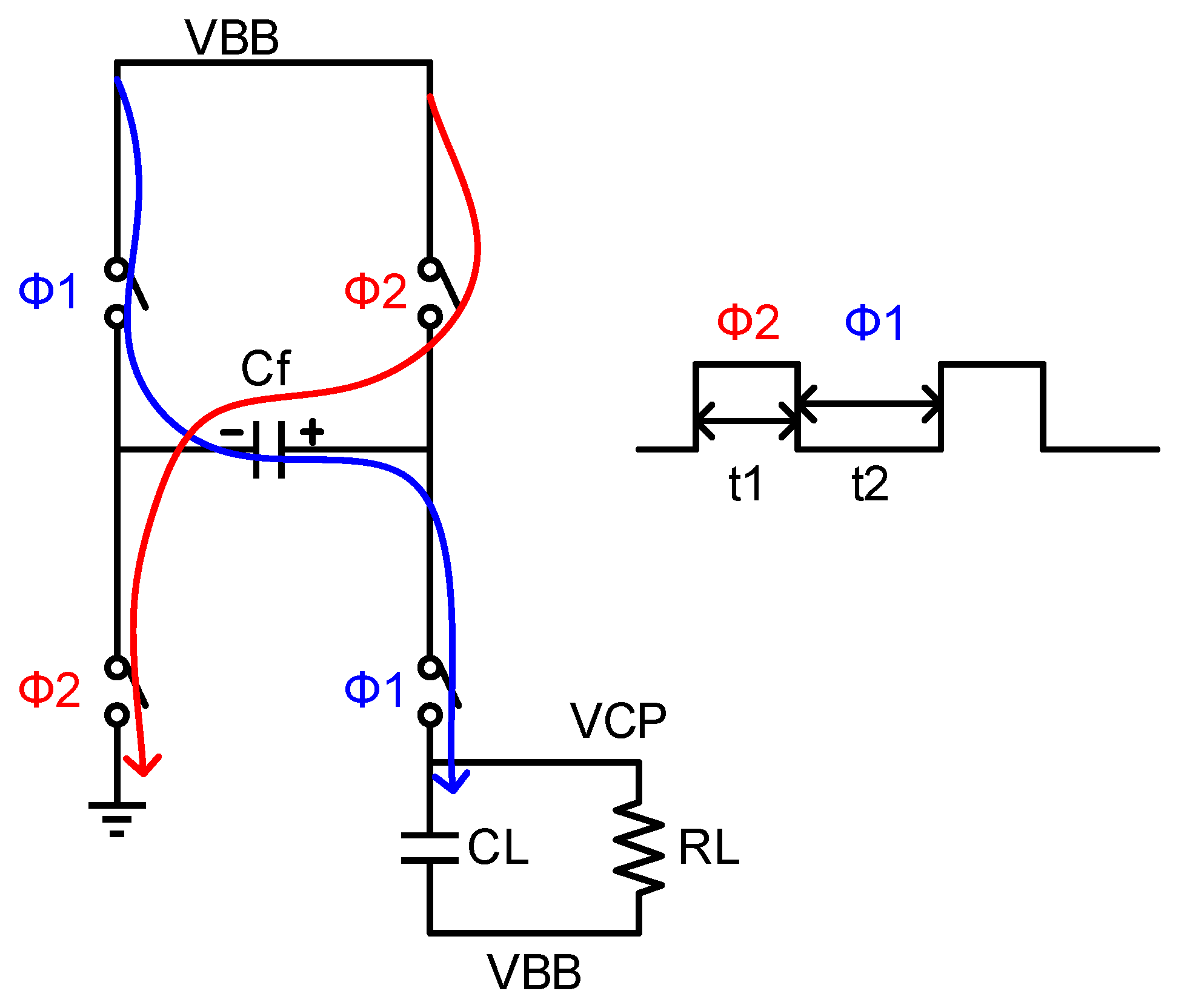

3. Critical Circuit Design

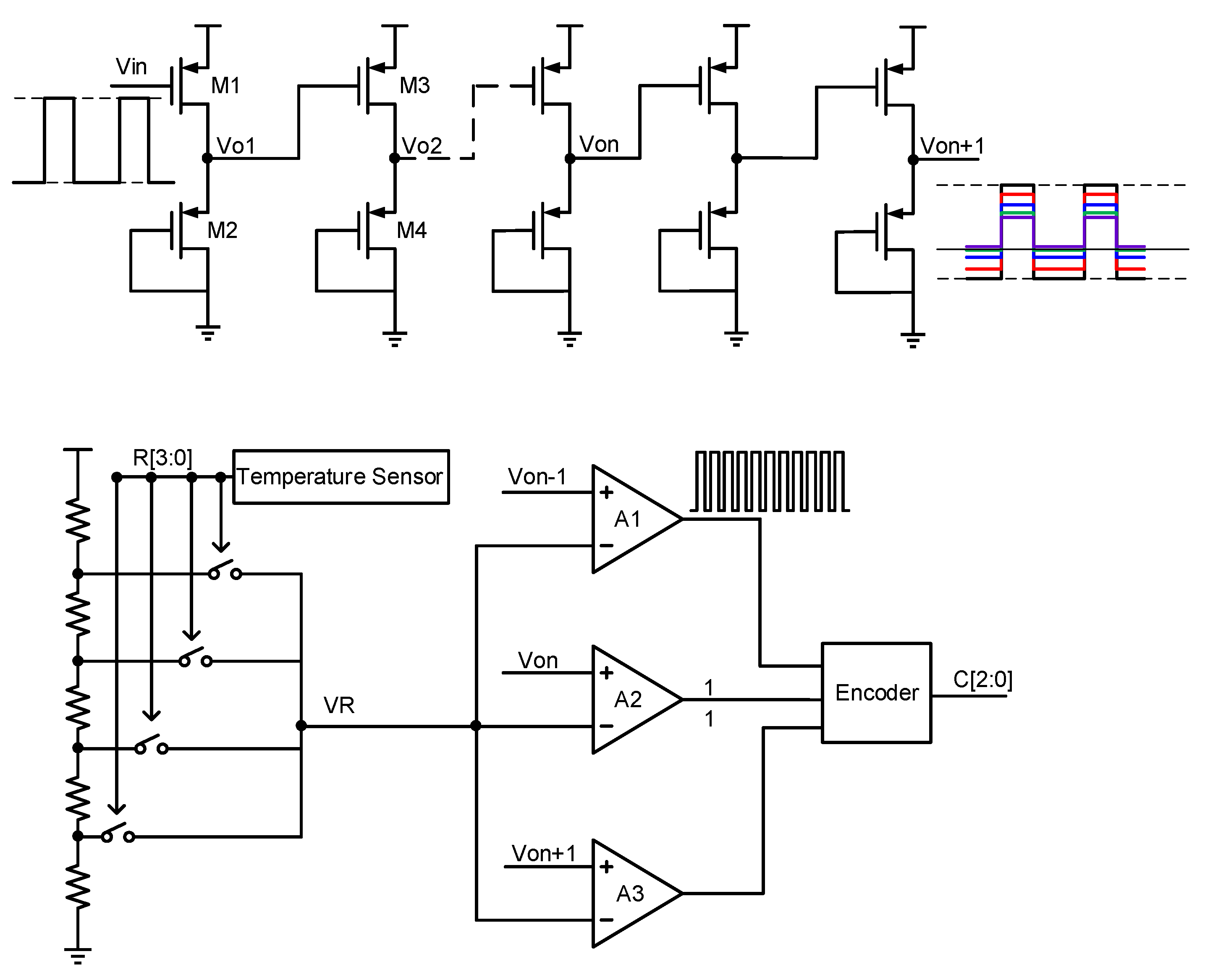

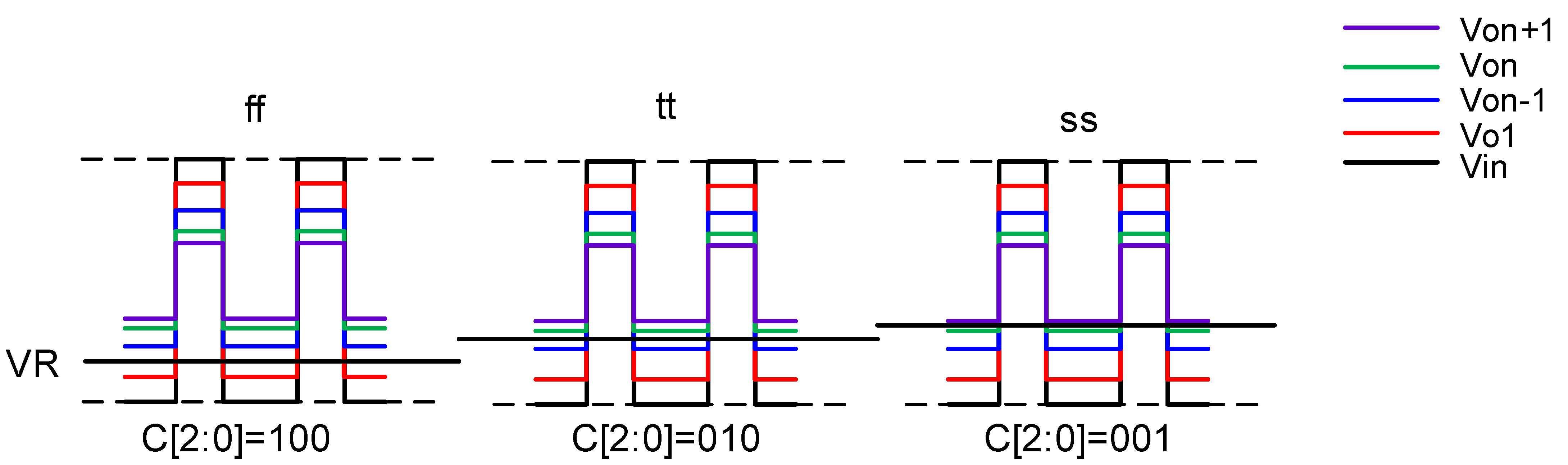

3.1. PWM Modulation Module

3.2. Process Corner Detection Module

4. Simulation and Experimental Results

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Singh, A.; Singh, T.; Pindoo, I.; Choudhary, A.; Kumar, R.; Bhullar, P. Transient response and dynamic power dissipation comparison of various Dickson charge pump configurations based on charge transfer switches. In Proceedings of the 2015 6th International Conference on Computing, Communication and Networking Technologies (ICCCNT), Dallas-Fortworth, TX, USA, 13–15 July 2015; pp. 1–6. [Google Scholar] [CrossRef]

- Chen, J.J.; Zheng, C.H.; Hwang, Y.S. A new single-inductor triple-output buck converter using CMOS technology. In Proceedings of the 2010 International Power Electronics Conference—ECCE ASIA, Sapporo, Japan, 21—24 June 2010; pp. 82–85. [Google Scholar] [CrossRef]

- Matsumoto, H.; Neba, Y.; Asahara, H. Variable-Form Carrier-Based PWM for Boost-Voltage Motor Driver with a Charge-Pump Circuit. IEEE Trans. Ind. Electron. 2015, 62, 4728–4738. [Google Scholar] [CrossRef]

- Wei, C.L.; Wu, C.H.; Wu, L.Y.; Shih, M.H. An Integrated Step-Up/Step-Down DC–DC Converter Implemented with Switched-Capacitor Circuits. IEEE Trans. Circuits Syst. II Express Briefs 2010, 57, 813–817. [Google Scholar] [CrossRef]

- Chen, M.; Wu, X.; Zhao, M. Novel high efficiency low ripple charge pump using variable frequency modulation. In Proceedings of the 2010 International Conference on Microelectronics, Cairo, Egypt, 19–22 December 2010; pp. 228–231. [Google Scholar] [CrossRef]

- Tan, Y.; Ishikuro, H. A Discrete-Time Model for Frequency Modulated Charge Pumps with Synchronized Controller. In Proceedings of the 2020 IEEE 63rd International Midwest Symposium on Circuits and Systems (MWSCAS), Springfield, MA, USA, 9–12 August 2020; pp. 929–932. [Google Scholar] [CrossRef]

- Huang, H.W.; Chen, K.H.; Kuo, S.Y. Dithering Skip Modulation, Width and Dead Time Controllers in Highly Efficient DC-DC Converters for System-On-Chip Applications. IEEE J. Solid-State Circuits 2007, 42, 2451–2465. [Google Scholar] [CrossRef]

- Wolpert, D.; Ampadu, P. A Low-Power Safety Mode for Variation Tolerant Systems-on-Chip. In Proceedings of the 2008 IEEE International Symposium on Defect and Fault Tolerance of VLSI Systems, Cambridge, MA, USA, 1–3 October 2008; pp. 33–41. [Google Scholar] [CrossRef]

- Chang, M.H.; Lin, S.Y.; Wu, P.C.; Zakoretska, O.; Chuang, C.T.; Chen, K.N.; Wang, C.C.; Chen, K.H.; Chiu, C.T.; Tong, H.M.; et al. Near-/Sub-Vth process, voltage, and temperature (PVT) sensors with dynamic voltage selection. In Proceedings of the 2013 IEEE International Symposium on Circuits and Systems (ISCAS), Beijing, China, 19–23 May 2013; pp. 133–136. [Google Scholar] [CrossRef]

- Huang, H.; Xu, H.; Elies, B.; Chiu, Y. A Non-Interleaved 12-b 330-MS/s Pipelined-SAR ADC with PVT-Stabilized Dynamic Amplifier Achieving Sub-1-dB SNDR Variation. IEEE J. Solid-State Circuits 2017, 52, 3235–3247. [Google Scholar] [CrossRef]

- Zhang, J.; Ren, X.; Liu, S.; Chan, C.H.; Zhu, Z. An 11-bit 100-MS/s Pipelined-SAR ADC Reusing PVT-Stabilized Dynamic Comparator in 65-nm CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 1174–1178. [Google Scholar] [CrossRef]

- Chen, C.L.; Tseng, H.Y.; Kuo, R.C.; Wang, C.C. A slew rate self-adjusting 2 × VDD output buffer with PVT compensation. In Proceedings of the Technical Program of 2012 VLSI Design, Automation and Test, Hsinchu, Taiwan, 23–25 April 2012; pp. 1–4. [Google Scholar] [CrossRef]

- Giron-Allende, A.; Avendaño, V.; Martinez-Guerrero, E. A design methodology using flip-flops controlled by PVT variation detection. In Proceedings of the 2015 IEEE 6th Latin American Symposium on Circuits & Systems (LASCAS), Montevideo, Uruguay, 24–27 February 2015; pp. 1–4. [Google Scholar] [CrossRef]

- Kim, K.K.; Kim, Y.B. A Novel Adaptive Design Methodology for Minimum Leakage Power Considering PVT Variations on Nanoscale VLSI Systems. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2009, 17, 517–528. [Google Scholar] [CrossRef]

- Wang, C.C.; Chao, K.Y.; Sampath, S.; Suresh, P. Anti-PVT-Variation Low-Power Time-to-Digital Converter Design Using 90-nm CMOS Process. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2020, 28, 2069–2073. [Google Scholar] [CrossRef]

- Biswas, A.; Sinangil, Y.; Chandrakasan, A.P. A 28 nm FDSOI integrated reconfigurable switched-capacitor based step-up DC-DC converter with 88% peak efficiency. In Proceedings of the ESSCIRC 2014—40th European Solid State Circuits Conference (ESSCIRC), Venice Lido, Italy, 22–26 September 2014; pp. 271–274. [Google Scholar] [CrossRef]

- Hua, Z.; Lee, H. A Reconfigurable Dual-Output Switched-Capacitor DC-DC Regulator with Sub-Harmonic Adaptive-on-Time Control for Low-Power Applications. IEEE J. -Solid-State Circuits 2015, 50, 724–736. [Google Scholar] [CrossRef]

- Teh, C.K.; Suzuki, A. 12.3 A 2-output step-up/step-down switched-capacitor DC-DC converter with 95.8% peak efficiency and 0.85-to-3.6 V input voltage range. In Proceedings of the 2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016; pp. 222–223. [Google Scholar] [CrossRef]

- Wei, C.L.; Shih, M.H. Design of a Switched-Capacitor DC-DC Converter with a Wide Input Voltage Range. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 1648–1656. [Google Scholar] [CrossRef]

- Karadi, R.; Pique, G.V. 4.8 3-phase 6/1 switched-capacitor DC-DC boost converter providing 16 V at 7 mA and 70.3% efficiency in 1.1 mm3. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 92–93. [Google Scholar] [CrossRef]

- Yim, T.; Lee, C.; Yoon, H. A High Speed Modified Dickson Charge Pump. In Proceedings of the 2021 IEEE International Symposium on Circuits and Systems (ISCAS), Daegu, Korea, 22–28 May 2021; pp. 1–5. [Google Scholar] [CrossRef]

- Abdi, A.; Kim, H.S.; Cha, H.K. A High-Voltage Generation Charge-Pump IC Using Input Voltage Modulated Regulation for Neural Implant Devices. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 342–346. [Google Scholar] [CrossRef]

- Zhao, J.; Yao, L.; Xue, R.F.; Li, P.; Je, M.; Xu, Y.P. An Integrated Wireless Power Management and Data Telemetry IC for High-Compliance-Voltage Electrical Stimulation Applications. IEEE Trans. Biomed. Circuits Syst. 2016, 10, 113–124. [Google Scholar] [CrossRef] [PubMed]

- Shen, B.; Bose, S.; Johnston, M.L. A 1.2 V–20 V Closed-Loop Charge Pump for High Dynamic Range Photodetector Array Biasing. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 327–331. [Google Scholar] [CrossRef]

- Xie, Y.; Huang, S.; Xue, Y.; Duan, Q. A low-voltage with high pumping efficiency charge pump for flash memory. J. Phys. Conf. Ser. 2020, 1550, 052027. [Google Scholar] [CrossRef]

- Patil, A.; Bhat, S.; Santra, A. An Accurate, Power and Area Efficient 13.33x Charge Pump with Wide-Range Programmability for Biomedical Sensors. In Proceedings of the 2020 33rd International Conference on VLSI Design and 2020 19th International Conference on Embedded Systems (VLSID), Bangalore, India, 4–8 January 2020; pp. 219–224. [Google Scholar] [CrossRef]

- Li, X.; Li, R.; Ju, C.; Hou, B.; Zhang, R. A Regulated Temperature-Insensitive High-Voltage Charge Pump in Standard CMOS Process for Micromachined Gyroscopes. Sensors 2019, 19, 4149. [Google Scholar] [CrossRef] [Green Version]

| R[3:0] | 0000 | 1000 | 1100 | 1110 | 1111 |

|---|---|---|---|---|---|

| ss | 135–110 °C | 105–75 °C | 70–40 °C | 35–−5 °C | −10–−40 °C |

| tt | 135–110 °C | 105–80 °C | 75–45 °C | 40–−5 °C | 0–−40 °C |

| ff | 135–105 °C | 100–75 °C | 70–40 °C | 35–−5 °C | 0–−40 °C |

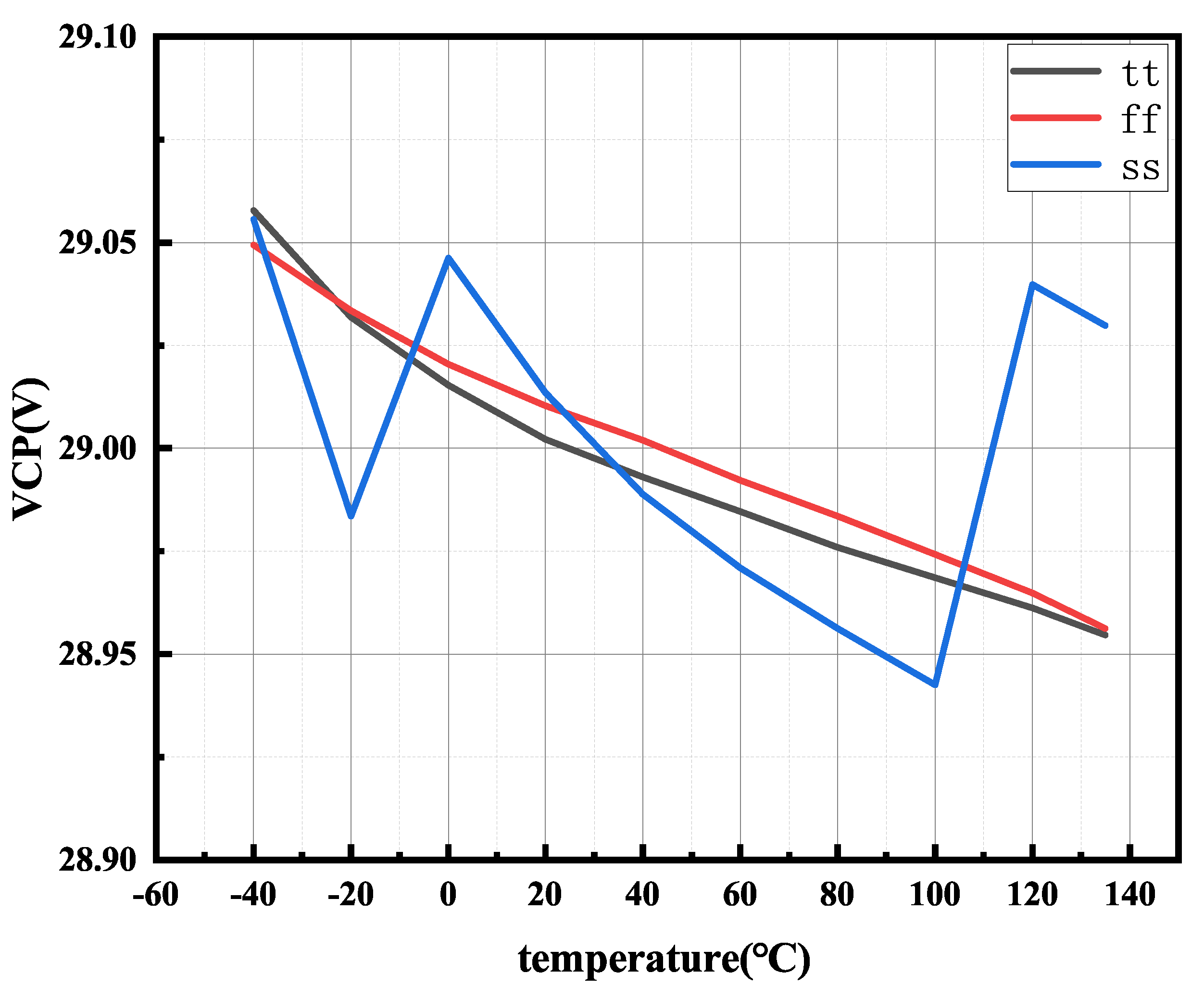

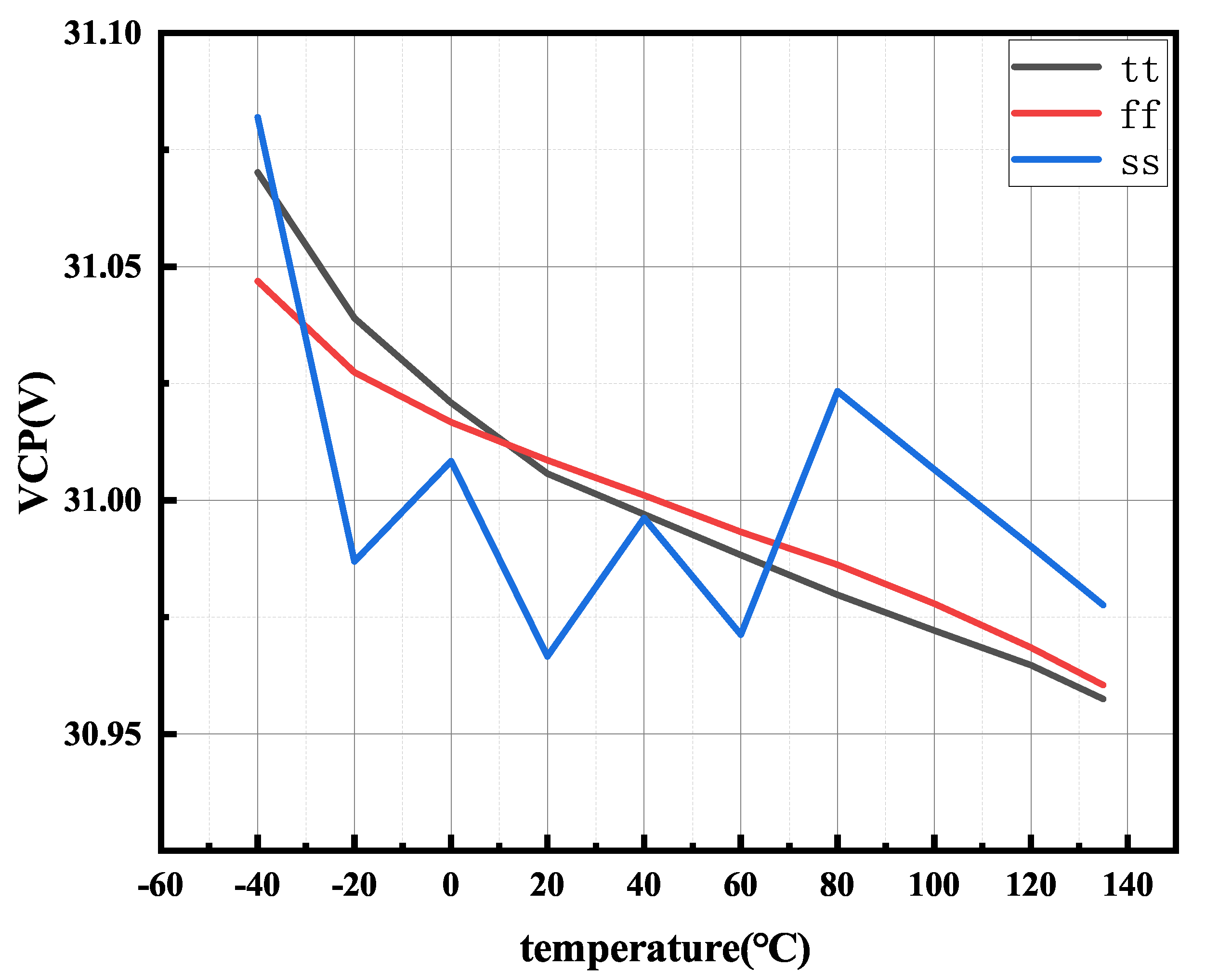

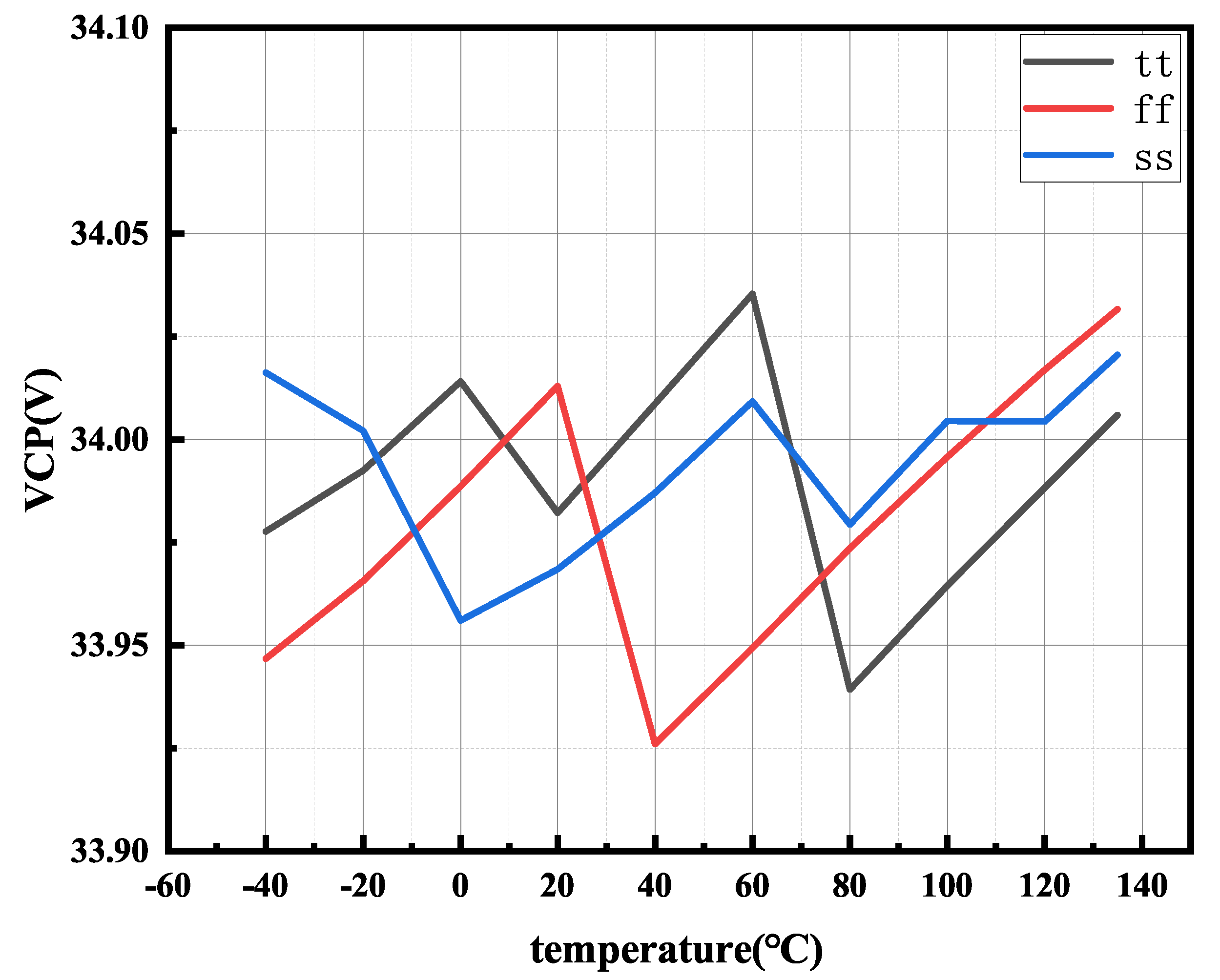

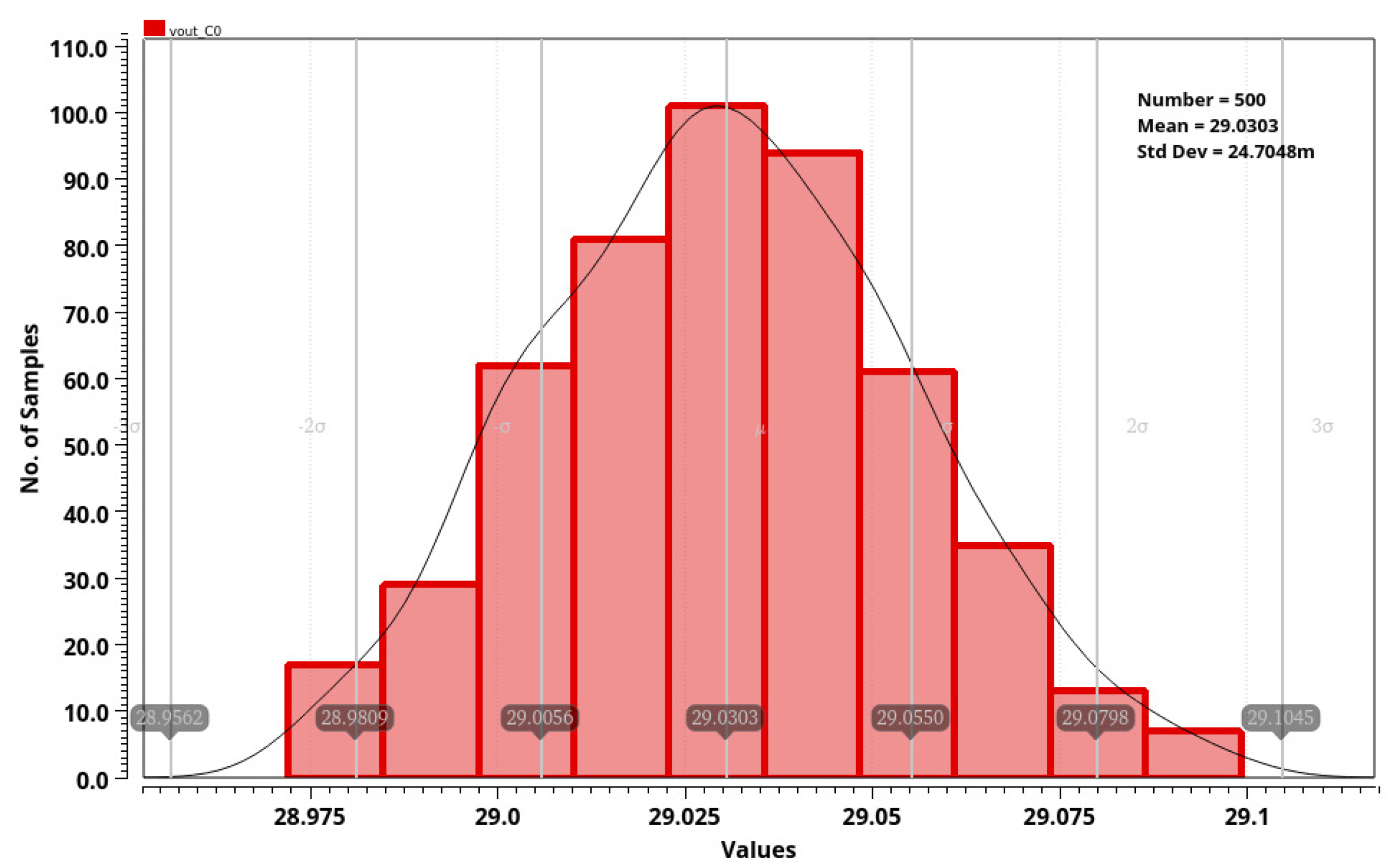

| V (VCP-VBB) | ss | tt | ff |

|---|---|---|---|

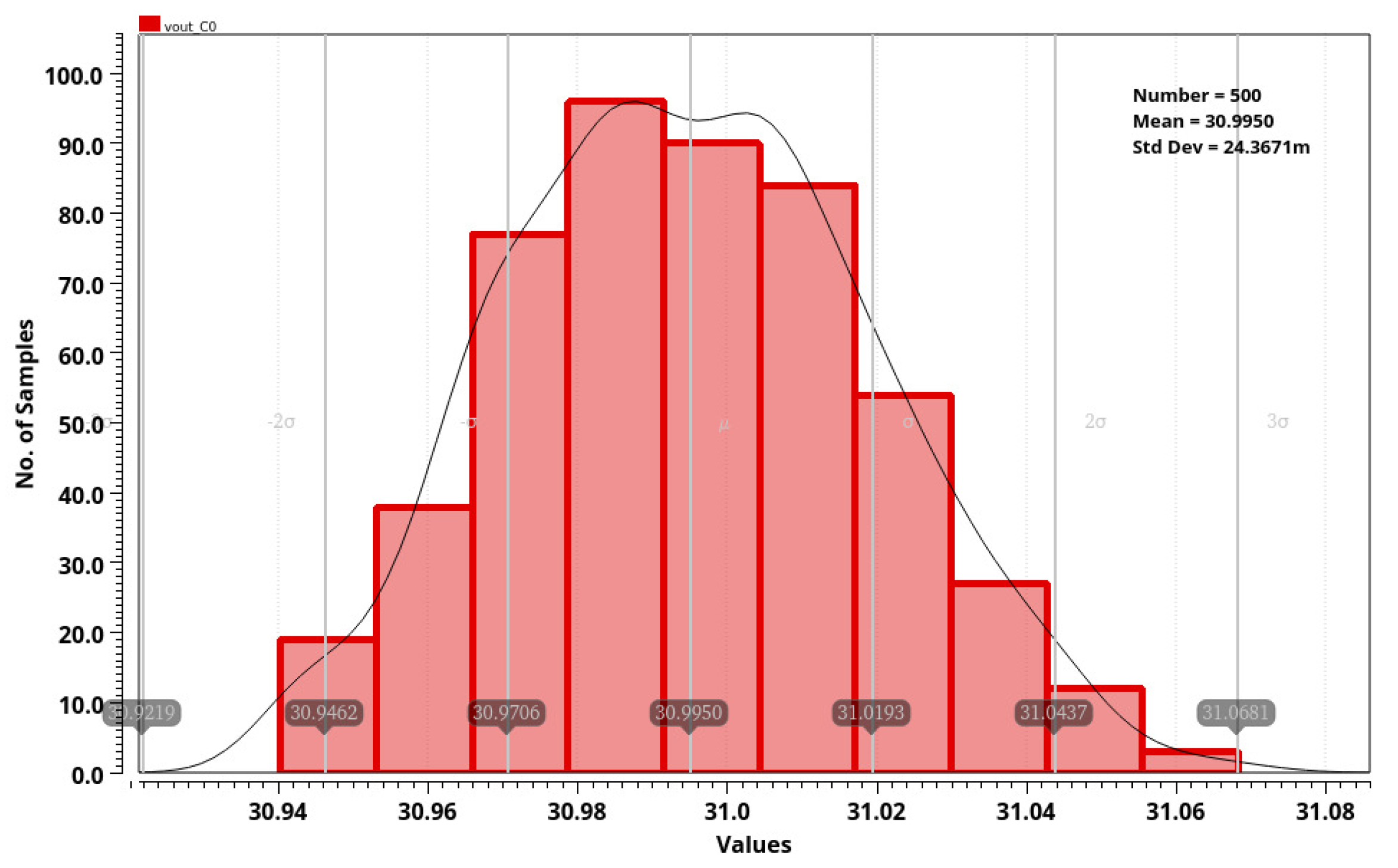

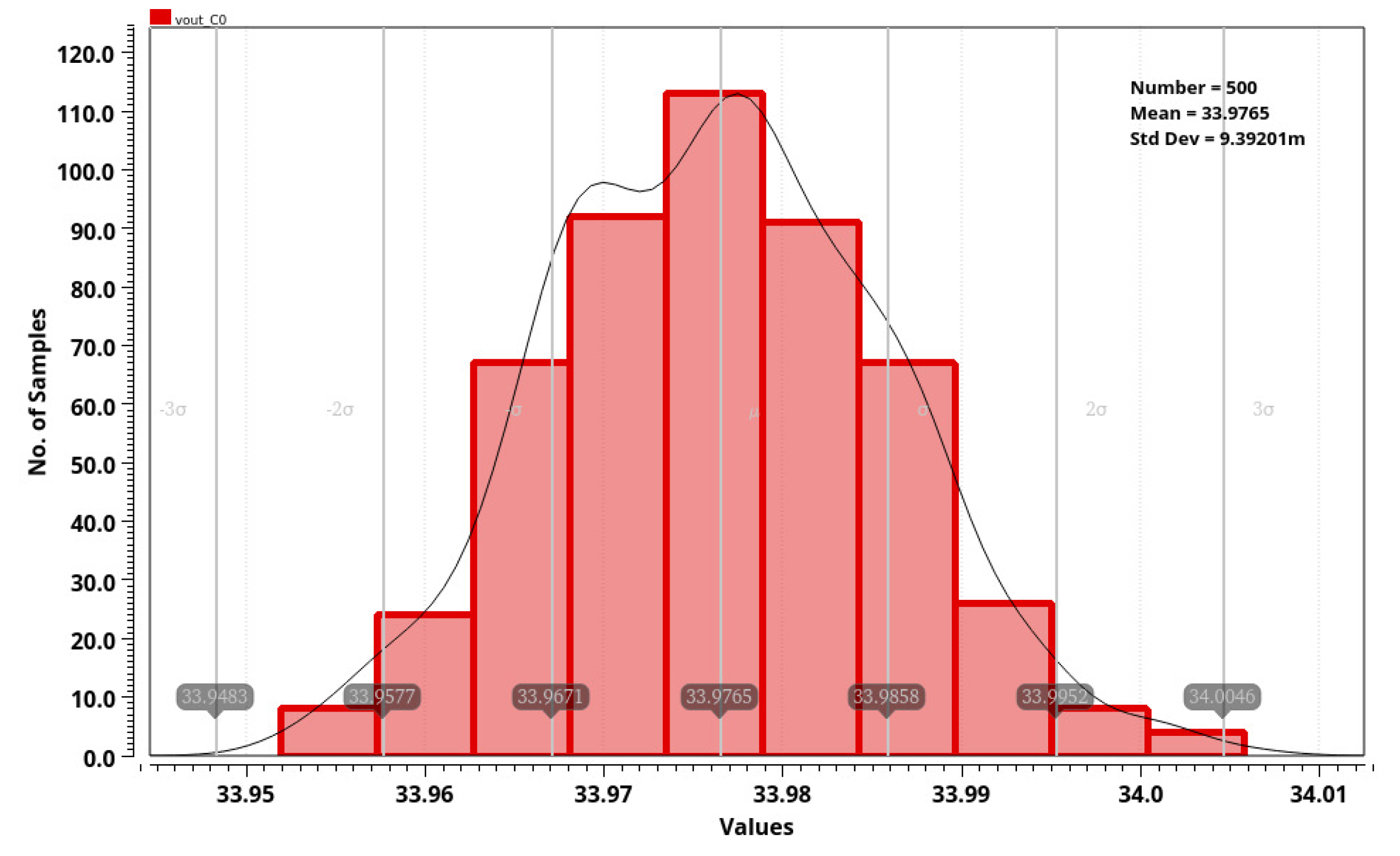

| 5 V | ±0.197% | ±0.199% | ±0.170% |

| 7 V | ±0.265% | ±0.226% | ±0.151% |

| 10 V | ±0.129% | ±0.179% | ±0.218% |

| Reference | [21] | [22] | [23] | [20] | [24] | [25] | [26] | [27] | This Work |

|---|---|---|---|---|---|---|---|---|---|

| Input Voltage (V) | 1.2 | 2.8 | 4.6 | 3.3 | 3.3 | 1.2 | 1.8 | 5 | 5–32 |

| Vout Voltage (V) | 7.08 | 12.8 | 20 | 16 | 5/19.6 | 6.129 | 7.5–24 | 13–16.95 | 10–42 |

| Output ripple (Vripple/Vout) 1 | 0.2% | <1% @max.load | <0.6% @max.load | <1% @max.load | - | 0.23% | <1% | <1.1% | <0.3% @max.load |

| Compensation for PVT Variations | no | no | no | no | no | no | no | no | yes |

| Maximum loading current (mA) | 0.1 | 0.01–1 | 0.6 | 0.1–7 | - | 0.3 | 0.1 | - | 30 |

| Frequency | 100 M | 10 K | 3 K–1 M | 6.67 M | 10/50 M | 100 M | 20 M | 10 K | 200 K |

| Flying capacitance | - | 1 u | 1 u | 1 u | - | - | - | - | 100 n |

| Load capacitance | - | 1 u | 1 u | 100 n | 1 n | - | 1 n | - | 1 u |

| No. of Stages | 5 | 4 | 4 | 16 | 1/11 | 5 | 15 | 2 | Single |

| Power dissipation (mW) | - | - | - | - | 3.56 | - | - | - | 4.753 |

| Area (mm) | - | 0.6 | - | 1.65 | 0.063 | - | 0.038 | 2.53 | 0.308 |

| Technology | 0.18 m | 0.18 m | 0.18 m | 0.16 m | 0.18 m | 0.18 m | 0.18 mBCD | 0.18 m | 0.18 mBCD |

| Result | Simulated | Measured | Measured | Measured | Measured | Simulated | Measured | Measured | Simulated |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ma, X.; Wang, L.; Yu, J. A 5 V-to-32 V Input PVT-Robust Charge-Pump Circuit with Adjustable Output in a 0.18 μm BCD Process. Electronics 2022, 11, 2828. https://doi.org/10.3390/electronics11182828

Ma X, Wang L, Yu J. A 5 V-to-32 V Input PVT-Robust Charge-Pump Circuit with Adjustable Output in a 0.18 μm BCD Process. Electronics. 2022; 11(18):2828. https://doi.org/10.3390/electronics11182828

Chicago/Turabian StyleMa, Xinyi, Liangkun Wang, and Jiaqing Yu. 2022. "A 5 V-to-32 V Input PVT-Robust Charge-Pump Circuit with Adjustable Output in a 0.18 μm BCD Process" Electronics 11, no. 18: 2828. https://doi.org/10.3390/electronics11182828

APA StyleMa, X., Wang, L., & Yu, J. (2022). A 5 V-to-32 V Input PVT-Robust Charge-Pump Circuit with Adjustable Output in a 0.18 μm BCD Process. Electronics, 11(18), 2828. https://doi.org/10.3390/electronics11182828