A Novel Heterogeneous Parallel System Architecture Based EtherCAT Hard Real-Time Master in High Performance Control System

Abstract

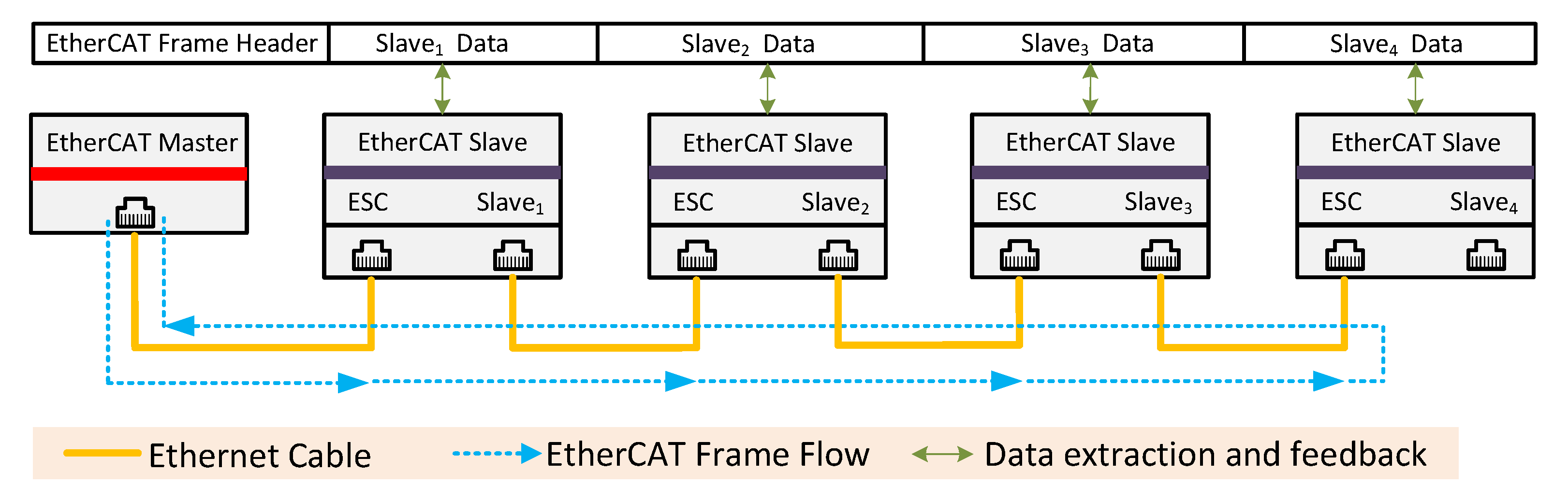

:1. Introduction

- We use hardware description language (HDL) to create a novel EMS. This EMS features data parallelism and conflict-free processing. In this way, the HPSA-based master can operate more efficiently and stably to achieve a lower cycle time and reduce the frame loss rate.

- We build an EMS-based EOS. This EOS supplies a stable and hard real-time operating environment for the HPSA-based master to mitigate the process scheduling latency and achieve high-speed operation of complex control algorithms.

- We place this HPSA-based master into EtherCAT systems. Experimental results demonstrate that the HPSA-based master can operate well. Compared with traditional EtherCAT masters, the performance of clock synchronization and cycle time have significantly improved.

2. Related Work

2.1. Cycle Time Optimization

2.2. Clock Synchronization Improvement

3. Composition of EMS

3.1. Process Part

3.1.1. Main Module

3.1.2. Operation Module

3.2. Function Part

3.2.1. Pretreatment Module

3.2.2. Configuration Module

4. Creation of EOS

4.1. The Hard Real-Time Characteristic Acquisition of EOS

4.2. Design Flow of Embedded EOS

5. Framework of HPSA-Based Hard Real-Time Master

5.1. PS Part

5.2. PL Part

6. Experimental Results

6.1. Experimental Setup

6.2. Experiment of Cycle Time

6.3. Experiment of Clock Synchronization

7. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Chuang, W.L.; Yeh, M.H.; Yeh, Y.L. Develop Real-Time Robot Control Architecture Using Robot Operating System and EtherCAT. Actuators 2021, 10, 141. [Google Scholar] [CrossRef]

- An, C.J.; Yi, H.C.; Kim, H.W.; Park, S.M.; Choi, J.Y. Preventing Data Loss in Linux-Based EtherCAT Master. Int. J. Future Comput. Commun. 2015, 4, 246. [Google Scholar] [CrossRef]

- Zhou, N.; Li, D. Cyber-Physical Codesign of Field-Level Reconfigurations in Networked Motion Controllers. IEEE/ASME Trans. Mechatron. 2020, 26, 2092–2103. [Google Scholar] [CrossRef]

- Park, S.M.; Kim, H.; Kim, H.W.; Cho, C.N.; Choi, J.Y. Synchronization improvement of distributed clocks in EtherCAT networks. IEEE Commun. Lett. 2017, 21, 1277–1280. [Google Scholar] [CrossRef]

- Knezic, M.; Dokic, B.; Ivanovic, Z. Increasing EtherCAT performance using frame size optimization algorithm. In Proceedings of the ETFA2011, Toulouse, France, 5–9 September 2011; pp. 1–4. [Google Scholar]

- Delgado, R.; Choi, B.W. Network-oriented real-time embedded system considering synchronous joint space motion for an omnidirectional mobile robot. Electronics 2019, 8, 317. [Google Scholar] [CrossRef]

- Maruyama, T.; Yamada, T. Communication architecture of EtherCAT master for high-speed and IT-enabled real-time systems. In Proceedings of the 2015 IEEE 20th Conference on Emerging Technologies & Factory Automation (ETFA), Luxembourg, 8–11 September 2015; pp. 1–8. [Google Scholar]

- Song, I.S.; Jeon, Y.H.; Kim, J.H.; Seo, S.H.; Kwon, K.H.; Chun, J.H.; Jeon, J.W. Implementation and analysis of the embedded master for EtherCAT. In Proceedings of the ICCAS 2010, Gyeonggi-do, Korea, 27–30 October 2010; pp. 2418–2422. [Google Scholar]

- Maruyama, T.; Yamada, T. Spatial-temporal communication redundancy for high performance EtherCAT master. In Proceedings of the 2017 22nd IEEE International Conference on Emerging Technologies and Factory Automation (ETFA), Limassol, Cyprus, 12–15 September 2017; pp. 1–6. [Google Scholar]

- Li, B.; Lin, H.; Sun, S.; Zheng, L. A synchronization method for local applications of EtherCAT master-slave in Open CNC system. In Proceedings of the 2018 IEEE International Conference on Information and Automation (ICIA), Wuyishan, China, 11–13 August 2018; pp. 527–533. [Google Scholar]

- Chen, X.; Li, D.; Wang, S.; Tang, H.; Liu, C. Frequency-tracking clock servo for time synchronization in networked motion control systems. IEEE Access 2017, 5, 11606–11614. [Google Scholar] [CrossRef]

- Park, S.M.; Kim, H.W.; Kim, H.J.; Choi, J.Y. Accuracy improvement of master-slave synchronization in EtherCAT networks. IEEE Access 2020, 8, 58620–58628. [Google Scholar] [CrossRef]

- Ganz, D.; Leschke, S.; Doran, H.D. Improving EtherCAT master-slave synchronization precision using PTCP embedded in EtherCAT frames: A proof-of-concept. In Proceedings of the 2015 IEEE World Conference on Factory Communication Systems (WFCS), Palma de Mallorca, Spain, 27–29 May 2015; pp. 1–7. [Google Scholar]

- Prytz, G.; Skaalvik, J. Redundant and synchronized EtherCAT network. In Proceedings of the International Symposium on Industrial Embedded System (SIES), Trento, Italy, 7–9 July 2010; pp. 201–204. [Google Scholar]

- Rehnman, M.; Gentzell, T. Synchronization in a force measurement system using EtherCAT. In Proceedings of the 2008 IEEE International Conference on Emerging Technologies and Factory Automation, Hamburg, Germany, 15–18 September 2008; pp. 1023–1030. [Google Scholar]

- Maruyama, T.; Yamada, T. Hardware acceleration architecture for EtherCAT master controller. In Proceedings of the 2012 9th IEEE International Workshop on Factory Communication Systems, Lemgo, Germany, 21–24 May 2012; pp. 223–232. [Google Scholar]

- Li, L.; Cong, P.; Cao, K.; Zhou, J.; Wei, T.; Chen, M.; Hu, S.; Hu, X.S. Game theoretic feedback control for reliability enhancement of EtherCAT-based networked systems. IEEE Trans. Comput.-Aided Des. Integr. Syst. 2018, 38, 1599–1610. [Google Scholar] [CrossRef]

- Lee, Y.; Lee, W.; Choi, B.; Park, G.; Park, Y. Reliable software architecture design with EtherCAT for a rescue robot. In Proceedings of the 2016 IEEE International Symposium on Robotics and Intelligent Sensors (IRIS), Tokyo, Japan, 17–20 December 2016; pp. 34–39. [Google Scholar]

- Prytz, G. A performance analysis of EtherCAT and PROFINET IRT. In Proceedings of the 2008 IEEE International Conference on Emerging Technologies and Factory Automation, Hamburg, Germany, 15–18 September 2008; pp. 408–415. [Google Scholar]

- Zhang, G.; Ni, F.; Li, Z.; Liu, H. A Control System Design for 7-DoF Light-weight Robot based on EtherCAT Bus. In Proceedings of the 2018 IEEE International Conference on Mechatronics and Automation (ICMA), Changchun, China, 5–8 August 2018; pp. 2169–2174. [Google Scholar]

- Akpinar, K.O.; Ozcelik, I. Methodology to Determine the Device-Level Periodicity for Anomaly Detection in EtherCAT-Based Industrial Control Network. IEEE Trans. Netw. Serv. Manag. 2020, 18, 2308–2319. [Google Scholar] [CrossRef]

- Shen, H.; Li, P.; Luo, X. Synchronous multi-axis motion control based on modified EtherCAT distributed clock. In Proceedings of the 2020 Chinese Automation Congress (CAC), Shanghai, China, 6–8 November 2020; pp. 3674–3678. [Google Scholar]

- Orfanus, D.; Indergaard, R.; Prytz, G.; Wien, T. EtherCAT-based platform for distributed control in high-performance industrial applications. In Proceedings of the 2013 IEEE 18th Conference on Emerging Technologies & Factory Automation (ETFA), Cagliari, Italy, 10–13 September 2013; pp. 1–8. [Google Scholar]

- Cena, G.; Scanzio, S.; Valenzano, A.; Zunino, C. Performance evaluation of the EtherCAT distributed clock algorithm. In Proceedings of the 2010 IEEE International Symposium on Industrial Electronics, Bari, Italy, 4–7 July 2010; pp. 3398–3403. [Google Scholar]

- Paprocki, M.; Erwiński, K. Synchronization of Electrical Drives via EtherCAT Fieldbus Communication Modules. Energies 2022, 15, 604. [Google Scholar] [CrossRef]

- Chen, X.; Li, D.; Wan, J.; Zhou, N. A clock synchronization method for EtherCAT master. Microprocess. Microsyst. 2016, 46, 211–218. [Google Scholar] [CrossRef]

- Adam, G.K. Real-Time Performance and Response Latency Measurements of Linux Kernels on Single-Board Computers. Computers 2021, 10, 64. [Google Scholar] [CrossRef]

- Duca, L.C.; Duca, A. Achieving Hard Real-Time Networking on PREEMPT_RT Linux with RTnet. In Proceedings of the 2020 International Symposium on Fundamentals of Electrical Engineering (ISFEE), Bucharest, Romania, 5–7 November 2020; pp. 1–4. [Google Scholar]

| Performance | Real-Time Ethernet Technologies | ||||

|---|---|---|---|---|---|

| Powerlink | PROFINET | SERCOS III | Ethernet/IP | EtherCAT | |

| Synchronization error | <<1 | 1 | <1 | <1 | <<1 |

| Cycle time | 100 | 1 ms | 25 | 100 | 100 |

| Communication scope | 100 m | 100 m | 40 m | 100 m | 100 m |

| Transmission speed | 100 M | 100 M | 100 M | 100 M | 100 M |

| Application cost | cheap | expensive | expensive | cheap | cheap |

| Cycle Time () | Operation Period () | |||||

|---|---|---|---|---|---|---|

| 1000 | 500 | 250 | 125 | 50 | 31.25 | |

| HPSA-based master | 995–1005 | 495–505 | 245–260 | 115–130 | 45–60 | 25–35 |

| TwinCAT master | 990–1010 | 490–515 | 230–270 | 80–160 | 0–100 | - |

| Sync Error (ns) | Cycle Time: 1000 | Cycle Time: 125 | ||||

|---|---|---|---|---|---|---|

| 2 Slaves | 5 Slaves | 10 Slaves | 2 Slaves | 5 Slaves | 10 Slaves | |

| HPSA-based system | 0–15 | 5–25 | 10–40 | 0–15 | 5–25 | 10–40 |

| TwinCAT system | 0–15 | 10–35 | 35–65 | 0–20 | 20–35 | 40–70 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Shi, H.; Lin, W.; Liu, C.; Yu, J. A Novel Heterogeneous Parallel System Architecture Based EtherCAT Hard Real-Time Master in High Performance Control System. Electronics 2022, 11, 3124. https://doi.org/10.3390/electronics11193124

Shi H, Lin W, Liu C, Yu J. A Novel Heterogeneous Parallel System Architecture Based EtherCAT Hard Real-Time Master in High Performance Control System. Electronics. 2022; 11(19):3124. https://doi.org/10.3390/electronics11193124

Chicago/Turabian StyleShi, Hongzhe, Weiyang Lin, Chenlu Liu, and Jinyong Yu. 2022. "A Novel Heterogeneous Parallel System Architecture Based EtherCAT Hard Real-Time Master in High Performance Control System" Electronics 11, no. 19: 3124. https://doi.org/10.3390/electronics11193124

APA StyleShi, H., Lin, W., Liu, C., & Yu, J. (2022). A Novel Heterogeneous Parallel System Architecture Based EtherCAT Hard Real-Time Master in High Performance Control System. Electronics, 11(19), 3124. https://doi.org/10.3390/electronics11193124