A 56 GS/s 8 Bit Time-Interleaved ADC in 28 nm CMOS

Abstract

:1. Introduction

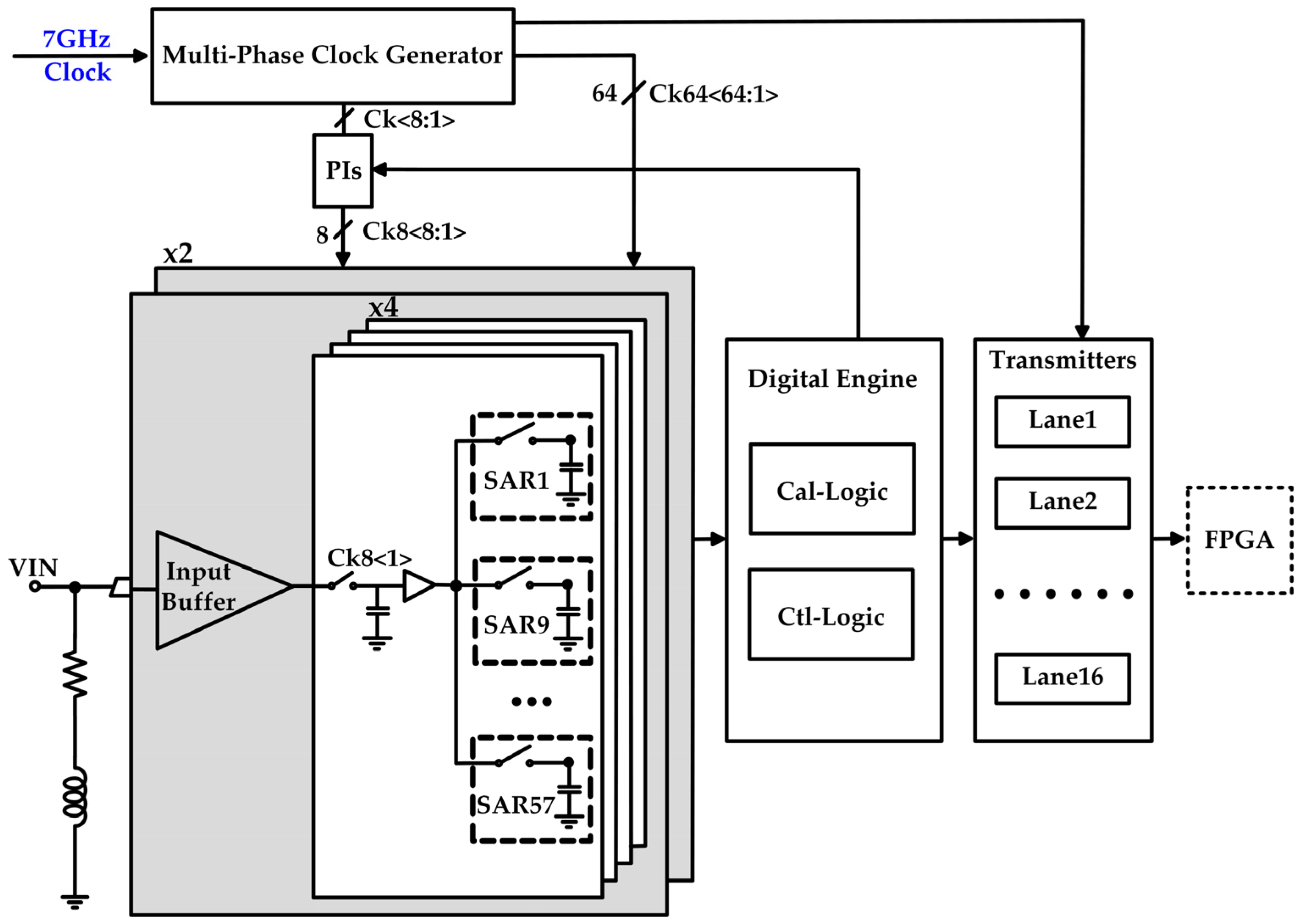

2. Chip Architecture

3. ADC Implementation

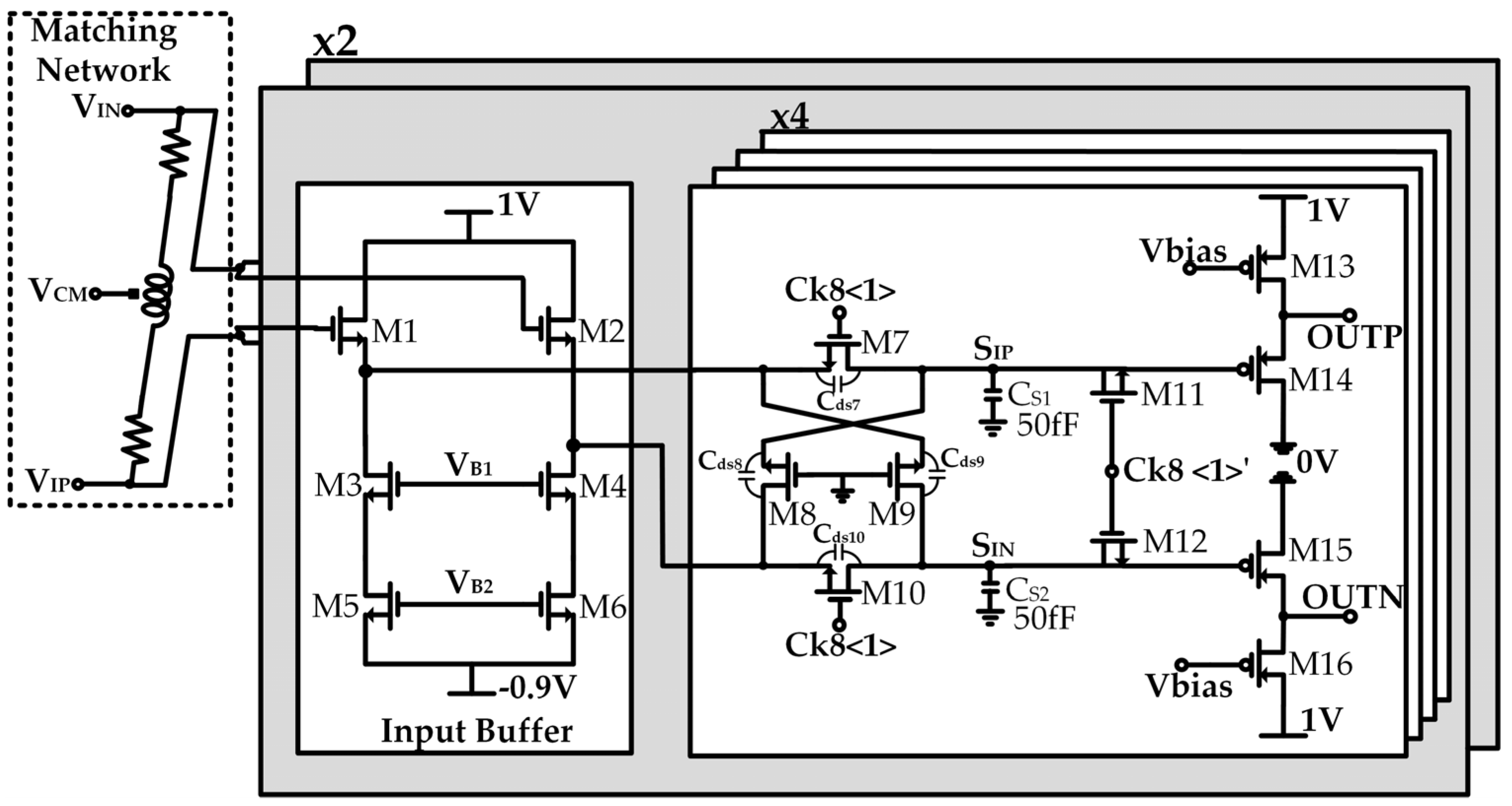

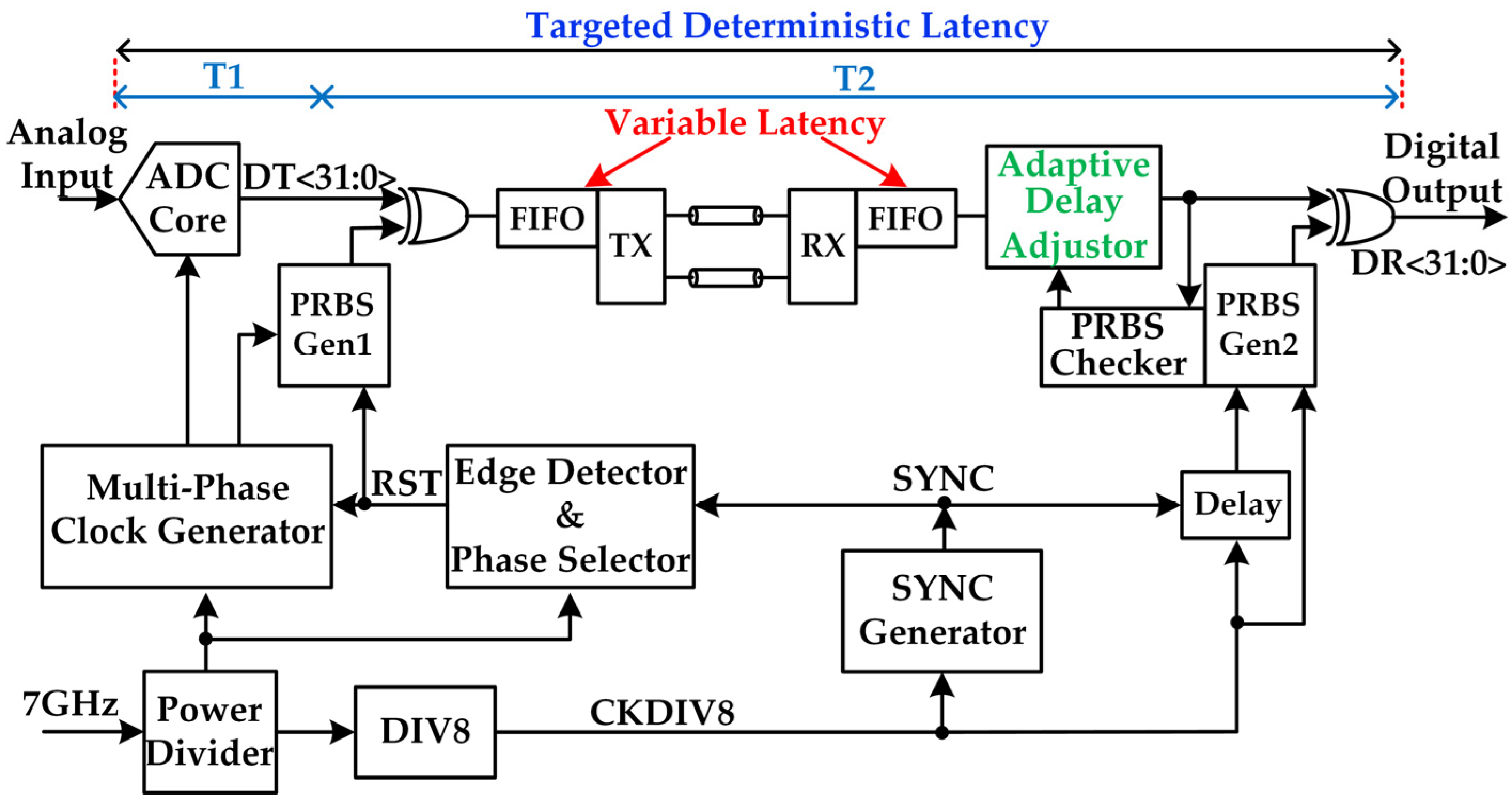

3.1. Sample Front-End

3.2. SAR ADC

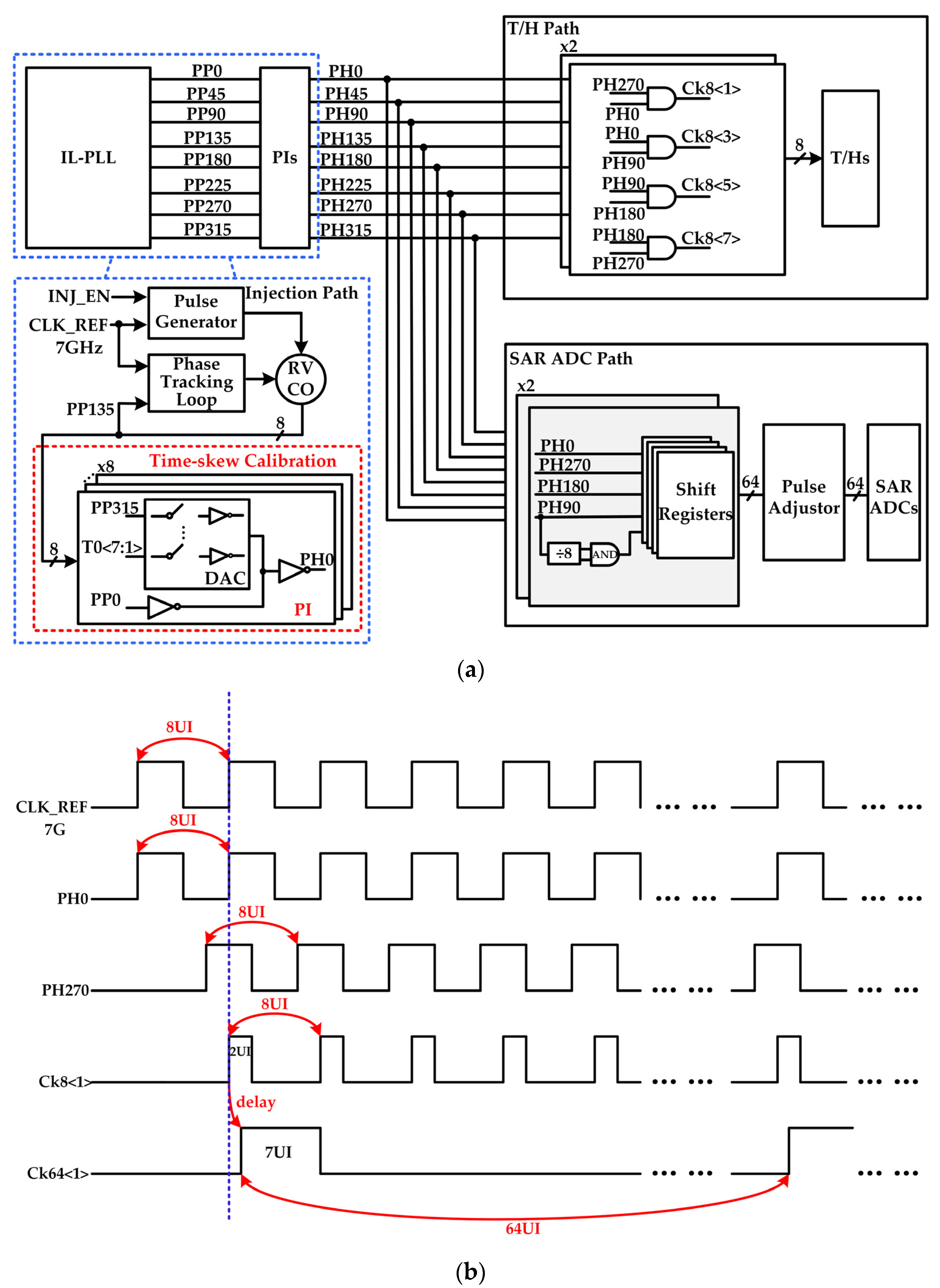

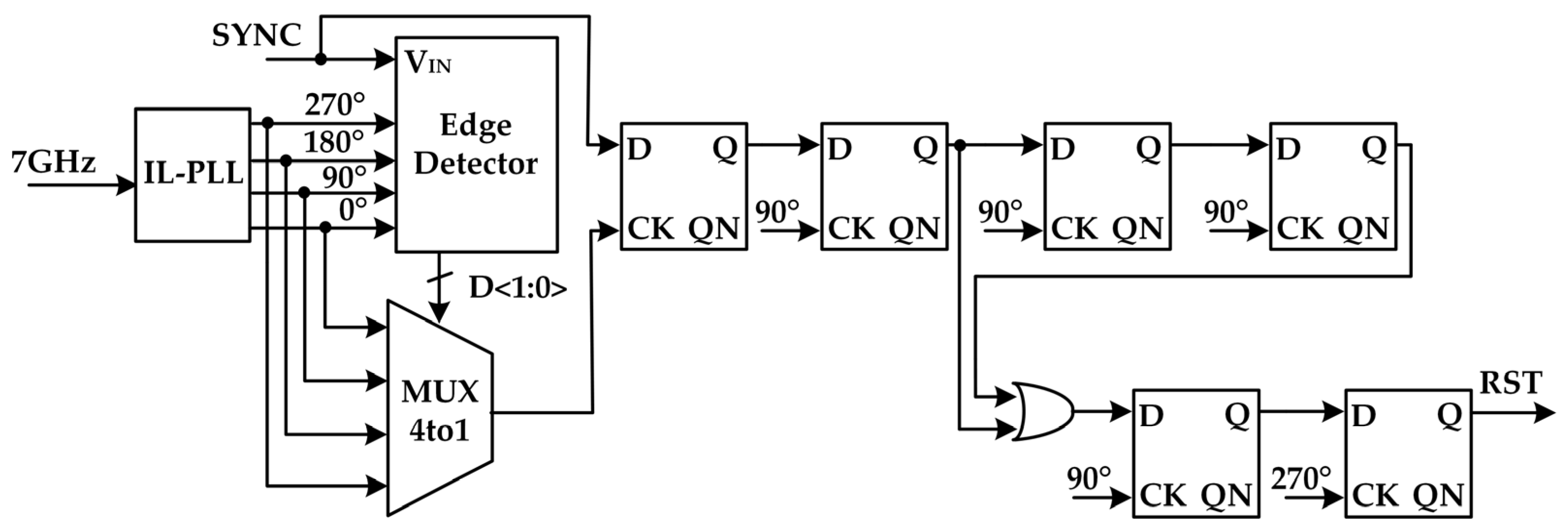

3.3. Multiple Phase Clock Generator

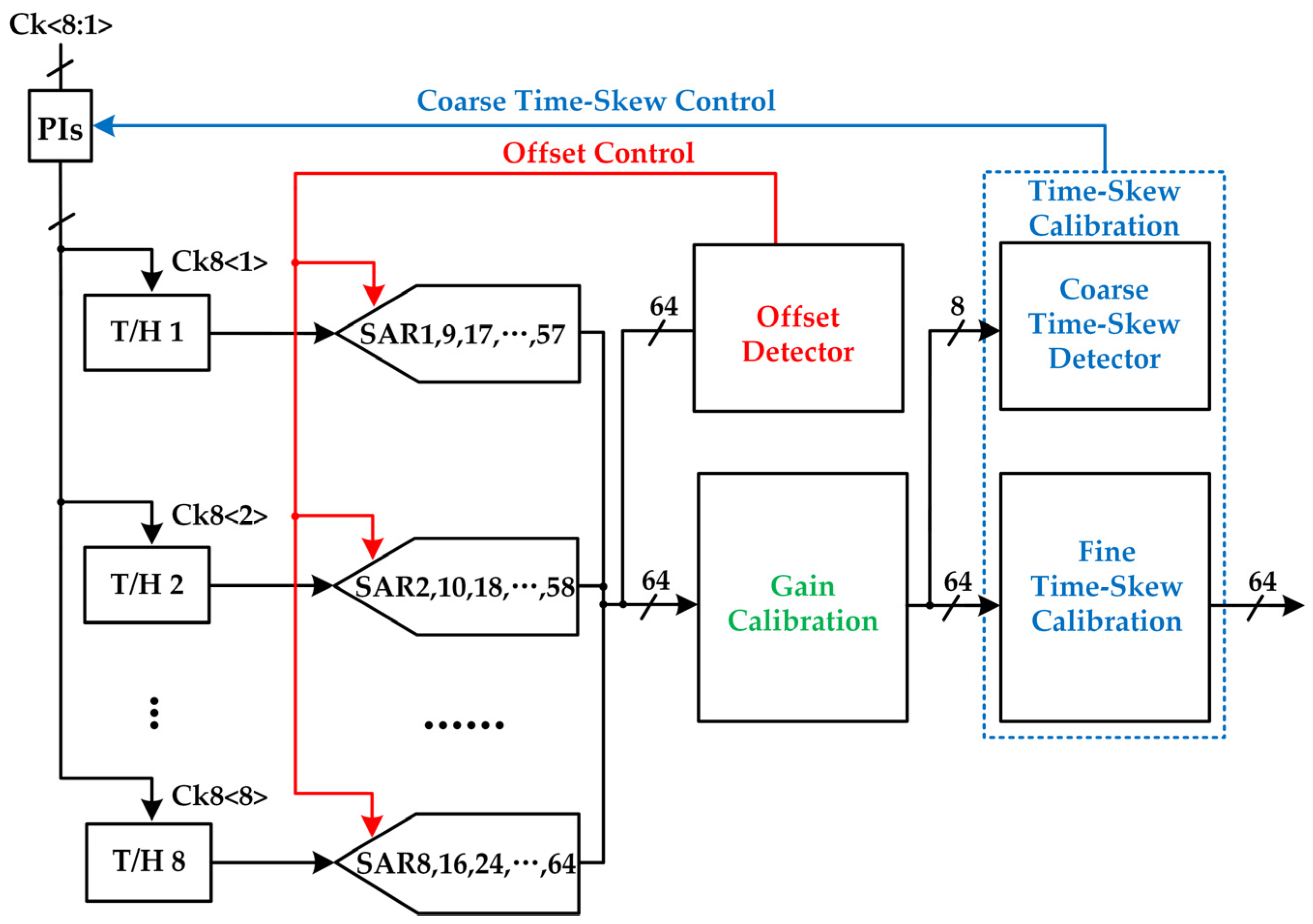

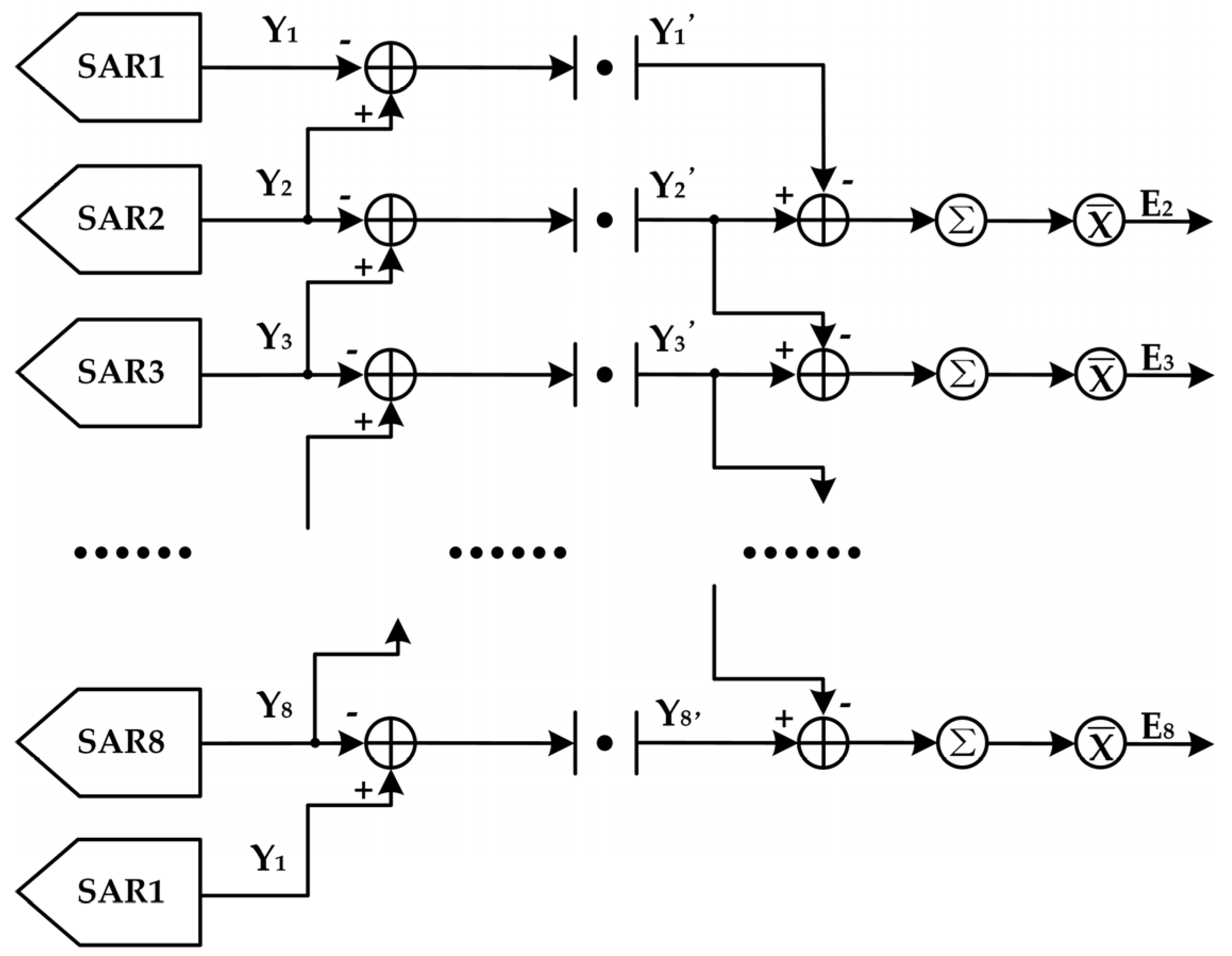

4. Dedicated Calibration

5. Deterministic Latency and Synchronization

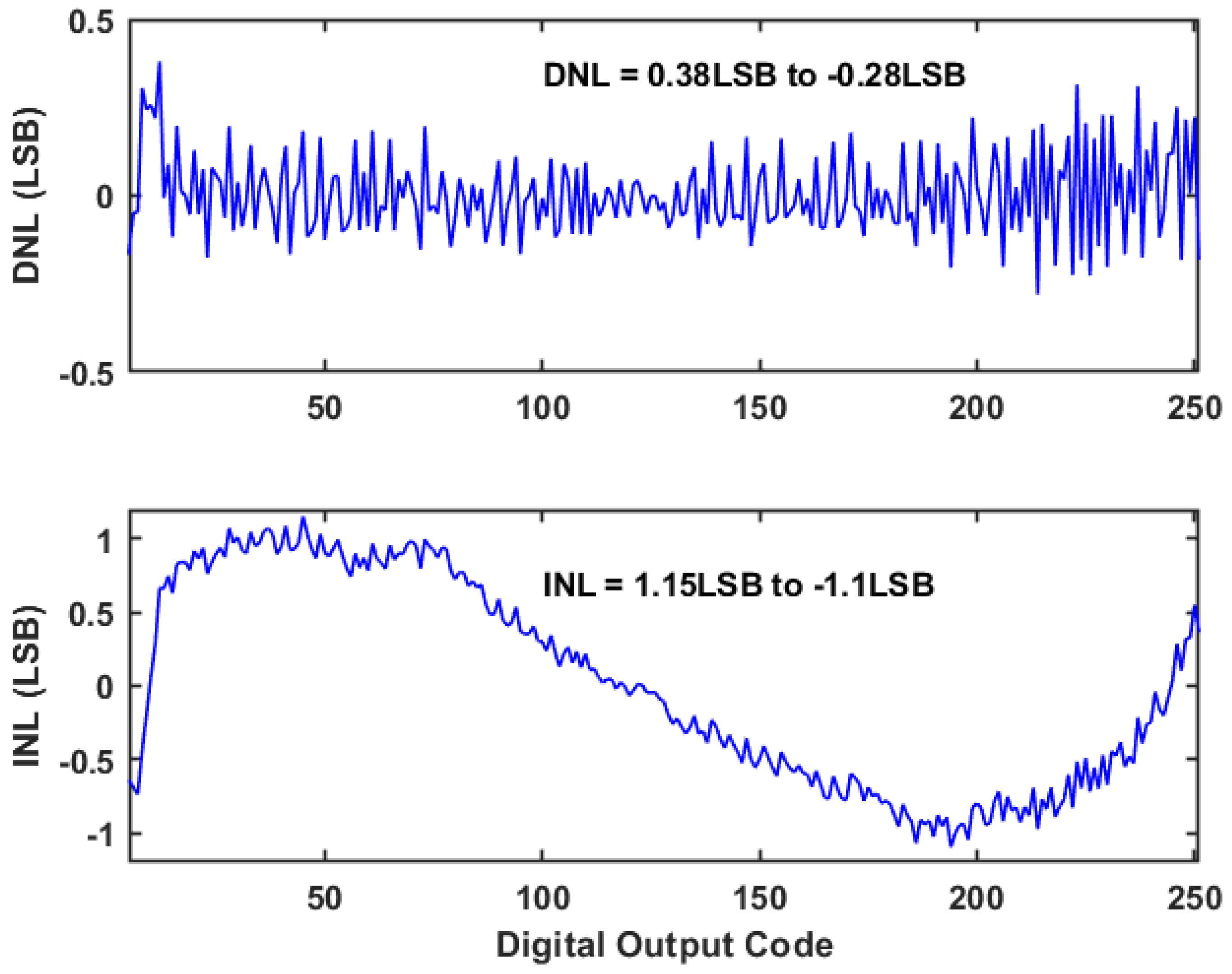

6. Measurement Results

7. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Upadhyaya, P.; Chi, F.; Lim, S.; Cho, J.; Chang, K. A Fully Adaptive 19–58-Gb/s PAM-4 and 9.5–29-Gb/s NRZ Wireline Transceiver with Configurable ADC in 16-nm FinFET. IEEE J. Solid-State Circuits 2019, 54, 18–28. [Google Scholar] [CrossRef]

- Krupnik, Y.; Perelman, Y.; Levin, I.; Sanhedrai, Y.; Eitan, Y.; Khairi, A.; Shifman, Y.; Landau, Y.; Virobnik, U.; Dolev, N.; et al. 112-Gb/s PAM4 ADC-Based SERDES Receiver with Resonant AFE for Long-Reach Channels. IEEE J. Solid-State Circuits 2020, 55, 1077–1085. [Google Scholar] [CrossRef]

- Lin, H.; Boecker, C.; Hossain, M.; Tangirala, S.; Vu, R.; Vamvakos, S.D.; Groen, E.; Li, S.; Choudhary, P.; Wang, N.; et al. ADC-DSP-Based 10-to-112-Gb/s Multi-Standard Receiver in 7-nm FinFET. IEEE J. Solid-State Circuits 2021, 56, 1265–1277. [Google Scholar] [CrossRef]

- Zheng, X.; Ding, H.; Zhao, F.; Wu, D.; Zhou, L.; Wu, J.; Lv, F.; Wang, J.; Liu, X. A 50–112-Gb/s PAM-4 Transmitter with a Fractional-Spaced FFE in 65-nm CMOS. IEEE J. Solid-State Circuits 2020, 55, 1864–1876. [Google Scholar] [CrossRef]

- Cai, C.; Zheng, X.; Chen, Y.; Wu, D.; Luan, J.; Zhou, L.; Wu, J.; Liu, X. A 1.4-Vppd 64-Gb/s PAM-4 Transmitter with 4-Tap Hybrid FFE Employing Fractionally-Spaced Pre-Emphasis and Baud-Spaced De-Emphasis in 28-nm CMOS. In Proceedings of the IEEE 47th European Solid State Circuits Conference (ESSCIRC), Grenoble, France, 13–22 September 2021; pp. 527–553. [Google Scholar]

- Cai, C.; Zheng, X.; Chen, Y.; Wu, D.; Luan, J.; Lu, D.; Zhou, L.; Wu, J.; Liu, X. A 1.55-to-32-Gb/s Four-Lane Transmitter with 3-Tap Feed Forward Equalizer and Shared PLL in 28-nm CMOS. Electronics 2021, 10, 1873. [Google Scholar] [CrossRef]

- Hong, H.; Kim, W.; Kang, H.; Park, S.; Choi, M.; Park, H.; Ryu, S. A decision-error-tolerant 45 nm CMOS 7b 1 GS/s nonbinary 2b/cycle SAR ADC. IEEE J. Solid-State Circuits 2014, 50, 543–555. [Google Scholar] [CrossRef]

- Ramkaj, A.; Strackx, M.; Steyaert, M.; Tavernier, F. A 1.25-GS/s 7-b SAR ADC with 36.4-dB SNDR at 5 GHz using switch-bootstrapping, USPC DAC and triple-tail comparator in 28-nm CMOS. IEEE J. Solid-State Circuits 2018, 53, 1889–1901. [Google Scholar] [CrossRef]

- Kull, L.; Toifl, T.; Schmatz, M.; Francese, P.A.; Menolfi, C.; Braendli, M.; Kossel, M.; Morf, T.; Andersen, T.M.; Leblebici, Y. A 3.1 mW 8b 1.2 GS/s single-channel asynchronous SAR ADC with alternate comparators for enhanced speed in 32 nm digital SOI CMOS. IEEE J. Solid-State Circuits 2013, 48, 3049–3058. [Google Scholar] [CrossRef]

- Wang, G.; Sun, K.; Zhang, Q.; Elahmadi, S.; Gui, P. A 43.6-dB SNDR 1-GS/s single-channel SAR ADC using coarse and fine comparators with background comparator offset calibration. In Proceedings of the 2017 IEEE European Solid State Circuits Conference (ESSCIRC), Leuven, Belgium, 11–14 September 2017; pp. 175–178. [Google Scholar]

- Schvan, P.; Bach, J.; Falt, C.; Flemke, P.; Gibbins, R.; Greshishchev, Y.; Ben-Hamida, N.; Pollex, D.; Sitch, J.; Wang, S.; et al. A 24 GS/s 6b ADC in 90nm CMOS. In Proceedings of the 2008 IEEE International Solid- State Circuits Conference (ISSCC), San Francisco, CA, USA, 3–7 February 2008; pp. 544–634. [Google Scholar]

- Duan, Y.; Alon, E. A 6b 46 GS/s ADC with >23 GHz BW and sparkle-code error correction. In Proceedings of the 2015 Symposium on VLSI Circuits (VLSI Circuits), Kyoto, Japan, 17–19 June 2015; pp. C162–C163. [Google Scholar]

- Kull, L.; Pliva, J.; Toifl, T.; Schmatz, M.; Francese, P.A.; Menolfi, C.; Brandli, M.; Kossel, M.; Morf, T.; Andersen, T.M. Implementation of low-power 6–8 b 30–90 GS/s time-interleaved ADCs with optimized input bandwidth in 32 nm CMOS. IEEE J. Solid-State Circuits 2016, 51, 636–648. [Google Scholar] [CrossRef]

- Xu, B.; Zhou, Y.; Chiu, Y. A 23-mW 24-GS/s 6-bit Voltage-Time Hybrid Time-Interleaved ADC in 28-nm CMOS. IEEE J. Solid-State Circuits 2017, 52, 1091–1100. [Google Scholar] [CrossRef]

- Jo, D.; Sung, B.; Seo, M.; Kim, W.; Ryu, S. A 40 nm CMOS 7 b 32 GS/s SAR ADC with background channel mismatch calibration. IEEE Trans. Circuits Syst. 2020, 67, 610–614. [Google Scholar] [CrossRef]

- Luan, J.; Wu, D.; Zheng, X.; Cai, C.; Wu, L.; Zhou, L.; Wu, J.; Liu, X. A Real-Time Output 50-GS/s 8-bit TI-ADC with Dedicated Calibration Techniques and Deterministic Latency. In Proceedings of the IEEE 47th European Solid State Circuits Conference (ESSCIRC), Grenoble, France, 13–22 September 2021; pp. 487–490. [Google Scholar]

- Greshishchev, Y.M.; Aguirre, J.; Besson, M.; Gibbins, R. A 40 GS/s 6b ADC in 65 nm CMOS. In Proceedings of the 2010 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 7–11 February 2010; pp. 390–391. [Google Scholar]

- Kull, L.; Luu, D.; Menolfi, C.; Brndli, M.; Andrea, F.P.; Morf, T.; Kossel, M.; Cevrero, A.; Ozkaya, I.; Toifl, T. A 24–72 GS/s 8 b time-interleaved SAR ADC with 2.0-to-3.3 pJ/conversion and >30 dB SNDR at nyquist in 14 nm CMOS FinFET. IEEE J. Solid-State Circuits 2018, 53, 3508–3516. [Google Scholar] [CrossRef]

- Sun, K.; Wang, G.; Zhang, Q.; Elahmadi, S.; Gui, P. A 56 GS/s 8bit time-interleaved ADC with ENOB and BW enhancement techniques in 28 nm CMOS. IEEE J. Solid-State Circuits 2019, 54, 821–833. [Google Scholar] [CrossRef]

- Liu, C.; Chang, S.; Huang, G.; Lin, Y.; Huang, C.; Huang, C.; Bu, L.; Tsai, C. A 10b 100 MS/s 1.13 mW SAR ADC with binary-scaled error compensation. In Proceedings of the 2010 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 7–11 February 2010; pp. 386–387. [Google Scholar]

- Cao, J.; Cui, D.; Nazemi, A.; He, T.; Li, G.; Catli, G.; Catli, B.; Khanpour, M.; Hu, K.; Ali, T.; et al. A transmitter and receiver for 100Gb/s coherent networks with integrated 4 × 64 GS/s 8b ADCs and DACs in 20 nm CMOS. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 484–485. [Google Scholar]

- Zheng, X.; Lv, F.; Zhou, L.; Wu, D.; Wu, J.; Zhang, C.; Rhee, W.; Liu, X. Frequency-Domain Modeling and Analysis of Injection-Locked Oscillators. IEEE J. Solid-State Circuits 2020, 55, 1651–1664. [Google Scholar] [CrossRef]

- Razavi, B. Design consideration for interleaved ADC. IEEE J. Solid-State Circuits 2013, 48, 1806–1817. [Google Scholar] [CrossRef] [Green Version]

- Lee, S.; Chandrakasan, A.; Lee, H. A 1 GS/s 10b 18.9 mW Time-Interleaved SAR ADC with Background Timing Skew Calibration. IEEE J. Solid-State Circuits 2014, 49, 2846–2856. [Google Scholar] [CrossRef]

- Chen, V.; Pileggi, L. A 69.5 mW 20 GS/s 6b time-interleaved ADC with embedded time-to-digital calibration in 32 nm CMOS SOI. IEEE J. Solid-State Circuits 2014, 49, 2891–2901. [Google Scholar] [CrossRef]

- Maloberti, F. Data Converters; Springer Science & Business Media: Berlin, Germany, 2007. [Google Scholar]

| Specification | [12] | [13] | [19] | [21] | This Work |

|---|---|---|---|---|---|

| Technology (nm) | 28 | 32 | 28 | 20 | 28 |

| Resolution (bits) | 6 | 8 | 8 | 8 | 8 |

| Sampling Rate (GS/s) | 46 | 90 | 56 | 64 | 56 |

| Output Communication | Memory On-chip | Memory On-chip | Memory On-chip | IP Integration | Real-time Output |

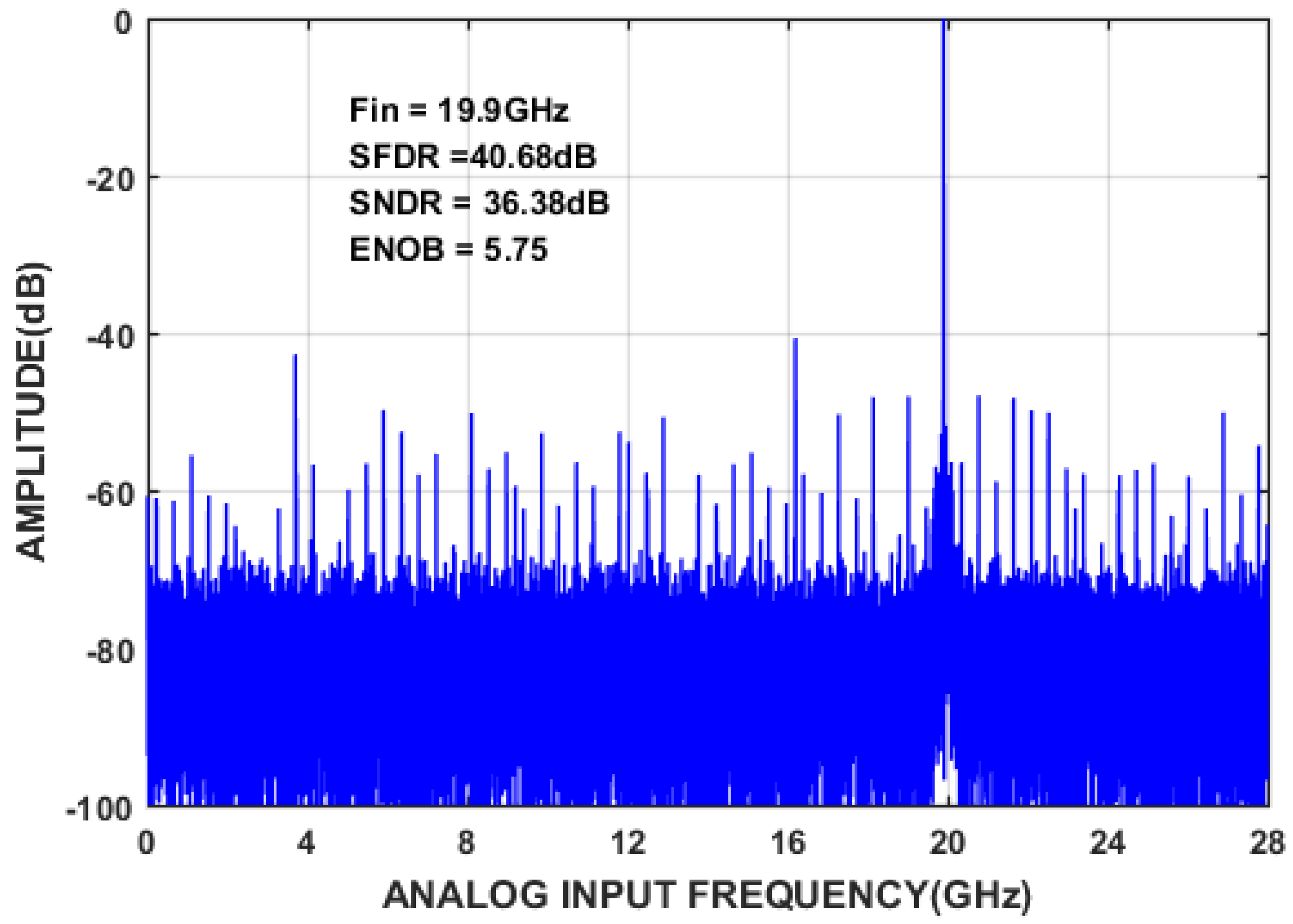

| SNDR@fin,low (dB@GHz) | 27@12 | 36@6 | 40.5@7 | 37.6@8 | [email protected] |

| SNDR@fin,high (dB@GHz) | [email protected] | [email protected] | 33@27 | 33.7@16 | [email protected] |

| SFDR@fin,low (dB@GHz) | [email protected] | NA | 47.7@2 | 50@1 | [email protected] |

| SFDR@fin,high (dB@GHz) | [email protected] | [email protected] | 42@27 | [email protected] | [email protected] |

| Power (mW) | 381 | 667 | 702 | 950 | 432 |

| FOM (fJ/conv.-step) | 453 | 144 | 145 | 240 | 85 |

| Area (mm2) | 0.14 (active) | 0.45 (active) | 0.878 (active) | 1.77 | 1.2 (active) |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Luan, J.; Zheng, X.; Wu, D.; Zhang, Y.; Wu, L.; Zhou, L.; Wu, J.; Liu, X. A 56 GS/s 8 Bit Time-Interleaved ADC in 28 nm CMOS. Electronics 2022, 11, 688. https://doi.org/10.3390/electronics11050688

Luan J, Zheng X, Wu D, Zhang Y, Wu L, Zhou L, Wu J, Liu X. A 56 GS/s 8 Bit Time-Interleaved ADC in 28 nm CMOS. Electronics. 2022; 11(5):688. https://doi.org/10.3390/electronics11050688

Chicago/Turabian StyleLuan, Jian, Xuqiang Zheng, Danyu Wu, Yuzhen Zhang, Linzhen Wu, Lei Zhou, Jin Wu, and Xinyu Liu. 2022. "A 56 GS/s 8 Bit Time-Interleaved ADC in 28 nm CMOS" Electronics 11, no. 5: 688. https://doi.org/10.3390/electronics11050688