Fabrication and Characterization of Micrometer Scale Graphene Structures for Large-Scale Ultra-Thin Electronics

Abstract

:1. Introduction

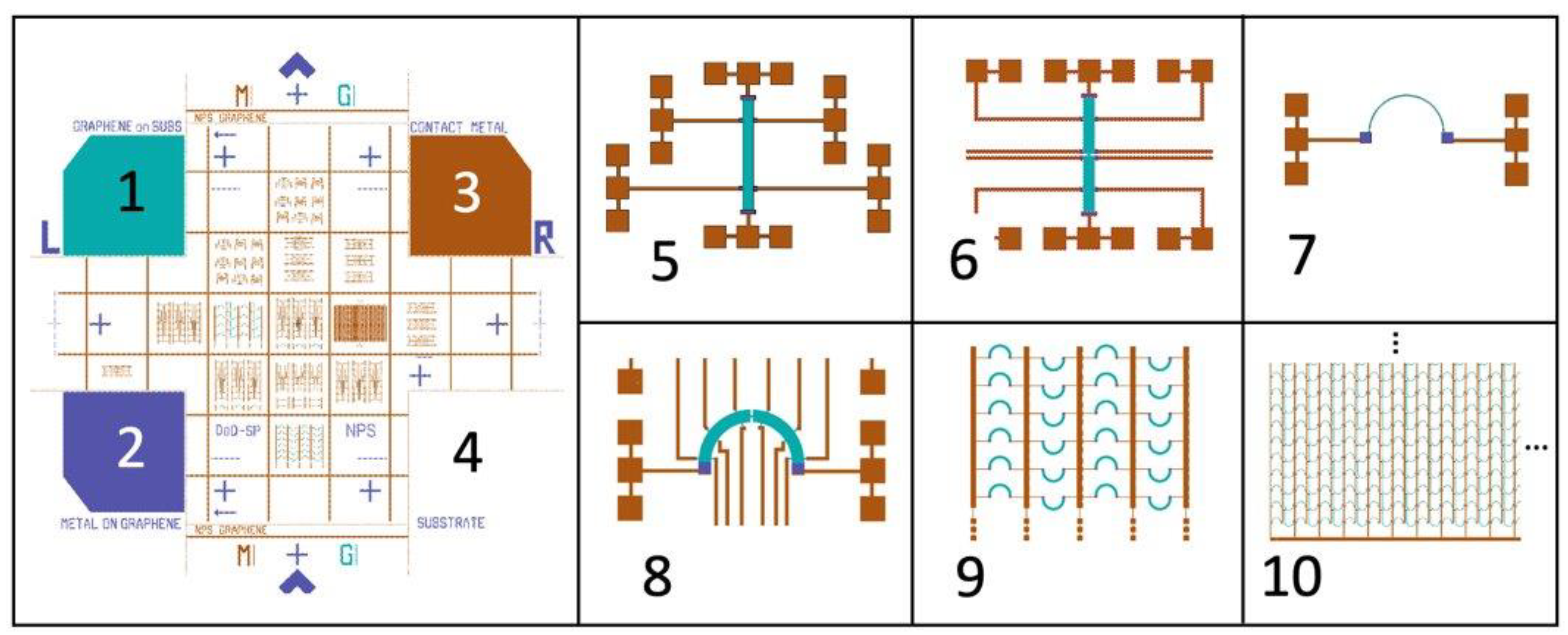

2. Materials and Methods

2.1. Fabrication

2.2. Characterization

2.2.1. Raman Spectrum

2.2.2. Patterning Fidelity

3. Results

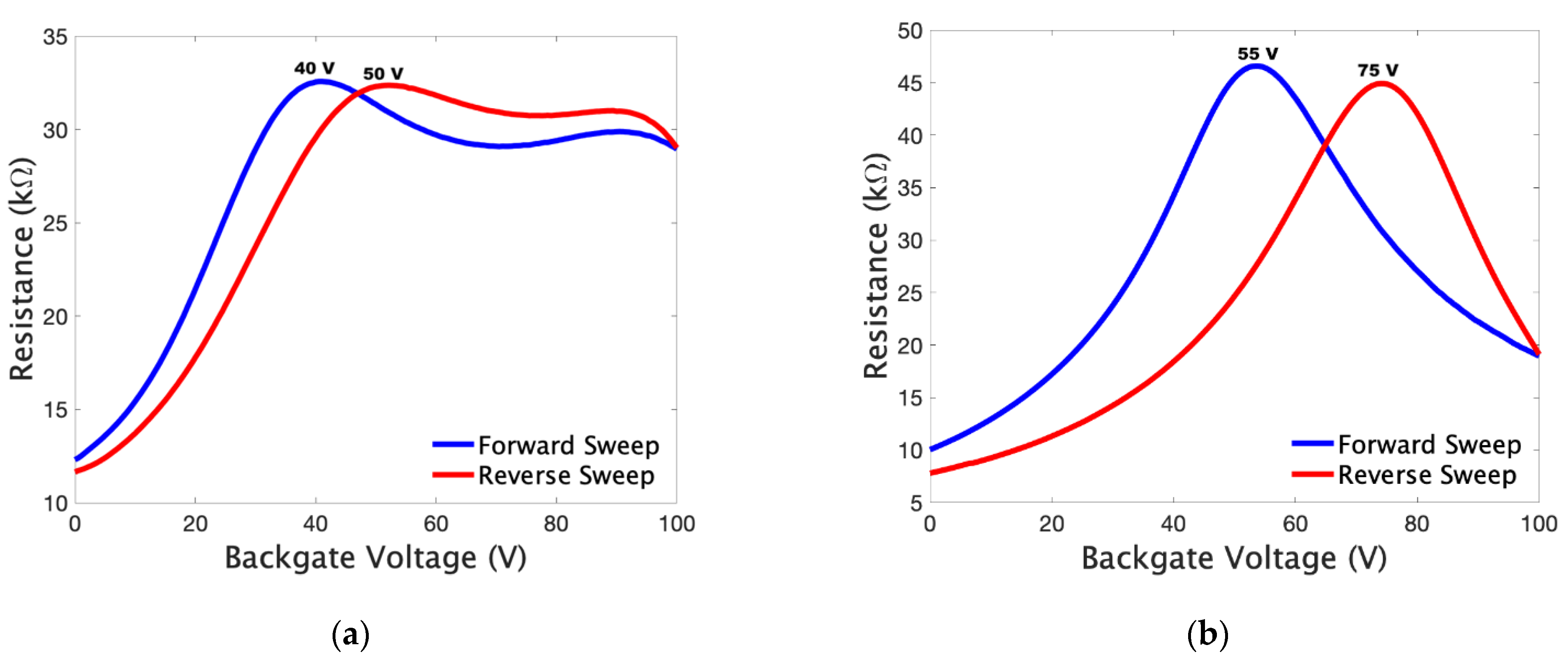

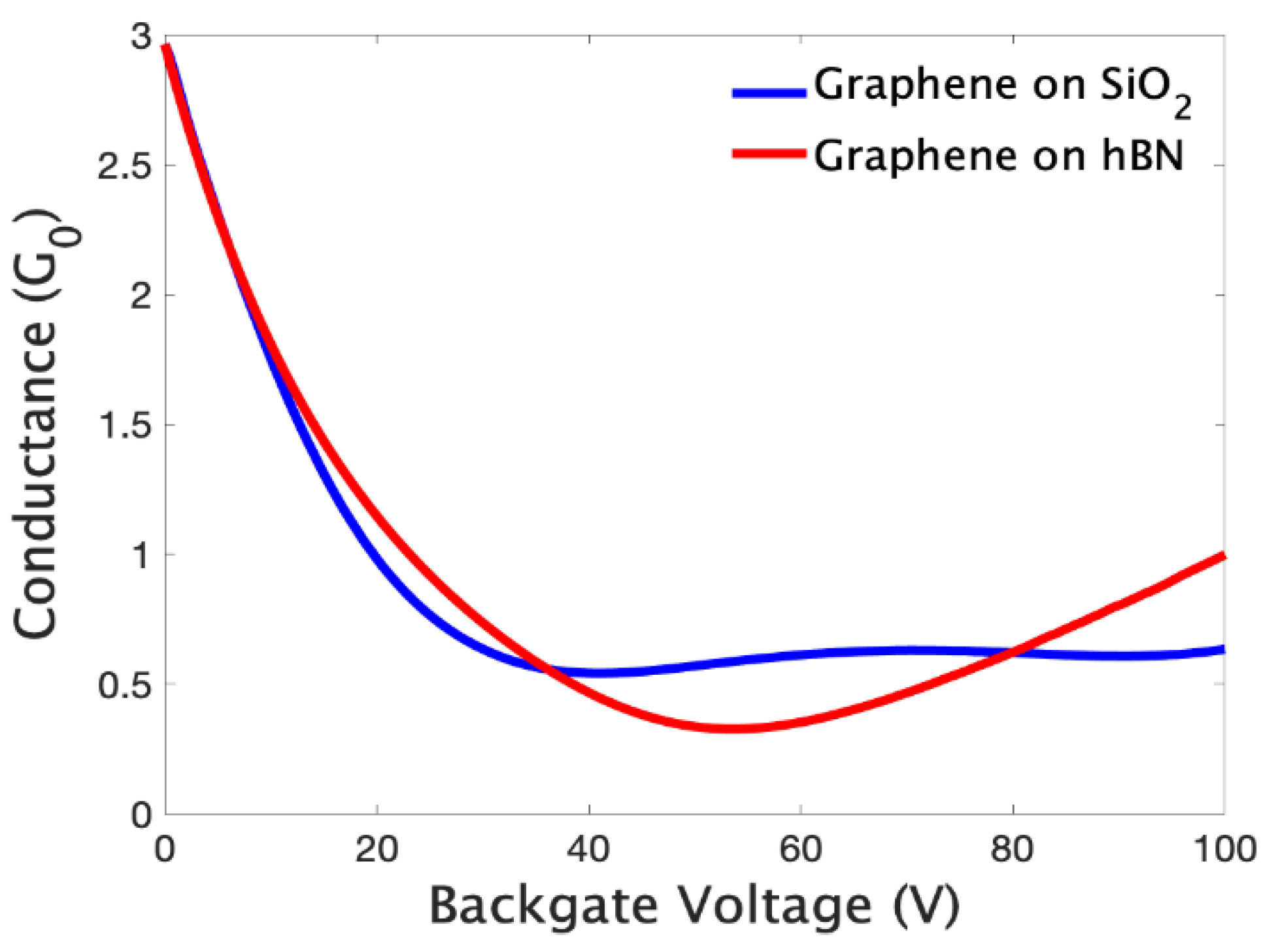

3.1. Electrical Resistance Measurements

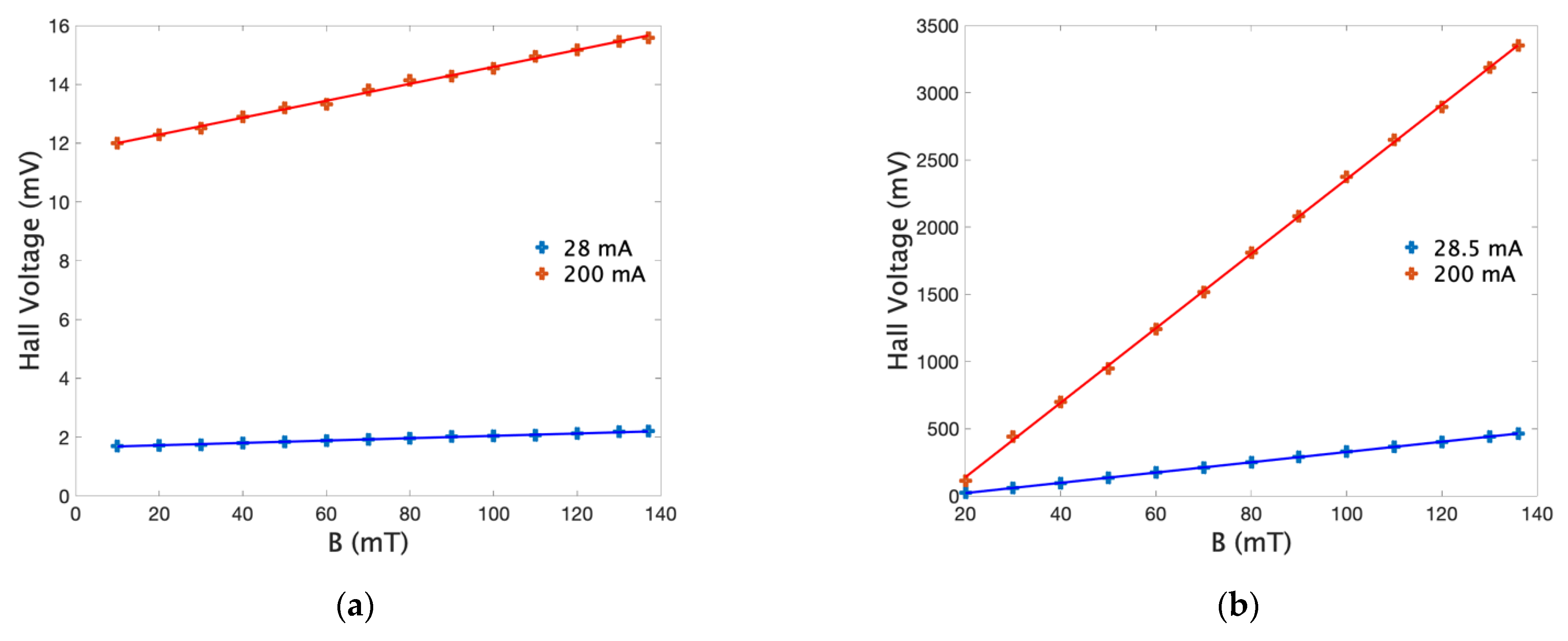

3.2. Hall Effect Measurements

4. Discussion

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Novoselov, K.S. Electric Field Effect in Atomically Thin Carbon Films. Science 2004, 306, 666–669. [Google Scholar] [CrossRef] [Green Version]

- Novoselov, K.S.; Jiang, D.; Schedin, F.; Booth, T.J.; Khotkevich, V.V.; Morozov, S.V.; Geim, A.K. Two-Dimensional Atomic Crystals. Proc. Natl. Acad. Sci. USA 2005, 102, 10451–10453. [Google Scholar] [CrossRef] [Green Version]

- Banszerus, L.; Sohier, T.; Epping, A.; Winkler, F.; Libisch, F.; Haupt, F.; Watanabe, K.; Taniguchi, T.; Müller-Caspary, K.; Marzari, N.; et al. Extraordinary High Room-Temperature Carrier Mobility in Graphene-WSe2 Heterostructures. arXiv 2019, arXiv:1909.09523. [Google Scholar]

- Shishir, R.S.; Ferry, D.K. Velocity Saturation in Intrinsic Graphene. J. Phys. Condens. Matter 2009, 21, 344201. [Google Scholar] [CrossRef] [PubMed]

- Reina, A.; Jia, X.; Ho, J.; Nezich, D.; Son, H.; Bulovic, V.; Dresselhaus, M.S.; Kong, J. Large Area, Few-Layer Graphene Films on Arbitrary Substrates by Chemical Vapor Deposition. Nano Lett. 2009, 9, 30–35. [Google Scholar] [CrossRef] [PubMed]

- Chae, S.J.; Güneş, F.; Kim, K.K.; Kim, E.S.; Han, G.H.; Kim, S.M.; Shin, H.-J.; Yoon, S.-M.; Choi, J.-Y.; Park, M.H.; et al. Synthesis of Large-Area Graphene Layers on Poly-Nickel Substrate by Chemical Vapor Deposition: Wrinkle Formation. Adv. Mater. 2009, 21, 2328–2333. [Google Scholar] [CrossRef]

- Bae, S.; Kim, H.; Lee, Y.; Xu, X.; Park, J.-S.; Zheng, Y.; Balakrishnan, J.; Lei, T.; Kim, H.R.; Song, Y.I.; et al. Roll-to-Roll Production of 30-Inch Graphene Films for Transparent Electrodes. Nat. Nanotechnol. 2010, 5, 574–578. [Google Scholar] [CrossRef] [Green Version]

- Kitaura, R.; Miyata, Y.; Xiang, R.; Hone, J.; Kong, J.; Ruoff, R.S.; Maruyama, S. Chemical Vapor Deposition Growth of Graphene and Related Materials. J. Phys. Soc. Jpn. 2015, 84, 121013. [Google Scholar] [CrossRef]

- De Fazio, D.; Purdie, D.G.; Ott, A.K.; Braeuninger-Weimer, P.; Khodkov, T.; Goossens, S.; Taniguchi, T.; Watanabe, K.; Livreri, P.; Koppens, F.H.L.; et al. High-Mobility, Wet-Transferred Graphene Grown by Chemical Vapor Deposition. ACS Nano 2019, 13, 8926–8935. [Google Scholar] [CrossRef] [Green Version]

- Cheap Tubes Inc. CVD Graphene on Si-SiO2 4 Inch; Cheap Tubes Inc.: Grafton, VT, USA.

- Chen, J.-H.; Jang, C.; Xiao, S.; Ishigami, M.; Fuhrer, M.S. Intrinsic and Extrinsic Performance Limits of Graphene Devices on SiO2. Nat. Nanotechnol. 2008, 3, 206–209. [Google Scholar] [CrossRef]

- Majety, S.; Cao, X.K.; Dahal, R.; Pantha, B.N.; Li, J.; Lin, J.Y.; Jiang, H.X. Semiconducting Hexagonal Boron Nitride for Deep Ultraviolet Photonics. In Quantum Sensing Nanophotonic Devices IX; International Society for Optics and Photonics: Bellingham, WA, USA, 2012. [Google Scholar] [CrossRef]

- Garcia, A.G.F.; Neumann, M.; Amet, F.; Williams, J.R.; Watanabe, K.; Taniguchi, T.; Goldhaber-Gordon, D. Effective Cleaning of Hexagonal Boron Nitride for Graphene Devices. Nano Lett. 2012, 12, 4449–4454. [Google Scholar] [CrossRef] [PubMed]

- Kim, K.K.; Kim, S.M.; Lee, Y.H. A New Horizon for Hexagonal Boron Nitride Film. J. Korean Phys. Soc. 2014, 64, 1605–1616. [Google Scholar] [CrossRef]

- Yamoah, M.A.; Yang, W.; Pop, E.; Goldhaber-Gordon, D. High-Velocity Saturation in Graphene Encapsulated by Hexagonal Boron Nitride. ACS Nano 2017, 11, 9914–9919. [Google Scholar] [CrossRef] [PubMed]

- Kim, S.M.; Hsu, A.; Araujo, P.T.; Lee, Y.-H.; Palacios, T.; Dresselhaus, M.; Idrobo, J.-C.; Kim, K.K.; Kong, J. Synthesis of Patched or Stacked Graphene and HBN Flakes: A Route to Hybrid Structure Discovery. Nano Lett. 2013, 13, 933–941. [Google Scholar] [CrossRef] [PubMed]

- Stehle, Y.; Meyer, H.M.; Unocic, R.R.; Kidder, M.; Polizos, G.; Datskos, P.G.; Jackson, R.; Smirnov, S.N.; Vlassiouk, I.V. Synthesis of Hexagonal Boron Nitride Monolayer: Control of Nucleation and Crystal Morphology. Chem. Mater. 2015, 27, 8041–8047. [Google Scholar] [CrossRef]

- Guo, Q.; Li, C.; Deng, B.; Yuan, S.; Guinea, F.; Xia, F. Infrared Nanophotonics Based on Graphene Plasmonics. ACS Photonics 2017, 4, 2989–2999. [Google Scholar] [CrossRef]

- Huang, S.; Song, C.; Zhang, G.; Yan, H. Graphene Plasmonics: Physics and Potential Applications. Nanophotonics 2016, 6, 1191–1204. [Google Scholar] [CrossRef]

- Kim, J.Y.; Cho, N.S.; Cho, S.; Kim, K.; Cheon, S.; Kim, K.; Kang, S.-Y.; Cho, S.M.; Lee, J.-I.; Oh, J.-Y.; et al. Graphene Electrode Enabling Electrochromic Approaches for Daylight-Dimming Applications. Sci. Rep. 2018, 8, 16924. [Google Scholar] [CrossRef]

- Woo, Y. Transparent Conductive Electrodes Based on Graphene-Related Materials. Micromachines 2018, 10, 13. [Google Scholar] [CrossRef] [Green Version]

- Beiranvand, B.; Sobolev, A.S. A Proposal for a Multi-Functional Tunable Dual-Band Plasmonic Absorber Consisting of a Periodic Array of Elliptical Grooves. J. Opt. 2020, 22, 105005. [Google Scholar] [CrossRef]

- Beiranvand, B.; Sobolev, A.S.; Sheikhaleh, A. A Proposal for a Dual-Band Tunable Plasmonic Absorber Using Concentric-Rings Resonators and Mono-Layer Graphene. Optik 2020, 223, 165587. [Google Scholar] [CrossRef]

- Dong, Y.; Xiong, L.; Phinney, I.Y.; Sun, Z.; Jing, R.; McLeod, A.S.; Zhang, S.; Liu, S.; Ruta, F.L.; Gao, H.; et al. Fizeau Drag in Graphene Plasmonics. Nature 2021, 594, 513–516. [Google Scholar] [CrossRef] [PubMed]

- Morgado, T.A.; Silveirinha, M.G. Active Graphene Plasmonics with a Drift-Current Bias. ACS Photonics 2021, 8, 1129–1136. [Google Scholar] [CrossRef]

- Liu, C. Foundations of MEMS, 2nd ed.; Prentice Hall: Upper Saddle River, NJ, USA, 2012; ISBN 978-0-13-249736-7. [Google Scholar]

- Childres, I.; Jauregui, L.A.; Park, W.; Cao, H.; Chen, Y.P. Raman Spectroscopy of Graphene and Related Materials. New Dev. Photon Mater. Res. 2013, 1, 1–20. [Google Scholar]

- Wojtaszek, M. Graphene: A Two Type Charge Carrier System. Master’s Thesis, Faculteit der Wiskunde en Natuurwetenschappen, Groningen, The Netherlands, 2009. [Google Scholar]

- Guo, Y.; Wei, X.; Shu, J.; Liu, B.; Yin, J.; Guan, C.; Han, Y.; Gao, S.; Chen, Q. Charge Trapping at the MoS-SiO2 Interface and Its Effects on the Characteristics of MoS Metal-Oxide-Semiconductor Field Effect Transistors. Appl. Phys. Lett. 2015, 106, 103109. [Google Scholar] [CrossRef]

- Zhong, H.; Zhang, Z.; Xu, H.; Qiu, C.; Peng, L.-M. Comparison of Mobility Extraction Methods Based on Field-Effect Measurements for Graphene. AIP Adv. 2015, 5, 057136. [Google Scholar] [CrossRef]

- Hui, Y.X.; An, N.; Chen, K.; Li, X.J.; Li, W.L.; Ren, Z.Y. Research on Hall Effect of Graphene by Var Der Pauw Method. Adv. Mater. Res. 2015, 1120–1121, 383–387. [Google Scholar] [CrossRef]

- Van Wees, B.J.; van Houten, H.; Beenakker, C.W.J.; Williamson, J.G.; Kouwenhoven, L.P.; van der Marel, D.; Foxon, C.T. Quantized Conductance of Point Contacts in a Two-Dimensional Electron Gas. Phys. Rev. Lett. 1988, 60, 848–850. [Google Scholar] [CrossRef] [Green Version]

- Sze, S.; Irvin, J. Resistivity, Mobility and Impurity Levels in GaAs, Ge, and Si at 300 K. Solid-State Electron. 1968, 11, 599–602. [Google Scholar] [CrossRef]

- Tse, W.-K.; Hwang, E.H.; Sarma, S.D. Ballistic Hot Electron Transport in Graphene. Appl. Phys. Lett. 2008, 93, 023128. [Google Scholar] [CrossRef] [Green Version]

| Dielectric Material | nTLM (cm−2) | nHall (cm−2) | RHall (m3/C) | μTLM (cm2/Vs) | μHall (cm2/Vs) | μ (cm2/Vs) |

|---|---|---|---|---|---|---|

| Graphene on SiO2 | 2.79 × 1012 | 7.8 × 1015 | 1.435 × 10−11 | 5.20 × 103 | 3.5 | 2.6 |

| Graphene on hBN | 3.84 × 1012 | 8.2 × 1012 | 1.365 × 10−8 | 3.78 × 103 | 3 × 103 | 2.68 × 103 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Planillo, J.; Alves, F. Fabrication and Characterization of Micrometer Scale Graphene Structures for Large-Scale Ultra-Thin Electronics. Electronics 2022, 11, 752. https://doi.org/10.3390/electronics11050752

Planillo J, Alves F. Fabrication and Characterization of Micrometer Scale Graphene Structures for Large-Scale Ultra-Thin Electronics. Electronics. 2022; 11(5):752. https://doi.org/10.3390/electronics11050752

Chicago/Turabian StylePlanillo, Jordan, and Fabio Alves. 2022. "Fabrication and Characterization of Micrometer Scale Graphene Structures for Large-Scale Ultra-Thin Electronics" Electronics 11, no. 5: 752. https://doi.org/10.3390/electronics11050752

APA StylePlanillo, J., & Alves, F. (2022). Fabrication and Characterization of Micrometer Scale Graphene Structures for Large-Scale Ultra-Thin Electronics. Electronics, 11(5), 752. https://doi.org/10.3390/electronics11050752