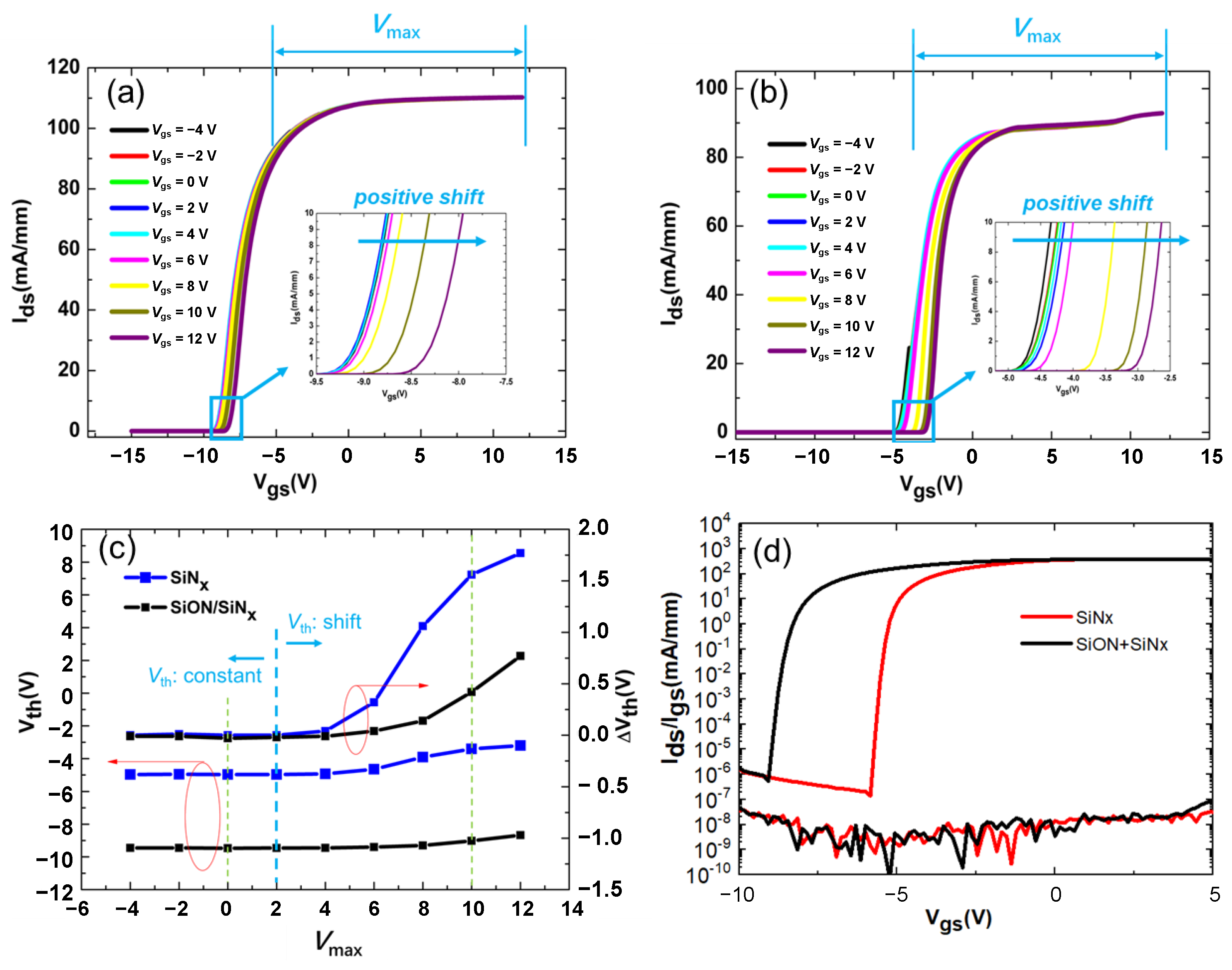

Low Threshold Voltage Shift in AlGaN/GaN MIS-HEMTs on Si Substrate Using SiNx/SiON as Composite Gate Dielectric

Abstract

:1. Introduction

2. Materials and Methods

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Baliga, B.J. Gallium nitride devices for power electronic applications. Semicond. Sci. Technol. 2013, 28, 074011. [Google Scholar] [CrossRef]

- Fu, H.; Fu, K.; Yang, C.; Liu, H.; Hatch, K.A.; Peri, P.; Mudiyanselage, D.H.; Li, B.; Kim, T.-H.; Alugubelli, S.R.; et al. Selective area regrowth and doping for vertical gallium nitride power devices: Materials challenges and recent progress. Mater. Today 2021, 49, 296–323. [Google Scholar] [CrossRef]

- Chen, K.J.; Häberlen, O.; Lidow, A.; Lin Tsai, C.; Ueda, T.; Uemoto, Y.; Wu, Y. GaN-on-Si power technology: Devices and applica-tions. IEEE Trans. Electron Devices 2017, 64, 779–795. [Google Scholar] [CrossRef]

- Ikeda, N.; Niiyama, Y.; Kambayashi, H.; Sato, Y.; Nomura, T.; Kato, S.; Yoshida, S. GaN Power Transistors on Si Substrates for Switching Applications. Proc. IEEE 2010, 98, 1151–1161. [Google Scholar] [CrossRef]

- Hao, R.; Sun, C.; Fang, B.; Xu, N.; Tao, Z.; Zhang, H.; Wei, X.; Lin, W.; Zhang, X.; Yu, G.; et al. Monolithic integration of en-hancement/depletion-mode high electron mobility transistors using hydrogen plasma treatment. Appl. Phys. Express 2019, 12, 036502. [Google Scholar] [CrossRef]

- Hashizume, T.; Nishiguchi, K.; Kaneki, S.; Kuzmik, J.; Yatabe, Z. State of the art on gate insulation and surface passivation for GaN-based power HEMTs. Mater. Sci. Semicond. Processing 2018, 78, 85–95. [Google Scholar] [CrossRef]

- Fu, K.; Fu, H.; Huang, X.; Yang, T.H.; Chen, H.; Baranowski, I.; Montes, J.; Yang, C.; Zhou, J.; Zhao, Y. Threshold switching and memory behaviors of epitaxially regrown GaN-on-GaN vertical p-ndiodes with high temperature stability. IEEE Electron Device Lett. 2019, 40, 375. [Google Scholar] [CrossRef]

- Lagger, P.; Ostermaier, C.; Pobegen, G.; Pogany, D. Towards understanding the origin of threshold voltage instability of AlGaN/GaN MIS-HEMTs. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 10–13 December 2012; pp. 13.1.1–13.1.4. [Google Scholar]

- Asubar, J.T.; Yatabe, Z.; Gregusova, D.; Hashizume, T. Controlling surface/interface states in GaN-based transistors: Surface model insulated gate and surface passivation. J. Appl. Phys. 2021, 129, 121102. [Google Scholar] [CrossRef]

- Joshi, V.; Gupta, S.D.; Chaudhuri, R.R.; Shrivastava, M. Physical Insights Into the Impact of Surface Traps on Breakdown Char-acteristics of AlGaN/GaN HEMTs—Part I. IEEE Trans. Electron Devices 2021, 68, 72–79. [Google Scholar] [CrossRef]

- Arulkumaran, S.; Egawa, T.; Ishikawa, H.; Jimbo, T.; Sano, Y. Surface passivation effects on AlGaN/GaN high-electron-mobility transistors with SiO2, Si3N4, and silicon oxynitride. Appl. Phys. Lett. 2004, 84, 613. [Google Scholar] [CrossRef]

- Zhang, Z.; Li, W.; Fu, K.; Yu, G.; Zhang, X.; Zhao, Y. AlGaN/GaN MIS-HEMTs of Very Low Vth Hysteresis and Current Collapse with In-Situ Pre-Deposition Plasma Nitridation and LPCVD-Si3N4 Gate Insulator. IEEE Electron Device Lett. 2017, 38, 2. [Google Scholar] [CrossRef]

- Sun, Z.; Cheng, W.; Gao, J.; Liang, H.; Huang, H.; Wang, R.; Sun, N.; Tao, P.; Ren, Y.; Song, S.; et al. Improving Performances of Enhancement-Mode AlGaN/GaN MIS-HEMTs on 6-inch Si Substrate Utilizing SiON/Al2O3 Stack Dielectrics. IEEE Electron Device Lett. 2020, 41, 135–138. [Google Scholar] [CrossRef]

- Kim, H.S.; Han, S.W.; Jang, W.H.; Cho, C.H.; Seo, K.S.; Oh, J.; Cha, H.Y. Normally-off GaN-on-Si MISFET using PECVD SiON gate dielectric. IEEE Electron Device Lett. 2017, 38, 1090–1093. [Google Scholar] [CrossRef]

- Dutta, G.; DasGupta, N.; DasGupta, A. Effect of Sputtered-Al2O3 Layer Thickness on the Threshold Voltage of III-Nitride MIS-HEMTs. IEEE Trans. Electron Devices 2016, 63, 4. [Google Scholar] [CrossRef]

- Sun, X.; Saadat, O.I.; Chang-Liao, K.S.; Palacios, T.; Cui, S.; Ma, T.P. Study of gate oxide traps in HfO2/AlGaN/GaN met-al-oxide-semiconductor high-electron-mobility transistors by use of ac transconductance method. Appl. Phys. Lett. 2013, 102, 103504. [Google Scholar] [CrossRef] [Green Version]

- Cui, P.; Zhang, J.; Jia, M.; Lin, G.; Wei, L.; Zhao, H.; Gundlach, L.; Zeng, Y. InAlN/GaN metal–insulator–semiconductor high-electron-mobility transistor with plasma enhanced atomic layer-deposited ZrO2 as gate dielectric. Jpn. J. Appl. Phys. 2020, 59, 020901. [Google Scholar] [CrossRef]

- Yang, T.-H.; Brown, J.; Fu, K.; Zhou, J.; Hatch, K.; Yang, C.; Montes, J.; Qi, X.; Fu, H.; Nemanich, R.J.; et al. AlGaN/GaN metal–insulator–semiconductor high electron mobility transistors (MISHEMTs) using plasma deposited BN as gate dielectric. Appl. Phys. Lett. 2021, 118, 072102. [Google Scholar] [CrossRef]

- Zhang, Z.; Yu, G.; Zhang, X.; Deng, X.; Li, S.; Fan, Y.; Sun, S.; Song, L.; Tan, S.; Wu, D.; et al. Studies on High Voltage GaN-on-Si MIS-HEMTs Using LPCVD-Si3N4 as Gate Dielectric and Passivation Layer, Electron Devices. IEEE Trans. Electron Devices 2015, 63, 731–738. [Google Scholar] [CrossRef]

- Rzin, M.; Guillet, B.; Mechin, L.; Gamarra, P.; Lacam, C.; Medjdoub, F.; Routoure, J.-M. Routoure, Impact of the in situ SiN Thickness on Low-Frequency Noise in MOVPE InAlGaN/GaN HEMTs. IEEE Trans. Electron Devices 2019, 66, 5080–5083. [Google Scholar] [CrossRef]

- Roccaforte, F.; Fiorenza, P.; Greco, G.; Nigro, R.L.; Giannazzo, F.; Iucolano, F.; Saggio, M. Emerging trends in wide band gap sem-iconductors (SiC and GaN) technology for power devices. Microelectron. Eng. 2018, 187–188, 66–77. [Google Scholar] [CrossRef]

- Zeng, F.; An, J.X.; Zhou, G.; Li, W.; Wang, H.; Duan, T.; Jiang, L.; Yu, H. A Comprehensive Review of Recent Progress on GaN High Electron Mobility Transistors: Devices, Fabrication and Reliability. Electronics 2018, 7, 377. [Google Scholar] [CrossRef] [Green Version]

- Hua, M.; Zhang, Z.; Wei, J.; Lei, J.; Tang, G.; Fu, K.; Cai, Y.; Zhang, B.; Chen, K.J. Integration of LPCVD-SiNx gate dielectric with recessed-gate E-mode GaN MIS-FETs: Toward high performance, high stability and long TDDB lifetime. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 260–263. [Google Scholar]

- Nishio, K.; Yayama, T.; Miyazaki, T.; Taoka, N.; Shimizu, M. Ultrathin silicon oxynitride layer on GaN for dangling-bond-free GaN/insulator interface. Sci. Rep. 2018, 8, 1391. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Long, R.D.; McIntyre, P.C. Surface Preparation and Deposited Gate Oxides for Gallium Nitride Based Metal Oxide Semiconductor Devices. Materials 2012, 5, 1297–1335. [Google Scholar] [CrossRef]

- Cheng, K.-Y.; Wu, S.-C.; Yu, C.-J.; Wang, T.-W.; Liao, J.-H.; Wu, M.-C. Comparative study on performance of AlGaN/GaN MS-HEMTs with SiNx, SiOx, and SiNO surface passivation. Solid-State Electron. 2020, 170, 107824. [Google Scholar] [CrossRef]

- Geng, K.; Chen, D.; Zhou, Q.; Wang, H. AlGaN/GaN MIS-HEMT with PECVD SiNx, SiON, SiO2 as Gate Dielectric and Passivation Layer. Electronics 2018, 7, 416. [Google Scholar] [CrossRef] [Green Version]

- Zhang, Z.; Song, L.; Li, W.; Fu, K.; Yu, G.; Zhang, X.; Fan, Y.; Deng, X.; Li, S.; Sun, S.; et al. Mechanism of leakage of ion-implantation isolated AlGaN/GaN MIS-high electron mobility transistors on Si substrate. Solid-State Electron. 2017, 134, 39–45. [Google Scholar] [CrossRef]

- Yamada, T.; Watanabe, K.; Nozaki, M.; Shih, H.-A.; Nakazawa, S.; Anda, Y.; Ueda, T.; Yoshigoe, A.; Hosoi, T.; Shimura, T.; et al. Physical and electrical characterizations of AlGaN/GaN MOS gate stacks with AlGaN surface oxidation treatment. Jpn. J. Appl. Phys. 2018, 57, 06KA07. [Google Scholar] [CrossRef] [Green Version]

- Yamada, H.; Yamada, T. A semiconductor physics based model for thermal characteristics in electronic electrolytic energy storage devices. J. Appl. Phys. 2021, 129, 174501. [Google Scholar] [CrossRef]

- Yamada, T.; Devine, E.P.; Ghandiparsi, S.; Bartolo-Perez, C.; Mayet, A.S.; Cansizoglu, H.; Gao, Y.; Ahamed, A.; Wang, S.-Y.; Islam, M.S. Modeling of nanohole silicon pin/nip photodetectors: Steady state and transient characteristics. Nanotechnology 2021, 32, 365201. [Google Scholar] [CrossRef]

- Yang, S.; Liu, S.; Lu, Y.; Liu, C.; Chen, K.J. AC-capacitance techniques for interface trap analysis in GaN-based buried-channel MIS-HEMTs. IEEE Trans. Electron Devices 2015, 62, 1870–1878. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, X.; Wei, X.; Zhang, P.; Zhang, H.; Zhang, L.; Deng, X.; Fan, Y.; Yu, G.; Dong, Z.; Fu, H.; et al. Low Threshold Voltage Shift in AlGaN/GaN MIS-HEMTs on Si Substrate Using SiNx/SiON as Composite Gate Dielectric. Electronics 2022, 11, 895. https://doi.org/10.3390/electronics11060895

Zhang X, Wei X, Zhang P, Zhang H, Zhang L, Deng X, Fan Y, Yu G, Dong Z, Fu H, et al. Low Threshold Voltage Shift in AlGaN/GaN MIS-HEMTs on Si Substrate Using SiNx/SiON as Composite Gate Dielectric. Electronics. 2022; 11(6):895. https://doi.org/10.3390/electronics11060895

Chicago/Turabian StyleZhang, Xiaodong, Xing Wei, Peipei Zhang, Hui Zhang, Li Zhang, Xuguang Deng, Yaming Fan, Guohao Yu, Zhihua Dong, Houqiang Fu, and et al. 2022. "Low Threshold Voltage Shift in AlGaN/GaN MIS-HEMTs on Si Substrate Using SiNx/SiON as Composite Gate Dielectric" Electronics 11, no. 6: 895. https://doi.org/10.3390/electronics11060895

APA StyleZhang, X., Wei, X., Zhang, P., Zhang, H., Zhang, L., Deng, X., Fan, Y., Yu, G., Dong, Z., Fu, H., Cai, Y., Fu, K., & Zhang, B. (2022). Low Threshold Voltage Shift in AlGaN/GaN MIS-HEMTs on Si Substrate Using SiNx/SiON as Composite Gate Dielectric. Electronics, 11(6), 895. https://doi.org/10.3390/electronics11060895