1. Introduction

In many modern integrated circuit applications, better speed and lower power consumption are important criteria. Because of the reducing device sizes and low voltage supply, these criteria are met utilizing cutting-edge complementary metal-oxide-semiconductor (CMOS) technologies. Unfortunately, due to smaller device sizes and low power supply, many prior analog circuit architectures, such as analog-to-digital converters, are more difficult to overcome the lower voltage headroom and the lower dynamic range

The time-domain technique is a relatively recent method of processing time that utilizes time delay, time difference or pulse width rather than voltage or current, as in traditional processing methods. As a result, in time-domain circuits and systems, time is the quantity of interest [

1,

2,

3]. Even for such a scaled technology, time-domain design is a very promising design method since it offers a better trade-off between dynamic range and power consumption. The advantage of time-domain systems is that they use high-speed MOS devices, which means they have a shorter time delay and so process time with more precision [

4,

5,

6].

The main advantages of the time-domain design approach are improved dynamic range and time resolution when compared to analog voltage or current mode circuits under the same low-supply environment [

4,

5,

6] and better power efficiency for high-speed performance because they are primarily composed of CMOS digital building blocks (gates, etc.) [

1].

Signal filtering is one of the most important functions in many state-of-the-art applications, such as biomedical sensor interfacing, image processing, wireless receivers, etc. Signal filtering, which is based on finite/infinite impulse response filter implementation (FIR/IIR), belongs among the basic signal processing operations in traditional discrete-time digital signal processing (DT-DSP).

FIR/IIR implementations require some fundamental operators, such as z−1 operators and signal adders, along with signal multipliers, for the implementations of the filter coefficients. Traditional FIR/IIR implementations are mainly based on pure digital design approach and, therefore, can be categorized as discrete-time/discrete-signal processing systems. The circuit realization of the basic operators is achieved using flip-flops as delay element and digital logic gates for the implementation of the digital logic adders and multipliers.

The FIR/IIR counterpart implementations in time-mode require the basic operators to work in time domain which means that

z−1, adders [

4,

7,

8] and multipliers [

9,

10] must be able to handle time-mode quantities [

11]. These systems are categorized as discrete-time/continuous signal processing (DT-CSP) systems [

12].

Few works about time-mode FIR/IIR or other time-mode filter implementations have been reported in the literature. A 2nd-order Butterworth and Chebyshev Type I time-mode filters have been presented in [

13]. These implementations are based on time-mode signal processing circuits, which, unfortunately, cannot be used as separate modules leading to complicate configurations. A set of time-mode building blocks used to build a sampled-data 2nd-order low-pass IIR filter along with the methodology for the construction of higher-order systems are presented in [

14]. A 3-tap FIR filter and a new way of analog computation using novel time-mode operator circuitries are presented in [

12].

Our work proposes the implementation of a 3rd order sampled-data low pass time-mode FIR filter which is based on the novel time-mode multiplier and time-mode adder. Both circuits are based on the modification of a simple time register topology [

15,

16]. A 3rd order low-pass topology offers a satisfactory trade off between high-frequency rejection, chip area and current consumption. The proposed time-mode operators feature several advantages leading to robust FIR filter implementation: (a) low circuit complexity including few transistors, (b) high accuracy in time storing (c) synchronization with the reference sampling clock and (d) modular design. The main advantage of the proposed time-mode FIR compared with aforementioned state-of-the-art works is that it can be easily realized based on the topological diagram of the traditional FIR approach in voltage mode and substituting one-by-one the voltage-mode operators with the time-mode counterpart modular operators.

The paper is organized as follows. A brief presentation about time-mode signal processing and the definition of the time-mode operators presented in

Section 2. The circuit modifications of the time register in order to build the multiplier and adder operators are described in

Section 3. In

Section 4, the proposed time-mode modules are presented and analyzed, while the FIR filter is analyzed in

Section 5. The simulation results are reported in

Section 6.

2. Time-Mode Signal Processing

The time-mode circuits and systems process the time difference between two consecutives pulses or the time width of a constant frequency pulse. This work will focus on the time processing approach that handles the pulse width of a constant frequency pulse. In

Figure 1, a conceptual block diagram is presented.

The input signal

Vin is converted to time-mode by using a sample/hold stage (S/H) and pulse width modulator (PWM). S/H is necessary for high-frequency input bandwidth and can be omitted for low-frequency input signals (e.g., signal which comes from sensor interfacing circuit). Based on the PWM technique, input voltage

Vin will correspond to an input pulse width

Tin of a constant frequency pulse [

2,

17] according to the next equation:

where

kVT is the voltage-to-time conversion factor, and

n is the number of sample, while the constant frequency is assumed the sampling frequency

fsampling. It is clear that

Tin can take continuous values according to Equation (1), but the time is discrete by mean of sampling time, and the corresponding system is considered a DT-CSP system [

12]. Afterward, the signal is processed by the main time-mode systems, which is capable of handling the pulse widths of a pulse train.

One of the major building blocks embedded in continuous or discrete signal processing is the filters: analog filters or FIR/IIR filters. Despite implementation, filters must be capable of filtering out all the unwanted signals/components, which are corrupted with the signal or bandwidth of interest. From the time-mode point of view, any filter implementation is similar to FIR/IIR discrete filters mainly due the use of discrete sampling time.

This study will concentrate on the implementation of time-domain FIR filters. A FIR filter is a signal processing filter whose impulse response (or response to any finite length input) has a limited duration since it settles to zero in a finite time. Each value in the output sequence for a causal discrete-time time-mode FIR filter of order

N is a weighted sum of the most recent input values [

18]:

where

Tin[n] is the input pulse width;

Tout[n] is the output pulse width;

N is the filter order;

bi is the filter’s coefficient at the i-th instant for 0 ≤ i ≤ N of an Nth-order FIR filter.

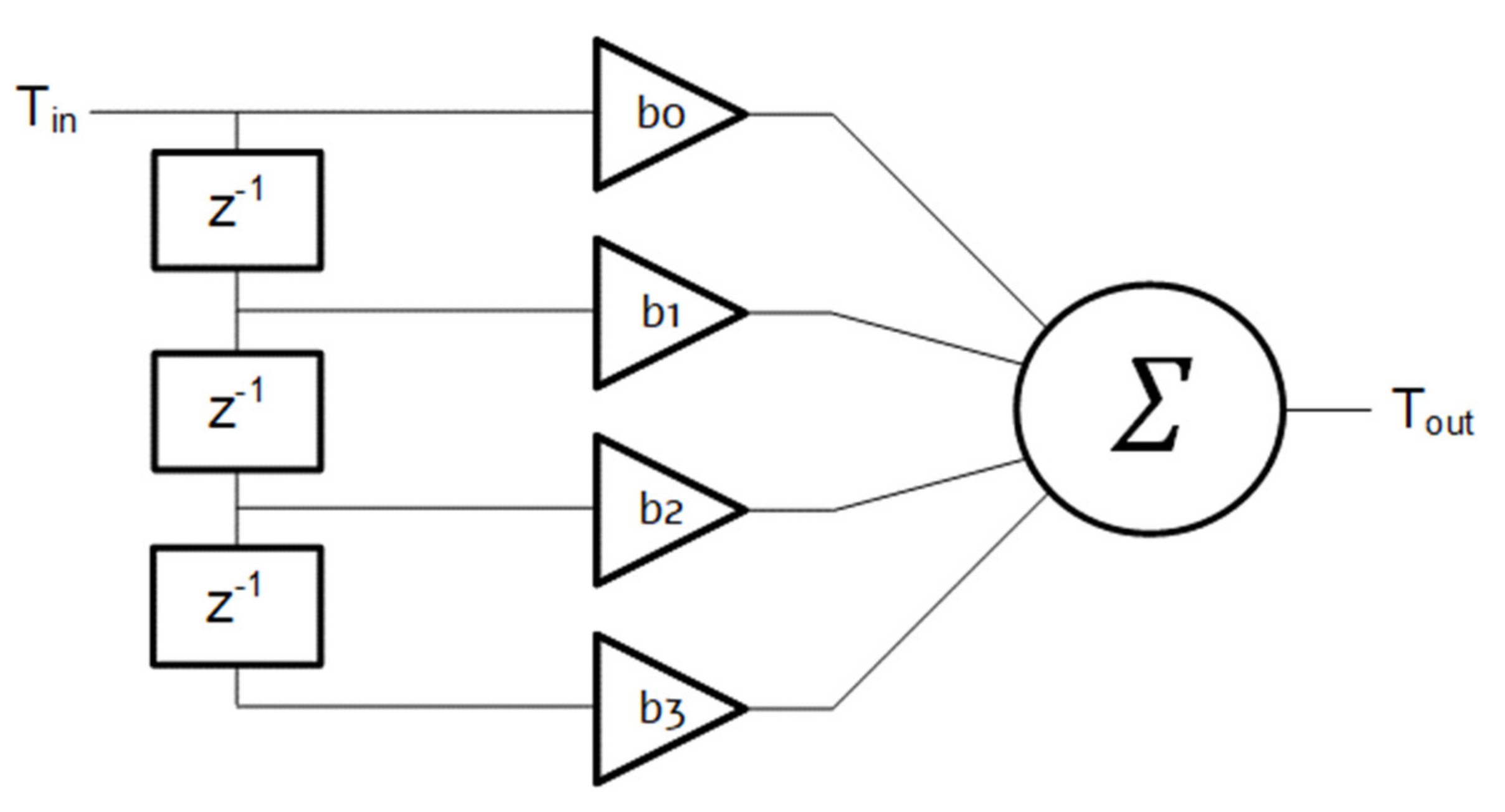

Therefore, the most important operators in the corresponding time-mode FIR filters will be the time-mode

z−1 operators, time-mode multiplier and the time-mode adders. The block diagram of these operators in the time-mode are presented in

Figure 2. The circuit implementations of the aforementioned operators will be described in the next sections.

3. Multiplying and Adding Operations of the Time Register

Figure 3a shows the time register (TR), and

Figure 3b shows its symbol. When

SET = 0, transistor M

1 is turned on, and the capacitor voltage is set to

VDD (supply voltage). Τhe capacitor discharges when transistor M

2 is ON, which is controlled by the OR gate. Through a digital calibration loop, the M

3′s gate voltage

CTRL may be utilized to calibrate the variance of the discharging slope [

16]. To synchronize the output with

CLK, the synchronization circuitry consists of an AND gate, a fast comparator [

16] and an inverter. The comparator is designed to provide quick transient response, and its triple point voltage

Vtp is set to match

VDD/2 [

16].

Figure 3c shows a time diagram of a time register that describes the synchronization procedure. The

SET signal’s time interval

TCLK is a pulse with a fixed pulse width and a 25% duty cycle. The capacitor voltage remained constant when both

IN and

CLK are 0. The larger the pulse width

Tin of the

IN signal, the more discharging time due to

Tin appeared, considering that the discharging time due to

CLK stays the same.

The output is a pulse with width equal to TCLK − Tin, allowing the value of Tin to be stored, while the output pulse is synchronized with the CLK signal.

Using the aforementioned time register circuit, the circuit can store the time interval of an input pulse and amplify the pulse width by a gain factor. The new circuit is called time amplifier and is presented in

Figure 4. In this configuration, the operation of the OR gate is performed by the two-transistor branches

Ma1–

Mb1 and

Ma2–

Mb2. Transistors M

a1 and

Ma2 have the same aspect ratio acting as switches. The aspect ratios of

Mb1,

Mb2 are different, featuring a different discharging slope. Assuming that the channel widths of

Mb2 and

Mb1 are

Wb.2 and

Wb.1, respectively, while both transistors have the same channel length. Then, intuitively, using

Figure 3c, the discharging slope between

Tin and

TCLK will be different. The discharging

slopein that corresponds to

Tin will be given by

where

a is the time gain and is given by

and

slopeclk is the discharging reference slope caused by

TCLK. Therefore, the output pulse width will be equal to

A time adder circuit, which is based on the time register, is presented in

Figure 5. A time adder simply adds the pulse widths

Tin.1,

Tin.2, …,

Tin.n of

n number input pulses. Transistors

Mb.1,

Mb.2 …,

Mb.n,

Mb.n+1 have the same aspect ratio. Therefore, the discharging slope caused by

Tin.1,

Tin.2, …,

Tin.n will be given by

and the output pulse width will be

The main problem of the time register is the strong impact of the technology process (P) variations and chip temperature (T) variation (PT variations). The discharging slope of the capacitor voltage discharging shows variation over PT variations because of its dependency by the discharging drain current of a MOS device and the value on-chip capacitor. A digital calibration loop can be used in order to calibrate the discharging slope achieving better performance stability [

16].

6. Results

In the following section, the performance of the proposed circuits is presented. All circuits are designed and verified by simulation in Samsung 28 nm FD-SOI CMOS technology with a supply voltage V

DD = 1 V. The voltage triple point of comparator was adjusted to be 0.5 V using an appropriate triple-point compensation circuitry [

15]. Considering that the input pulse width

Tin is varied as a sinusoid, the maximum allowable peak-to-peak amplitude

Tin.pp.aval can theoretically be equal to

TCLK, which is equal to 50 ns in our implementation. As long as

Tin.pp is close to

TCLK then shorter pulses are generated inside

z−1 circuit increasing the signal distortion. Therefore, a maximum peak-to-peak input amplitude

Tin.pp.max of 40 ns is satisfactory, covering 80% of the maximum available range of 50 ns.

6.1. Time-Mode z−1 Multiplier

The operation of the

z−1 multiplier is shown in

Figure 10. Timing waveforms for a

z−1 multiplier for a multiplying coefficient are equal to 0.28, (a) synchronization clock, (b) input pulses width with

Tin = 20 ns and (c) output pulses with pulse width

Tout = 5.55 ns. In

Figure 10a, the synchronization clock is presented. In

Figure 10b,c, the input and output pulses are presented, respectively. The input pulse width

Tin is 20 ns, while the multiplier coefficient is chosen to be equal to 0.28. As a result, the circuit generates output pulses with a pulse width of

Tout = 5.55 ns, as expected. In

Figure 11, two cases of multiplication coefficient, with nominal values of 0.28 and 0.21, are presented in relation to the input pulse width. In the worst-case scenario of

Tin.pp = 40 ns, the relative inaccuracy of the multiplication coefficient is less than 5%.

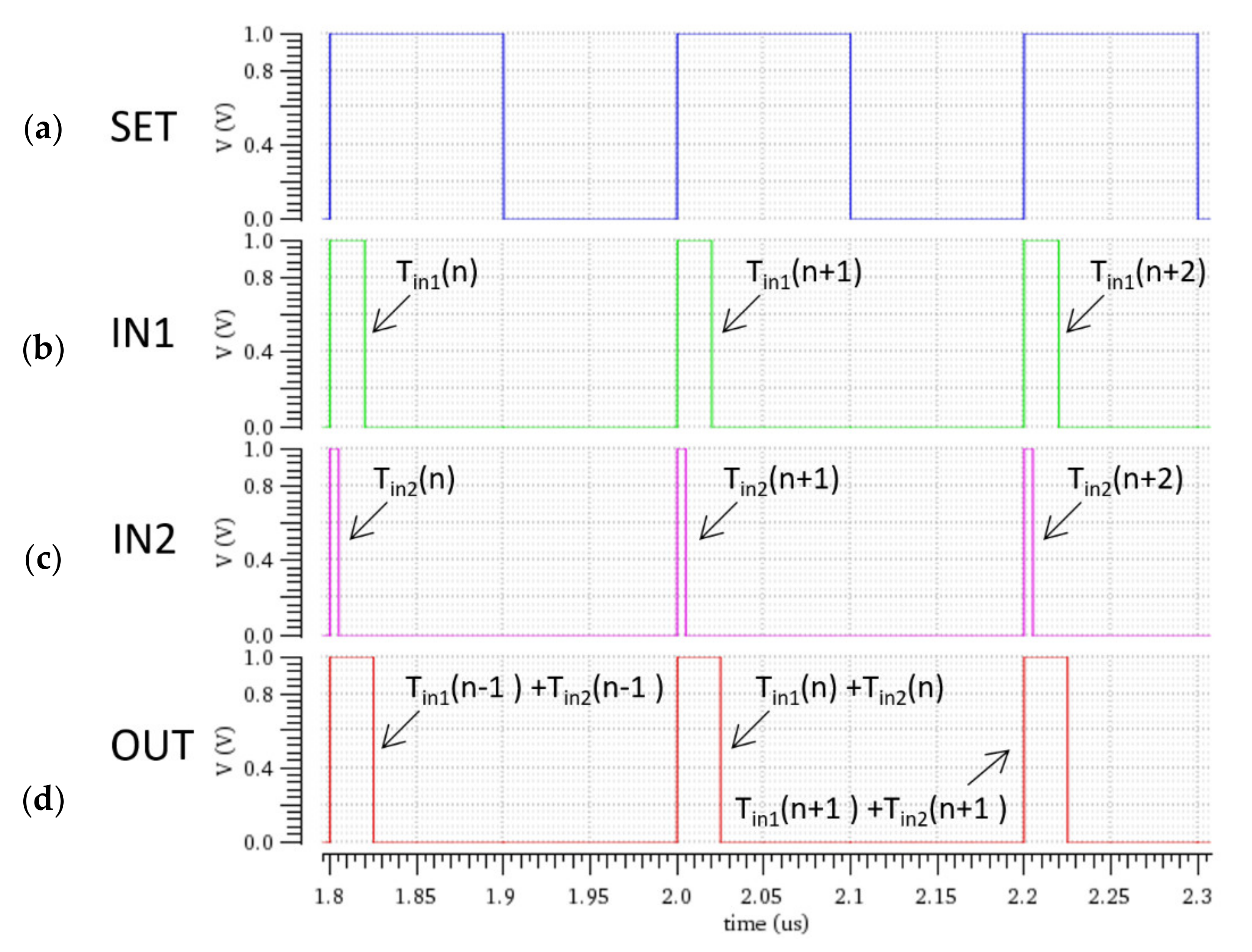

6.2. Time-Mode z−1 Adder

Figure 12 depicts the operation of a 2-input

z−1 adder. The input pulse widths are 20 ns and 5 ns, respectively. The adder generates output pulses with pulse width

Tout, which is the sum of the two preceding and equal to 25.08 ns.

Figure 13 demonstrates the output pulse width of the Adder using a stable

Tin1 at 5 ns at one input, while at the second input

Tin2 ranges between 0 ns and 40 ns. It is obvious that the proposed adder can add linearly all values of the dynamic range of 40 ns.

6.3. Time-Mode FIR Filter

The simulated magnitude response of the ideal and the implemented time-mode 3rd-order FIR filter is presented in

Figure 14. The sampling frequency was 5 MHz. The average power consumption is 200 μA, which includes the consumption of both actual filter circuit and digital calibration. The approximated filter coefficient values are presented in

Table 1. The notch frequency of the ideal filter is selected to be around 1.31 MHz, which is close to the 1.38 MHz notch frequency of the implemented FIR filter. There is a frequency shift of 70 KHz. These frequency response discrepancies can be mainly attributed to the approximation error of the filter coefficients.

The SNDR simulated results versus

Tin.peak are reported in

Figure 15, where

Tin.peak is the amplitude of a sinusoidal signal of 50 kHz. The SNDR peak is at around 38.6 dB.

The maximum input

Tin is defined by the upper limit of the input signal of the

z−1 structure, which is a bit less than 50 ns. The lower limit is mainly limited by the noise contribution of the MOS devices, which appeared as clock jitter, charge injection and leakage. Based on

Figure 15, the noise level is around 10 ps.

Table 2 compares the proposed filter implementation to the state-of-the-art time-mode filters. Our implementation operates under the lowest power supply; it has relatively low power consumption for a 3rd order filter topology also using the highest sampling frequency.