A Dual-Mode Control Scheme to Improve Light Load Efficiency for Active-Clamp Flyback Converter

Abstract

:1. Introduction

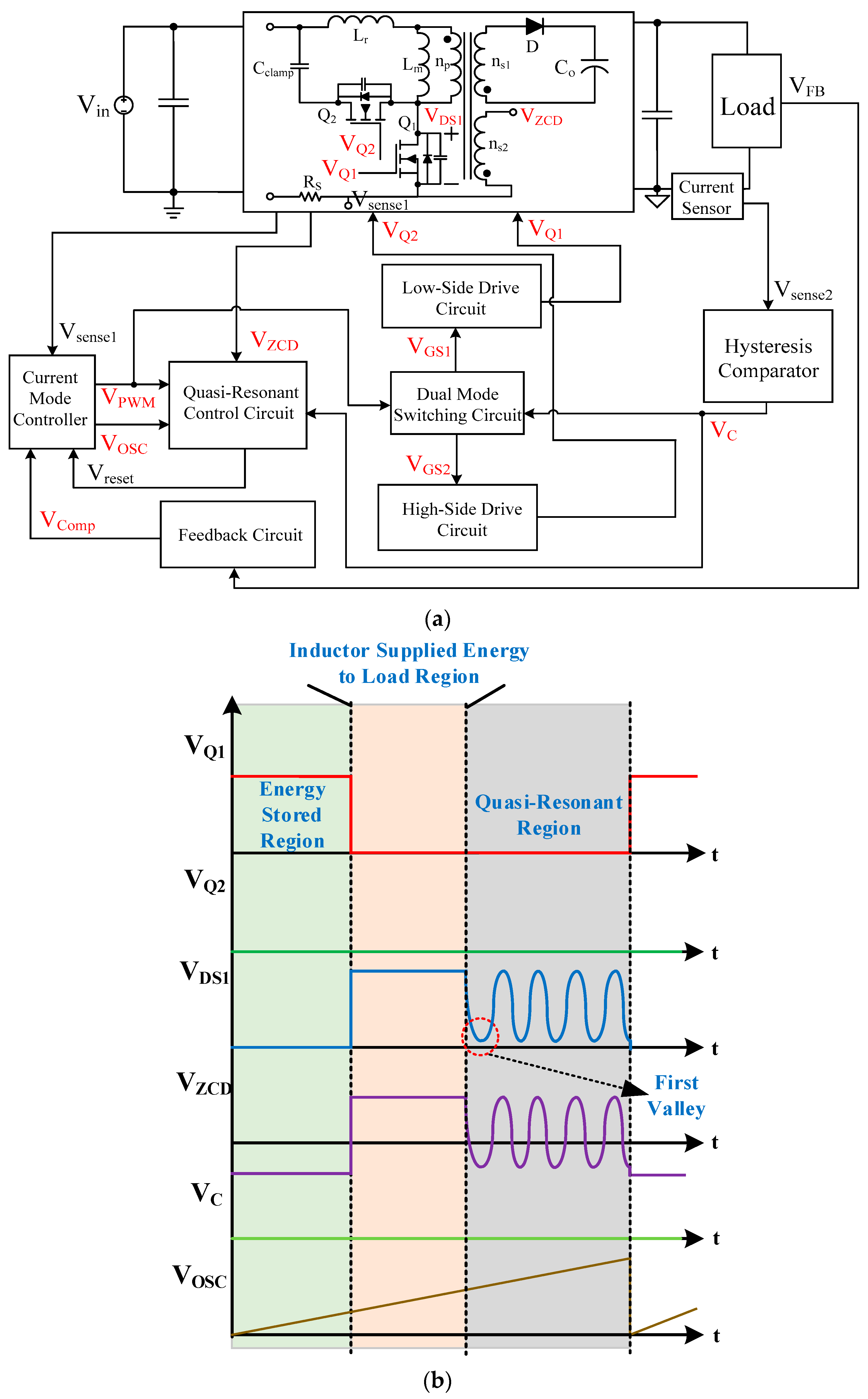

2. Proposed Novel Dual-Mode ACF Converter Structure

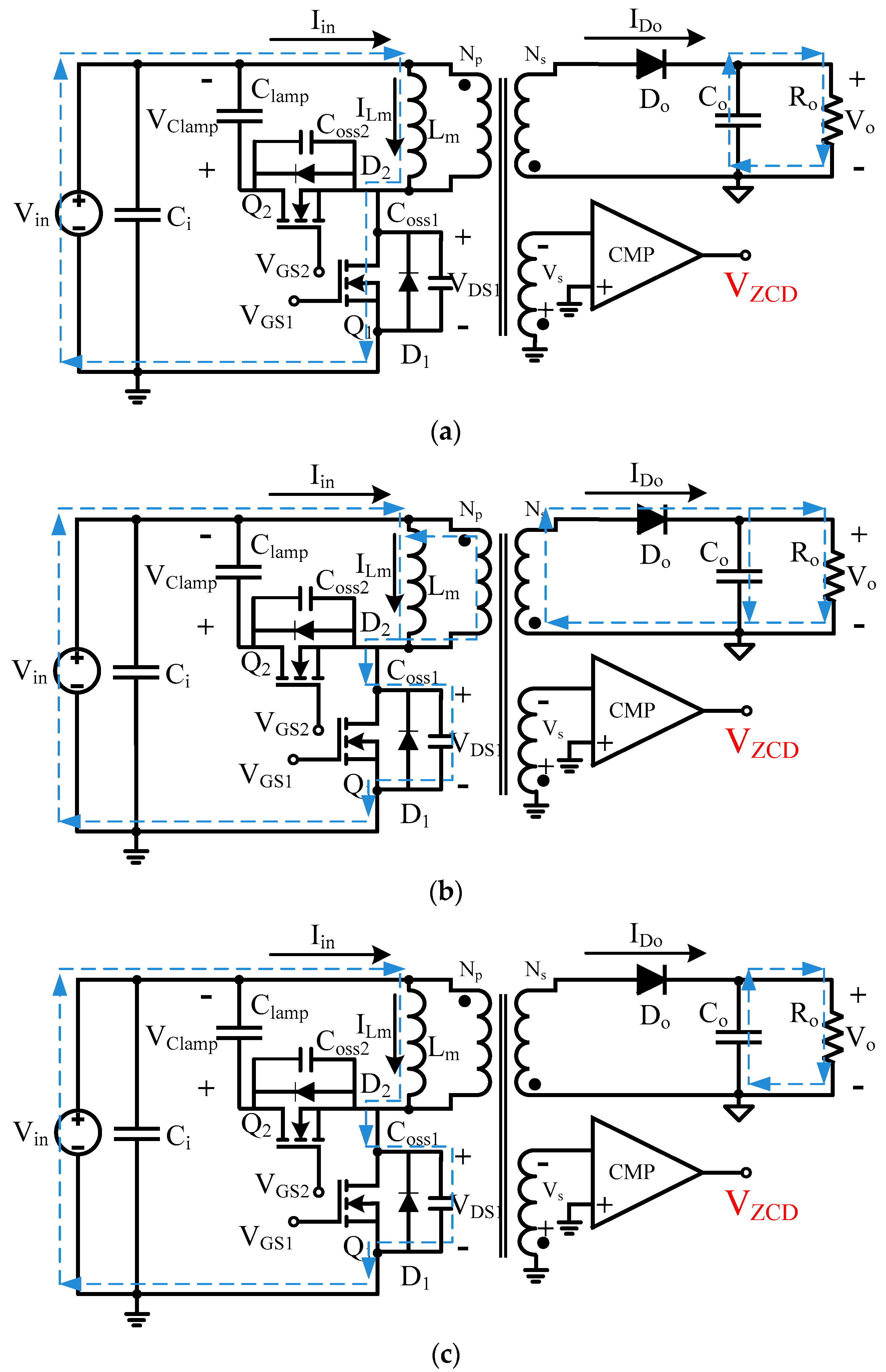

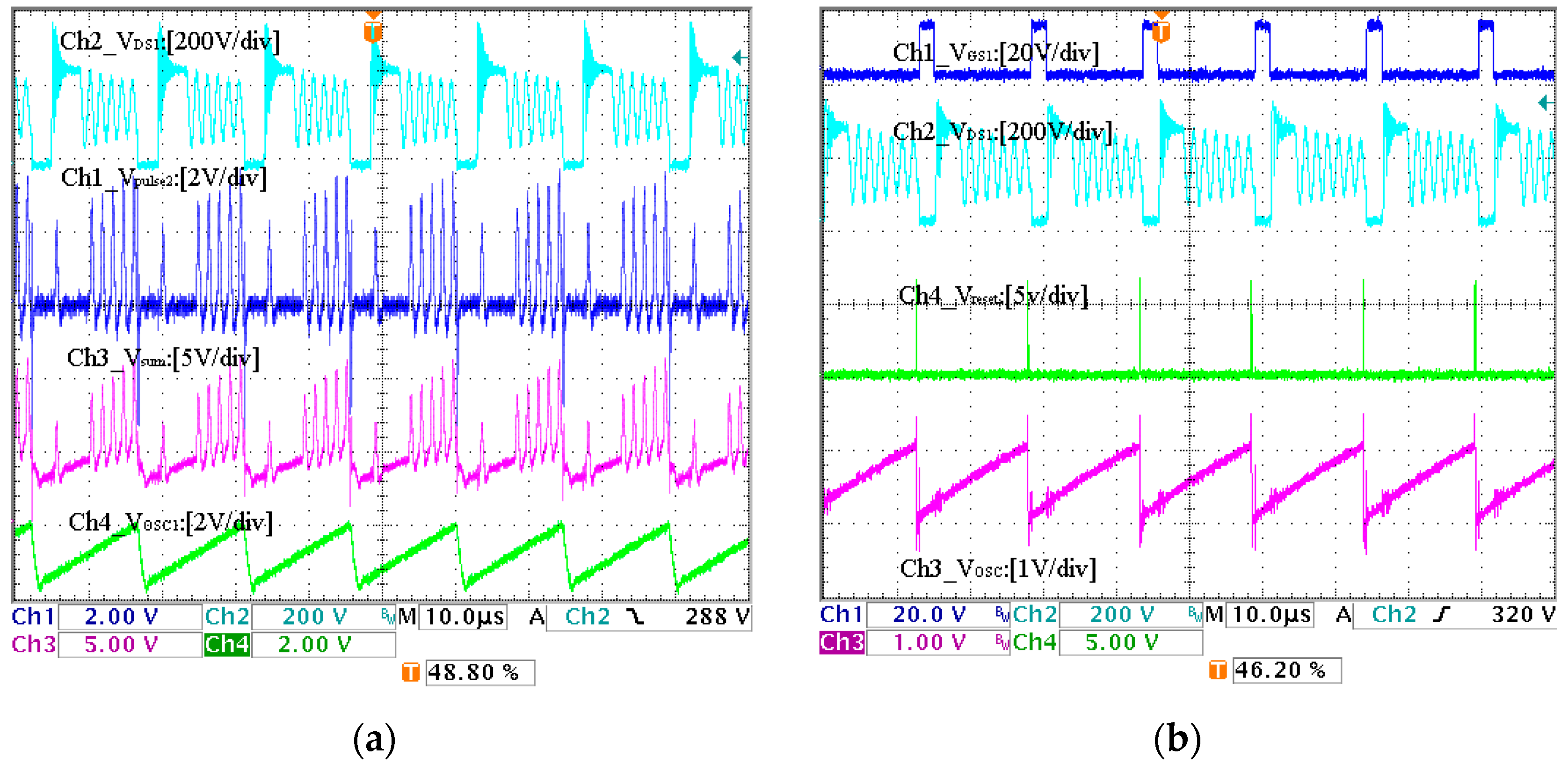

2.1. The Proposed Circuit Structure and Principle of Operation

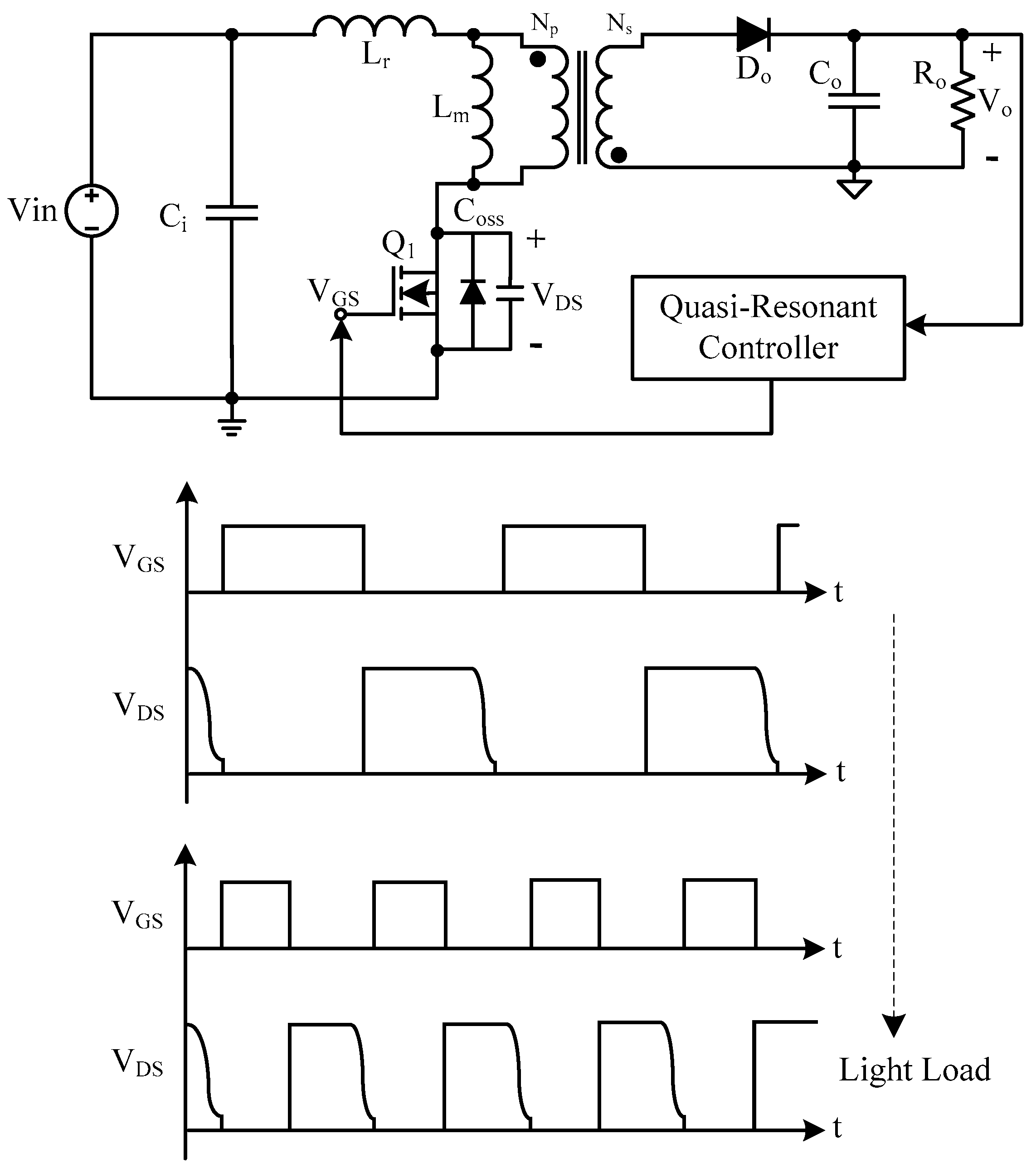

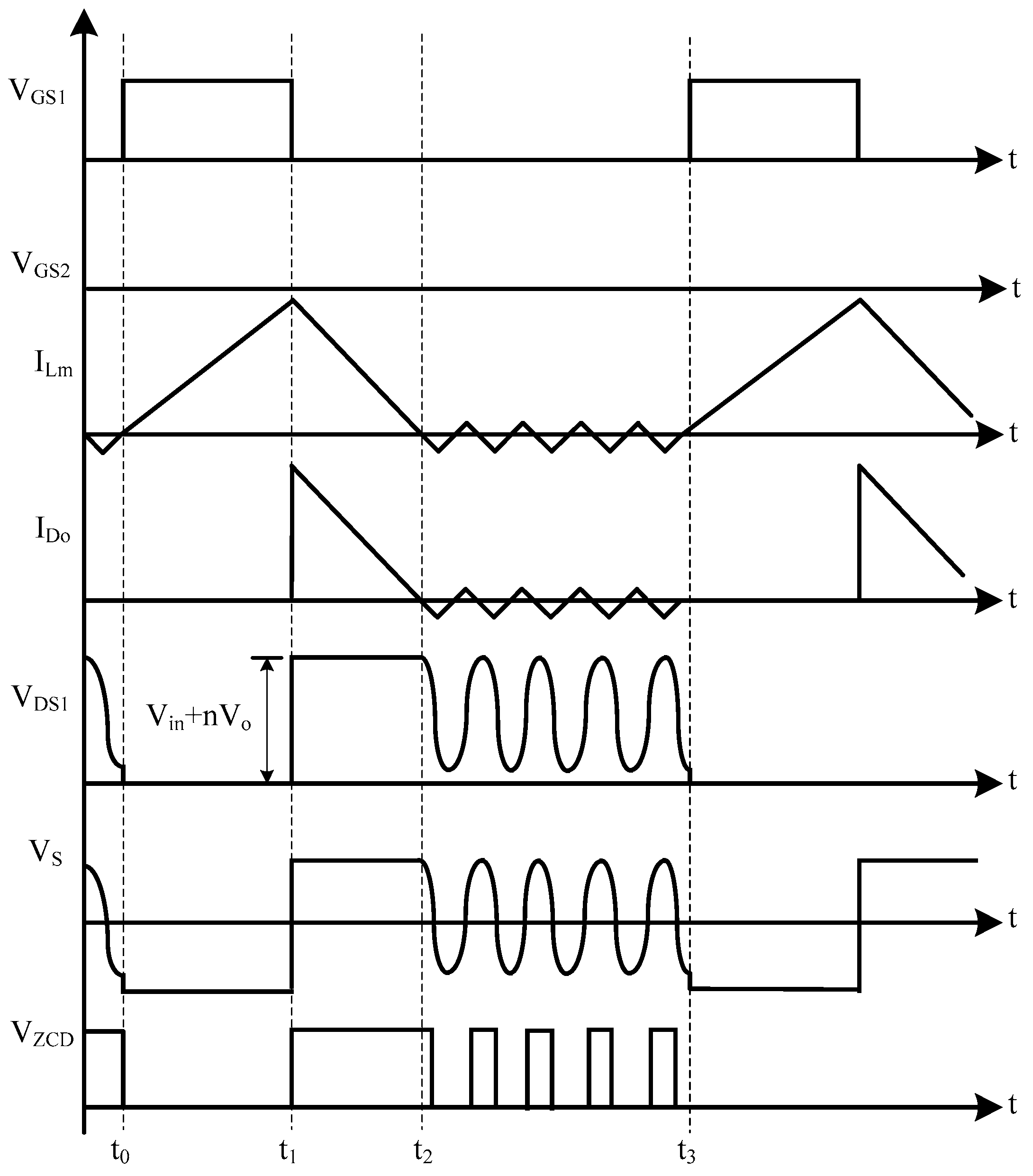

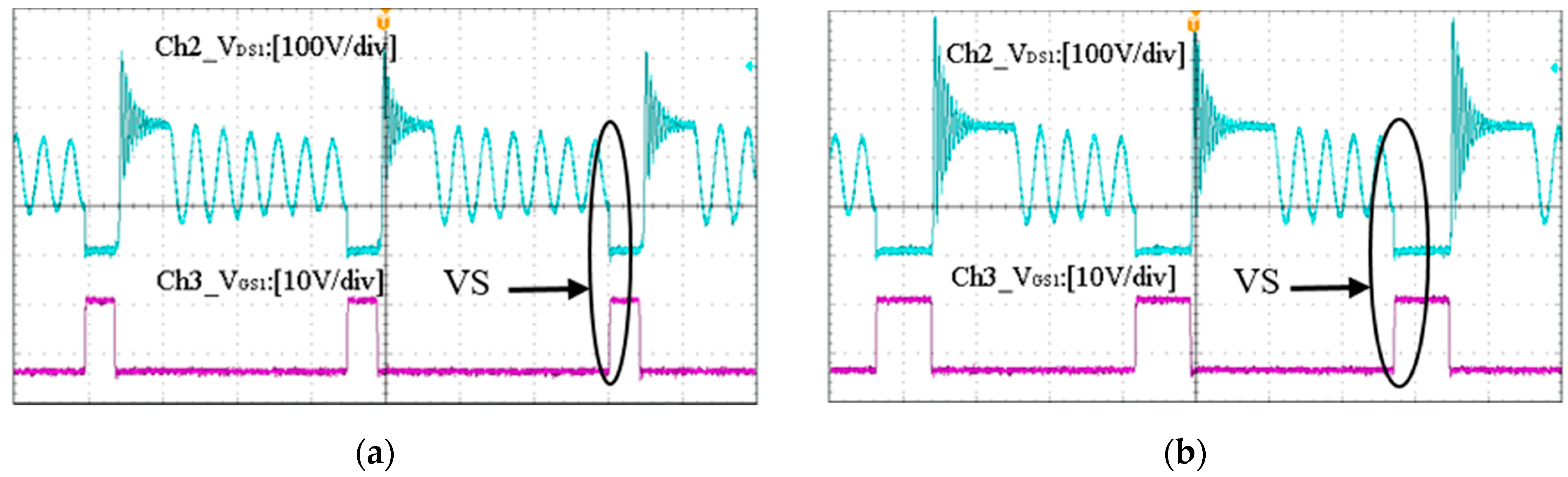

2.1.1. Light Load

2.1.2. Heavy Load

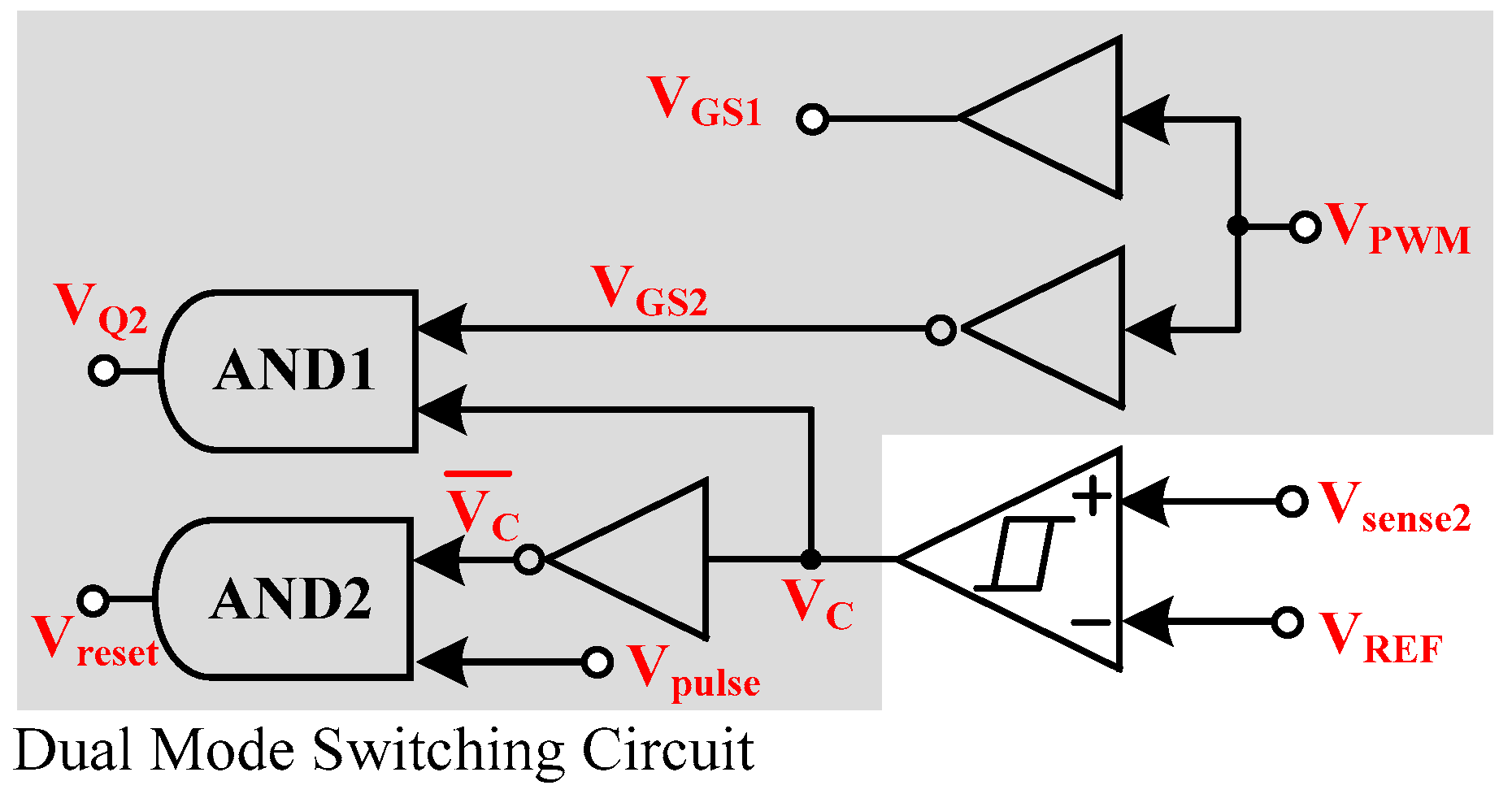

2.2. The Control Circuit of the Proposed Novel Dual-Mode ACF Converter

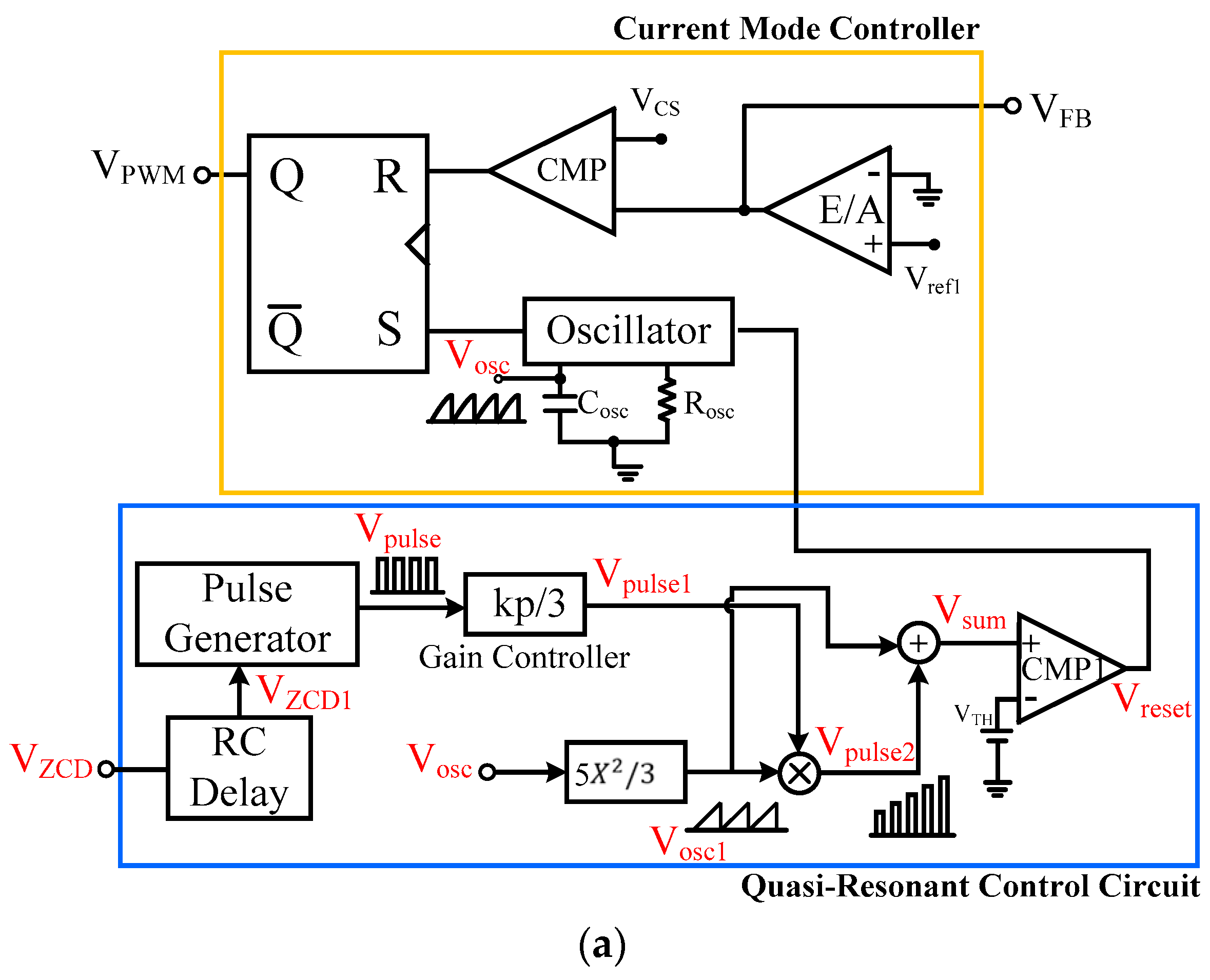

2.2.1. Dual-Mode Switching Circuit

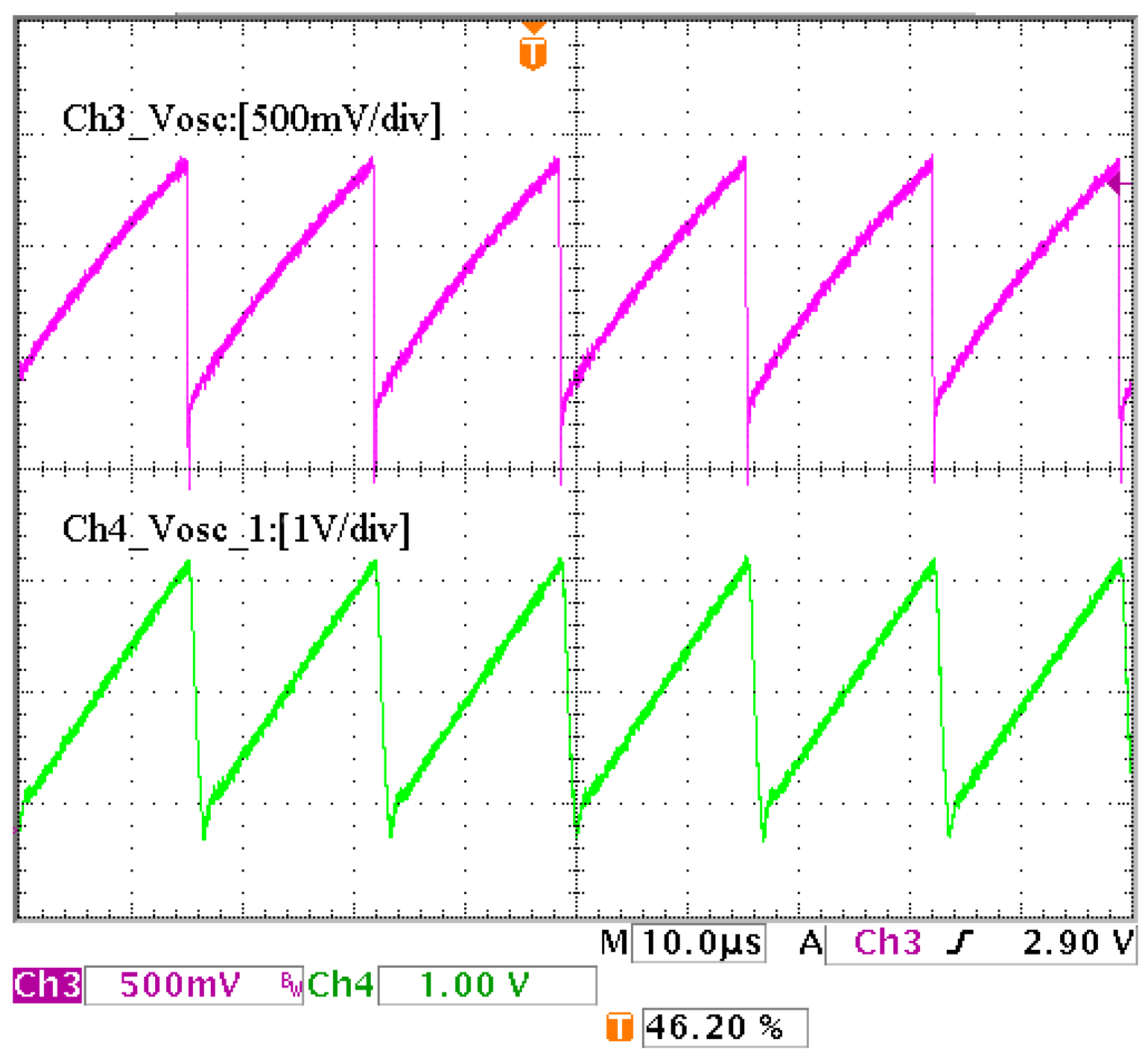

2.2.2. Proposed QR Control Circuit

- The operating principle of the ACF converter operating in the QR mode:

- The main switch (Q1) and the auxiliary switch (Q2) have no leakage current and forward resistance;

- The leakage inductance (Lr) is negligible;

- The parasitic capacitances, Coss1 and Coss2, are much smaller than Cclamp;

- Non-ideal characteristics, such as the forward voltage drop and the resistance effect of the secondary-side rectifier diode, are ignored;

- The output capacitance is large enough to be considered as a constant voltage source;

- The turn ratio n = Np/Ns.

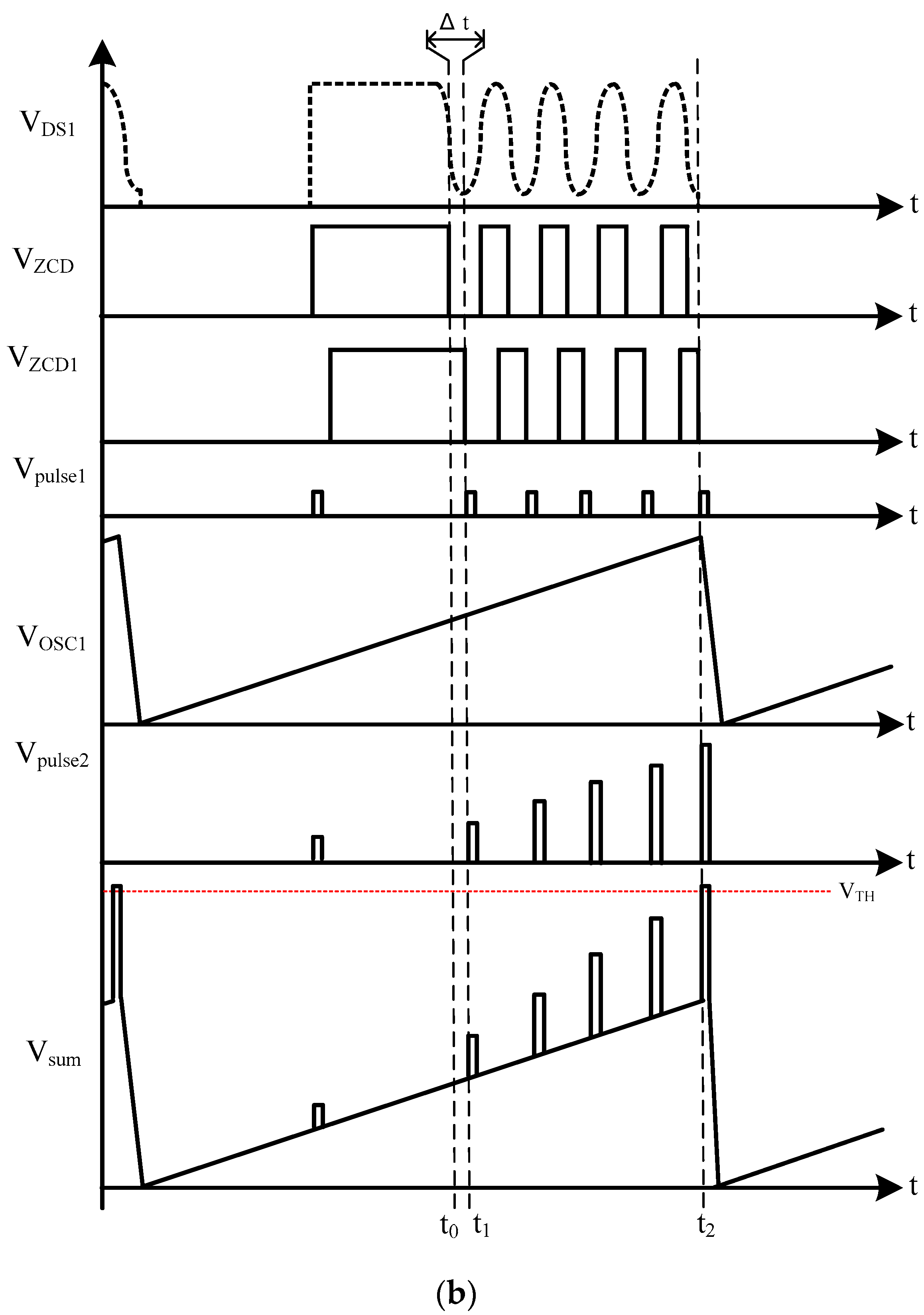

- The operating principle of the QR control circuit with the maximum switching frequency-limiting function:

3. Design of the Proposed Novel Dual-Mode ACF Converter

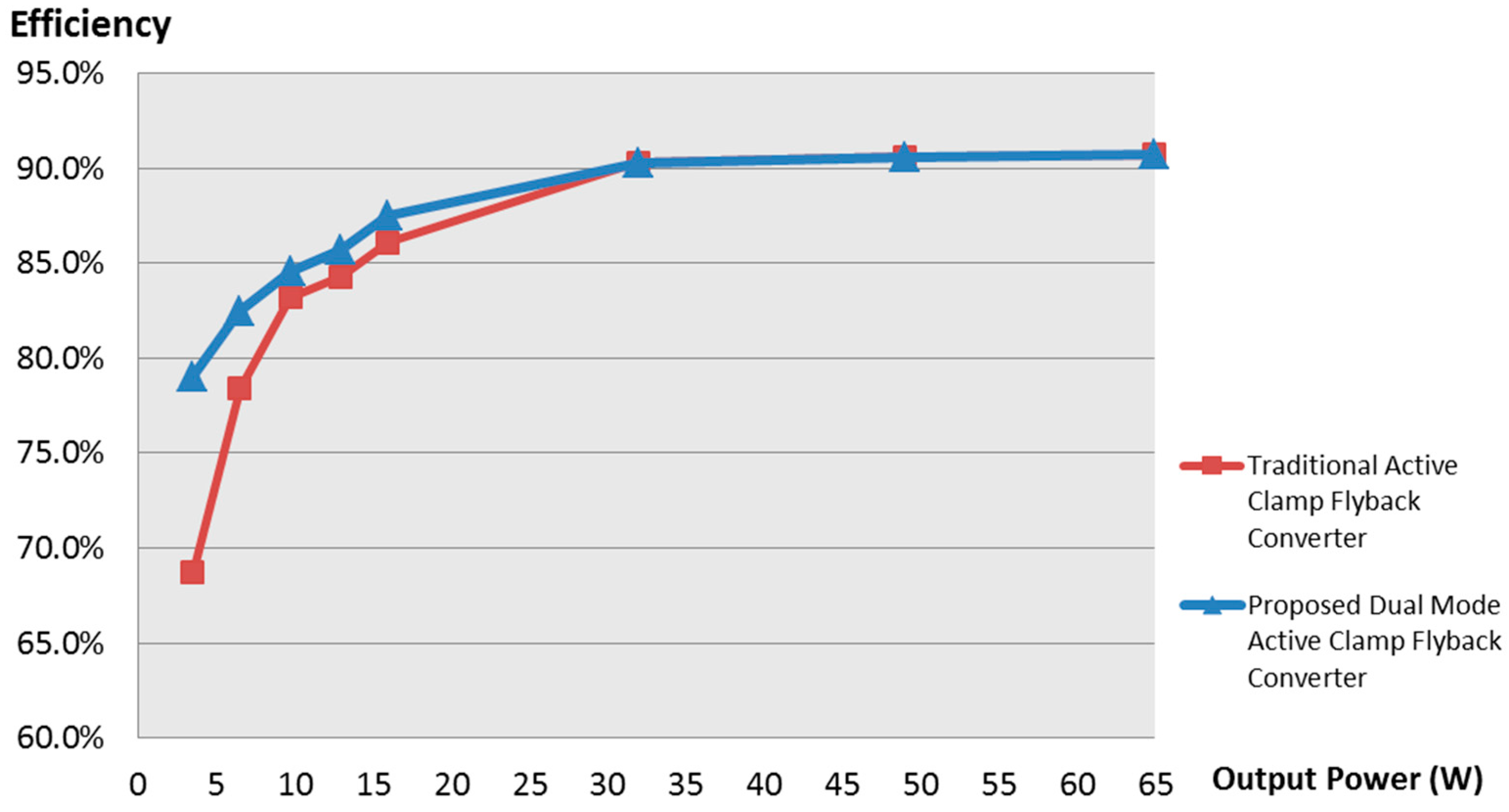

4. Experimental Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Watson, R.; Hua, G.C.; Lee, F.C. Characterization of an active clamp flyback topology for power factor correction applications. IEEE Trans. Power Electron. 1996, 11, 191–198. [Google Scholar] [CrossRef]

- Watson, R.; Lee, F.C.; Hua, G.C. Utilization of an active-clamp circuit to achieve soft switching in flyback converters. IEEE Trans. Power Electron. 1996, 11, 162–169. [Google Scholar] [CrossRef]

- Papanikolaou, N.P.; Tatakis, E.C. Active voltage clamp in flyback converters operating in CCM mode under wide load variation. IEEE Trans. Power Electron. 2004, 51, 632–640. [Google Scholar] [CrossRef]

- Liu, P.-H. Design consideration of active clamp flyback converter with highly nonlinear junction capacitance. In Proceedings of the 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 4–8 March 2018; pp. 783–790. [Google Scholar]

- Wu, S.-T.; Cheng, Y.-T. Design and Implementation of a Single-Stage PFC Active-Clamp Flyback Converter with Dual Transformers. Electronics 2021, 10, 2588. [Google Scholar] [CrossRef]

- Leng, C.-M.; Chiu, H.J. Three-Output Flyback Converter with Synchronous Rectification for Improving Cross-Regulation and Efficiency. Electronics 2021, 10, 430. [Google Scholar] [CrossRef]

- Medina-Garcia, A.; Schlenk, M.; Morales, D.P.; Rodríguez, N. Resonant Hybrid Flyback, a New Topology for High Density Power Adaptors. Electronics 2018, 7, 363. [Google Scholar] [CrossRef] [Green Version]

- Jung, J.; Ahmed, S. Flyback converter with novel active clamp control and secondary side post regulator for low standby power consumption under high-efficiency operation. IET Power Electron. 2011, 4, 1058–1067. [Google Scholar] [CrossRef]

- Kim, J.h.; Ryu, M.-H.; Min, B.d.; Song, E.-H. A Method to Reduce Power Consumption of Active-Clamped Flyback Converter at No-Load Condition. In Proceedings of the IECON 2006—32nd Annual Conference on IEEE Industrial Electronics, Paris, France, 6–10 November 2006; pp. 2811–2814. [Google Scholar]

- Wang, C.; Xu, S.; Shen, W.D.; Lu, S.L.; Sun, W.F. A Single-Switched High-Switching-Frequency Quasi-Resonant Flyback Converter. IEEE Trans. Power Electron. 2019, 34, 8775–8786. [Google Scholar] [CrossRef]

- Li, J.T.; van Horck, F.B.M.; Daniel, B.J.; Bergveld, H.J. A High-Switching-Frequency Flyback Converter in Resonant Mode. IEEE Trans. Power Electron. 2017, 32, 8582–8592. [Google Scholar] [CrossRef]

- Park, H.P.; Jung, J.H. Design Methodology of Quasi-Resonant Flyback Converter With a Divided Resonant Capacitor. IEEE Trans. Power Electron. 2021, 68, 10796–10805. [Google Scholar] [CrossRef]

- Wang, J.; Lin, C.-W.; Huang, K.-Y.; Wong, J.-S. The Novel Quasi-Resonant Flyback Converter With Autoregulated Structure for Parallel/Serial Input. IEEE Trans. Power Electron. 2020, 67, 992–1004. [Google Scholar] [CrossRef]

- Jeng, S.-L.; Peng, M.T.L.; Hsu, C.Y.; Chieng, W.-H.; Shu, J.P.H. Quasi-resonant flyback DC/DC converter using GaN power transistors. World Electr. Veh. J. 2012, 5, 567–573. [Google Scholar] [CrossRef] [Green Version]

- Pressman, A.I. Switching Power Supply Design; McGraw-Hill: New York, NY, USA, 1998. [Google Scholar]

| Parameters | Value |

|---|---|

| Input voltage, Vin | 155 V |

| Maximum output power, Po,max | 65 W |

| Output voltage, Vout | 19 V |

| Output current, Iout | 3.42 A |

| Switching frequency, Fsw | 65 kHz |

| Maximum duty cycle, Dmax | 0.4 |

| Efficiency, η | 90% |

| Maximum magnetic flux density, Bmax | 2000 G |

| Input Voltage, Vin | Input Current, Iin | Output Voltage, Vo | Output Current, Io | Efficiency, η |

|---|---|---|---|---|

| 155 V | 0.030 A | 19.3 V | 0.19 A | 79% |

| 155 V | 0.052 A | 19.3 V | 0.34 A | 82.5% |

| 155 V | 0.075 A | 19.3 V | 0.51 A | 84.6% |

| 155 V | 0.098 A | 19.3 V | 0.68 A | 85.7% |

| 155 V | 0.119 A | 19.3 V | 0.84 A | 87.5% |

| 155 V | 0.229 A | 19.2 V | 1.67 A | 90.3% |

| 155 V | 0.349 A | 19.2 V | 2.55 A | 90.6% |

| 155 V | 0.464 A | 19.2 V | 3.41 A | 90.7% |

| Output Power, Po | Output Voltage, Vo | Load Regulation, LR |

|---|---|---|

| 3.5 W | 19.289 V | 1.52% |

| 6.5 W | 19.303 V | 1.59% |

| 13.0 W | 19.304 V | 1.60% |

| 19.5 W | 19.305 V | 1.61% |

| 26.0 W | 19.293 V | 1.54% |

| 32.5 W | 19.258 V | 1.36% |

| 39.0 W | 19.236 V | 1.24% |

| 45.5 W | 19.226 V | 1.19% |

| 52.0 W | 19.227 V | 1.19% |

| 58.5 W | 19.222 V | 1.17% |

| 65.0 W | 19.207 V | 1.09% |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tran, T.N.T.; Wang, H.-C.; Wang, J.-M. A Dual-Mode Control Scheme to Improve Light Load Efficiency for Active-Clamp Flyback Converter. Electronics 2022, 11, 1308. https://doi.org/10.3390/electronics11091308

Tran TNT, Wang H-C, Wang J-M. A Dual-Mode Control Scheme to Improve Light Load Efficiency for Active-Clamp Flyback Converter. Electronics. 2022; 11(9):1308. https://doi.org/10.3390/electronics11091308

Chicago/Turabian StyleTran, Thanh Nhat Trung, Hung-Chia Wang, and Jian-Min Wang. 2022. "A Dual-Mode Control Scheme to Improve Light Load Efficiency for Active-Clamp Flyback Converter" Electronics 11, no. 9: 1308. https://doi.org/10.3390/electronics11091308