Fabrication of 30 µm Sn Microbumps by Electroplating and Investigation of IMC Characteristics on Shear Strength

Abstract

1. Introduction

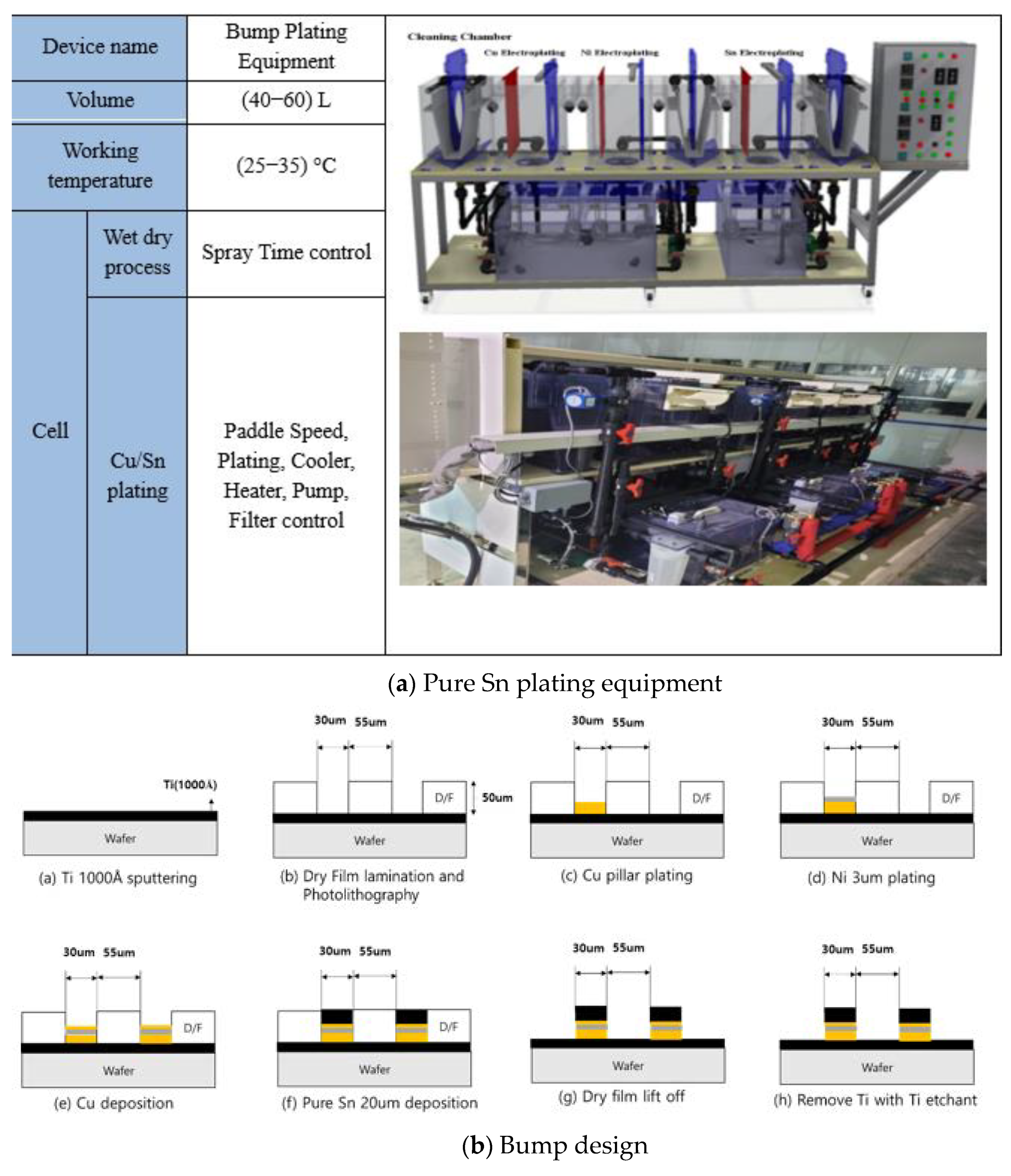

2. Experimental

- 1.

- Observation of changes in bump depending on Sn electroplating equipment and process conditions:

- (a)

- Sn micro bump plating equipment and evaluation

- (b)

- Observation of Changes in Pure Sn Concentration

- (c)

- Observation of Sn bump Changes in Additive

- (d)

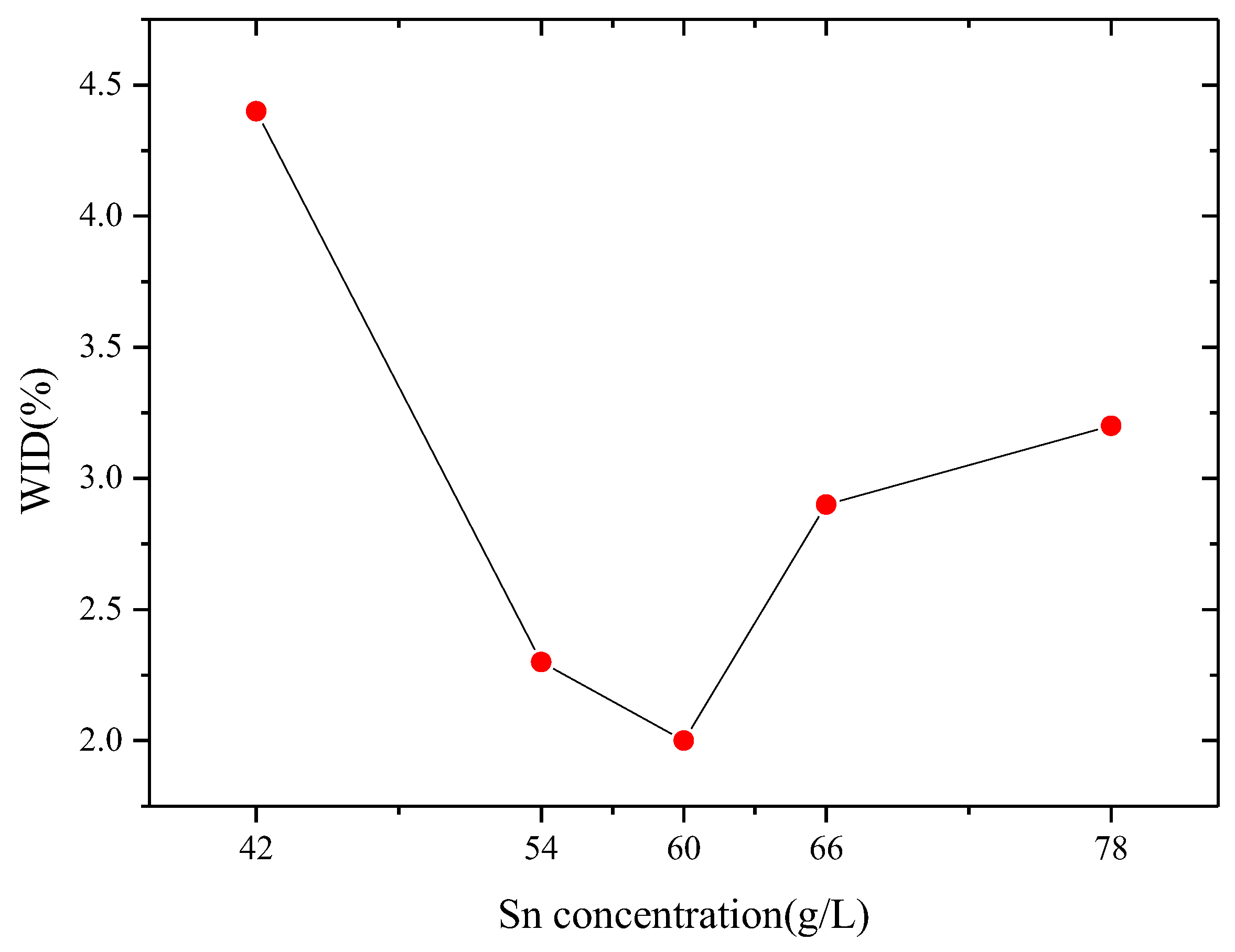

- Observation of changes in plating process temperature

- (e)

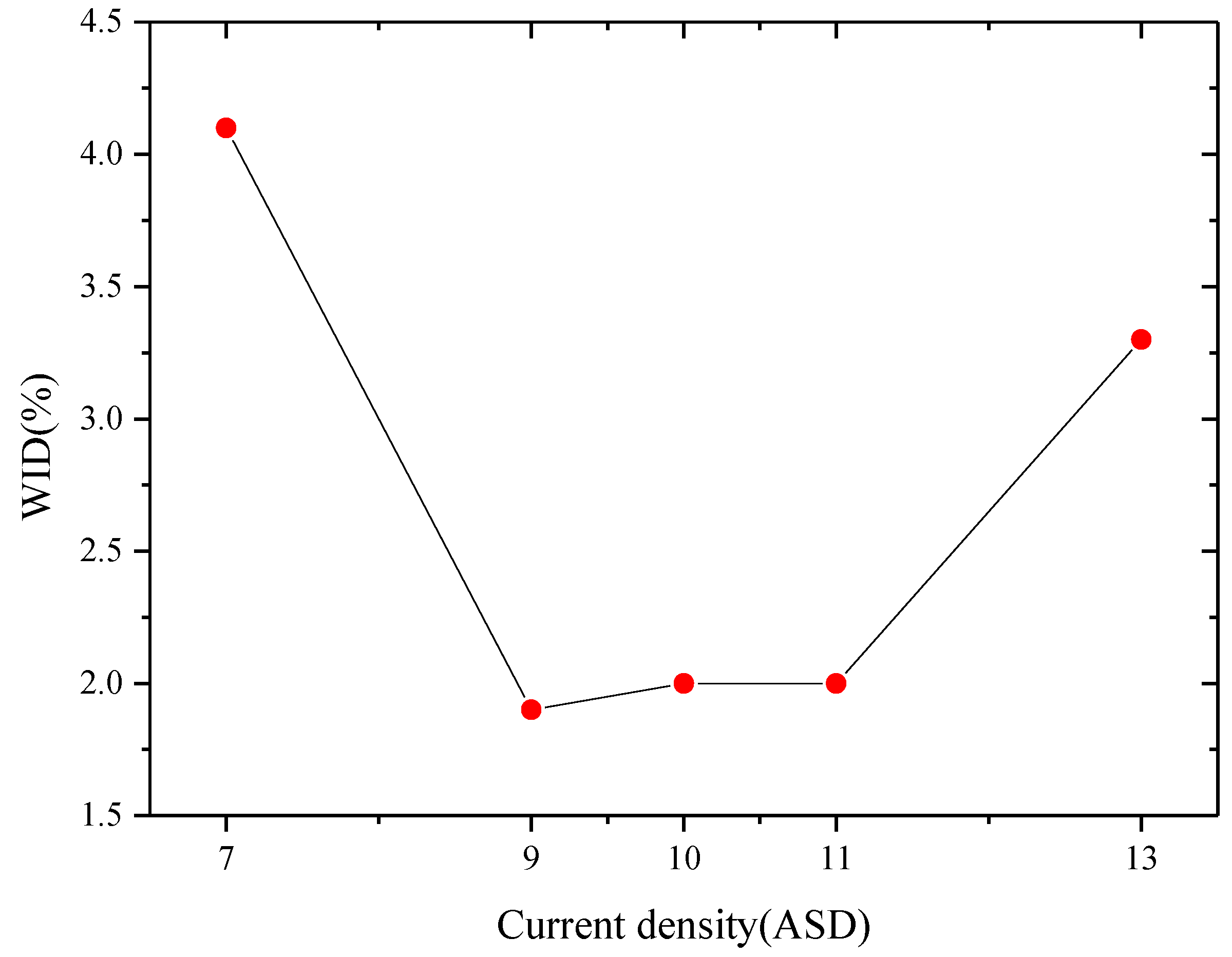

- Observation of changes in current density (ASD: Ampere per Square Decimeter)

- (f)

- Verifying the formation of a void

- 2.

- Preparation of samples for evaluating the shear strength of the pure Sn

- (a)

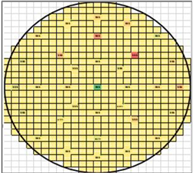

- Observation of Sn plating thickness uniformity on 4-inch wafer

- (b)

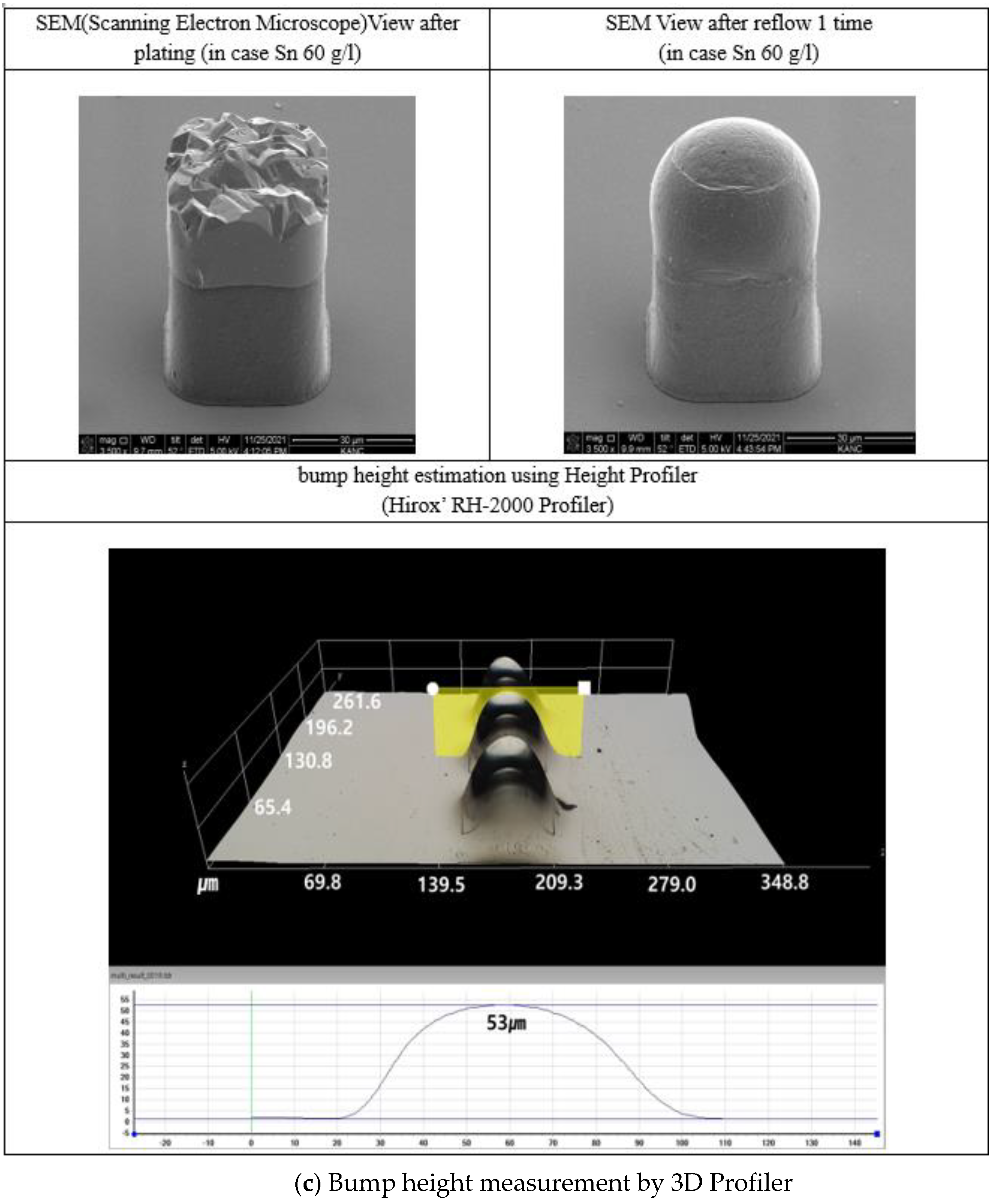

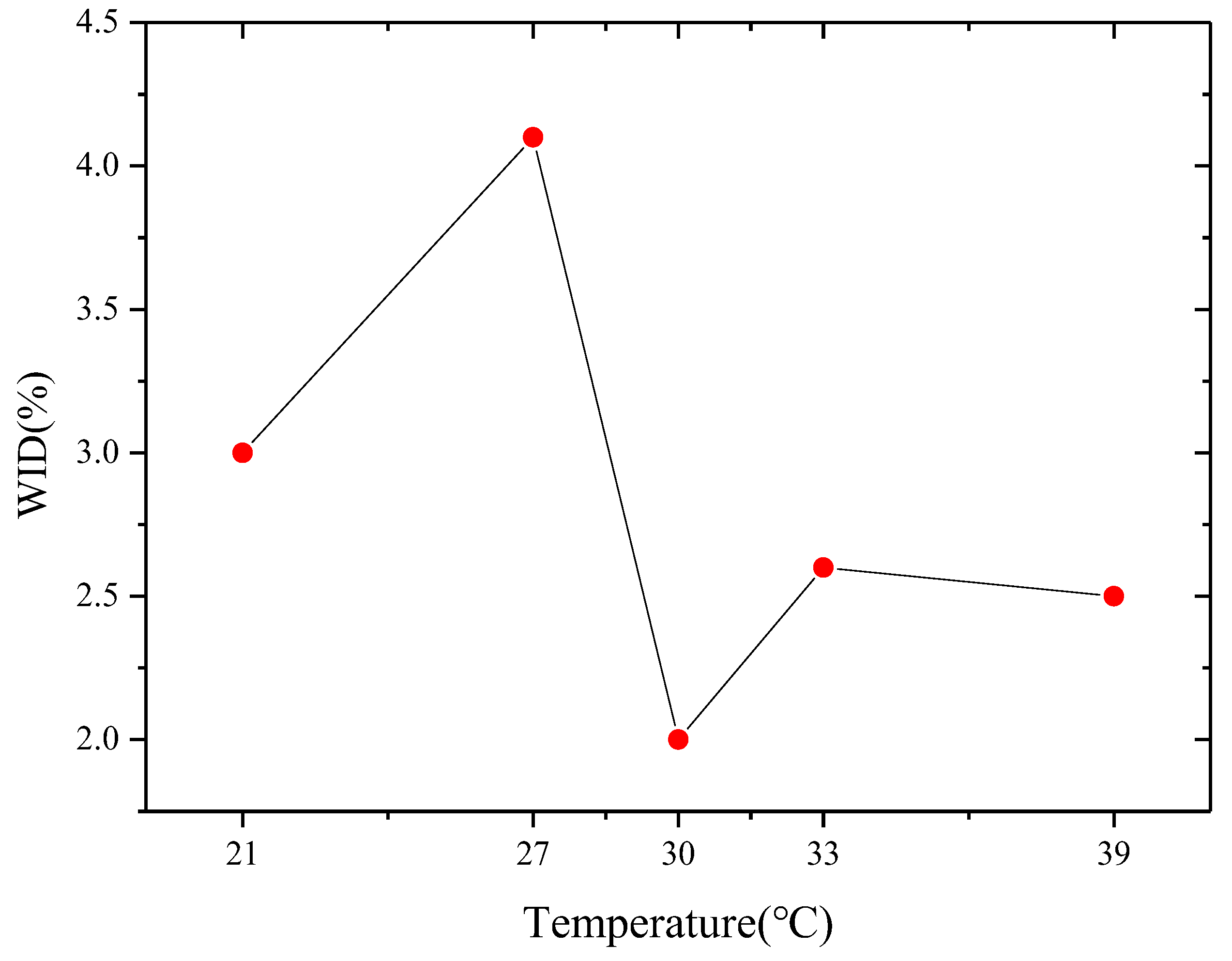

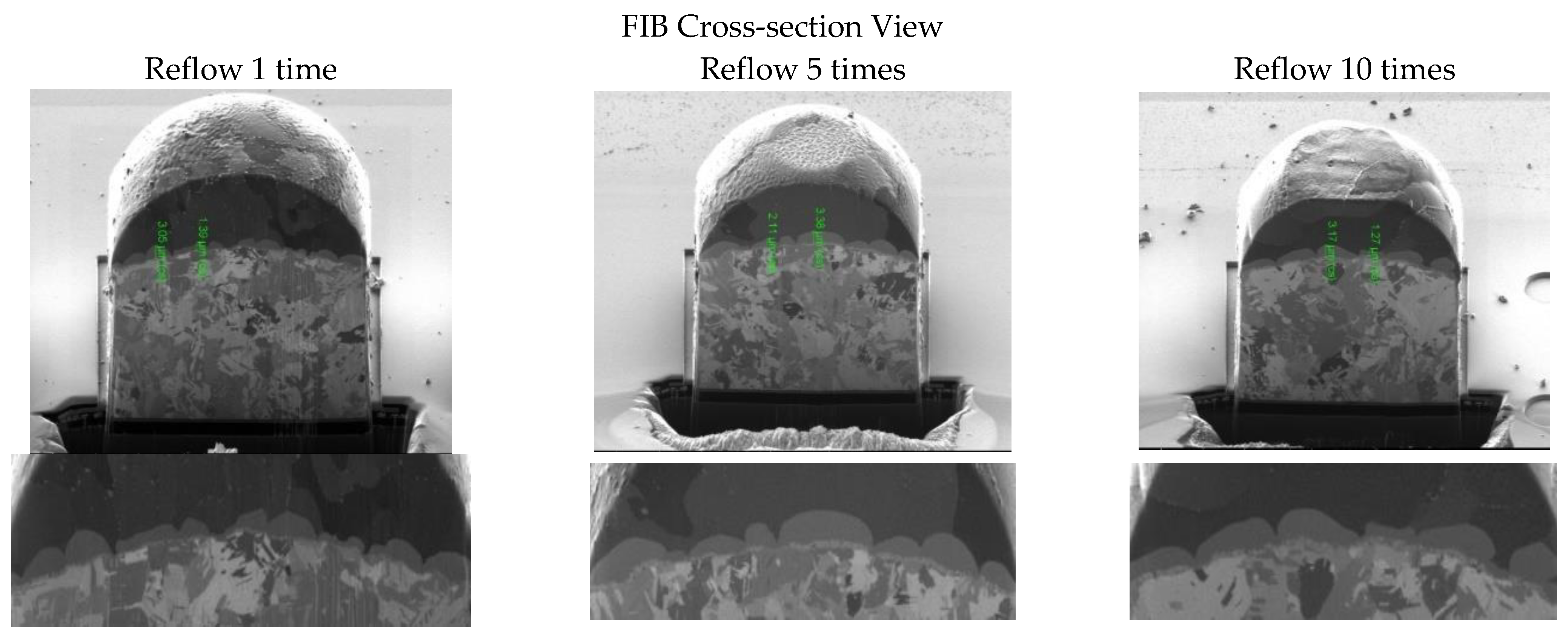

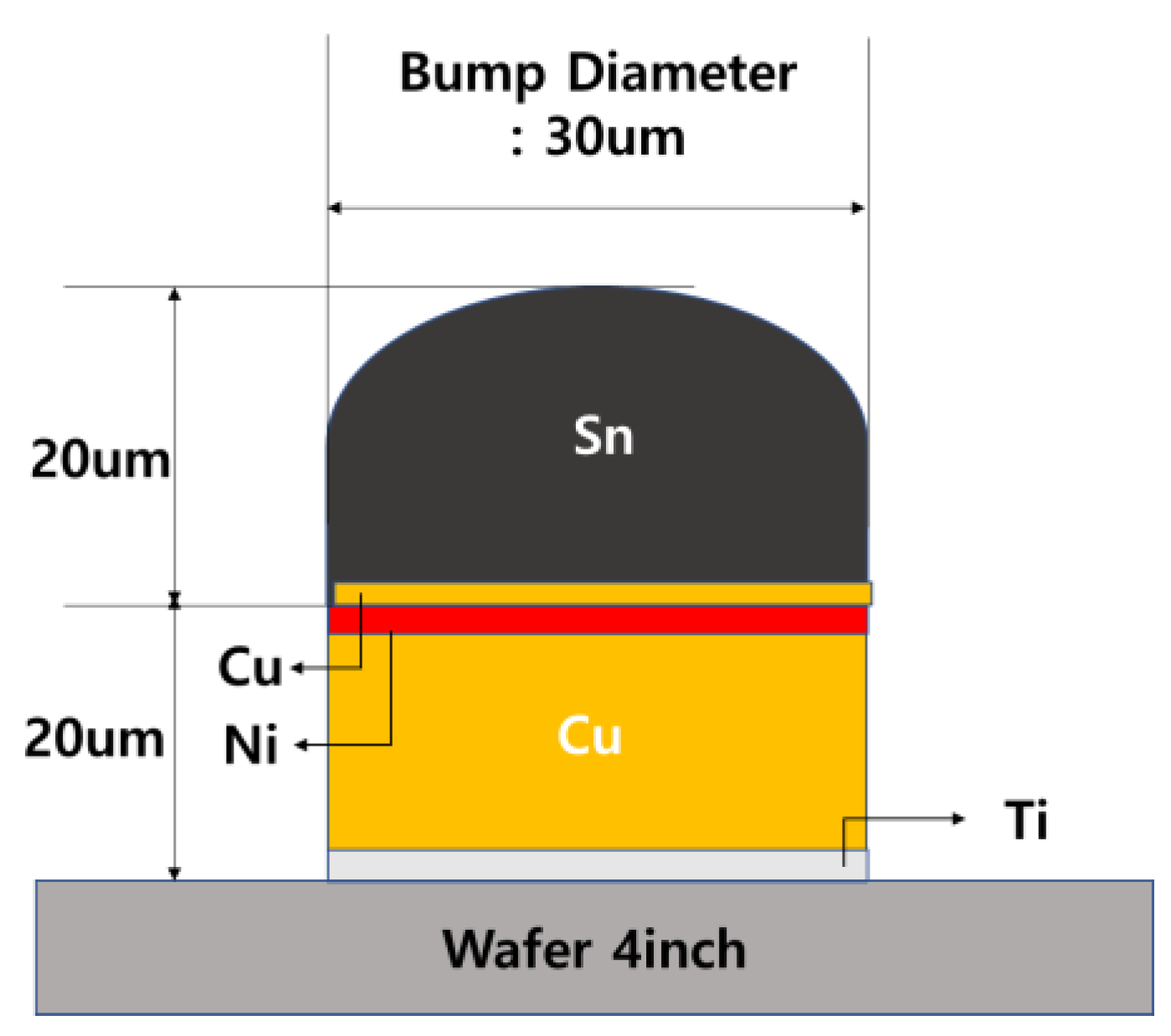

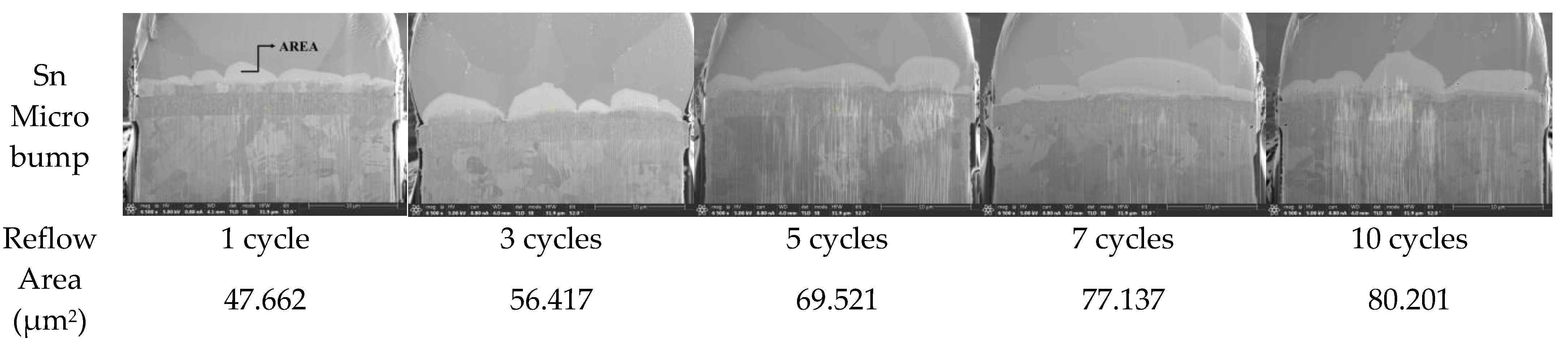

- Results of pure Sn bump geometry formed by plating

3. Results and Discussion

- (a)

- Shear test and evaluation

- (b)

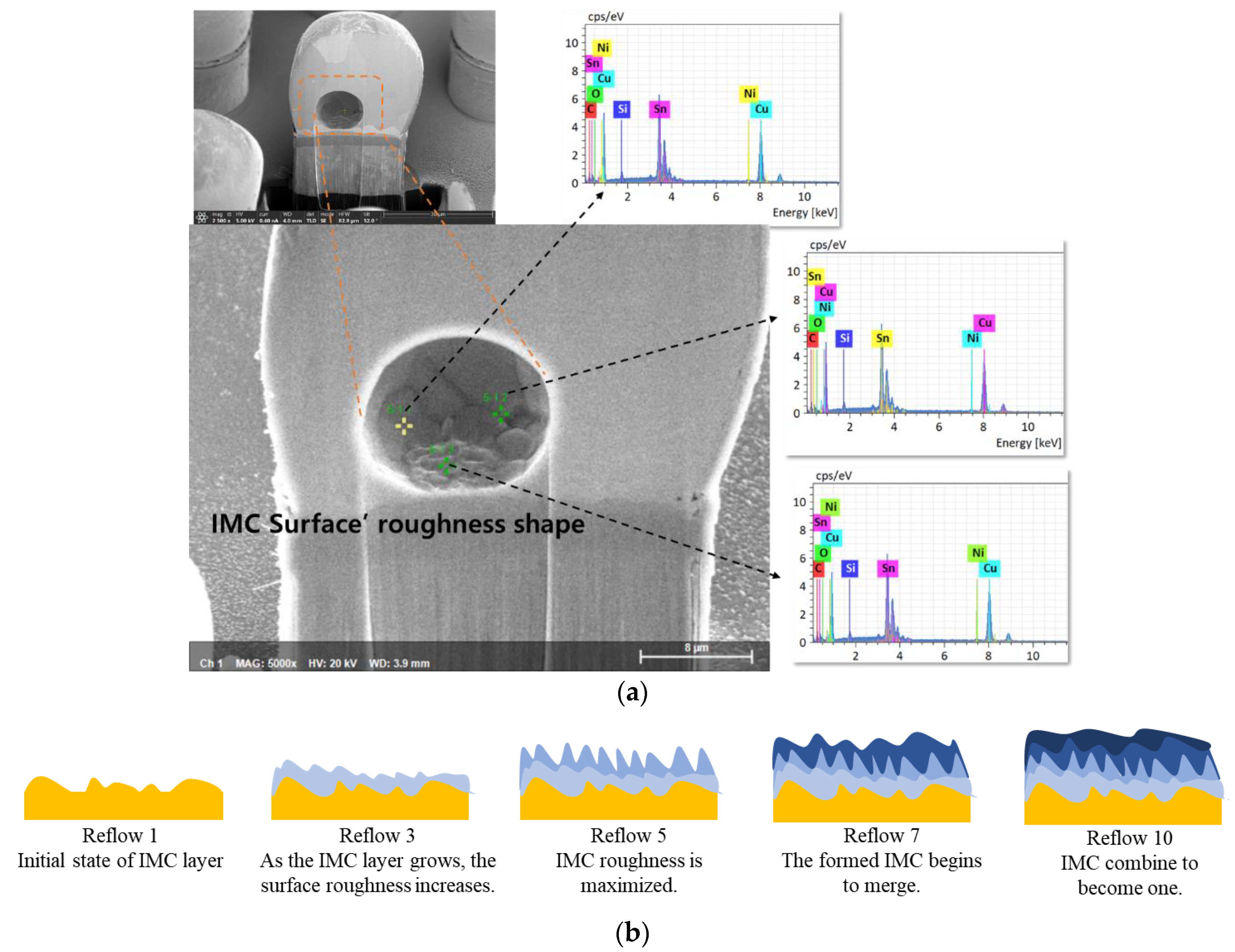

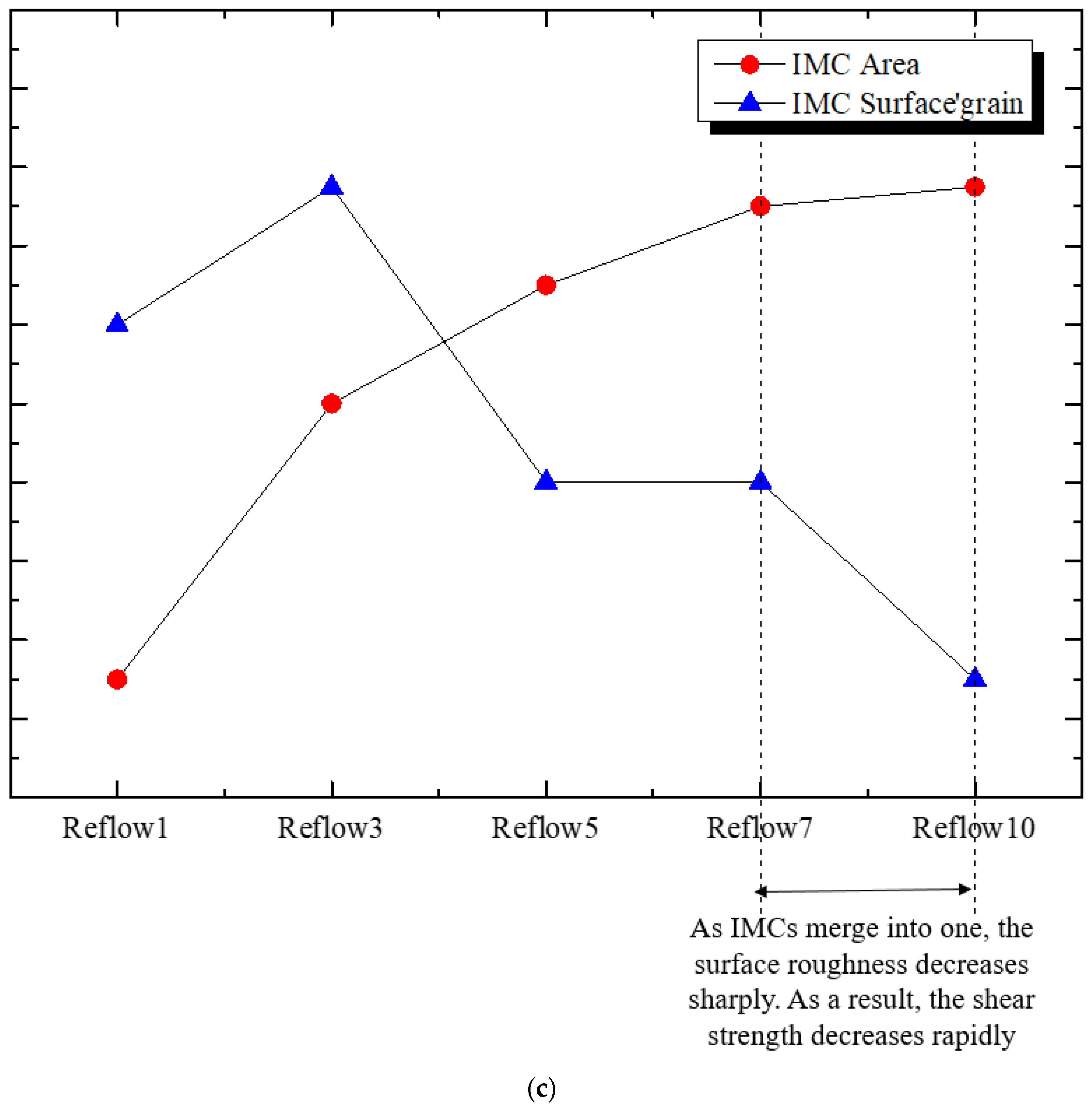

- Growth of IMC (Inter-Metallic Compound)

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- De Vos, J.; Jourdain, A.; Erismis, M.; Zhang, W.; De Munck, K.; La Manna, A.; Tezcan, D.S.; Soussan, P. High density 20 μm pitch CuSn microbump process for high-end 3D applications. In Proceedings of the 2011 IEEE 61st Electronic Components and Technology Conference (ECTC), Lake Buena Vista, FL, USA, 31 May–3 June 2011; pp. 27–31. [Google Scholar]

- Son, H.; Noh, S.; Jung, H.; Lee, W.; Oh, J.; Kim, N. Reliability studies on micro-bumps for 3-D TSV integration. In Proceedings of the 2013 IEEE 63rd Electronic Components and Technology Conference, Las Vegas, NV, USA, 28–31 May 2013; pp. 29–34. [Google Scholar]

- Ohara, Y.; Noriki, A.; Sakuma, K.; Lee, K.W.; Murugesan, M.; Bea, J.; Yamada, F.; Fukushima, T.; Tanaka, T.; Koyanagi, M. 10 µm fine pitch Cu/Sn micro-bumps for 3-D super-chip stack. In Proceedings of the 2009 IEEE International Conference on 3D System Integration, San Francisco, CA, USA, 28–30 September2009; pp. 1–6. [Google Scholar]

- Xiong, W.; Qi, L.; Luo, J.; Zhang, D.; Liang, J.; Yi, H. Experimental investigation on the height deviation of bumps printed by solder jet technology. J. Mater. Process. Technol. 2017, 243, 291–298. [Google Scholar] [CrossRef]

- Lee, J.-B. Semiconductor Memory Road Map: Advances in Semiconductor Memory. IEEE Solid-State Circuits Mag. 2016, 8, 66–74. [Google Scholar] [CrossRef]

- Kim, K. Silicon technologies and solutions for the data-driven world. In Proceedings of the 2015 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 22–26 February2015; pp. 1.1.1–1.1.9. [Google Scholar]

- Kang, U. 8 Gb 3-D DDR3 DRAM using through-silicon-via technology. IEEE J. Solid-State Circuits 2010, 45, 115–119. [Google Scholar] [CrossRef]

- Smith, K.; Hanaway, P.; Jolley, M.; Gleason, R.; Strid, E.; Daenen, T.; Dupas, L.; Knuts, B.; Marinissen, E.J.; Van Dievel, M. Evaluation of TSV and micro-bump probing for wide I/O testing. In Proceedings of the 2011 IEEE International Test Conference, Anaheim, CA, USA, 20–22 September 2011; pp. 1–10. [Google Scholar]

- Yoon, S.W.; Ku, J.H.; Suthiwongsunthorn, N.; Marimuthu, P.C.; Carson, F. Fabrication and packaging of microbump interconnections for 3D TSV. In Proceedings of the 2009 IEEE International Conference on 3D System Integration, San Francisco, CA, USA, 28–30 September 2009; pp. 1–5. [Google Scholar]

- Lee, J.; Lee, C.Y.; Kim, C.; Kalchuri, S. Micro Bump System for 2nd Generation Silicon Interposer with GPU and High Bandwidth Memory (HBM) Concurrent Integration. In Proceedings of the 2018 IEEE 68th Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 29 May–1 June 2018; pp. 607–612. [Google Scholar]

- Arai, S.; Akatsuka, H.; Kaneko, N. Sn-Ag Solder Bump Formation for Flip-Chip Bonding by Electroplating. J. Electrochem. Soc. 2003, 150, C730. [Google Scholar] [CrossRef]

- Sahaym, U.; Miller, S.L.; Norton, M.G. Effect of plating temperature on Sn surface morphology. Mater. Lett. 2010, 64, 1547–1550. [Google Scholar] [CrossRef]

- Wright, S.L.; Tsang, C.K.; Maria, J.; Dang, B.; Polastre, R.; Andry, P.; Knickerbocker, J. Micro-interconnection reliability: Thermal, electrical and mechanical stress. In Proceedings of the 2012 IEEE 62nd Electronic Components and Technology Conference, San Diego, CA, USA, 29 May–1 June 2012; pp. 1278–1286. [Google Scholar]

- Hsiao, H.-Y.; Trigg, A.D.; Chai, T.C. Failure Mechanism for Fine Pitch Microbump in Cu/Sn/Cu System During Current Stressing. IEEE Trans. Compon. Packag. Manuf. Technol. 2015, 5, 314–319. [Google Scholar] [CrossRef]

- Jung, H.-R.; Kim, H.-H.; Lee, W.-J. Characterization of small-sized eutectic Sn-Bi solder bumps fabricated using electroplating. J. Electron. Mater. 2006, 35, 1067–1073. [Google Scholar] [CrossRef]

- Tanida, K.; Umemoto, M.; Tanaka, N.; Tomita, Y.; Takahashi, K. Micro Cu Bump Interconnection on 3D Chip Stacking Technology. Jpn. J. Appl. Phys. 2004, 43, 2264–2270. [Google Scholar] [CrossRef]

- Na, S.-H.; Lim, S.-K.; Kim, J.-S.; Park, H.-S.; Oh, H.-J.; Choi, J.-W.; Suh, S.-J. Experimental study of bump void formation according to process conditions. Microelectron. Reliab. 2013, 53, 638–644. [Google Scholar] [CrossRef]

- Mei, Z.; Ahmad, M.; Hu, M.; Ramakrishna, G. Kirkendall voids at Cu/solder interface and their effects on solder joint reliability. In Proceedings of the Electronic Components and Technology, 2005, ECTC ’05, Lake Buena Vista, FL, USA, 1 May–3 June 2005; Volume 1, pp. 415–420. [Google Scholar]

- Zhou, S.; Zhang, Y.-B.; Gao, L.-Y.; Li, Z.; Liu, Z.-Q. The self-healing of Kirkendall voids on the interface between Sn and (1 1 1) oriented nanotwinned Cu under thermal aging. Appl. Surf. Sci. 2022, 588, 152900. [Google Scholar] [CrossRef]

- Liang, Y.C.; Chen, C.; Tu, K.N. Side Wall Wetting Induced Void Formation due to Small Solder Volume in Micro bumps of Ni/SnAg/Ni upon Reflow. ECS Solid State Lett. 2012, 1, P60. [Google Scholar] [CrossRef]

- Liu, H.; Xu, C.; Liu, X.; Yu, D.; Dai, F.; Lu, Y.; Shangguan, D. Effect of IMC growth on thermal cycling reliability of micro solder bumps. In Proceedings of the 2013 IEEE 15th Electronics Packaging Technology Conference (EPTC 2013), Singapore, 11–13 December 2013; pp. 836–839. [Google Scholar]

- Li, M.-L.; Zhang, L.; Jiang, N.; Zhong, S.-J.; Zhang, L. Influences of silicon carbide nanowires’ addition on IMC growth behavior of pure Sn solder during solid–liquid diffusion. J. Mater. Sci. Mater. Electron. 2021, 32, 18067–18075. [Google Scholar] [CrossRef]

- Lee, Y.-H.; Lee, H.-T. Shear strength and interfacial microstructure of Sn–Ag–xNi/Cu single shear lap solder joints. Mater. Sci. Eng. A 2007, 444, 75–83. [Google Scholar] [CrossRef]

- Pang, J.H.; Low, T.H.; Xiong, B.S.; Luhua, X.; Neo, C.C. Thermal cycling aging effects on Sn–Ag–Cu solder joint microstructure, IMC and strength. Thin Solid Films 2004, 462–463, 370–375. [Google Scholar] [CrossRef]

- Chan, Y.; So, A.C.; Lai, J. Growth kinetic studies of Cu–Sn intermetallic compound and its effect on shear strength of LCCC SMT solder joints. Mater. Sci. Eng. B 1998, 55, 5–13. [Google Scholar] [CrossRef]

- Xu, L.; Pang, J.H. Nano-indentation characterization of Ni–Cu–Sn IMC layer subject to isothermal aging. Thin Solid Films 2006, 504, 362–366. [Google Scholar] [CrossRef]

- Hou, L.; Moelans, N.; Derakhshandeh, J.; De Wolf, I.; Beyne, E. Study of the effect of Sn grain boundaries on IMC morphology in solid state inter-diffusion soldering. Sci. Rep. 2019, 9, 14862. [Google Scholar] [CrossRef]

- Kunwar, A.; Coutinho, Y.A.; Hektor, J.; Ma, H.; Moelans, N. Integration of machine learning with phase field method to model the electromigration induced Cu6Sn5 IMC growth at anode side Cu/Sn interface. J. Mater. Sci. Technol. 2020, 59, 203–219. [Google Scholar] [CrossRef]

- Guo, B.; Ma, H.; Kunwar, A.; Chu, X. Effect of the degree of super cooling on growth mechanism of Cu6Sn5 in pure Sn/Cu solder joint. J. Mater. Sci. Mater. Electron. 2021, 32, 7528–7540. [Google Scholar]

- Datta, M. Manufacturing processes for fabrication of flip-chip micro-bumps used in microelectronic packaging: An overview. J. Micromanuf. 2019, 3, 69–83. [Google Scholar] [CrossRef]

- Ma, X.; Qian, Y.; Yoshida, F. Effect of La on the Cu–Sn intermetallic compound (IMC) growth and solder joint reliability. J. Alloys Compd. 2002, 334, 224–227. [Google Scholar] [CrossRef]

| Experimental Condition | Evaluation Method | ||

|---|---|---|---|

| Current Density/Time | (7–13) ASD/3 min | ||

| Materials | Sn Concentration | (40–80) g/L | Height Uniformity (WID) = (Max–Min)/Avg × 100 Observation of the surface of the plated bump |

| ACID Concentration | 165 g/L | ||

| Additive concentration | 120 mL/L | ||

| Process condition | Temperature | (20–40) °C | |

| Plating cell capacity | 7 L | ||

| Velocity of flow | 3.5 L/min | ||

| Condition | Bump Height (µm) | Average (µm) | Max-Min (µm) | WID (%) | |||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Sn 42 g/L | P1 | P2 | P3 | P4 | P5 | P6 | P7 | P8 | 54.6 | 4.8 | ±4.4 |

| 54.8 | 56.0 | 53.7 | 53.8 | 52.3 | 53.3 | 55.9 | 52.7 | ||||

| P9 | P10 | P11 | P12 | P13 | P14 | P15 | P16 | ||||

| 54.0 | 53.7 | 56.0 | 53.4 | 52.7 | 56.5 | 57.1 | 57.0 | ||||

| Sn 54 g/L | P1 | P2 | P3 | P4 | P5 | P6 | P7 | P8 | 57.1 | 2.6 | ±2.3 |

| 56.3 | 55.8 | 57.5 | 56.9 | 56.7 | 56.7 | 56.5 | 58.3 | ||||

| P9 | P10 | P11 | P12 | P13 | P14 | P15 | P16 | ||||

| 58.4 | 57.4 | 57.2 | 56.8 | 57.9 | 56.5 | 57.1 | 57.0 | ||||

| Sn 60 g/L | P1 | P2 | P3 | P4 | P5 | P6 | P7 | P8 | 55.0 | 2.2 | ±2.0 |

| 54.9 | 54.9 | 54.7 | 56.0 | 55.5 | 54.7 | 55.1 | 56.0 | ||||

| P9 | P10 | P11 | P12 | P13 | P14 | P15 | P16 | ||||

| 55.0 | 55.4 | 54.6 | 55.5 | 54.9 | 53.8 | 54.5 | 54.1 | ||||

| Sn 66 g/L | P1 | P2 | P3 | P4 | P5 | P6 | P7 | P8 | 54.3 | 3.2 | ±2.9 |

| 53.9 | 54.4 | 54.0 | 53.7 | 54.7 | 53.9 | 55.5 | 55.9 | ||||

| P9 | P10 | P11 | P12 | P13 | P14 | P15 | P16 | ||||

| 55.9 | 52.7 | 52.9 | 54.4 | 54.4 | 54.6 | 53.8 | 53.8 | ||||

| Sn 78 g/L | P1 | P2 | P3 | P4 | P5 | P6 | P7 | P8 | 56.6 | 3.6 | ±3.2 |

| 57.4 | 56.4 | 57.8 | 55.5 | 55.1 | 57.6 | 58.3 | 55.5 | ||||

| P9 | P10 | P11 | P12 | P13 | P14 | P15 | P16 | ||||

| 55.1 | 57.4 | 57.8 | 56.2 | 54.7 | 55.6 | 57.6 | 56.8 | ||||

| Condition | Bump Height (µm) | Average (µm) | Max-Min (µm) | WID (%) | |||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Additive Add. 42 mL/L | P1 | P2 | P3 | P4 | P5 | P6 | P7 | P8 | 52.5 | 4.1 | ±3.9 |

| 52.5 | 52.9 | 53.0 | 50.2 | 53.5 | 53.5 | 52.6 | 52.3 | ||||

| P9 | P10 | P11 | P12 | P13 | P14 | P15 | P16 | ||||

| 52.3 | 51.9 | 53.0 | 52.7 | 52.0 | 51.9 | 52.1 | 54.3 | ||||

| Additive Add. 54 mL/L | P1 | P2 | P3 | P4 | P5 | P6 | P7 | P8 | 54.9 | 4.0 | ±3.6 |

| 55.9 | 56.7 | 52.7 | 56.1 | 54.8 | 54.6 | 56.3 | 55.3 | ||||

| P9 | P10 | P11 | P12 | P13 | P14 | P15 | P16 | ||||

| 54.6 | 54.9 | 53.2 | 56.1 | 55.7 | 54.1 | 54.0 | 54.0 | ||||

| Additive Add. 60 mL/L | P1 | P2 | P3 | P4 | P5 | P6 | P7 | P8 | 55.0 | 2.2 | ±2.0 |

| 54.9 | 54.9 | 54.7 | 56.0 | 55.5 | 54.7 | 55.1 | 56.0 | ||||

| P9 | P10 | P11 | P12 | P13 | P14 | P15 | P16 | ||||

| 55.0 | 55.4 | 54.6 | 55.5 | 54.9 | 53.8 | 54.5 | 54.1 | ||||

| Additive Add. 66 mL/L | P1 | P2 | P3 | P4 | P5 | P6 | P7 | P8 | 54.6 | 4.1 | ±3.8 |

| 54.8 | 54.4 | 52.5 | 55.2 | 54.3 | 55.4 | 53.9 | 55.1 | ||||

| P9 | P10 | P11 | P12 | P13 | P14 | P15 | P16 | ||||

| 55.1 | 53.8 | 53.9 | 56.6 | 55.1 | 54.7 | 54.8 | 53.9 | ||||

| Additive Add. 78 mL/L | P1 | P2 | P3 | P4 | P5 | P6 | P7 | P8 | 54.7 | 6.8 | ±6.2 |

| 54.0 | 54.6 | 52.7 | 55.8 | 54.8 | 54.2 | 54.5 | 57.7 | ||||

| P9 | P10 | P11 | P12 | P13 | P14 | P15 | P16 | ||||

| 57.8 | 53.2 | 51.0 | 56.2 | 56.1 | 53.4 | 54.3 | 54.4 | ||||

| Condition | Bump Height (µm) | Average (µm) | Max-Min (µm) | WID (%) | |||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| 21 °C | P1 | P2 | P3 | P4 | P5 | P6 | P7 | P8 | 54.9 | 3.3 | ±3.0 |

| 55.5 | 56.0 | 55.2 | 55.2 | 55.3 | 54.6 | 55.7 | 55.3 | ||||

| P9 | P10 | P11 | P12 | P13 | P14 | P15 | P16 | ||||

| 55.1 | 54.9 | 54.1 | 54.3 | 54.9 | 52.7 | 55.1 | 54.1 | ||||

| 27 °C | P1 | P2 | P3 | P4 | P5 | P6 | P7 | P8 | 53.7 | 4.5 | ±4.2 |

| 52.8 | 53.5 | 53.2 | 54.3 | 53.4 | 53.1 | 54.4 | 54.7 | ||||

| P9 | P10 | P11 | P12 | P13 | P14 | P15 | P16 | ||||

| 56.5 | 53.1 | 52.7 | 52.0 | 52.5 | 52.6 | 54.9 | 54.7 | ||||

| 30 °C | P1 | P2 | P3 | P4 | P5 | P6 | P7 | P8 | 55.0 | 2.2 | ±2.0 |

| 54.9 | 54.9 | 54.7 | 56.0 | 55.5 | 54.7 | 55.1 | 56.0 | ||||

| P9 | P10 | P11 | P12 | P13 | P14 | P15 | P16 | ||||

| 55.0 | 55.4 | 54.6 | 55.5 | 54.9 | 53.8 | 54.5 | 54.1 | ||||

| 33 °C | P1 | P2 | P3 | P4 | P5 | P6 | P7 | P8 | 54.0 | 2.8 | ±2.6 |

| 53.0 | 53.2 | 53.6 | 54.7 | 55.6 | 54.3 | 54.8 | 55.7 | ||||

| P9 | P10 | P11 | P12 | P13 | P14 | P15 | P16 | ||||

| 55.5 | 53.3 | 53.1 | 53.9 | 54.3 | 53.3 | 53.4 | 52.9 | ||||

| 39 °C | P1 | P2 | P3 | P4 | P5 | P6 | P7 | P8 | 56.6 | 2.8 | ±2.5 |

| 57.7 | 57.9 | 56.0 | 57.1 | 57.0 | 56.5 | 55.2 | 58.0 | ||||

| P9 | P10 | P11 | P12 | P13 | P14 | P15 | P16 | ||||

| 58.0 | 55.5 | 56.2 | 56.9 | 56.2 | 55.7 | 55.9 | 55.5 | ||||

| Condition | Bump Height (µm) | Average (µm) | Max-Min (µm) | WID (%) | |||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| 7ASD | P1 | P2 | P3 | P4 | P5 | P6 | P7 | P8 | 54.8 | 4.5 | ±4.1 |

| 54.4 | 54.7 | 54.5 | 57.8 | 56.7 | 53.8 | 55.6 | 55.4 | ||||

| P9 | P10 | P11 | P12 | P13 | P14 | P15 | P16 | ||||

| 54.3 | 54.9 | 53.8 | 55.1 | 55.4 | 53.6 | 53.7 | 53.3 | ||||

| 9ASD | P1 | P2 | P3 | P4 | P5 | P6 | P7 | P8 | 55.5 | 2.1 | ±1.9 |

| 55.0 | 55.4 | 56.4 | 56.0 | 56.3 | 56.3 | 56.0 | 56.2 | ||||

| P9 | P10 | P11 | P12 | P13 | P14 | P15 | P16 | ||||

| 56.2 | 55.8 | 55.3 | 54.4 | 55.1 | 54.3 | 54.6 | 54.8 | ||||

| 10ASD | P1 | P2 | P3 | P4 | P5 | P6 | P7 | P8 | 55.0 | 2.2 | ±2.0 |

| 54.9 | 54.9 | 54.7 | 56.0 | 55.5 | 54.7 | 55.1 | 56.0 | ||||

| P9 | P10 | P11 | P12 | P13 | P14 | P15 | P16 | ||||

| 55.0 | 55.4 | 54.6 | 55.5 | 54.9 | 53.8 | 54.5 | 54.1 | ||||

| 11ASD | P1 | P2 | P3 | P4 | P5 | P6 | P7 | P8 | 54.4 | 2.1 | ±2.0 |

| 54.9 | 54.7 | 53.4 | 54.6 | 53.7 | 53.7 | 54.1 | 54.9 | ||||

| P9 | P10 | P11 | P12 | P13 | P14 | P15 | P16 | ||||

| 54.5 | 55.2 | 53.2 | 55.3 | 54.5 | 53.7 | 55.1 | 55.0 | ||||

| 13ASD | P1 | P2 | P3 | P4 | P5 | P6 | P7 | P8 | 54.9 | 3.6 µm | ±3.3 |

| 55.9 | 55.1 | 54.2 | 55.7 | 55.0 | 54.7 | 55.0 | 55.0 | ||||

| P9 | P10 | P11 | P12 | P13 | P14 | P15 | P16 | ||||

| 57.1 | 54.3 | 54.1 | 55.0 | 55.1 | 53.5 | 54.4 | 54.0 | ||||

| Sr. No. | Parameters Evaluated | Result of Experiment | Before Reflow | After Reflow |

|---|---|---|---|---|

| 1 | Sn Concentration | 60 g/L |  |  |

| 2 | Acid Concentration | 165 g/L | ||

| 3 | Additive Concentration | 120 mL/L | ||

| 4 | Temperature | 30 °C | ||

| 5 | Plating cell capacity | 7 L | ||

| 6 | Current density | 9 ASD | ||

| 7 | Plating time | 3 min | ||

| 8 | Velocity of flow | 3.5 L/min |

| Anode-Cathode Distance (mm) (Anode–Cathode) | Shielding Distance (mm) | Shielding Size (mm) | WIW (%) | Wafer Pattern |

|---|---|---|---|---|

| 155 | 65 | 65 | ±6.93 |  |

| 115 | 65 | 65 | ±3.88 | |

| 115 | 65 | 35 | ±7.86 |

| Measurement of Wafer and Bump SEM |  | |||

|---|---|---|---|---|

| After Plating | After reflow | Bump SEM view by position on wafer | ||

| #1 | #2 | #3 | ||

|  |  |  |  |

| Thickness (µm) for #1 | Ave. (µm) | Max-Min (µm) | WID (%) | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 24.02 | 0.4 | ±1.7 |

| 23.9 | 23.9 | 23.8 | 24.2 | 24.1 | 24.1 | 24.1 | 24.1 | 24.2 | 23.8 | |||

| Thickness (µm) for #1, #2, #3 | Ave. (µm) | Max-Min (µm) | WID (%) | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 24.02 | 0.9 | ±1.9 | |

| #1 | 23.9 | 23.9 | 23.8 | 24.1 | 24.2 | 24.1 | 24.1 | 24.1 | 24.2 | 23.8 | |||

| #2 | 24.7 | 24.4 | 24.4 | 24.4 | 24.3 | 24.6 | 24.7 | 24.6 | 24.6 | 24.3 | |||

| #3 | 23.8 | 24.2 | 24.4 | 24.3 | 24.2 | 24.2 | 24.1 | 24.1 | 23.8 | 24.2 | |||

| (Unit: gf) | Reflow 1 Cycle | Reflow 3 Cycle | Reflow 5 Cycle | Reflow 7 Cycle | Reflow 10 Cycle |

|---|---|---|---|---|---|

| Max | 5.852 | 9.594 | 8.052 | 8.740 | 3.324 |

| Min | 4.426 | 8.629 | 6.696 | 7.745 | 2.710 |

| Ave | 5.314 | 9.078 | 7.367 | 8.202 | 2.999 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Na, C.-Y.; Jeon, B.-M.; Kim, J.-W.; Jung, W.-S.; Jeong, J.-S.; Cho, S.-M.; Park, H.-S. Fabrication of 30 µm Sn Microbumps by Electroplating and Investigation of IMC Characteristics on Shear Strength. Electronics 2023, 12, 144. https://doi.org/10.3390/electronics12010144

Na C-Y, Jeon B-M, Kim J-W, Jung W-S, Jeong J-S, Cho S-M, Park H-S. Fabrication of 30 µm Sn Microbumps by Electroplating and Investigation of IMC Characteristics on Shear Strength. Electronics. 2023; 12(1):144. https://doi.org/10.3390/electronics12010144

Chicago/Turabian StyleNa, Chang-Yun, Byung-Min Jeon, Jong-Wook Kim, Woon-Seok Jung, Jae-Seong Jeong, Sung-Min Cho, and Hwa-Sun Park. 2023. "Fabrication of 30 µm Sn Microbumps by Electroplating and Investigation of IMC Characteristics on Shear Strength" Electronics 12, no. 1: 144. https://doi.org/10.3390/electronics12010144

APA StyleNa, C.-Y., Jeon, B.-M., Kim, J.-W., Jung, W.-S., Jeong, J.-S., Cho, S.-M., & Park, H.-S. (2023). Fabrication of 30 µm Sn Microbumps by Electroplating and Investigation of IMC Characteristics on Shear Strength. Electronics, 12(1), 144. https://doi.org/10.3390/electronics12010144