Stabilizing the Boost PFC Converter with a Time Delay Feedback Controller

Abstract

1. Introduction

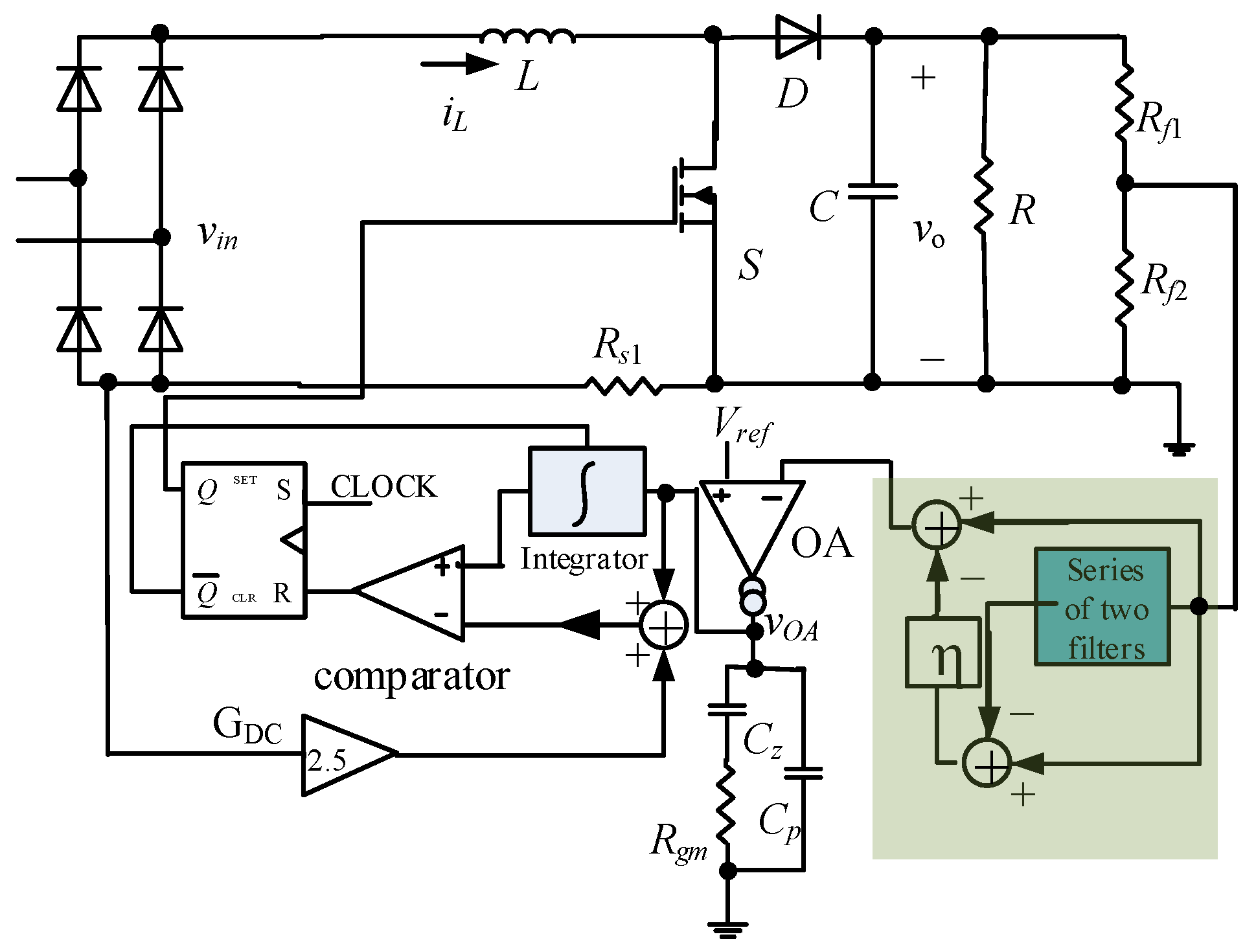

2. Description of the OCC Boost PFC Converter

2.1. Main Circuit

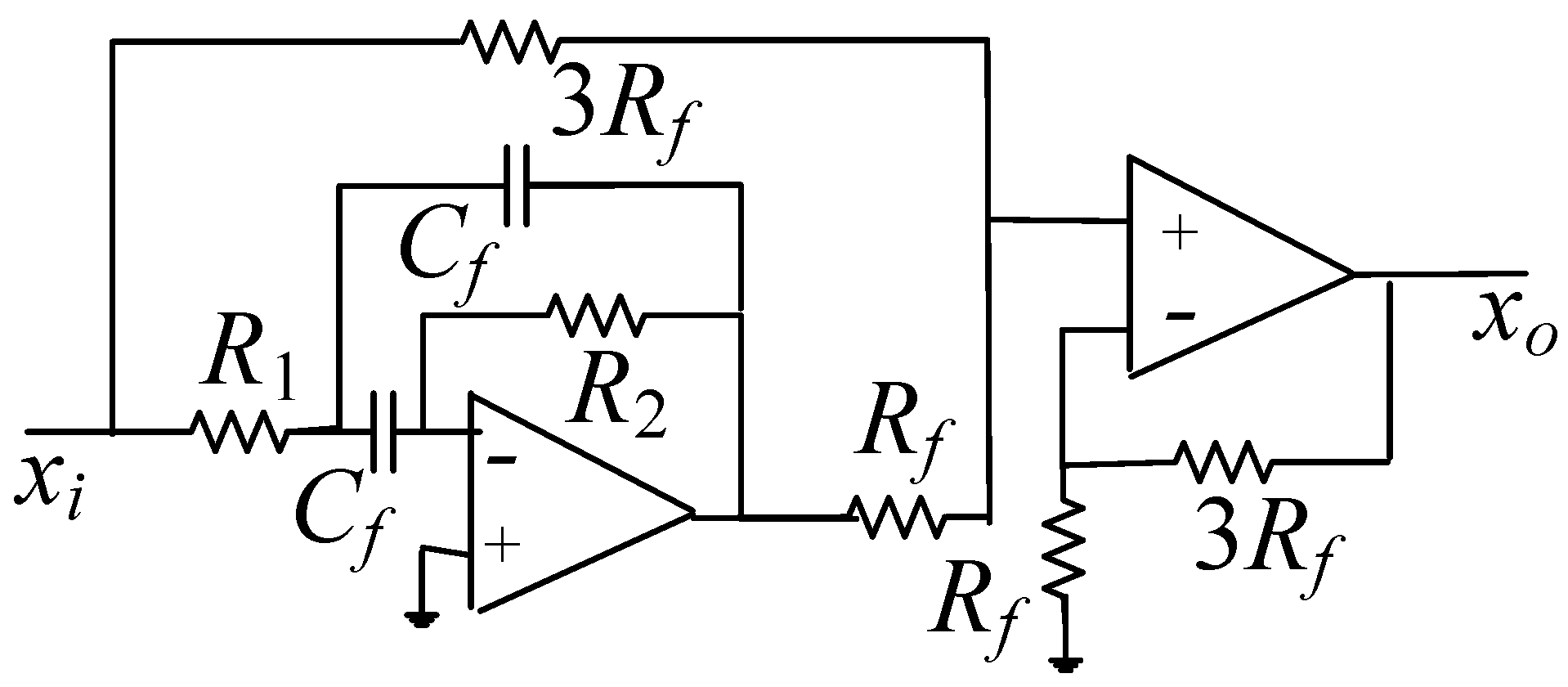

2.2. Control Circuit

3. Stability of the OCC Boost PFC Converter

3.1. DC Component

3.2. The Second Harmonic Component

3.3. The First Harmonic Component

3.4. Stability Boundary of Gain

4. Results

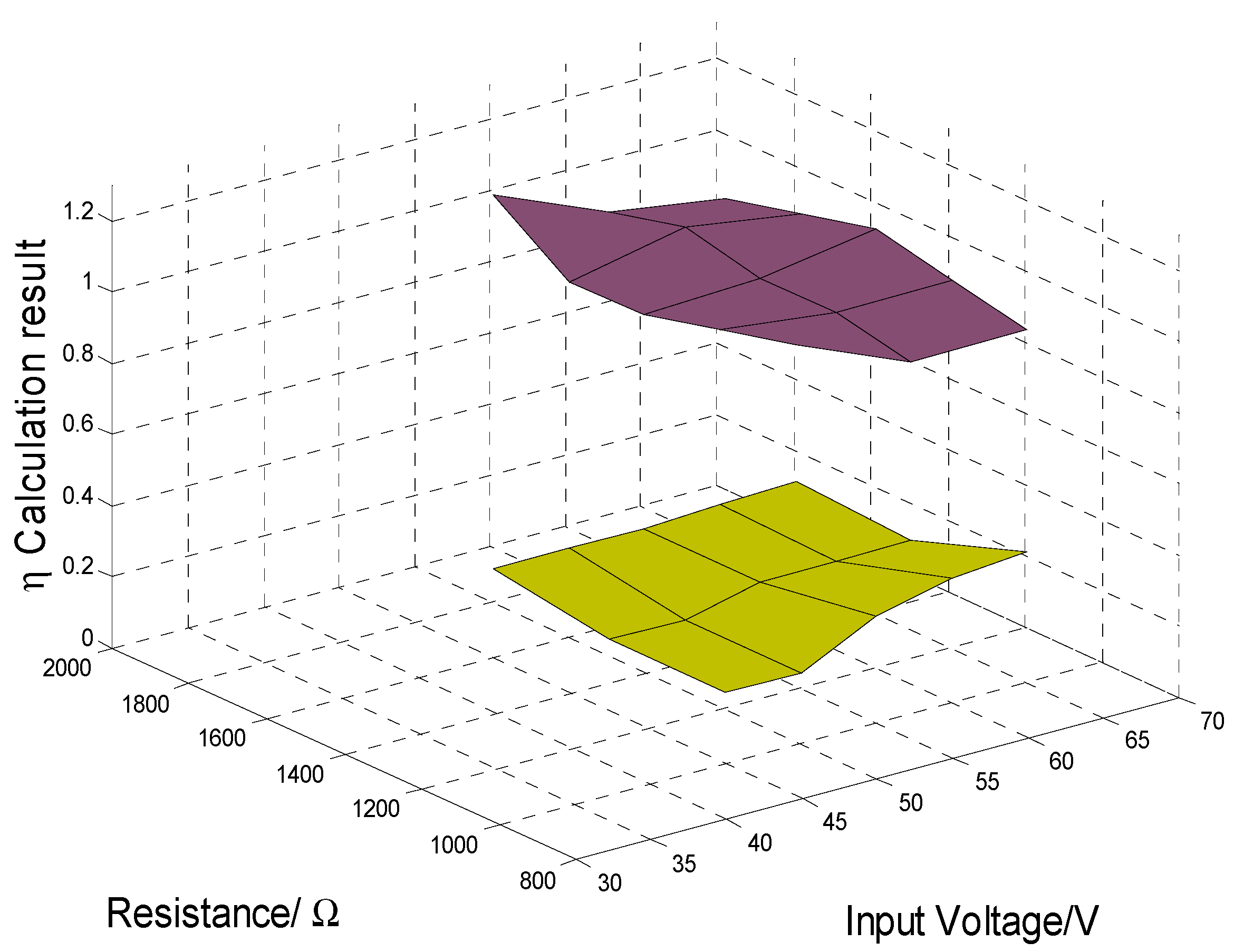

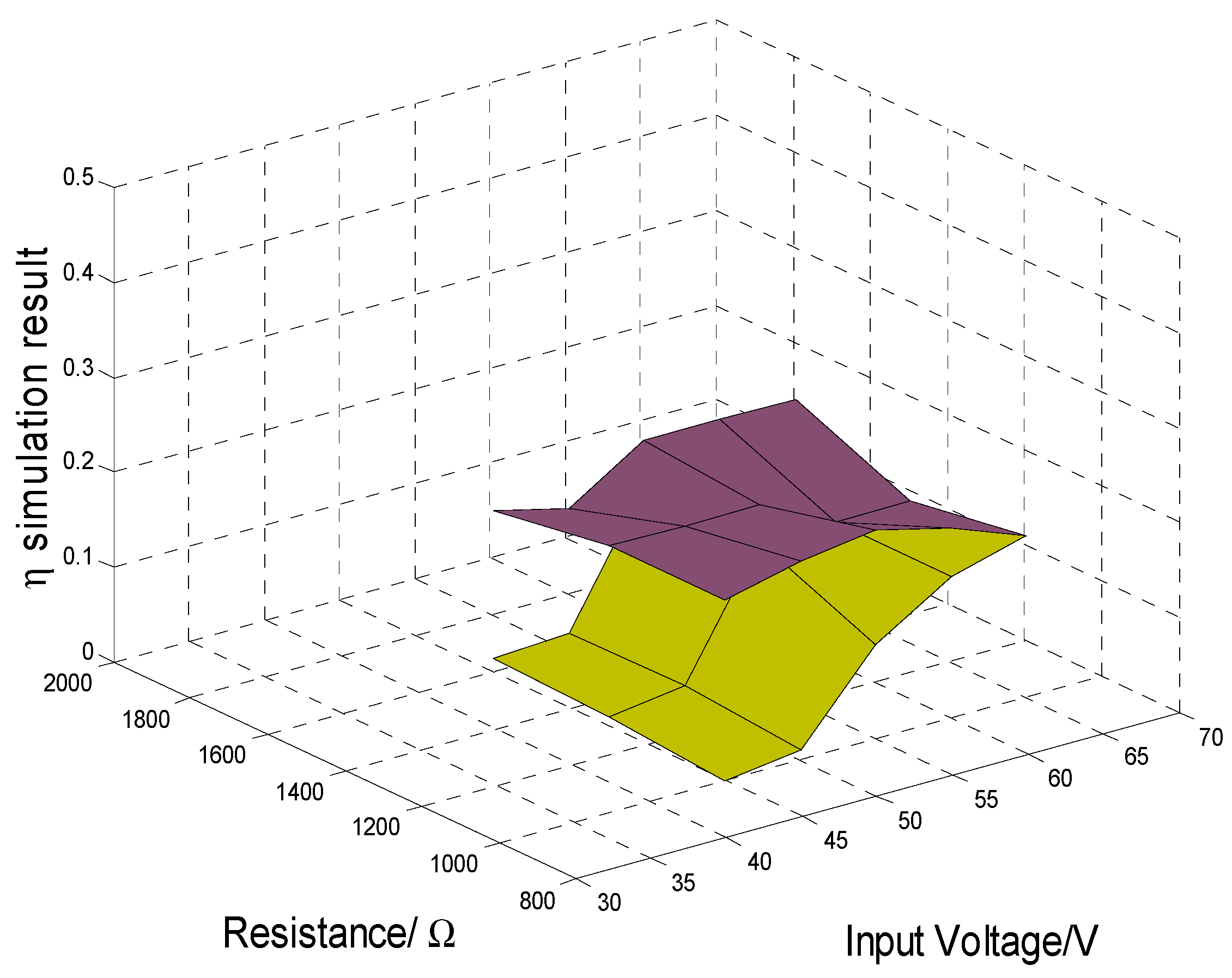

4.1. Calculated and Simulation Stability Boundary of Gain

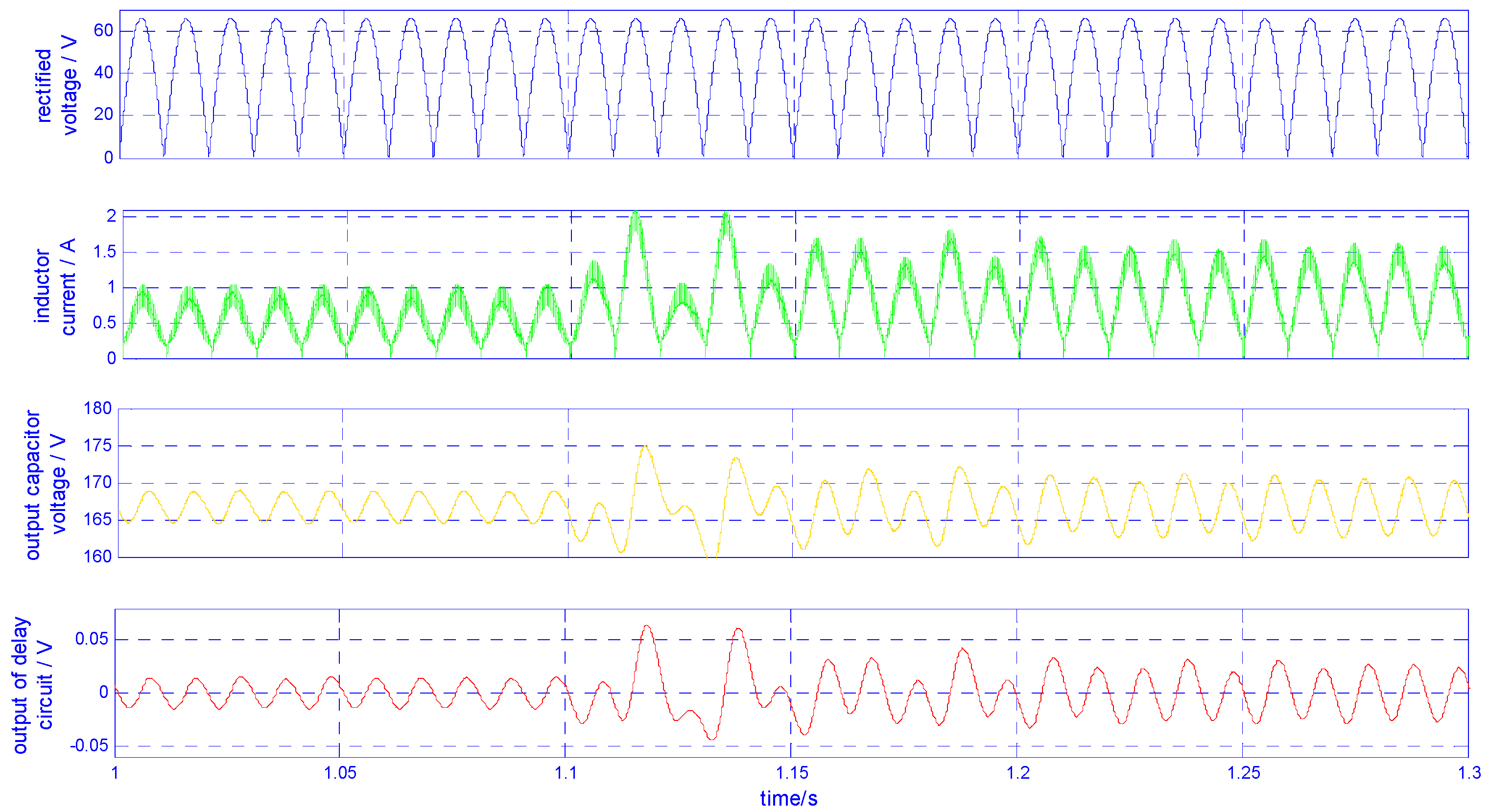

4.2. Simulation Results

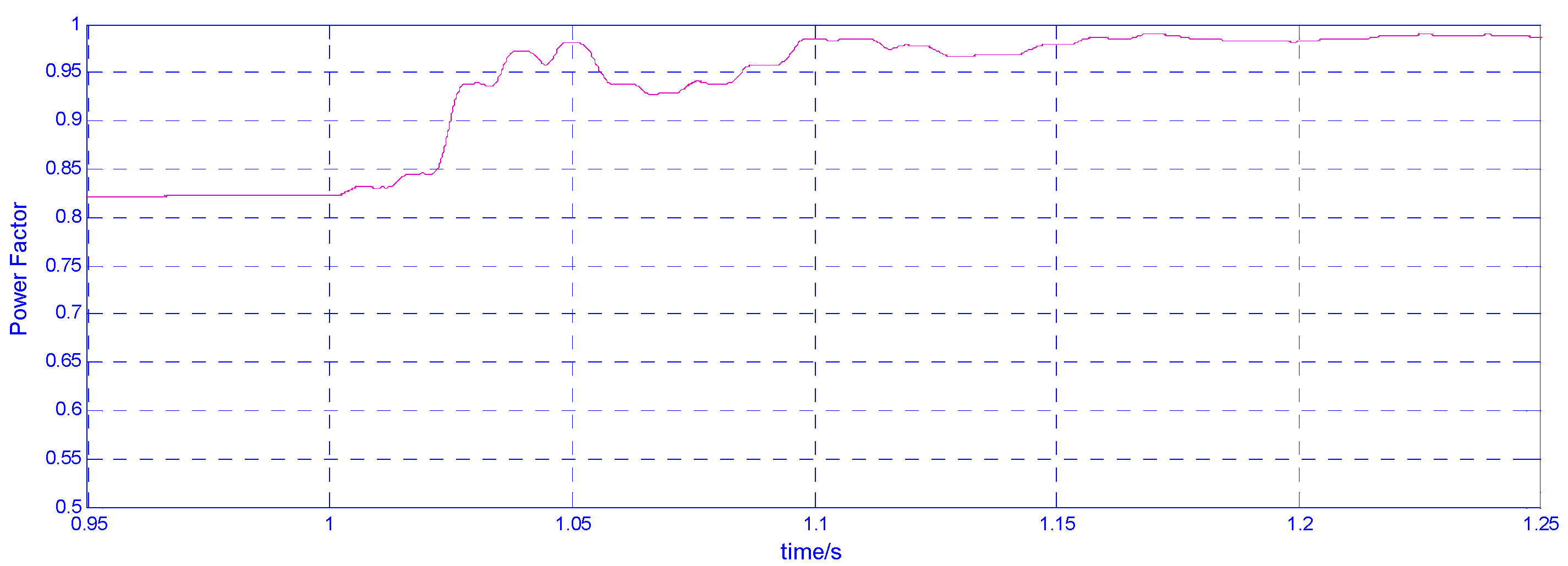

4.3. Improvement of PF

4.4. Dynamics Performances in Front of Load Change

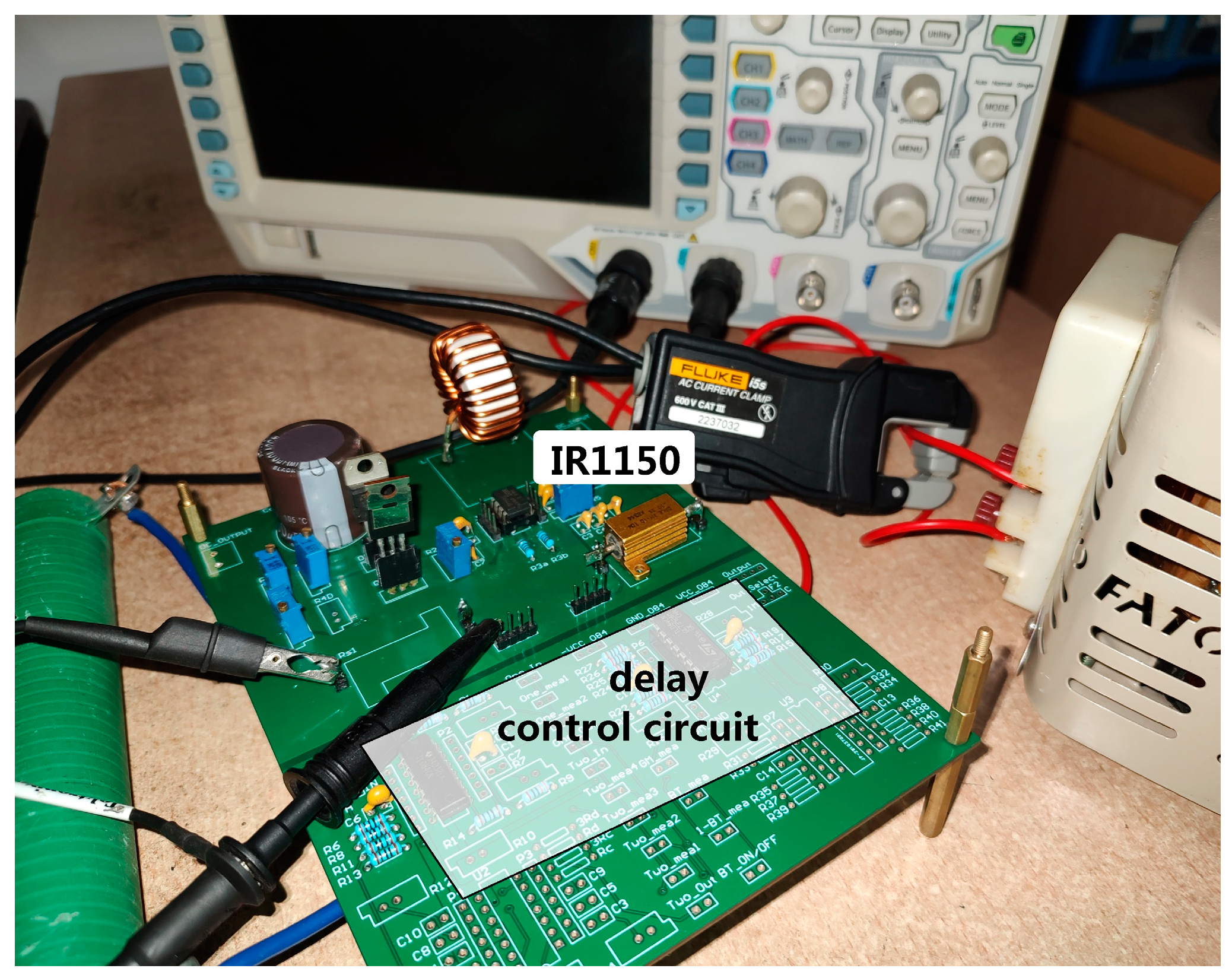

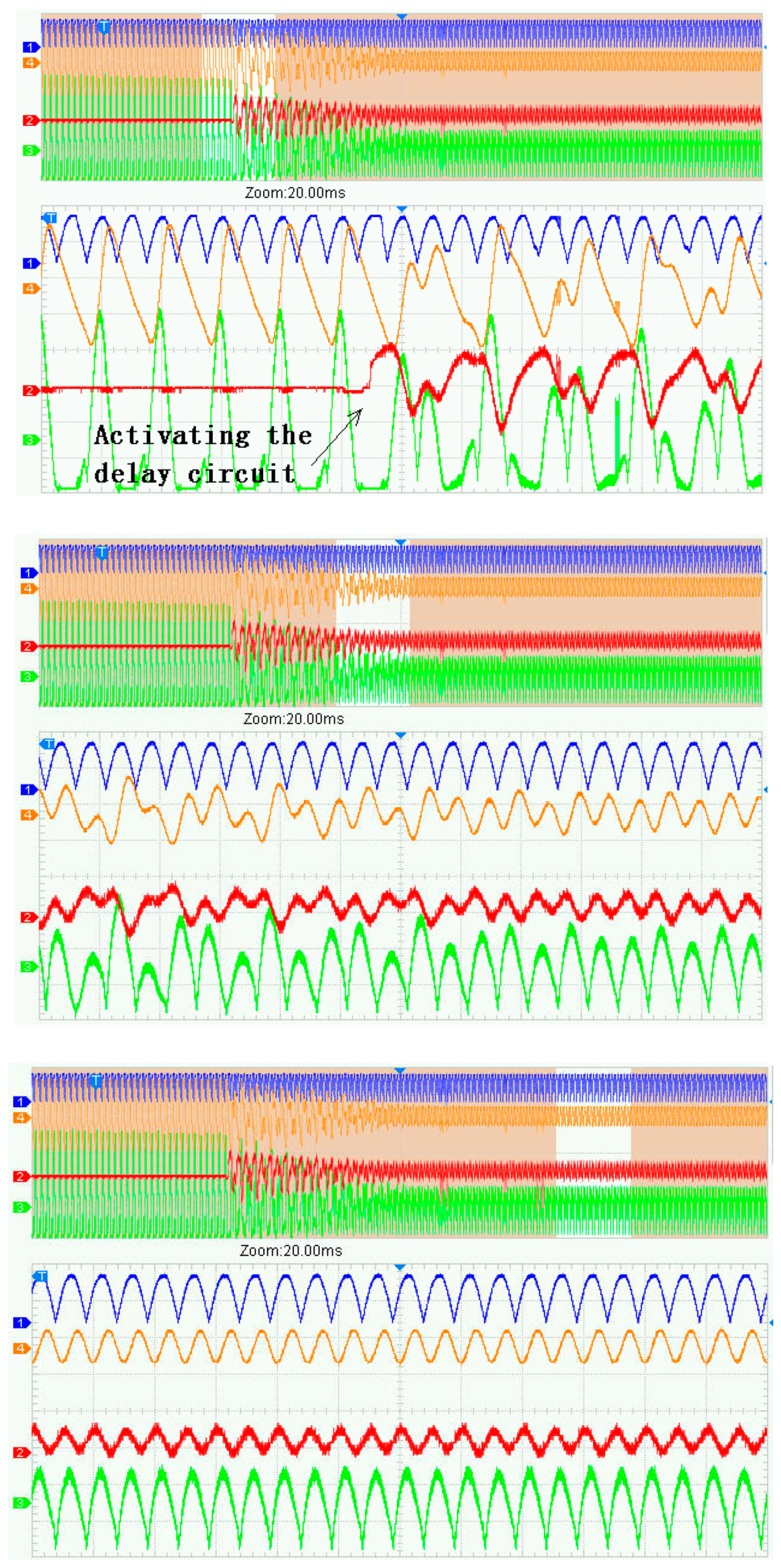

4.5. Experimental Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Chu, G.; Tse, C.K.; Wong, S.C. Line-frequency instability of PFC power supplies. IEEE Trans. Power Electron. 2009, 24, 469–482. [Google Scholar] [CrossRef]

- Zhang, R.; Ma, W.; Wang, L.; Hu, M.; Cao, L.; Zhou, H.; Zhang, Y. Line frequency instability of One-Cycle-Controlled boost power factor correction converter. Electronics 2018, 7, 203. [Google Scholar] [CrossRef]

- El Aroudi, A.; Orabi, M.; Haroun, R.; Martínez-Salamero, L. Asymptotic slow-scale stability boundary of PFC ac-dc power converters: Theoretical prediction and experimental validation. IEEE Trans. Ind. Electron. 2011, 58, 3448–3460. [Google Scholar] [CrossRef]

- Wang, F.; Zhang, H.; Ma, X. Analysis of slow-scale instability in boost PFC converter using the method of harmonic balance and floquet theory. IEEE Trans. Circuits Syst. I 2010, 57, 405–414. [Google Scholar] [CrossRef]

- Ma, W.; Wang, M.; Liu, S.; Li, S.; Yu, P. Stabilizing the average current-mode-controlled boost PFC converter via washout-filter-aided method. IEEE Trans. Circuits Syst. II Exp. Briefs 2011, 58, 595–599. [Google Scholar] [CrossRef]

- El Aroudi, A.; Haroun, R.; Cid-Pastor, A.; Martinez-Salamero, L. Suppression of Line Frequency Instabilities in PFC AC-DC Power Supplies by Feedback Notch Filtering the Pre-Regulator Output Voltage. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 796–809. [Google Scholar] [CrossRef]

- El Aroudi, A.; Orabi, M. Dynamics of PFC power converters subject to time-delayed feedback control. Int. J. Circuit Theory Appl. 2012, 40, 15–35. [Google Scholar] [CrossRef]

- Pyragas, K. Continuous control of chaos by self-controlling feedback. Phys. Lett. A 1992, 170, 421–428. [Google Scholar] [CrossRef]

- Maia, D.; Kurths, J.; Yanchuk, S. Stabilization of synchronous equilibria in regular dynamical networks with delayed coupling. Nonlinear Dyn. 2023, 111, 7377–7390. [Google Scholar] [CrossRef]

- Mohammadpour, M.; Abdelkefi, A.; Safarpour, P.; Gavagsaz-Ghoachani, R.; Zandi, M. Controlling chaos in bi-stable energy harvesting systems using delayed feedback control. Meccanica 2023, 58, 587–606. [Google Scholar] [CrossRef]

- Jafaripournimchahi, A.; Cai, Y.F.; Wang, H.; Sun, L. Environmental Analyses of Delayed-Feedback Control Effects in Continuum-Traffic Flow of Autonomous Vehicles. Sustainability 2022, 14, 11292. [Google Scholar] [CrossRef]

- Ma, W.; Wang, L.; Zhang, R.; Li, J.; Dong, Z.; Hu, M.; Liu, S. Hopf Bifurcation and Its Control in the One-Cycle Controlled Cuk Converter. IEEE Trans. Circuits Syst. II Express Briefs 2019, 8, 1411–1415. [Google Scholar] [CrossRef]

- Ma, W.; Zhang, R.; Wang, L.; Li, J.; Dong, Z.; Zhang, Y.; Hu, M. Stabilizing the buck converter with a first-order-filter-based time delay feedback controller. IEEE Access 2018, 6, 1967–1973. [Google Scholar] [CrossRef]

- Wong, S.C.; Tse, C.K.; Orabi, M.; Ninomiya, T. The method of double averaging: An approach for modeling power-factor-correction switching converters. IEEE Trans. Circuits Syst. 2006, 53, 454–462. [Google Scholar] [CrossRef]

- Orabi, M.; Haron, R.; Youssef, M.Z. Stability analysis of PFC converters with one-cycle control. In Proceedings of the 31st International Telecommunications Energy Conference, Incheon, Republic of Korea, 18–22 October 2009. [Google Scholar]

- Smedley, K.M.; Cuk, S. One-Cycle Control of Switching Converters. IEEE Trans. Power Electr. 1995, 10, 625–633. [Google Scholar] [CrossRef]

- Avrutin, V.; Zhusubaliyev, Z.T.; El Aroudi, A. Non-visible transformations of chaotic attractors due to their ultra-low density in AC-DC power factor correction converters. Nonlinear Dyn. 2020, 4, 2905–2924. [Google Scholar] [CrossRef]

- Avrutin, V.; Zhusubaliyev, Z.T.; Suissa, D.; El Aroudi, A. Non-observable chaos in piecewise smooth systems. Nonlinear Dyn. 2020, 99, 2031–2048. [Google Scholar] [CrossRef]

- Kim, S.; Bai, C.; Seok, H.; Choi, H.H.; Kim, M. Bridgeless Triple-Mode Resonant AC-DC Converter: Dynamic Modeling and Controls. IEEE Trans. Ind. Electron. 2020, 67, 4921–4933. [Google Scholar] [CrossRef]

- Caliskan, V.A.; Verghese, O.C.; Stankovic, A.M. Multifrequency averaging of DC/DC converters. IEEE Trans. Power Electron. 1999, 1, 124–133. [Google Scholar] [CrossRef]

- Khodabakhsh, J.; Moschopoulos, G. A Four-Switch Three-Phase AC-DC Converter with Galvanic Isolation. IEEE Trans. Power Electron. 2020, 35, 1699–1710. [Google Scholar] [CrossRef]

- Dorf, R.C.; Bishop, R.H. Modern Control Systems, 11th ed.; Pearson Education, Inc.: Upper Saddle River, NJ, USA; London, UK, 2008. [Google Scholar]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, R.; Dong, J.; Wang, L.; Ma, W.; Yin, G. Stabilizing the Boost PFC Converter with a Time Delay Feedback Controller. Electronics 2023, 12, 2291. https://doi.org/10.3390/electronics12102291

Zhang R, Dong J, Wang L, Ma W, Yin G. Stabilizing the Boost PFC Converter with a Time Delay Feedback Controller. Electronics. 2023; 12(10):2291. https://doi.org/10.3390/electronics12102291

Chicago/Turabian StyleZhang, Rui, Jie Dong, Lei Wang, Wei Ma, and Guofu Yin. 2023. "Stabilizing the Boost PFC Converter with a Time Delay Feedback Controller" Electronics 12, no. 10: 2291. https://doi.org/10.3390/electronics12102291

APA StyleZhang, R., Dong, J., Wang, L., Ma, W., & Yin, G. (2023). Stabilizing the Boost PFC Converter with a Time Delay Feedback Controller. Electronics, 12(10), 2291. https://doi.org/10.3390/electronics12102291