5.7 ps Resolution Time-to-Digital Converter Implementation Using Routing Path Delays

Abstract

:1. Introduction

2. Methodology

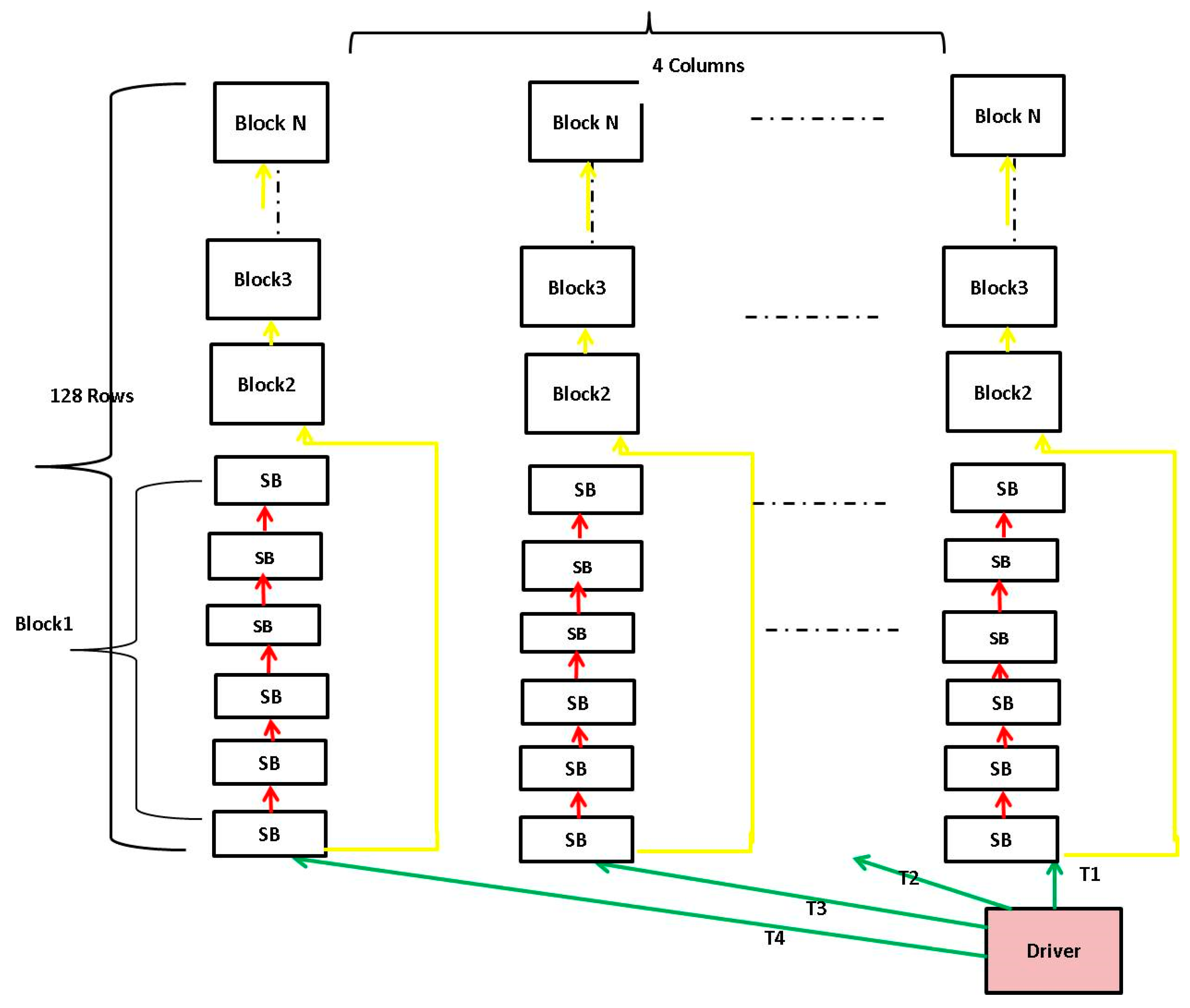

2.1. Principle and Architecture of the Implemented TDC

2.2. Enable Signal Generation

2.3. FPGA’s Routing Architecture (ZedBoard)

- Programmable logic blocks that implement logic functions;

- Programmable routing architecture that connects these logic blocks;

- Input/Output blocks connected to the logic blocks through the routing architecture to make off chip connections.

3. Experimental Results and Discussion

3.1. Implementation and Simulation Results

3.2. Parallel Delay Lines with Fixed Manual Routing of the EN Net

3.3. Experiments and Results

3.3.1. Histogram of the TDC

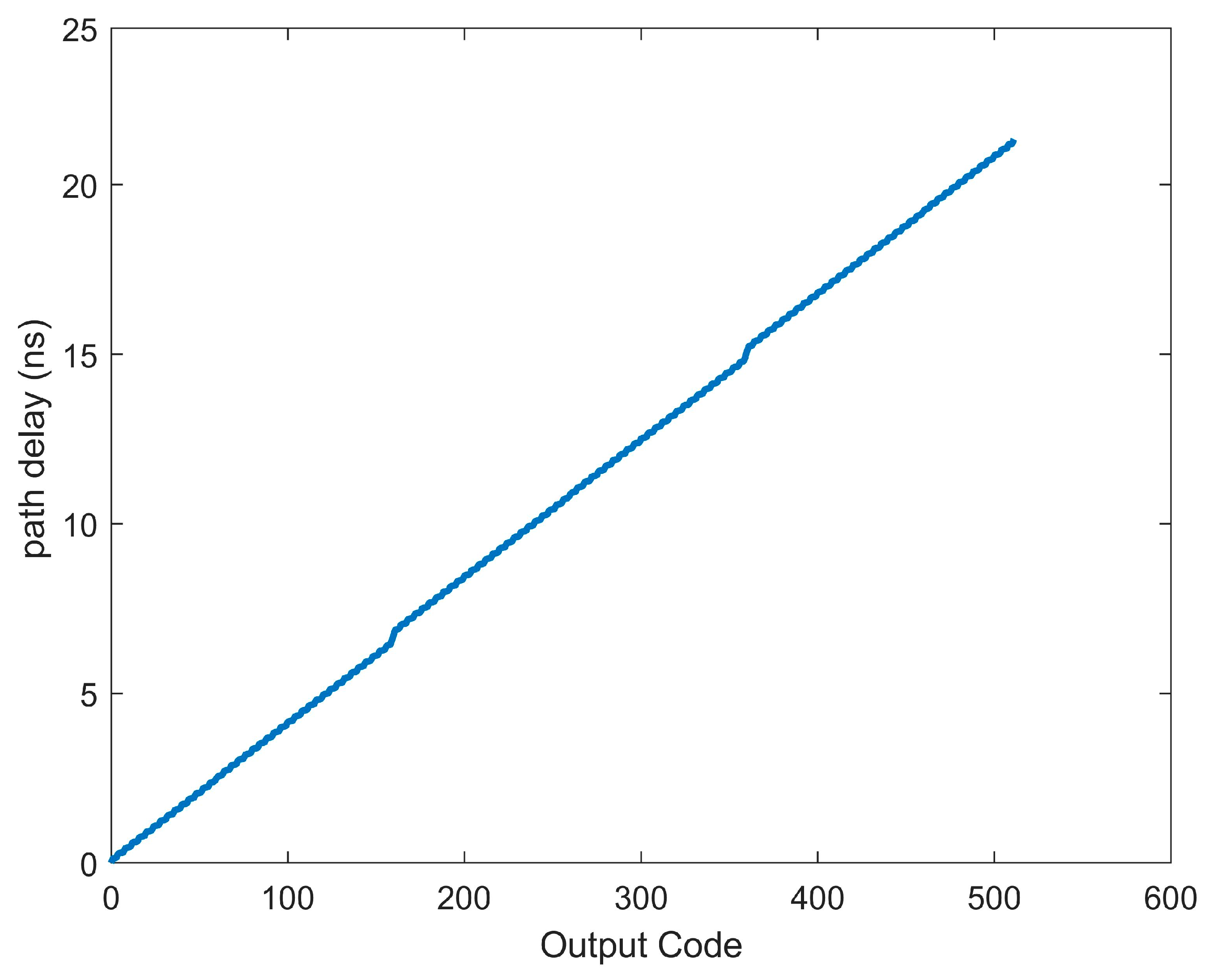

3.3.2. Transfer Function of the TDC

3.3.3. Non-Linearity of the TDC

3.3.4. Single-Shot Precision of the TDC

3.4. Comparison with Other TDCs

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Roberts, G.W.; Ali-Bakhshian, M. A brief introduction to time-to-digital and digital-to-time converters. IEEE Trans. Circuits Syst. II Express Briefs 2010, 57, 153–157. [Google Scholar] [CrossRef]

- Zhang, M.; Wang, H.; Liu, Y. A 7.4 ps FPGA-based TDC with a 1024-unit measurement matrix. Sensors 2017, 17, 865. [Google Scholar] [CrossRef]

- Van Bockel, B.; Leroux, P.; Prinzie, J. Tradeoffs in time-to-digital converter architectures for harsh radiation environments. IEEE Trans. Instrum. Meas. 2021, 70, 2005710. [Google Scholar] [CrossRef]

- Lai, J.; Luo, Y.; Shao, Q.; Bao, L.; Liu, X. A high-resolution TDC implemented in a 90 nm process FPGA. In Proceedings of the 2013 IEEE 10th International Conference on ASIC, Shenzhen, China, 28–31 October 2013; pp. 1–3. [Google Scholar]

- Tsai, T.-H.; Yuan, M.-S.; Chang, C.-H.; Liao, C.-C.; Li, C.-C.; Staszewski, R.B. 14.5 A 1.22 ps integrated-jitter 0.25-to-4 GHz fractional-N ADPLL in 16 nm FinFET CM0S. In Proceedings of the 2015 IEEE International Solid-State Circuits Conference-(ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 22–26 February 2015; pp. 1–3. [Google Scholar]

- Wu, W.; Staszewski, R.B.; Long, J.R. A 56.4-to-63.4 GHz multi-rate all-digital fractional-N PLL for FMCW radar applications in 65 nm CMOS. IEEE J. Solid-State Circ. 2014, 49, 1081–1096. [Google Scholar] [CrossRef]

- Prinzie, J.; Steyaert, M.; Leroux, P. A single shot TDC with 4.8 ps resolution in 40 nm CMOS for high energy physics applications. J. Instrum. 2015, 10, C01031. [Google Scholar] [CrossRef]

- Fishburn, M.; Menninga, L.H.; Favi, C.; Charbon, E. A 19.6 ps, FPGA-based TDC with multiple channels for open source applications. IEEE Trans. Nucl. Sci. 2013, 60, 2203–2208. [Google Scholar] [CrossRef]

- Kwiatkowski, P.K. Employing FPGA DSP blocks for time-to-digital conversion. Metrol. Meas. Syst. 2019, 26, 631–643. [Google Scholar]

- Cui, K.; Ren, Z.; Li, X.; Liu, Z.; Zhu, R. A high-linearity, ring-oscillator-based, Vernier time-to-digital converter utilizing carry chains in FPGAs. IEEE Trans. Nucl. Sci. 2016, 64, 697–704. [Google Scholar] [CrossRef]

- Mattada, M.P.; Guhilot, H. Time-to-digital converters—A comprehensive review. Int. J. Circuit Theory Appl. 2021, 49, 778–800. [Google Scholar] [CrossRef]

- Dikopoulos, E.; Birbas, M.; Birbas, A. An Adaptive Downsampling FPGA-Based TDC Implementation for Time Measurement Improvement. Chips 2022, 1, 175–190. [Google Scholar] [CrossRef]

- Fan, H.-H.; Cao, P.; Liu, S.-B.; An, Q. TOT measurement implemented in FPGA TDC. Chin. Phys. C 2015, 39, 116101. [Google Scholar] [CrossRef]

- Tontini, A.; Gasparini, L.; Pancheri, L.; Passerone, R. Design and characterization of a low-cost FPGA-based TDC. IEEE Trans. Nucl. Sci. 2018, 65, 680–690. [Google Scholar] [CrossRef]

- Dudek, P.; Szczepanski, S.; Hatfield, J.V. A high-resolution CMOS time-to-digital converter utilizing a Vernier delay line. IEEE J. Solid-State Circ. 2000, 35, 240–247. [Google Scholar] [CrossRef]

- Cui, K.; Li, X.; Liu, Z.; Zhu, R. Toward implementing multichannels, ring-oscillator-based, Vernier time-to-digital converter in FPGAs: Key design points and construction method. IEEE Trans. Radiat. Plasma Med. Sci. 2017, 1, 391–399. [Google Scholar] [CrossRef]

- Zhang, J.; Zhou, D. An 8.5-ps two-stage Vernier delay-line loop shrinking time-to-digital converter in 130-nm flash FPGA. IEEE Trans. Instrum. Meas. 2017, 67, 406–414. [Google Scholar] [CrossRef]

- Van Bockel, B.; Prinzie, J.; Cao, Y.; Leroux, P. A delay locked loop for time-to-digital converterswith quick recovery and low hysteresis. In Proceedings of the TWEPP 2018 Topical Workshop on Electronics for Particle Physics, Antwerpen, Belgium, 17–21 September 2019. [Google Scholar]

- Wang, Y.; Xie, W.; Chen, H.; Li, D.D.-U. High-resolution time-to-digital converters (TDCs) with a bidirectional encoder. Measurement 2023, 206, 112258. [Google Scholar] [CrossRef]

- Liu, C.; Wang, Y. A 128-channel, 710 M samples/second, and less than 10 ps RMS resolution time-to-digital converter implemented in a Kintex-7 FPGA. IEEE Trans. Nucl. Sci. 2015, 62, 773–783. [Google Scholar] [CrossRef]

- Wang, Y.; Liu, C.; Cheng, X.; Li, D. Spartan-6 FPGA based 8-channel time-to-digital converters for TOF-PET systems. In Proceedings of the 2015 IEEE Nuclear Science Symposium and Medical Imaging Conference (NSS/MIC), San Diego, CA, USA, 3–5 November 2015; pp. 1–3. [Google Scholar]

- Amiri, A.M.; Boukadoum, M.; Khouas, A. A multihit time-to-digital converter architecture on FPGA. IEEE Trans. Instrum. Meas. 2008, 58, 530–540. [Google Scholar] [CrossRef]

- Daigneault, M.-A.; David, J.P. A high-resolution time-to-digital converter on FPGA using dynamic reconfiguration. IEEE Trans. Instrum. Meas. 2011, 60, 2070–2079. [Google Scholar] [CrossRef]

- Wang, H.; Zhang, M.; Yao, Q. A new realization of time-to-digital converters based on FPGA internal routing resources. IEEE Trans. Ultrason. Ferroelectr. Freq. Control 2013, 60, 1787–1795. [Google Scholar] [CrossRef]

- Prado, D.F.G. Tutorial on FPGA routing. Electrón.-UNMSM 2006, 17, 23–33. [Google Scholar]

- Huang, H. A 0.1 ps Resolution Coarse-Fine Time-to-Digital Converter with 2.21 ps Single-Shot Precision. Ph.D. Thesis, The University of Texas at Dallas, Richardson, TX, USA, 2018. [Google Scholar]

- Brown, S.; Rose, J. Architecture of FPGAs and CPLDs: A tutorial. IEEE Des. Test Comput. 1996, 13, 42–57. [Google Scholar] [CrossRef]

- Farooq, U.; Marrakchi, Z.; Mehrez, H.; Farooq, U.; Marrakchi, Z.; Mehrez, H. FPGA architectures: An overview. In Tree-Based Heterogeneous FPGA Architectures: Application Specific Exploration and Optimization; Springer: Berlin/Heidelberg, Germany, 2012; pp. 7–48. [Google Scholar]

- Avnet. ZedBoard (Zynq Evaluation and Development) Hardware User’s Guide, Version 2.2; Avnet: Phoenix, AZ, USA, 2014. [Google Scholar]

- Farooq, U.; Marrakchi, Z.; Mehrez, H. Tree-Based Heterogeneous FPGA Architectures: Application Specific Exploration and Optimization; Springer Science & Business Media: Berlin/Heidelberg, Germany, 2012. [Google Scholar]

- Hanselman, D.C.; Littlefield, B.L. Mastering Matlab; Prentice Hall Press: Hoboken, NJ, USA, 2011. [Google Scholar]

- Wang, Y.; Liu, C. A nonlinearity minimization-oriented resource-saving time-to-digital converter implemented in a 28 nm Xilinx FPGA. IEEE Trans. Nucl. Sci. 2015, 62, 2003–2009. [Google Scholar] [CrossRef]

| 512-Unit TDC | 1024-Unit TDC | ||||

|---|---|---|---|---|---|

| Available | Used | Utilization (%) | Used | Utilization (%) | |

| Slice registers | 106,400 | 25,290 | 23.77 | 41,175 | 38.70 |

| Slice LUTs | 53,200 | 16,864 | 31.70 | 25,819 | 48.53 |

| LUTs as logic | 53,200 | 11,288 | 21.22 | 16,875 | 31.72 |

| LUTs as memory | 17,400 | 5576 | 32.05 | 8944 | 51.40 |

| Slices | 13,300 | 6947 | 52.23 | 11,041 | 83.02 |

| Block RAM | 140 | 32.5 | 23.21 | 32.5 | 23.21 |

| BUFGCTRL | 32 | 7 | 21.88 | 8 | 25.00 |

| MMCME2-ADV | 4 | 3 | 75 | 3 | 75 |

| Work | This Work | [2] (2017) | [4] (2013) | [8] (2013) | [9] (2019) | [12] (2022) | [19] (2023) | [32] (2015) |

|---|---|---|---|---|---|---|---|---|

| Method | Counters based on delay lines | Counters based on delay lines | Carry4 delay line | Carry4 delay line | DSP delay lines | Carry4 delay line | Carry4 delay line with WU +dual sampling | Carry4 delay line with calibration |

| FPGA process technology | 28 nm | 65 nm | 90 nm | 40 nm | 28 nm | 40 nm | 16 nm | 28 nm |

| Number of bins | 16,384 | 1024 | 256 | - | 480 | 300 | 6000 | 80 |

| Reference frequency | 171 MHz | 133.3 MHz | 115 MHz | - | 700 MHz | - | 450 MHz | 710 MHz |

| Resolution | 5.7 ps | 7.4 ps | 48 ps | 19. 6 ps | 4.2 ps | 20 ps | 0.46 ps | 15 ps (rms) |

| DNL | 0.4312 LSB (rms) | 0.74 LSB | - | 1.5 LSB | 20 LSB | 0.3 LSB (rms) | 6.84 LSB | 1 LSB |

| INL | 2.1545 LSB (rms) | 1.57 LSB | - | 1. 61 LSB | 31.54 LSB | 0.45 LSB (rms) | 72. 55 LSB | 0.8 LSB |

| Dynamic range | 93.6 ns | - | 6.150 ns | - | 4 ns | 3.2 ns | - | - |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Siecha, R.T.; Alemu, G.; Prinzie, J.; Leroux, P. 5.7 ps Resolution Time-to-Digital Converter Implementation Using Routing Path Delays. Electronics 2023, 12, 3478. https://doi.org/10.3390/electronics12163478

Siecha RT, Alemu G, Prinzie J, Leroux P. 5.7 ps Resolution Time-to-Digital Converter Implementation Using Routing Path Delays. Electronics. 2023; 12(16):3478. https://doi.org/10.3390/electronics12163478

Chicago/Turabian StyleSiecha, Roza Teklehaimanot, Getachew Alemu, Jeffrey Prinzie, and Paul Leroux. 2023. "5.7 ps Resolution Time-to-Digital Converter Implementation Using Routing Path Delays" Electronics 12, no. 16: 3478. https://doi.org/10.3390/electronics12163478

APA StyleSiecha, R. T., Alemu, G., Prinzie, J., & Leroux, P. (2023). 5.7 ps Resolution Time-to-Digital Converter Implementation Using Routing Path Delays. Electronics, 12(16), 3478. https://doi.org/10.3390/electronics12163478