A 10-Bit 400 MS/s Dual-Channel Time-Interleaved SAR ADC Based on Comparator Multiplexing

Abstract

:1. Introduction

2. Design Considerations

2.1. Conventional Architecture of TI-SAR ADC

2.2. Offset Mismatch in TI-SAR ADC

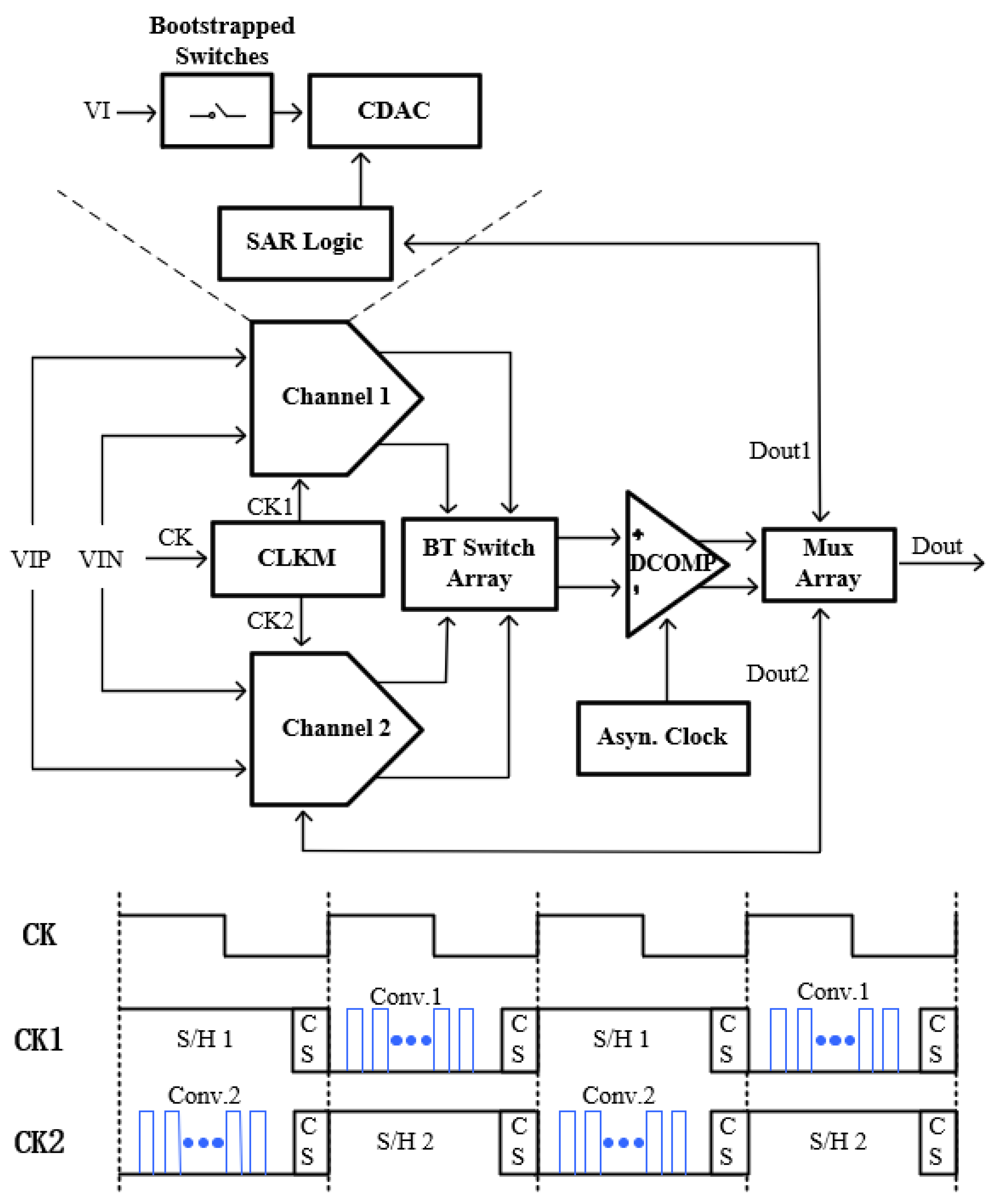

2.3. Comparator Multiplexing TI-SAR ADC

3. Circuit Implementation

3.1. Dual-Channel TI-SAR ADC

3.2. Split CDAC

3.3. Unit Capacitor

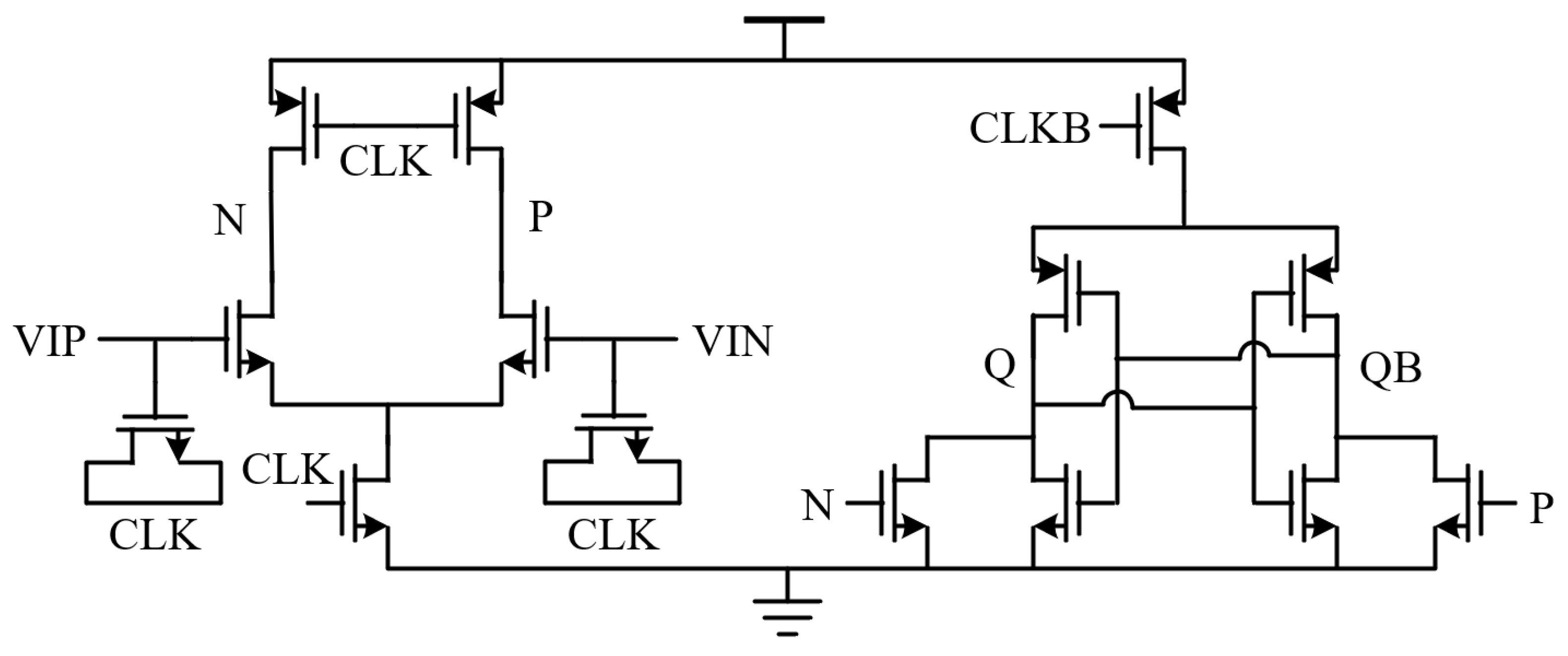

3.4. Double-Tail Dynamic Comparator with Clock Decoupling

3.5. BT Switch

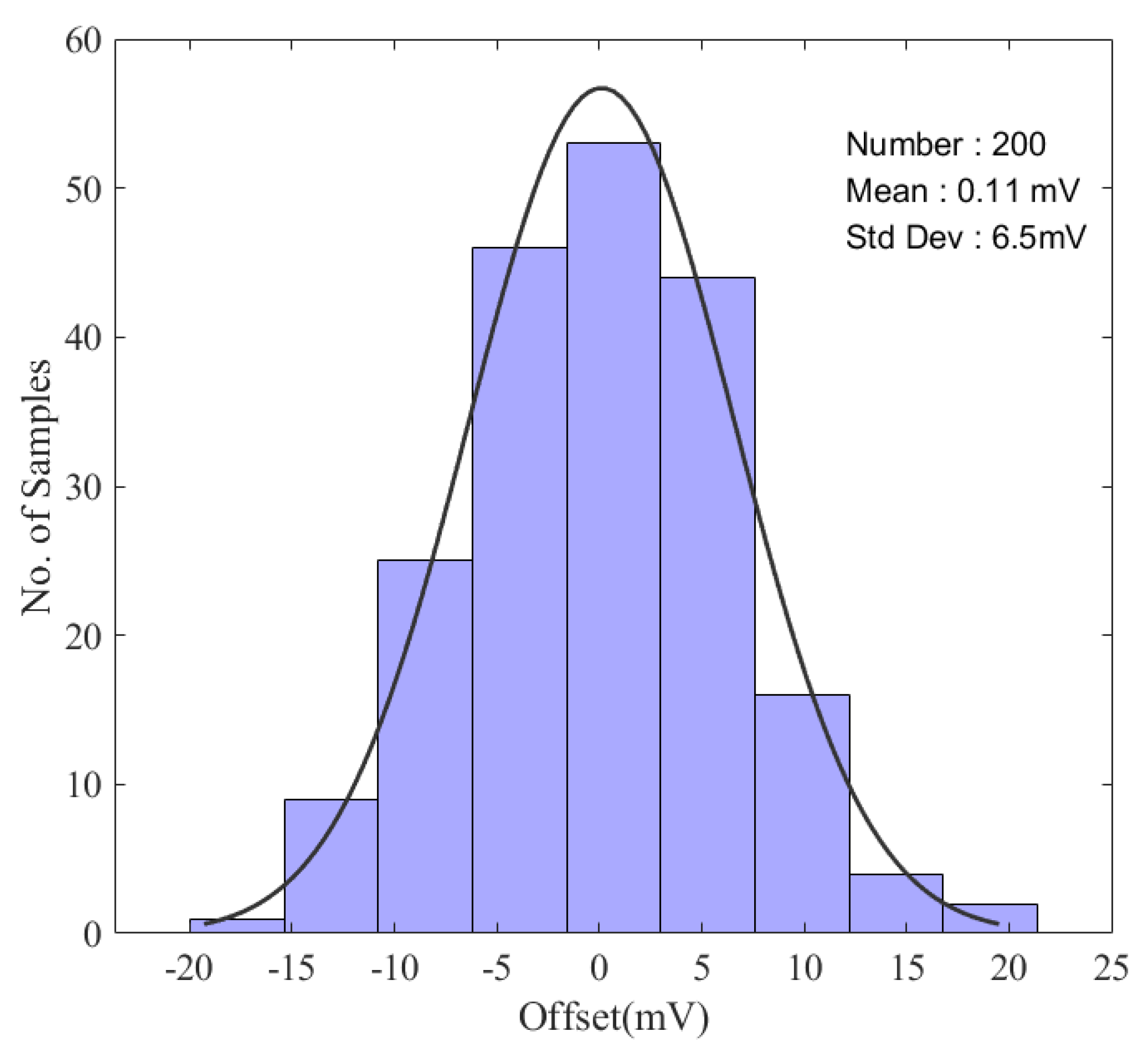

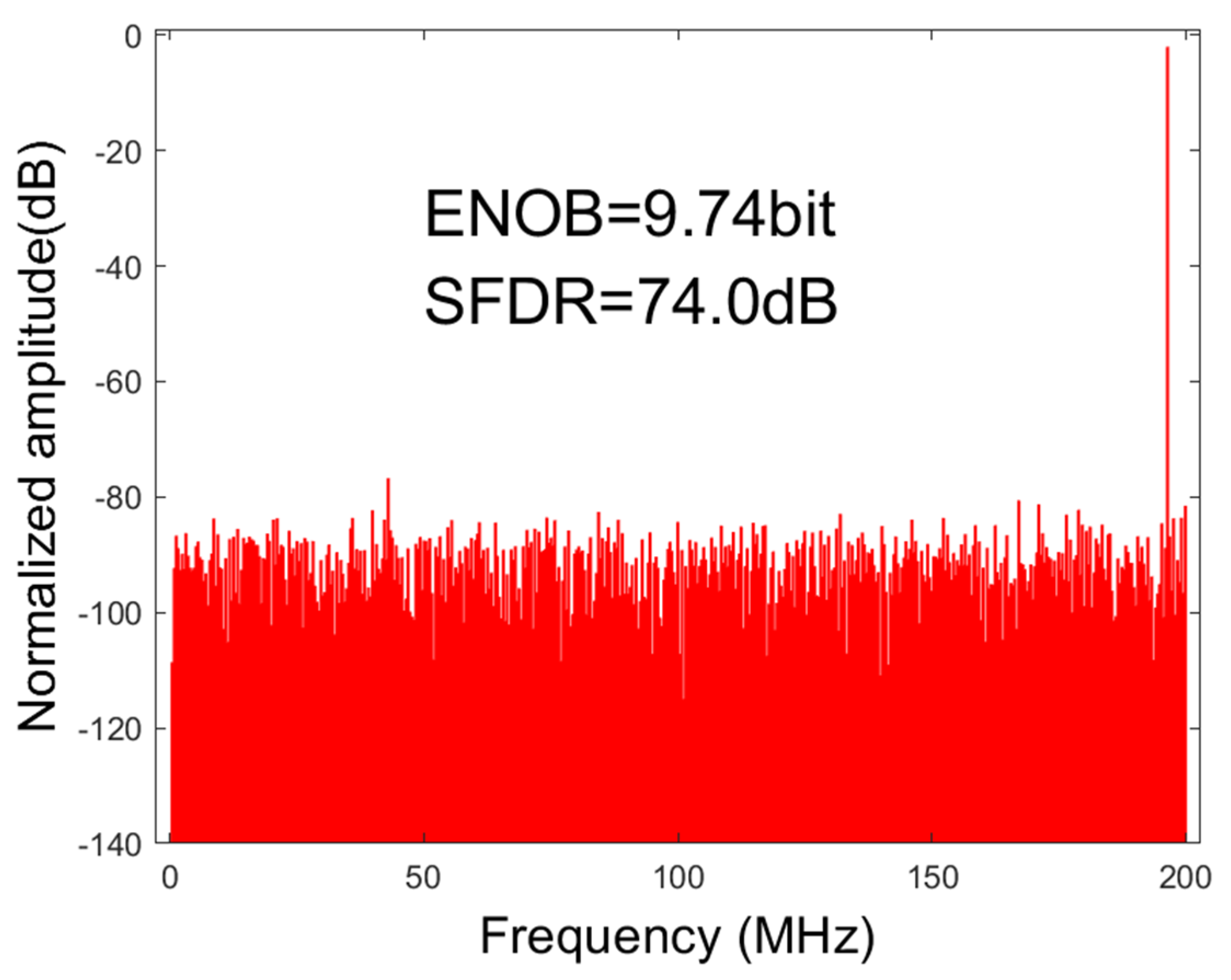

4. Simulation Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Liu, C.C.; Chang, S.J.; Huang, G.Y.; Lin, Y.Z.; Huang, C.M.; Huang, C.H.; Bu, L.; Tsai, C.C. A 10b 100MS/s 1.13mW SAR ADC with binary-scaled error compensation. In Proceedings of the 2010 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 7–11 February 2010; pp. 386–387. [Google Scholar]

- Liu, C.C.; Kuo, C.H.; Lin, Y.Z. A 10 bit 320 MS/s Low-Cost SAR ADC for IEEE 802.11ac Applications in 20 nm CMOS. IEEE J. Solid-State Circuits 2015, 50, 2645–2654. [Google Scholar] [CrossRef]

- Chan, C.H.; Zhu, Y.; Li, C.; Zhang, W.H.; Ho, I.M.; Wei, L.; Seng-Pan, U.; Martins, R.P. 60-dB SNDR 100-MS/s SAR ADCs with Threshold Reconfigurable Reference Error Calibration. IEEE J. Solid-State Circuits 2017, 52, 2576–2588. [Google Scholar] [CrossRef]

- Qiu, L.; Tang, K.; Zheng, Y.; Siek, L. A Flexible-Weighted Nonbinary Searching Technique for High-Speed SAR-ADCs. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2016, 24, 2808–2812. [Google Scholar] [CrossRef]

- Zhu, Y.; Chan, C.H.; Seng-Pan, U.; Martins, R.P. An 11b 450 MS/s Three-Way Time-Interleaved Subranging Pipelined-SAR ADC in 65 nm CMOS. IEEE J. Solid-State Circuits 2016, 51, 1223–1234. [Google Scholar] [CrossRef]

- Song, J.; Tang, X.; Sun, N. A 10-b 2b/cycle 300MS/s SAR ADC with a single differential DAC in 40nm CMOS. In Proceedings of the 2017 IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, USA, 30 April–3 May 2017; pp. 1–4. [Google Scholar]

- Moon, K.J.; Kang, H.W.; Jo, D.S.; Kim, M.Y.; Baek, S.Y.; Choi, M.; Ko, H.J.; Ryu, S.T. A 9.1 ENOB 21.7fJ/conversion-step 10b 500MS/s single-channel pipelined SAR ADC with a current-mode fine ADC in 28nm CMOS. In Proceedings of the 2017 Symposium on VLSI Circuits, Kyoto, Japan, 5–8 June 2017; pp. C94–C95. [Google Scholar]

- Kull, L.; Luu, D.; Menolfi, C.; Braendli, M.; Francese, P.A.; Morf, T.; Kossel, M.; Yueksel, H.; Cevrero, A.; Ozkaya, I.; et al. 28.5 A 10b 1.5GS/s pipelined-SAR ADC with background second-stage common-mode regulation and offset calibration in 14nm CMOS FinFET. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 474–475. [Google Scholar]

- Yu, Q.; Zhou, X.; Hu, K.; Huang, Z.; Chen, H.; Si, X.; Yang, J.; Li, Q. A 9.08 ENOB 10b 400MS/s Subranging SAR ADC with Subsetted CDAC and PDAS in 40nm CMOS. In Proceedings of the ESSCIRC 2021—IEEE 47th European Solid State Circuits Conference (ESSCIRC), Grenoble, France, 13–22 September 2021; pp. 391–394. [Google Scholar]

- Wang, J.C.; Li, B.Y.; Kuo, T.H. A 9.8-fJ/conv.-step FoMW 8b 2.5-GS/s Single-Channel CDAC-Assisted Subranging ADC with Reference-Embedded Comparators. In Proceedings of the 2022 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Honolulu, HI, USA, 12–17 June 2022; pp. 92–93. [Google Scholar]

- Hu, Y.S.; Shih, C.H.; Tai, H.Y.; Chen, H.W.; Chen, H.S. A 0.6V 6.4fJ/conversion-step 10-bit 150MS/s subranging SAR ADC in 40nm CMOS. In Proceedings of the 2014 IEEE Asian Solid-State Circuits Conference (A-SSCC), KaoHsiung, Taiwan, 10–12 November 2014; pp. 81–84. [Google Scholar]

- Chan, C.H.; Zhu, Y.; Zhang, W.H.; Seng-Pan, U.; Martins, R.P. A Two-Way Interleaved 7-b 2.4-GS/s 1-Then-2 b/Cycle SAR ADC with Background Offset Calibration. IEEE J. Solid-State Circuits 2018, 53, 850–860. [Google Scholar] [CrossRef]

- Fan, Q.; Hong, Y.; Chen, J. A Time-Interleaved SAR ADC with Bypass-Based Opportunistic Adaptive Calibration. IEEE J. Solid-State Circuits 2020, 55, 2082–2093. [Google Scholar] [CrossRef]

- Li, D.; Zhu, Z.; Liu, J.; Zhuang, H.; Yang, Y.; Sun, N. A 7-bit 900-MS/s 2-Then-3-bit/cycle SAR ADC with Background Offset Calibration. IEEE J. Solid-State Circuits 2020, 55, 3051–3063. [Google Scholar] [CrossRef]

- Chung, Y.H.; Hsu, Y.M. A 12-Bit 100-MS/s Subrange SAR ADC with a Foreground Offset Tracking Calibration Scheme. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 1094–1098. [Google Scholar] [CrossRef]

- Ding, M.; Harpe, P.; Liu, Y.H.; Busze, B.; Philips, K.; De Groot, H. A 46 μW 13 b 6.4 MS/s SAR ADC with Background Mismatch and Offset Calibration. IEEE J. Solid-State Circuits 2017, 52, 423–432. [Google Scholar] [CrossRef]

- Hsu, C.W.; Chang, S.J. A 1.6-GS/s 8b Flash-SAR Time-Interleaved ADC with Top-Plate Residue Based Gain Calibration. In Proceedings of the 2021 IEEE International Symposium on Circuits and Systems (ISCAS), Daegu, Republic of Korea, 22–28 May 2021; pp. 1–5. [Google Scholar]

- Zhu, Y.; Chan, C.H.; Seng-Pan, U.; Martins, R.P. A 10-bit 500-MS/s Partial-Interleaving Pipelined SAR ADC with Offset and Reference Mismatch Calibrations. IEEE Trans. Very Large Scale Integr. Syst. 2017, 25, 354–363. [Google Scholar] [CrossRef]

- Lopez-Angulo, A.; Gines, A.; Peralias, E. Calibration of Capacitor Mismatch and Static Comparator Offset in SAR ADC with Digital Redundancy. In Proceedings of the 2020 IEEE International Symposium on Circuits and Systems (ISCAS), Seville, Spain, 12–14 October 2020; pp. 1–5. [Google Scholar]

- Bichan, M.; Carusone, A.C. The effect of redundancy on mismatch-induced offset and random noise in a dynamic comparator. In Proceedings of the 2009 Ph.D. Research in Microelectronics and Electronics, Cork, Ireland, 12–17 July 2009; pp. 180–183. [Google Scholar]

- Kurosawa, N.; Kobayashi, H.; Maruyama, K.; Sugawara, H.; Kobayashi, K. Explicit analysis of channel mismatch effects in time-interleaved ADC systems. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 2001, 48, 261–271. [Google Scholar] [CrossRef]

- Kull, L.; Pliva, J.; Toifl, T.; Schmatz, M.; Francese, P.A.; Menolfi, C.; Brändli, M.; Kossel, M.; Morf, T.; Andersen, T.M.; et al. Implementation of Low-Power 6–8 b 30–90 GS/s Time-Interleaved ADCs with Optimized Input Bandwidth in 32 nm CMOS. IEEE J. Solid-State Circuits 2016, 51, 636–648. [Google Scholar] [CrossRef]

- Tripathi, V.; Murmann, B. An 8-bit 450-MS/s single-bit/cycle SAR ADC in 65-nm CMOS. In Proceedings of the 2013 Proceedings of the ESSCIRC (ESSCIRC), Bucharest, Romania, 16–20 September 2013; pp. 117–120. [Google Scholar]

- Chen, J.; Xing, X.; Yang, Z.; Feng, H.; Wang, Z. A 10-bit 200MS/s SAR ADC with reference buffer in 40nm CMOS. In Proceedings of the 2020 IEEE 15th International Conference on Solid-State & Integrated Circuit Technology (ICSICT), Kunming, China, 3–6 November 2020; pp. 1–3. [Google Scholar]

- Shen, L.; Li, F.; Wang, Z. A 10b 50 MS/s single-Channel asynchronous SAR ADC with two alternate comparators and comparator calibration. In Proceedings of the 2019 IEEE International Conference on Integrated Circuits, Technologies and Applications (ICTA), Chengdu, China, 13–15 November 2019; pp. 35–36. [Google Scholar]

- Yasin Adıyaman, M.; Karalar, T.C. Time-interleaved SAR ADC design with background calibration. Int. J. Circuit Theory Appl. 2020, 48, 321–334. [Google Scholar] [CrossRef]

- Xing, D.; Zhu, Y.; Chan, C.H.; Maloberti, F.; Seng-Pan, U.; Martins, R.P. Design of a High-Speed Time-Interleaved Sub-Ranging SAR ADC with Optimal Code Transfer Technique. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 66, 489–501. [Google Scholar] [CrossRef]

| Bit | Phase | CK1/2 | BT | SWPP | SWNN | SWPN | SWNP | |

|---|---|---|---|---|---|---|---|---|

| MSB | Sampling | 1 | 1 | 1 | 0 | 0 | 1 | |

| Charge transfer | 0 | 0 | 0 | 1 | 0 | 1 | ||

| conversion | Q = 1 | 0 | 0 | 1 | 1 | 1 | 1 | |

| Q = 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||

| Specifications | This Work *,a | [5] b | [6] b | [18] b | [25] a | [26] a | [27] b | |

|---|---|---|---|---|---|---|---|---|

| Technology | 40 nm | 40 nm | 65 nm | 40 nm | 65 nm | 180 nm | 40 nm | 65 nm |

| Architecture | Comp. mux. TI-SAR | TI-SAR | TI- Subranging Pipe-SAR | 2 b/cycle SAR | Partial-Interleaving Pipe-SAR | Two Comp. SAR | TI- SAR | TI- Subranging SAR |

| Num. of channels | 2 | 2 | 3 | 1 | 1/2 | 1 | 18 | 2 |

| Calibration | no | no | yes | no | yes | yes | yes | yes |

| Resolution (bit) | 10 | 10 | 11 | 10 | 10 | 10 | 10 | 10 |

| Sampling Rate (MS/s) | 400 | 400 | 450 | 300 | 500 | 50 | 2000 | 700 |

| SNDR @Nyq. (dB) | 60.2 (w/offset) | 31.9 (w/offset) | 56.2 | 47.0 | 52.9 | 61.3 | 52.3 | 53.3 |

| SFDR @Nyq. (dB) | 77.2 | 32.2 | 65.5 | 63.0 | 66.0 | 75.3 | 62.0 | 70.4 |

| Power (mW) | 2.40 | 2.20 | 7.40 | 2.10 | 8.20 | 6.60 | 10.5 | 9.50 |

| FOM @Nyq. (fJ/conv.-step) | 7.2 | 171.9 | 31.2 | 38.3 | 46.0 | 139.4 | 24.2 | 36.0 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, C.; Yang, Z.; Xing, X.; Duan, Q.; Zheng, X.; Gielen, G. A 10-Bit 400 MS/s Dual-Channel Time-Interleaved SAR ADC Based on Comparator Multiplexing. Electronics 2023, 12, 4062. https://doi.org/10.3390/electronics12194062

Wang C, Yang Z, Xing X, Duan Q, Zheng X, Gielen G. A 10-Bit 400 MS/s Dual-Channel Time-Interleaved SAR ADC Based on Comparator Multiplexing. Electronics. 2023; 12(19):4062. https://doi.org/10.3390/electronics12194062

Chicago/Turabian StyleWang, Cheng, Zhanpeng Yang, Xinpeng Xing, Quanzhen Duan, Xinfa Zheng, and Georges Gielen. 2023. "A 10-Bit 400 MS/s Dual-Channel Time-Interleaved SAR ADC Based on Comparator Multiplexing" Electronics 12, no. 19: 4062. https://doi.org/10.3390/electronics12194062