A 121 dB SNDR Zoom ADC Using Dynamic Amplifier and Asynchronous SAR Quantizer

Abstract

1. Introduction

2. Zoom ADC System Design

2.1. Zoom ADC Architecture

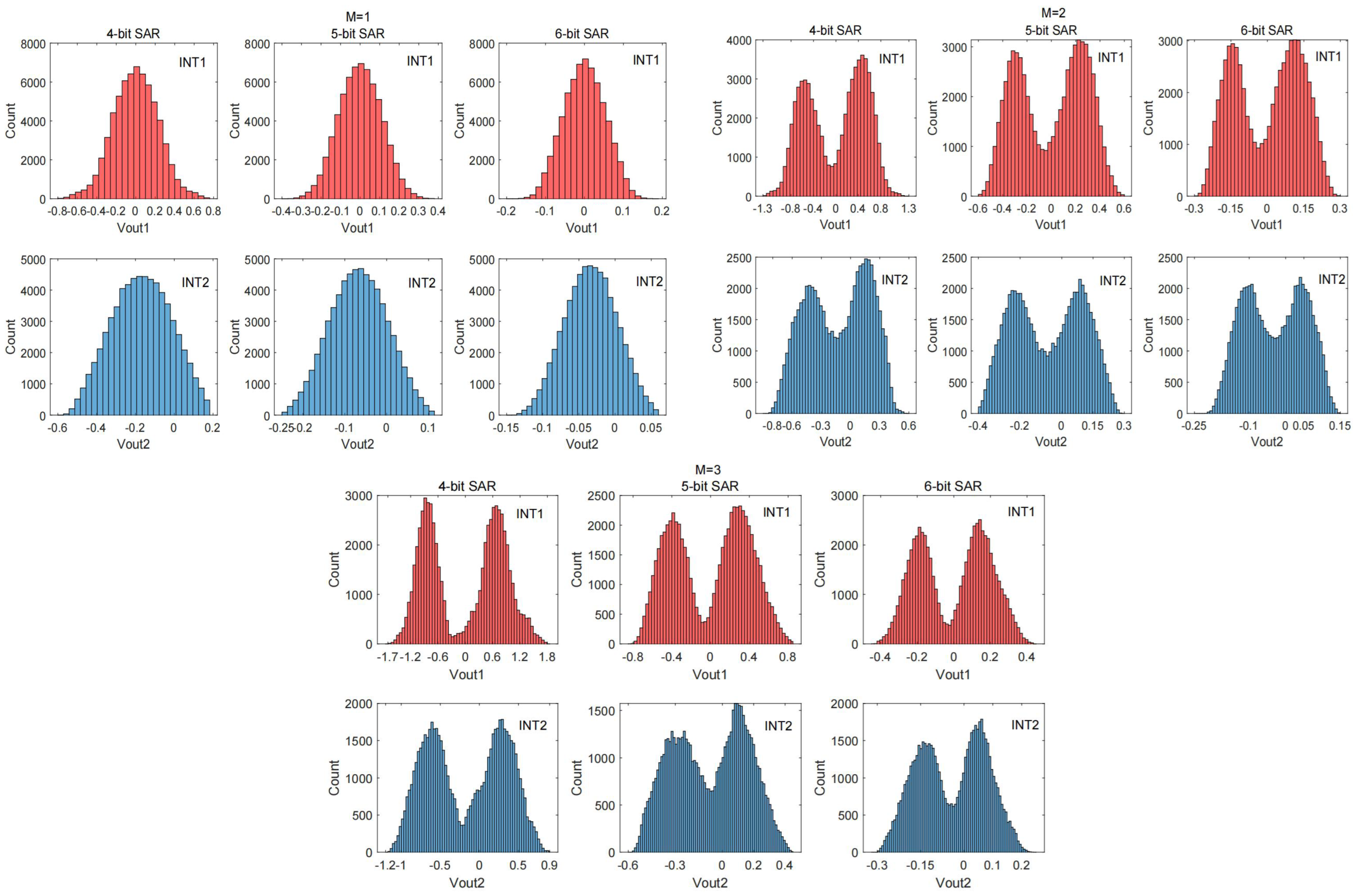

2.2. Maximum Input Frequency and Coarse Conversion Resolution

2.3. Amplifier Gain Error

3. Circuit Implementation

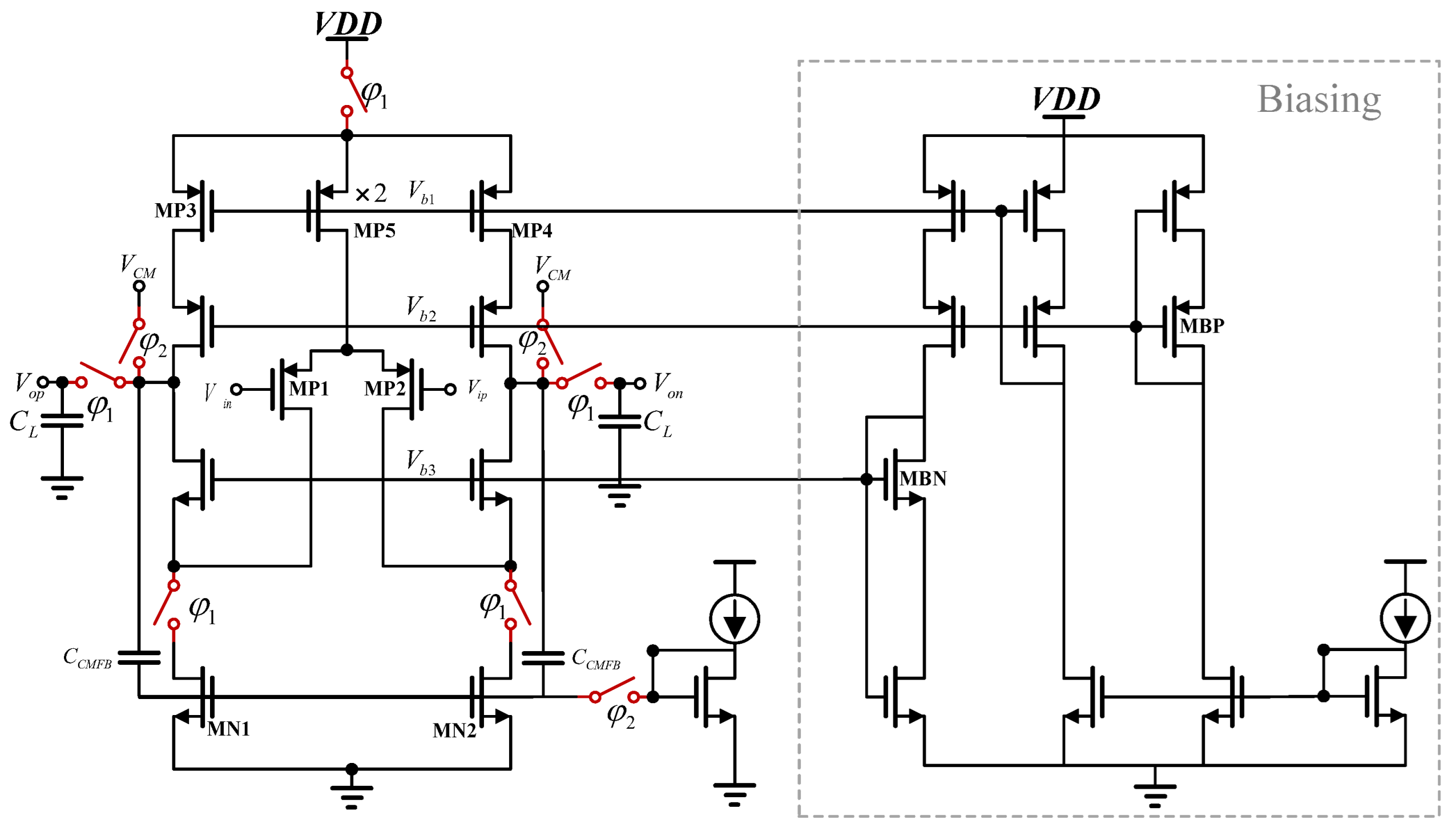

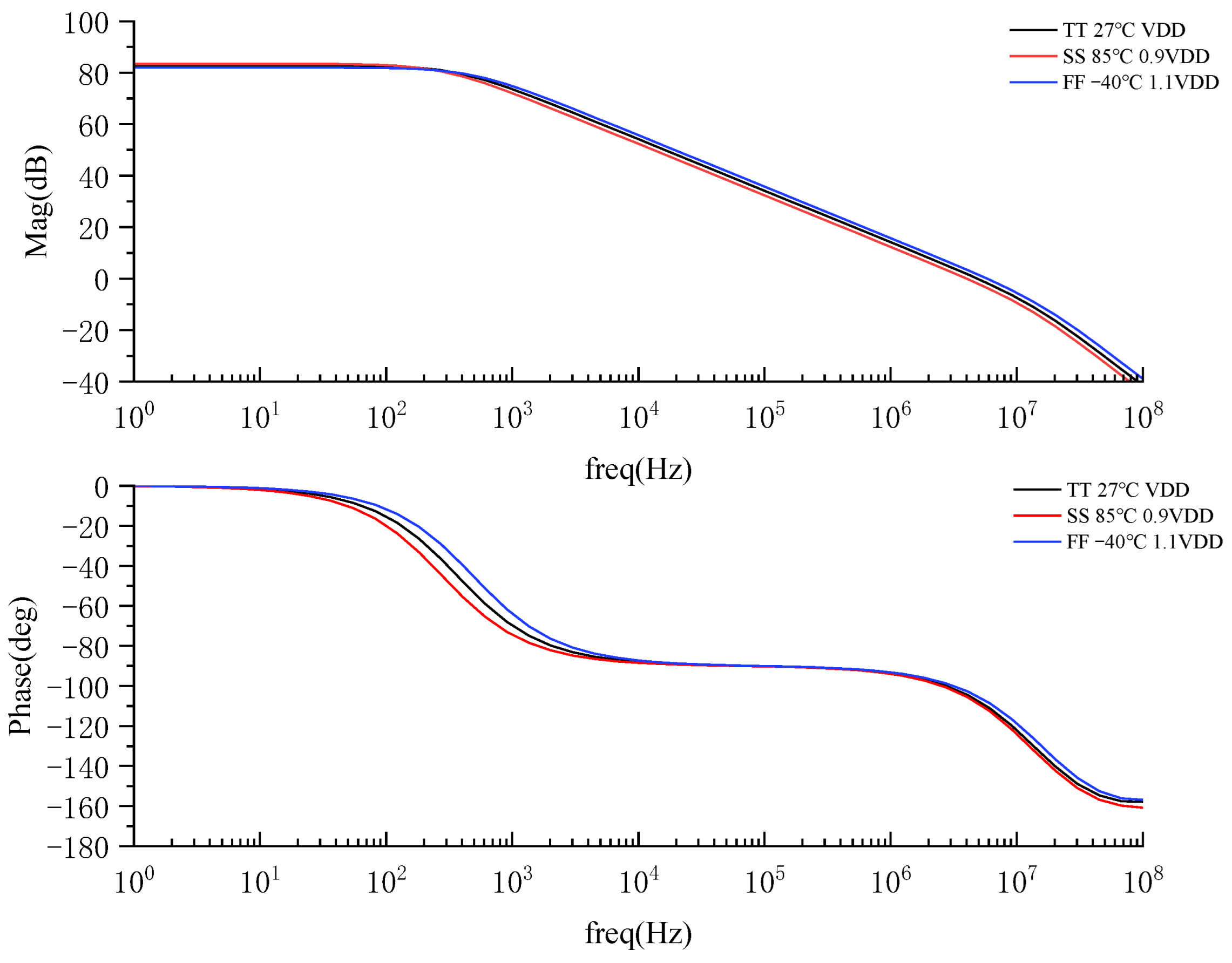

3.1. Dynamic Amplifier

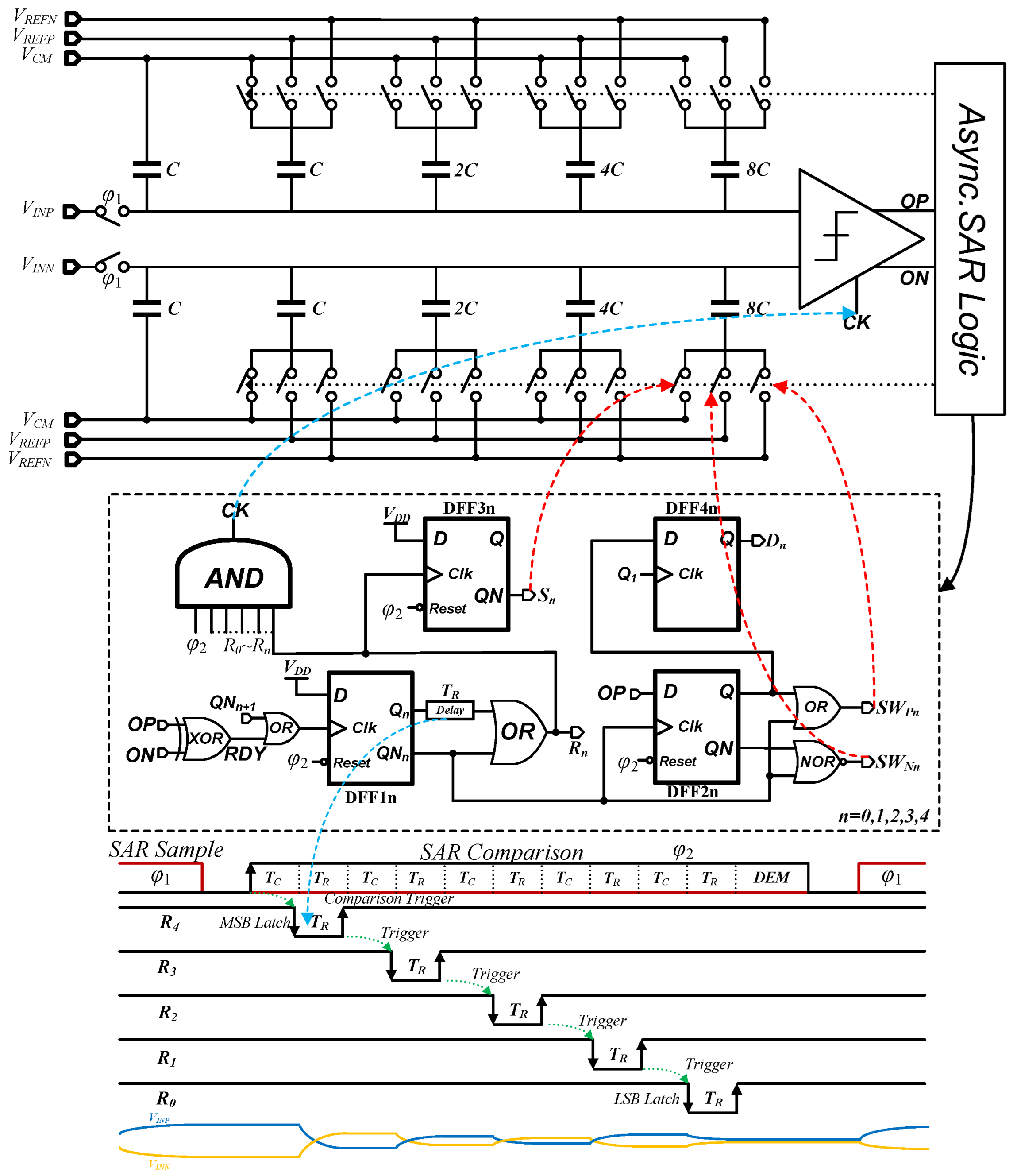

3.2. Coarse Conversion Asynchronous SAR ADC

3.3. Feedforward Adder Embedded 2-Bit SAR Quantizer

3.4. Dynamic Element Matching and Digital Logic

4. Simulation Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Ye, Y.; Liu, L.; Li, J.; Li, D.; Wang, Z. A 120 dB SNDR audio sigma-delta modulator with an asynchronous SAR quantizer. In Proceedings of the 2012 IEEE International Symposium on Circuits and Systems (ISCAS), Seoul, Republic of Korea, 20–23 May 2012; pp. 2357–2360. [Google Scholar] [CrossRef]

- Dorrer, L.; Kuttner, F.; Santner, A.; Kropf, C.; Hartig, T.; Torta, P.; Greco, P. A 2.2 mW, Continuous-Time Sigma-Delta ADC for Voice Coding with 95dB Dynamic Range in a 65 nm CMOS Process. In Proceedings of the 32nd European Solid-State Circuits Conference, Montreux, Switzerland, 19–21 September 2006; pp. 195–198. [Google Scholar] [CrossRef]

- Brewer, R.; Gorbold, J.; Hurrell, P.; Lyden, C.; Maurino, R.; Vickery, M. A 100 dB SNR 2.5 MS/s output data rate /spl Delta//spl Sigma/ ADC. In Proceedings of the ISSCC—2005 IEEE International Digest of Technical Papers. Solid-State Circuits Conference, San Francisco, CA, USA, 10 February 2005; Volume 1, pp. 172–591. [Google Scholar] [CrossRef]

- Gharbiya, A.; Johns, D.A. A 12-bit 3.125-MHz bandwidth 0–3 MASH delta-sigma modulator. In Proceedings of the ESSCIRC 2008—34th European Solid-State Circuits Conference, Edinburgh, UK, 15–19 September 2008; pp. 206–209. [Google Scholar] [CrossRef]

- Liu, J.; Li, D.; Zhong, Y.; Tang, X.; Sun, N. 27.1 A 250 kHz-BW 93 dB-SNDR 4th-Order Noise-Shaping SAR Using Capacitor Stacking and Dynamic Buffering. In Proceedings of the 2021 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 13–22 February 2021; Volume 64, pp. 369–371. [Google Scholar] [CrossRef]

- Cao, Y.; Chen, Y.; Ni, Z.; Ye, F.; Ren, J. An 11b 80 MS/s SAR ADC with Speed-Enhanced SAR Logic and High-Linearity CDAC. In Proceedings of the 2018 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Chengdu, China, 26–30 October 2018; pp. 18–21. [Google Scholar] [CrossRef]

- Liu, J.; Tang, X.; Zhao, W.; Shen, L.; Sun, N. A 13-bit 0.005-mm2 40-MS/s SAR ADC With kT/C Noise Cancellation. IEEE J. Solid-State Circuits 2020, 55, 3260–3270. [Google Scholar] [CrossRef]

- Xie, T.; Wang, T.H.; Liu, Z.; Li, S. An 84-dB-SNDR Low-OSR Fourth-Order Noise-Shaping SAR with an FIA-Assisted EF-CRFF Structure and Noise-Mitigated Push-Pull Buffer-in-Loop Technique. IEEE J. Solid-State Circuits 2022, 57, 3804–3815. [Google Scholar] [CrossRef]

- Zhang, Y.; Chen, C.H.; He, T.; Sobue, K.; Hamashita, K.; Temes, G.C. A two-capacitor SAR-assisted multi-step incremental ADC with a single amplifier achieving 96.6 dB SNDR over 1.2 kHz BW. In Proceedings of the 2017 IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, USA, 30 April–3 May 2017; pp. 1–4. [Google Scholar] [CrossRef]

- Kim, K.; Oh, S.; Chae, H. Conception and Simulation of a 2-Then-1-Bit/Cycle Noise-Shaping SAR ADC. Electronics 2021, 10, 2545. [Google Scholar] [CrossRef]

- Chae, Y.; Souri, K.; Makinwa, K.A.A. A 6.3 µW 20 bit Incremental Zoom-ADC with 6 ppm INL and 1 µV Offset. IEEE J. Solid-State Circuits 2013, 48, 3019–3027. [Google Scholar] [CrossRef]

- Gönen, B.; Sebastiano, F.; Quan, R.; van Veldhoven, R.; Makinwa, K.A.A. A Dynamic Zoom ADC With 109-dB DR for Audio Applications. IEEE J. Solid-State Circuits 2017, 52, 1542–1550. [Google Scholar] [CrossRef]

- Agah, A.; Vleugels, K.; Griffin, P.B.; Ronaghi, M.; Plummer, J.D.; Wooley, B.A. A High-Resolution Low-Power Incremental ΣΔ ADC with Extended Range for Biosensor Arrays. IEEE J. Solid-State Circuits 2010, 45, 1099–1110. [Google Scholar] [CrossRef]

- Agah, A.; Vleugels, K.; Griffin, P.B.; Ronaghi, M.; Plummer, J.D.; Wooley, B.A. A High-Resolution Low-Power Oversampling ADC with Extended-Range for Bio-Sensor Arrays. In Proceedings of the 2007 IEEE Symposium on VLSI Circuits, Kyoto, Japan, 14–16 June 2007; pp. 244–245. [Google Scholar] [CrossRef]

- Chae, Y.; Han, G. Low Voltage, Low Power, Inverter-Based Switched-Capacitor Delta-Sigma Modulator. IEEE J. Solid-State Circuits 2009, 44, 458–472. [Google Scholar] [CrossRef]

- Karmakar, S.; Gönen, B.; Sebastiano, F.; van Veldhoven, R.; Makinwa, K.A.A. A 280 μ W Dynamic Zoom ADC with 120 dB DR and 118 dB SNDR in 1 kHz BW. IEEE J. Solid-State Circuits 2018, 53, 3497–3507. [Google Scholar] [CrossRef]

- Gönen, B.; Karmakar, S.; van Veldhoven, R.; Makinwa, K.A.A. A Continuous-Time Zoom ADC for Low-Power Audio Applications. IEEE J. Solid-State Circuits 2020, 55, 1023–1031. [Google Scholar] [CrossRef]

- Zhang, B.; Dou, R.; Liu, L.; Wu, N. A 91.2 dB SNDR 66.2 fJ/conv. dynamic amplifier based 24 kHz ΔΣ modulator. In Proceedings of the 2016 IEEE Asian Solid-State Circuits Conference (A-SSCC), Toyama, Japan, 7–9 November 2016; pp. 317–320. [Google Scholar] [CrossRef]

- Park, H.; Nam, K.; Su, D.K.; Vleugels, K.; Wooley, B.A. A 0.7-V 870-μ W Digital-Audio CMOS Sigma-Delta Modulator. IEEE J. Solid-State Circuits 2009, 44, 1078–1088. [Google Scholar] [CrossRef]

- Steiner, M.; Greer, N. 15.8 A 22.3 b 1 kHz 12.7 mW switched-capacitor ΔΣ modulator with stacked split-steering amplifiers. In Proceedings of the 2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016; pp. 284–286. [Google Scholar] [CrossRef]

- Dessouky, M.; Kaiser, A. Very low-voltage digital-audio /spl Delta//spl Sigma/ modulator with 88-dB dynamic range using local switch bootstrapping. IEEE J. Solid-State Circuits 2001, 36, 349–355. [Google Scholar] [CrossRef]

- Chiang, S.h.W.; Sun, H.; Razavi, B. A 10-Bit 800-MHz 19-mW CMOS ADC. In Proceedings of the 2013 Symposium on VLSI Circuits, Kyoto, Japan, 12–14 June 2013; pp. C100–C101. [Google Scholar]

- van der Goes, F.; Ward, C.M.; Astgimath, S.; Yan, H.; Riley, J.; Zeng, Z.; Mulder, J.; Wang, S.; Bult, K. A 1.5 mW 68 dB SNDR 80 Ms/s 2 × Interleaved Pipelined SAR ADC in 28 nm CMOS. IEEE J. Solid-State Circuits 2014, 49, 2835–2845. [Google Scholar] [CrossRef]

- Hariprasath, V.; Guerber, J.; Lee, S.H.; Moon, U.K. Merged capacitor switching based SAR ADC with highest switching energy-efficiency. Electron. Lett. 2010, 46, 620–621. [Google Scholar] [CrossRef]

- Schinkel, D.; Mensink, E.; Klumperink, E.; van Tuijl, E.; Nauta, B. A Double-Tail Latch-Type Voltage Sense Amplifier with 18 ps Setup + Hold Time. In Proceedings of the 2007 IEEE International Solid-State Circuits Conference. Digest of Technical Papers, San Francisco, CA, USA, 11–15 February 2007; pp. 314–605. [Google Scholar] [CrossRef]

- Baird, R.; Fiez, T. Linearity enhancement of multibit /spl Delta//spl Sigma/ A/D and D/A converters using data weighted averaging. IEEE Trans. Circuits Syst. II Analog Digit. Signal Process. 1995, 42, 753–762. [Google Scholar] [CrossRef]

- Zhang, Y.; Chen, C.H.; He, T.; Temes, G.C. A 16 b Multi-Step Incremental Analog-to-Digital Converter with Single-Opamp Multi-Slope Extended Counting. IEEE J. Solid-State Circuits 2017, 52, 1066–1076. [Google Scholar] [CrossRef]

- Kuo, S.C.; Huang, J.S.; Huang, Y.C.; Kao, C.W.; Hsu, C.W.; Chen, C.H. A Multi-Step Incremental Analog-to-Digital Converter with a Single Opamp and Two-Capacitor SAR Extended Counting. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 2890–2899. [Google Scholar] [CrossRef]

- Wang, B.; Sin, S.W.; U, S.P.; Maloberti, F.; Martins, R.P. A 550-μW 20-kHz BW 100.8-dB SNDR Linear-Exponential Multi-Bit Incremental ΣΔ ADC With 256 Clock Cycles in 65-nm CMOS. IEEE J. Solid-State Circuits 2019, 54, 1161–1172. [Google Scholar] [CrossRef]

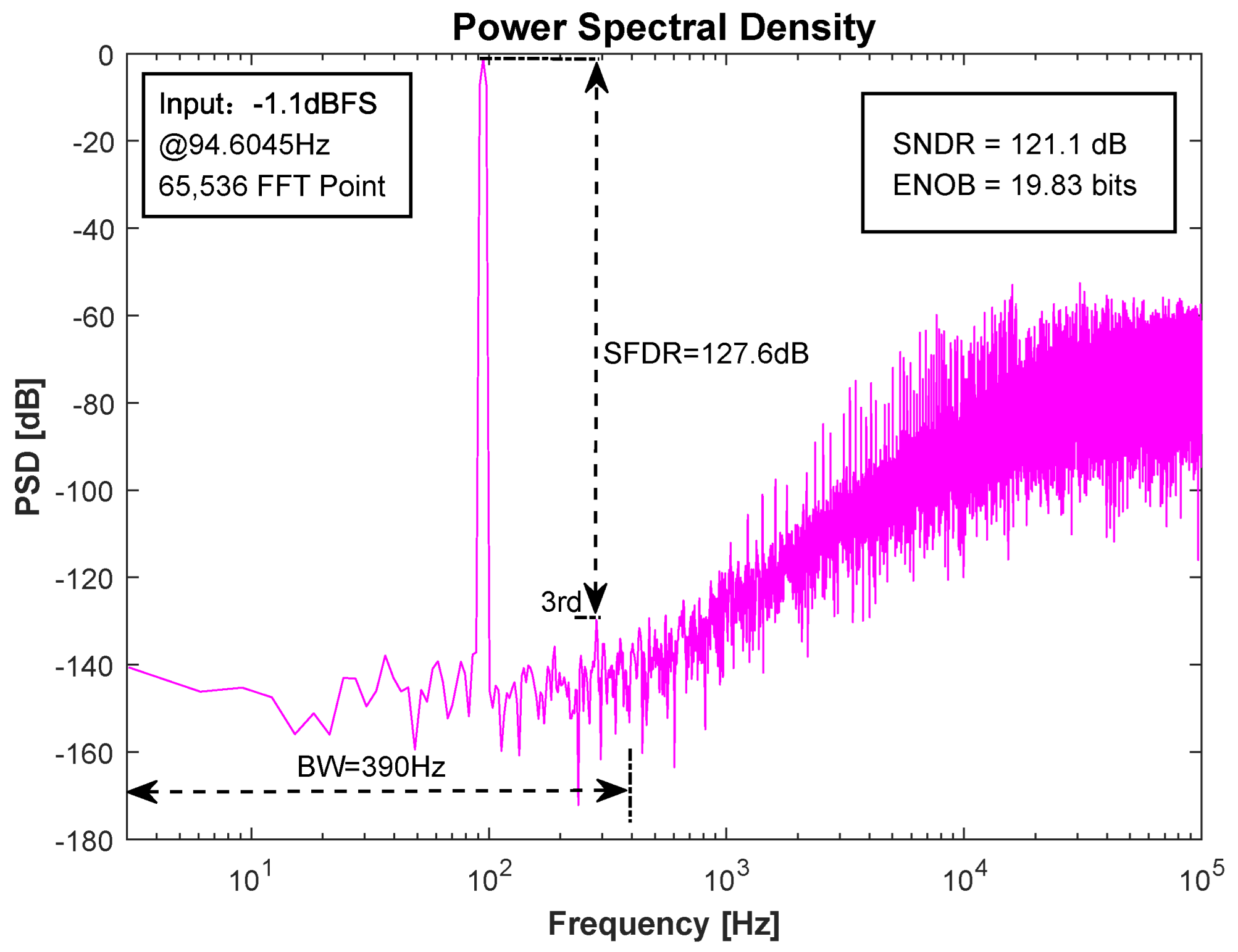

| Parameter | SS, 85 °C, 0.9 VDD | TT, 27 °C, VDD | FF, −40 °C, 1.1 VDD |

|---|---|---|---|

| SNDR (dB) | 120.4 | 121.1 | 121.6 |

| ENOB (bit) | 19.70 | 19.83 | 19.90 |

| Parameter | This Work | [11] | [12] | [1] | [27] | [29] | [28] |

|---|---|---|---|---|---|---|---|

| Architecture | Zoom | Zoom | Zoom | Multi-bit | IADC1 | IADC2 | IADC1 |

| (SAR + + SAR) | (SAR + ) | (SAR + ) | ( + SAR) | +Multi-Slope | +Exp. Count | +Binary Counting | |

| Technology (nm) | 350 | 160 | 160 | 180 | 180 | 65 | 180 |

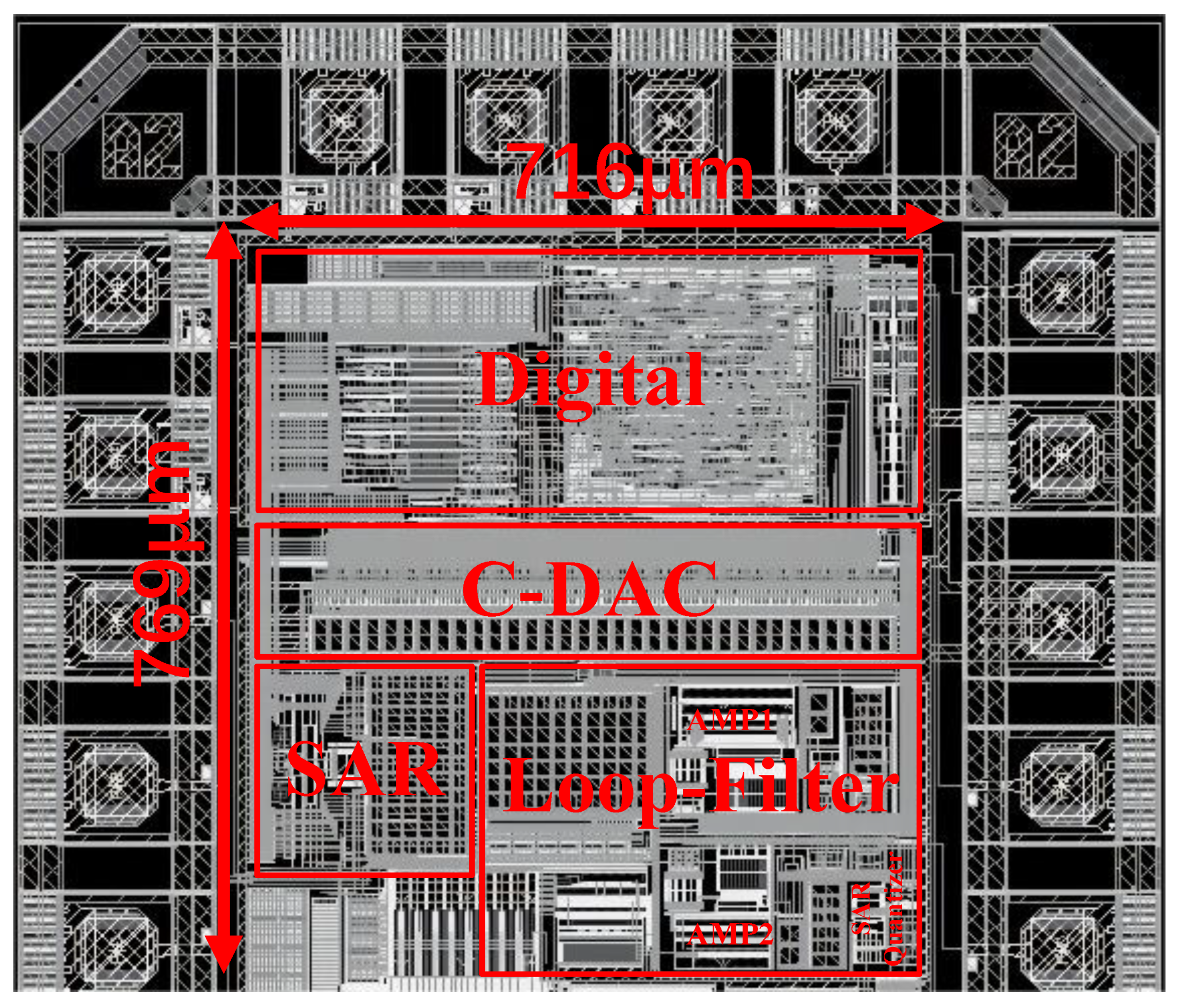

| Area (mm) | 0.55 | 0.375 | 0.16 | 2.3 | 0.5 | 0.134 | 0.27 |

| Supply voltage (V) | 2.5 | 1.8 | 1.8 | 3.3 | 1.5 | 1.2 | 1.5 |

| (MHz) | 0.2 | 0.0256 | 11.29 | 3.072 | 0.642 | 10.24 | 0.642 |

| BW (kHz) | 0.39 | 0.0125 | 20 | 24 | 1 | 20 | 1.2 |

| Power (W) | 170 | 6.3 | 1120 | 20,000 | 34.6 | 550 | 33.2 |

| OSR | 256 | 1024 | 282 | 64 | 321 | 256 | 268 |

| SNDR (dB) | 121.1 | 119.8 | 103 | 120 | 96.8 | 100.8 | 96.6 |

| SFDR (dB) | 127.6 | – | – | 125.2 | – | 121 | 111 |

| (dB) | 184.7 | 182.7 | 175.5 | 180.8 | 171.4 | 176.4 | 172.2 |

| Result | Simulated | Measured | Measured | Simulated | Measured | Measured | Measured |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jia, Y.; Guo, J.; Guo, G. A 121 dB SNDR Zoom ADC Using Dynamic Amplifier and Asynchronous SAR Quantizer. Electronics 2023, 12, 313. https://doi.org/10.3390/electronics12020313

Jia Y, Guo J, Guo G. A 121 dB SNDR Zoom ADC Using Dynamic Amplifier and Asynchronous SAR Quantizer. Electronics. 2023; 12(2):313. https://doi.org/10.3390/electronics12020313

Chicago/Turabian StyleJia, Yangchen, Jiangfei Guo, and Guiliang Guo. 2023. "A 121 dB SNDR Zoom ADC Using Dynamic Amplifier and Asynchronous SAR Quantizer" Electronics 12, no. 2: 313. https://doi.org/10.3390/electronics12020313

APA StyleJia, Y., Guo, J., & Guo, G. (2023). A 121 dB SNDR Zoom ADC Using Dynamic Amplifier and Asynchronous SAR Quantizer. Electronics, 12(2), 313. https://doi.org/10.3390/electronics12020313