The Design of a Wide-Dynamic-Range and High-Linearity RMS Power Detector for mm-Wave Applications in 65 nm CMOS

Abstract

:1. Introduction

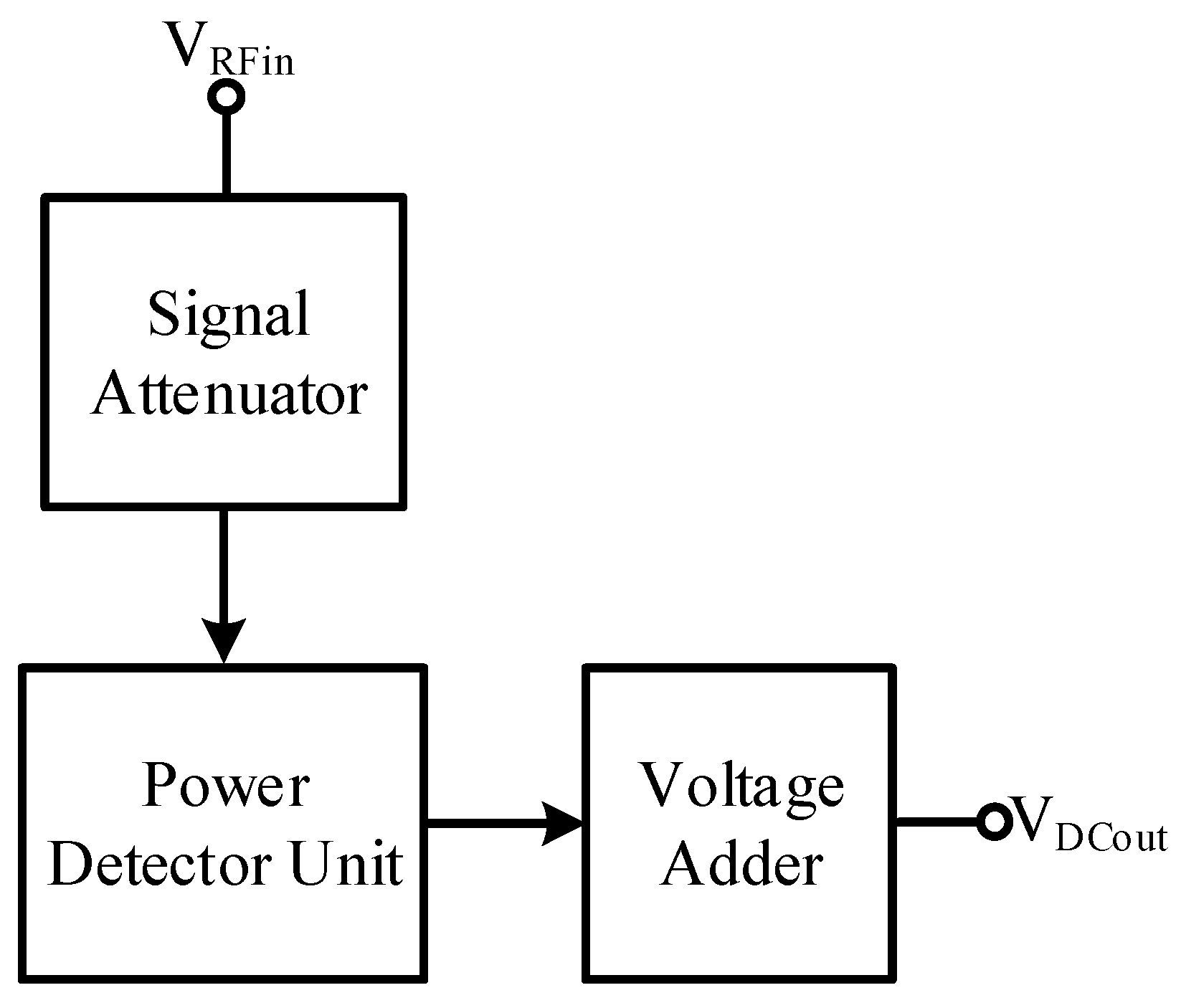

2. The Principle of the Power Detector System

2.1. The Radio Frequency Signal Attenuator

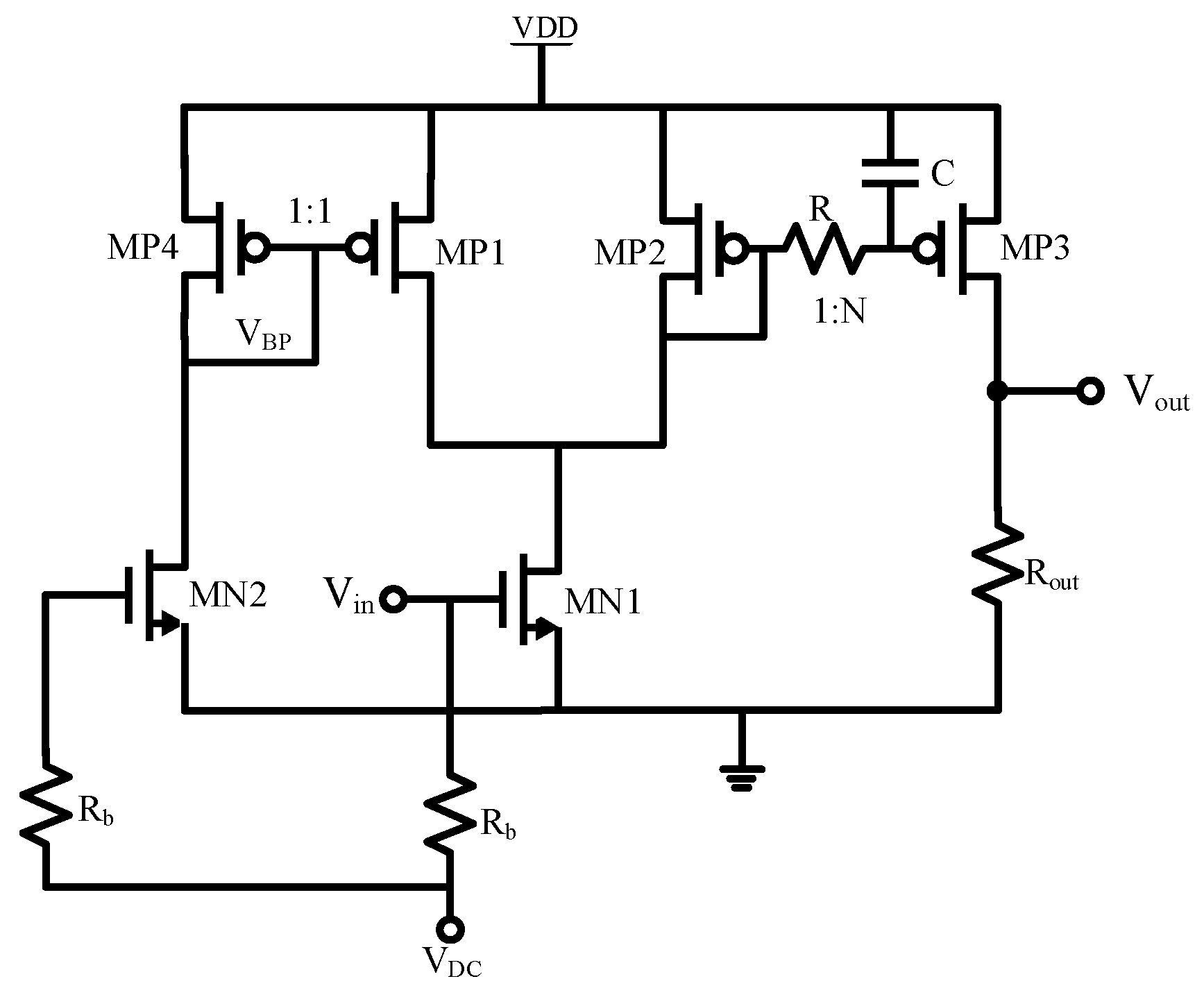

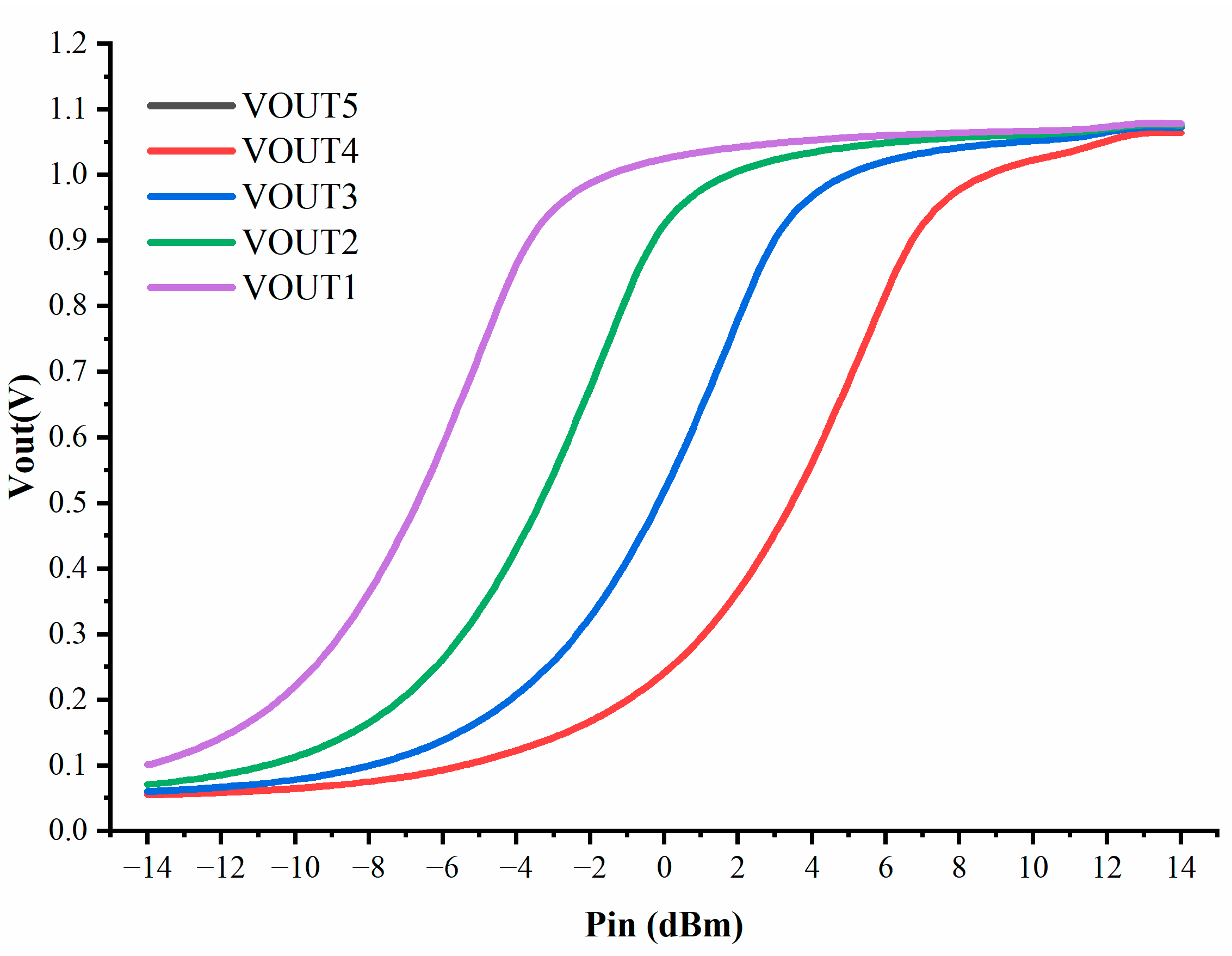

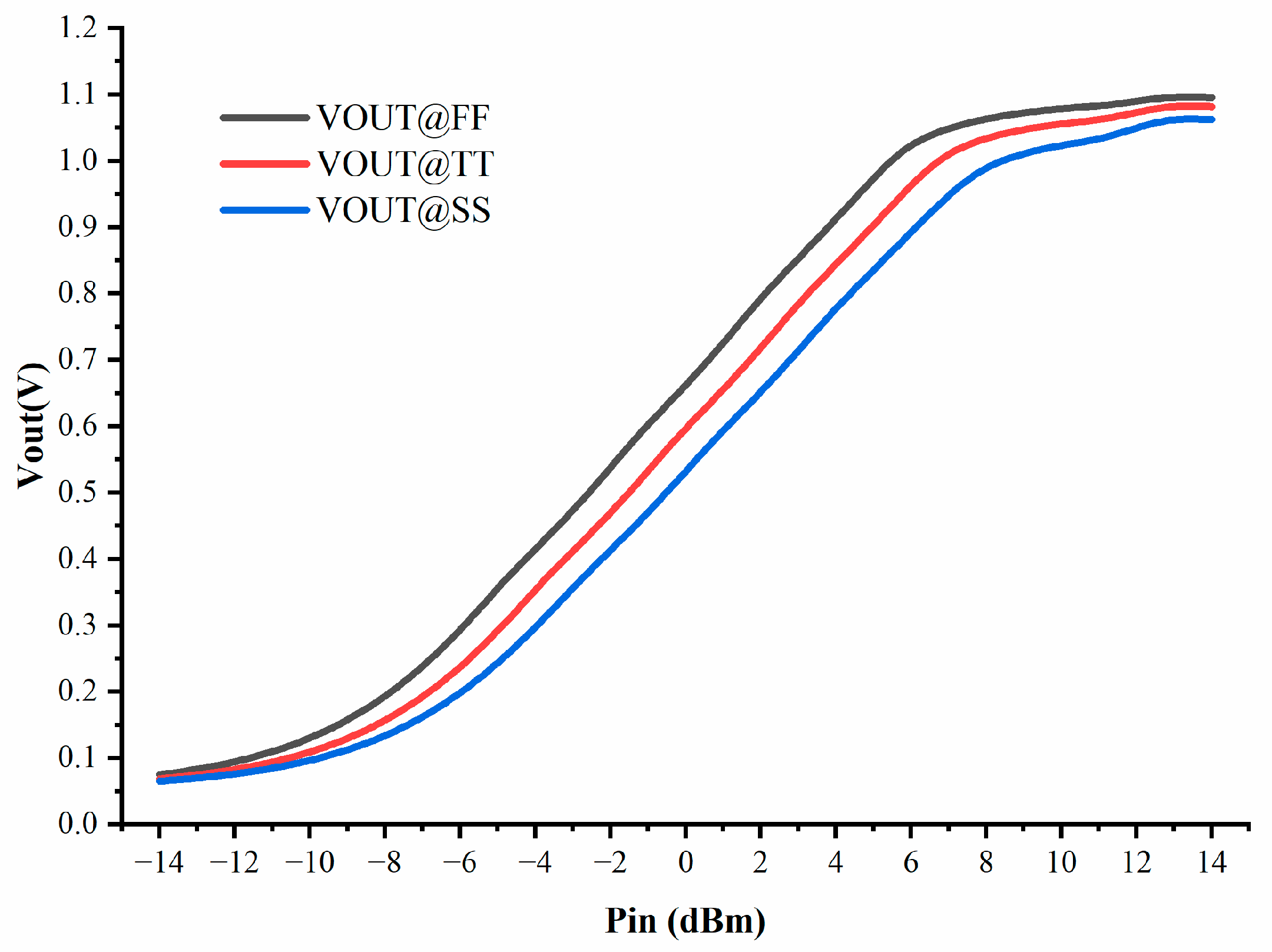

2.2. Power Detector Unit and Equalization Technique

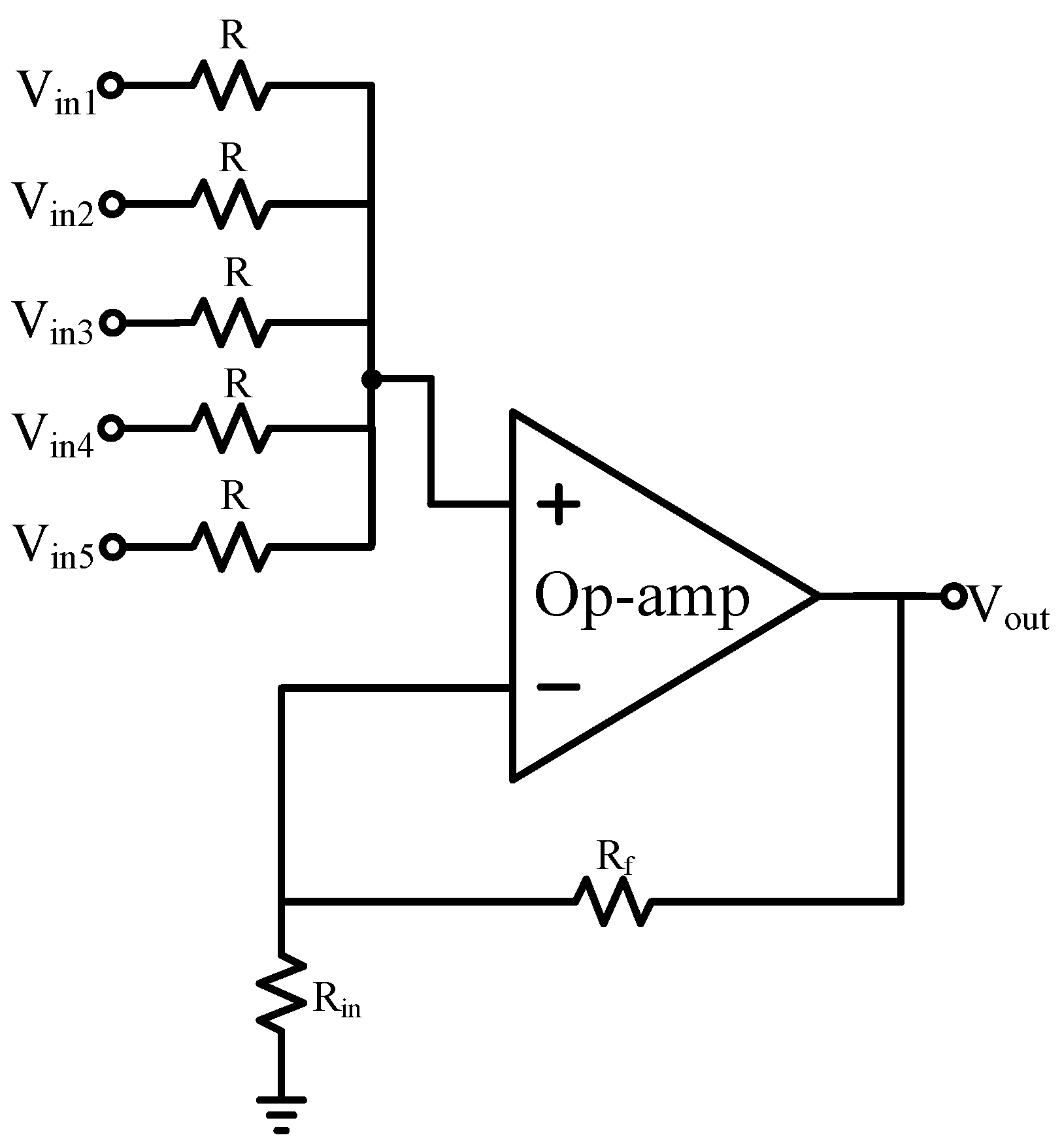

2.3. The Linear Proportional Voltage Adder

3. Design and Implementation of the Proposed Power Detector

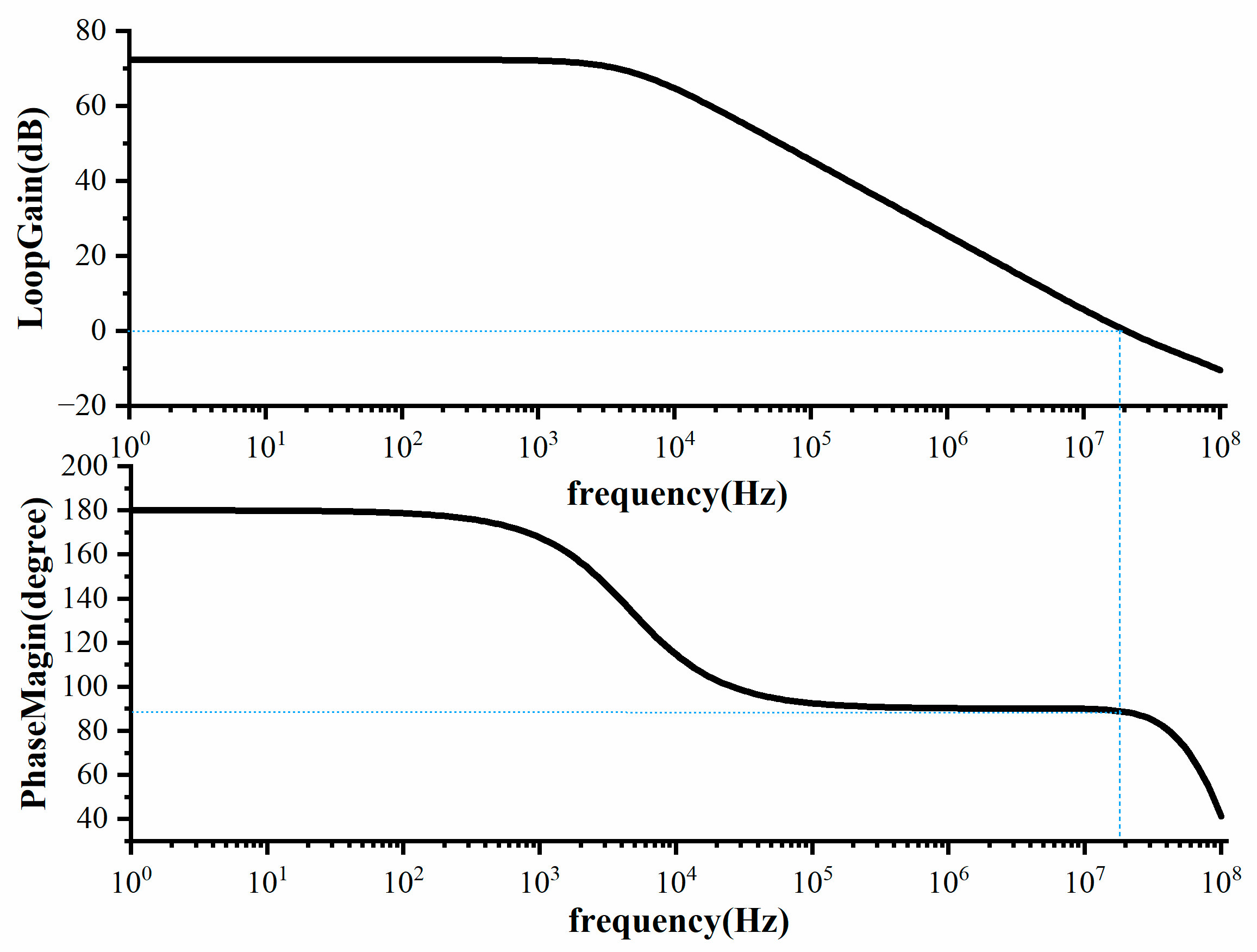

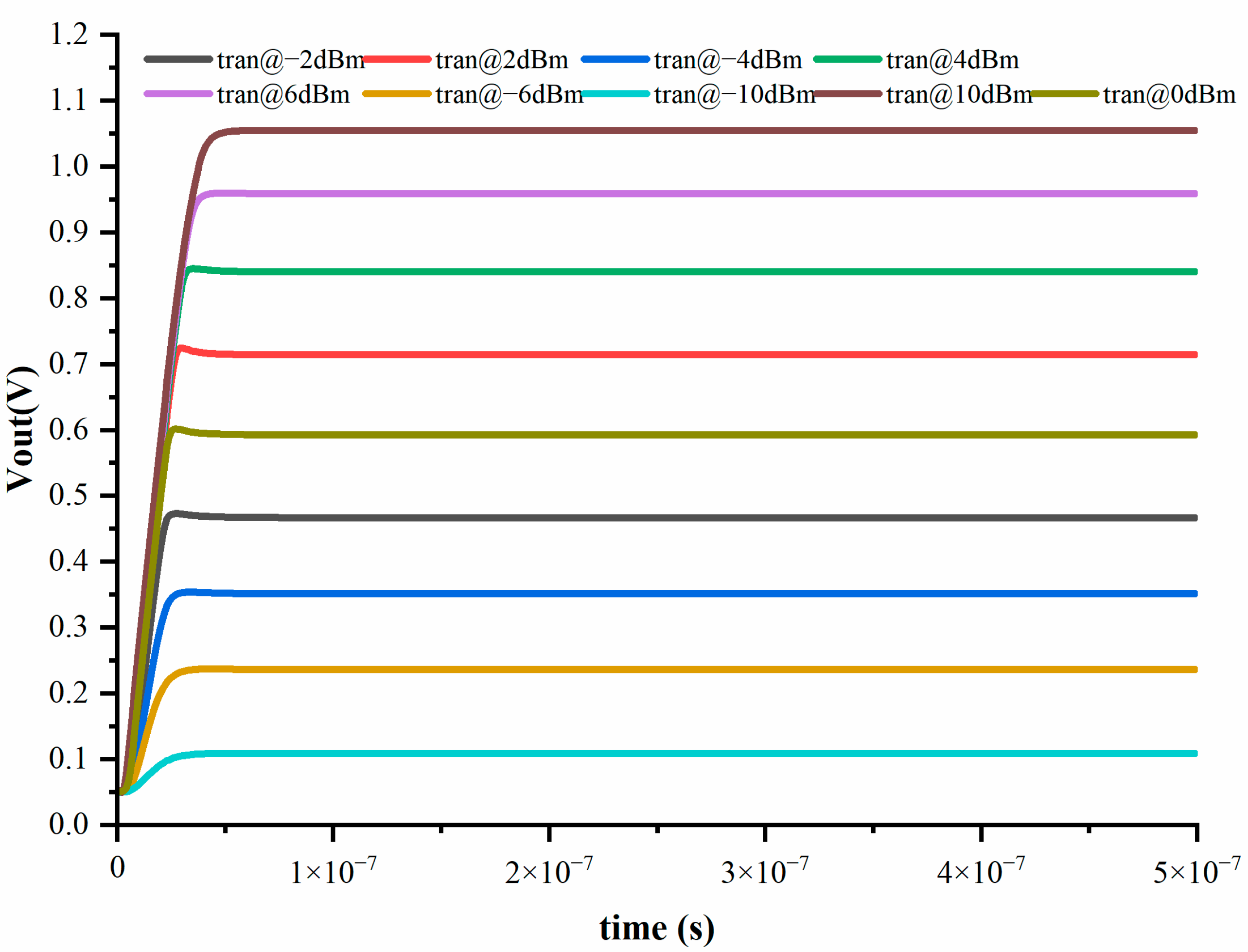

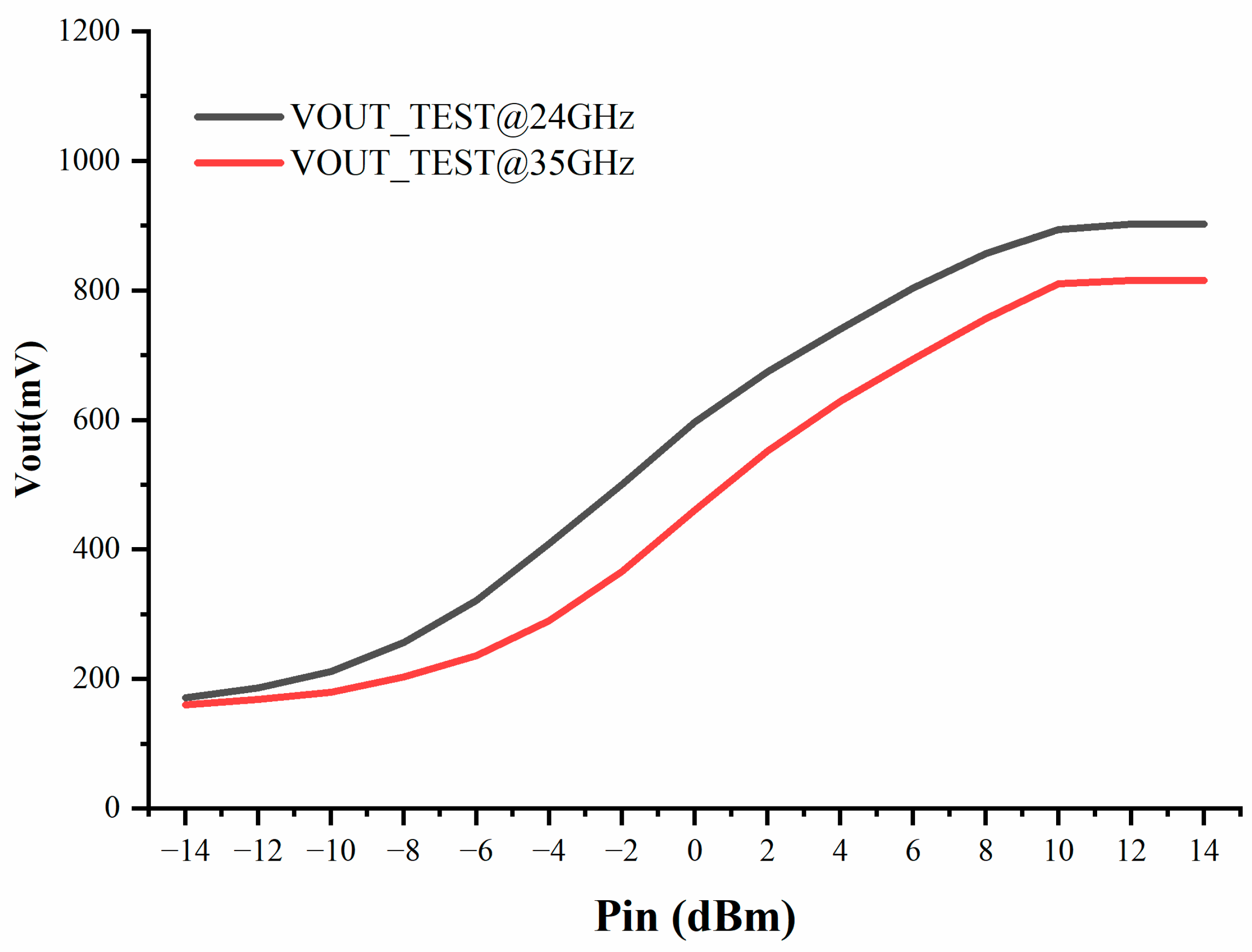

4. Simulation and Measurement Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Feng, J.; Onabajo, M. Wide Dynamic Range CMOS Amplifier Design for RF Signal Power Detection via Electro-Thermal Coupling. J. Electron. Test. 2014, 30, 101–109. [Google Scholar] [CrossRef]

- Wu, G.; Belostotski, L.; James, W.H. A 65 nm CMOS broadband self-calibrated power detector for the square kilometre array radio telescope. J. Eng. 2014, 2014, 494–502. [Google Scholar] [CrossRef]

- Choi, J.; Lee, J.; Xi, Y.; Myoung, S.S.; Baek, S.; Kwon, D.H.; Bui, Q.D.; Lee, J.; Oh, D.; Cho, T.B. Wide Dynamic-Range CMOS RMS Power Detector. IEEE Trans. Microw. Theory Tech. 2016, 64, 868–880. [Google Scholar] [CrossRef]

- Zhou, Y.; Chia, Y.W. A Low-Power Ultra-Wideband CMOS True RMS Power Detector. IEEE Trans. Microw. Theory Tech. 2008, 56, 1052–1058. [Google Scholar] [CrossRef]

- Sakphrom, S.; Thanachayanont, A. A low-power CMOS RF power detector. In Proceedings of the 2012 19th IEEE International Conference on Electronics, Circuits, and Systems, Seville, Spain, 9–12 December 2012; IEEE: Piscataway, NJ, USA, 2013. [Google Scholar]

- Zhou, Y.; Wah, M. A wide band CMOS RF power detector. In Proceedings of the 2006 IEEE International Symposium on Circuits & Systems, Kos, Greece, 21–24 May 2006; IEEE: Piscataway, NJ, USA, 2006. [Google Scholar]

- Hangue, P.A.R.K.; Jaejun, L.E.E.; Jaechun, L.E.E.; Sangwook, N.A.M. A CMOS RF Power Detector Using an Improved Unbalanced Source Coupled Pair. IEICE Trans. Electron. 2009, 91, 1969–1970. [Google Scholar]

- Sleiman, S.B.; Ismail, M. A CMOS amplitude detector for RF-BIST and calibration. In Proceedings of the 2009 16th IEEE International Conference on Electronics, Circuits and systems, Yasmine Hammamet, Tunesia, 13–19 December 2009; IEEE: Piscataway, NJ, USA, 2010. [Google Scholar]

- Richardson, F.D.; Kouki, A.B.; Gagnon, G. A CMOS RF power detector for an Automatic Impedance Matching System. In Proceedings of the 2011 9th IEEE International New Circuits & Systems Conference, Bordeaux, France, 26–29 June 2011; IEEE: Piscataway, NJ, USA, 2011. [Google Scholar]

- Jiang, Y.; Liu, X.; Zhang, Q.; Su, X.; Yu, Z.; Zhang, H. A 55-dB Dynamic Range Wideband RF Logarithmic Power Detector with Temperature and DC Offset Compensation. IEICE Electron. Express 2021, 18, 20200426. [Google Scholar] [CrossRef]

- Wang, J.; Zheng, Y.; Yang, F.; Liao, H. A wide band CMOS radio frequency RMS power detector with 42-dB dynamic range. In Proceedings of the 2015 IEEE International Symposium on Circuits & Systems, Lisbon, Portugal, 24–27 May 2015; IEEE: Piscataway, NJ, USA, 2015. [Google Scholar]

- Serhan, A.; Lauga-Larroze, E.; Fournier, J.M. A 700 MHz output bandwidth, 30 dB dynamic range, common-base mm-wave power detector. In Proceedings of the 2015 IEEE MTT-S International Microwave Symposium, Phoenix, AZ, USA, 17–22 May 2015; IEEE: Piscataway, NJ, USA, 2015. [Google Scholar]

- Levinger, R.; Katz, O.; Sheinman, B.; Carmon, R.; Ben-Yishay, R.; Mazor, N.; Pivnik, S.; Elad, D.; Socher, E. An E-band 40 dB dynamic range multi-tanh power detector in 0.13 μm SiGe technology. In Proceedings of the 2014 9th European Microwave Integrated Circuit Conference, Rome, Italy, 6–7 October 2014; IEEE: Piscataway, NJ, USA, 2014; pp. 170–173. [Google Scholar]

- Munzer, D.J.; Mannem, N.S.; Garay, E.; Wang, H. A Broadband Mm-Wave VSWR-Resilient Joint True-Power Detector and Impedance Sensor Supporting Single-Ended Antenna Interfaces. In Proceedings of the 2022 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 20–26 February 2022; IEEE: Piscataway, NJ, USA, 2022. [Google Scholar]

- Amer, A.E.; Ashry, A.; Abdalla, M.A.Y.; Eshrah, I.A. Gilbert Based Power Detector for 5G mm-Wave Transceivers Built-in-Self Test. In Proceedings of the 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 26–29 May 2019; IEEE: Piscataway, NJ, USA, 2019. [Google Scholar]

- Stärke, P.; Rieß, V.; Fritsche, D.; Carta, C.; Ellinger, F. A wideband square-law power detector with high dynamic range and combined logarithmic amplifier for 100 GHz F-Band in 130 nm SiGe BiCMOS. In Proceedings of the 2017 IEEE Bipolar/BiCMOS Circuits and Technology Meeting (BCTM), Miami, FL, USA, 19–21 October 2017; IEEE: Piscataway, NJ, USA, 2017. [Google Scholar]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wu, X.-A.; Zhang, Z.; Liu, H.; Tian, T. The Design of a Wide-Dynamic-Range and High-Linearity RMS Power Detector for mm-Wave Applications in 65 nm CMOS. Electronics 2023, 12, 4402. https://doi.org/10.3390/electronics12214402

Wu X-A, Zhang Z, Liu H, Tian T. The Design of a Wide-Dynamic-Range and High-Linearity RMS Power Detector for mm-Wave Applications in 65 nm CMOS. Electronics. 2023; 12(21):4402. https://doi.org/10.3390/electronics12214402

Chicago/Turabian StyleWu, Xi-An, Zechen Zhang, Hong Liu, and Tong Tian. 2023. "The Design of a Wide-Dynamic-Range and High-Linearity RMS Power Detector for mm-Wave Applications in 65 nm CMOS" Electronics 12, no. 21: 4402. https://doi.org/10.3390/electronics12214402