Digitalized Control Algorithm of Bridgeless Totem-Pole PFC with a Simple Control Structure Based on the Phase Angle

Abstract

:1. Introduction

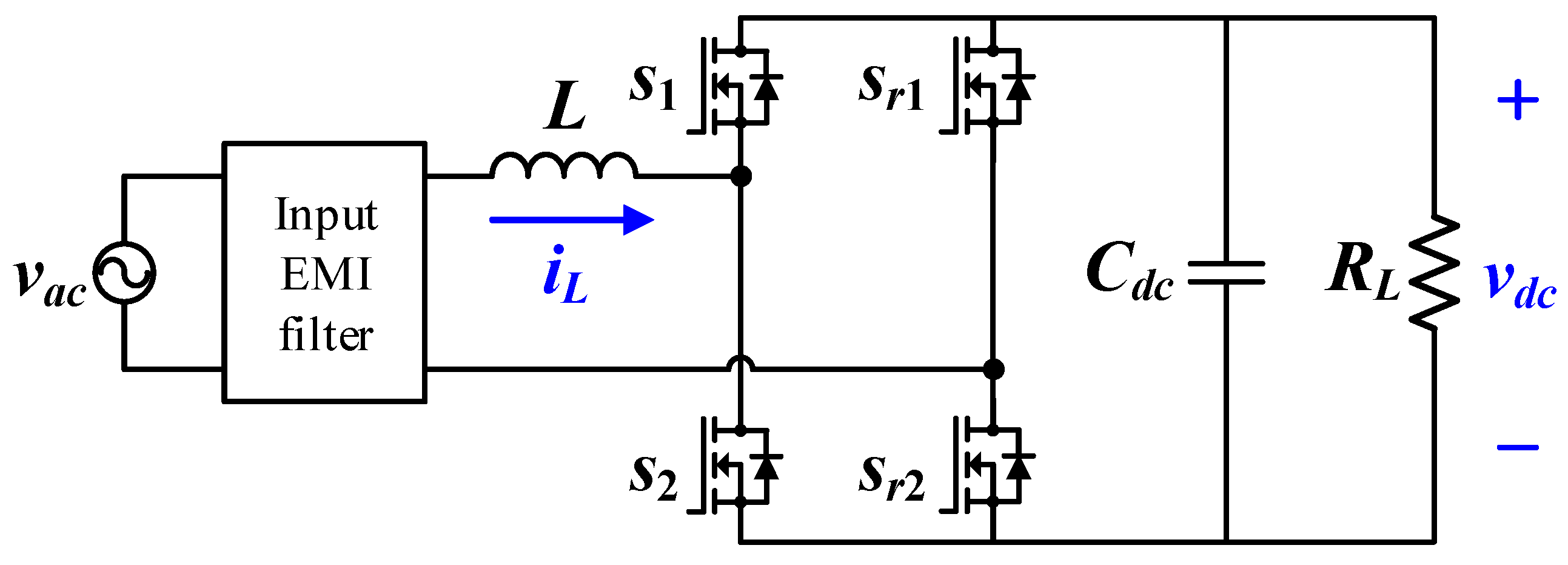

2. Operation Principle of TBPFC

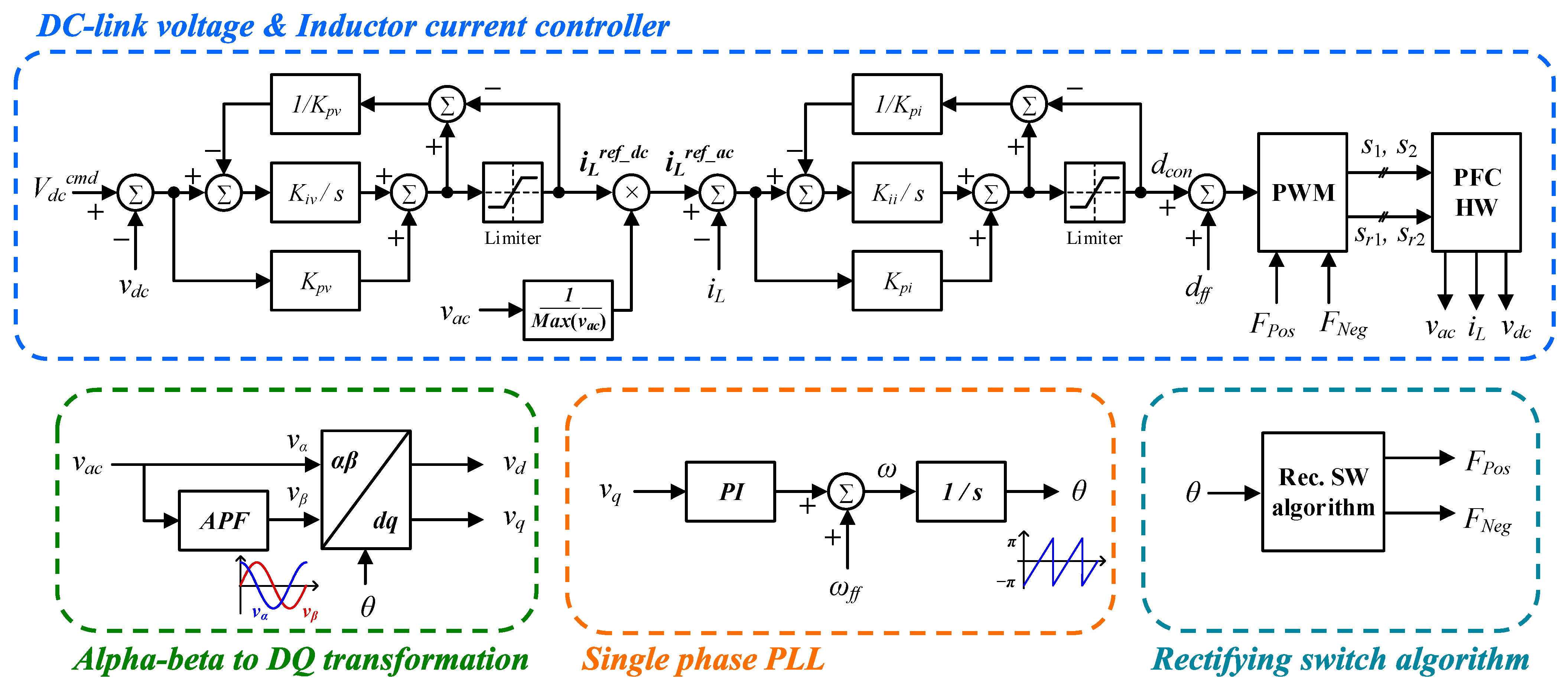

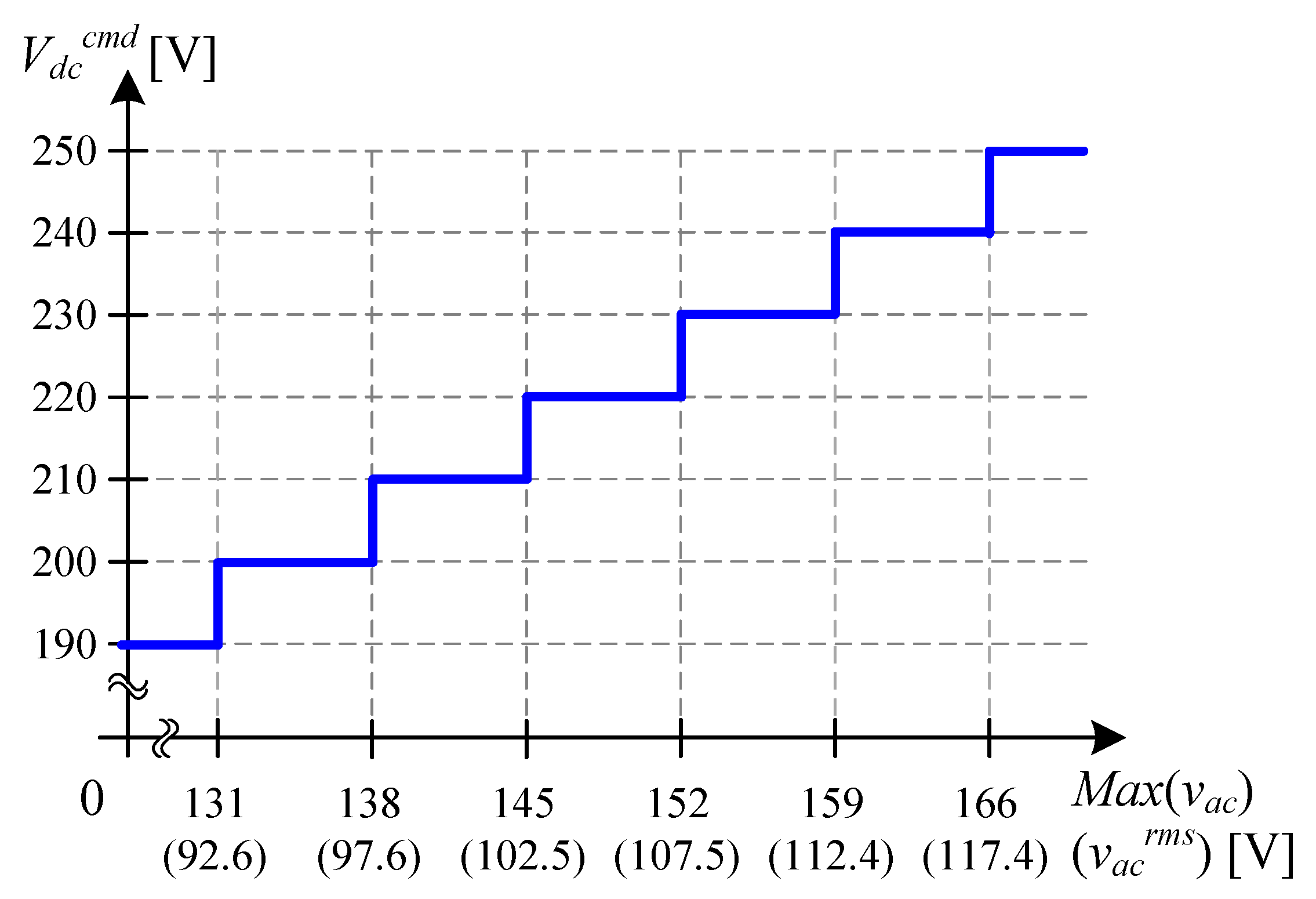

3. Proposed Control Algorithm

3.1. Digitalized Double Loop Controller

3.2. Coordinate Transformation and PLL

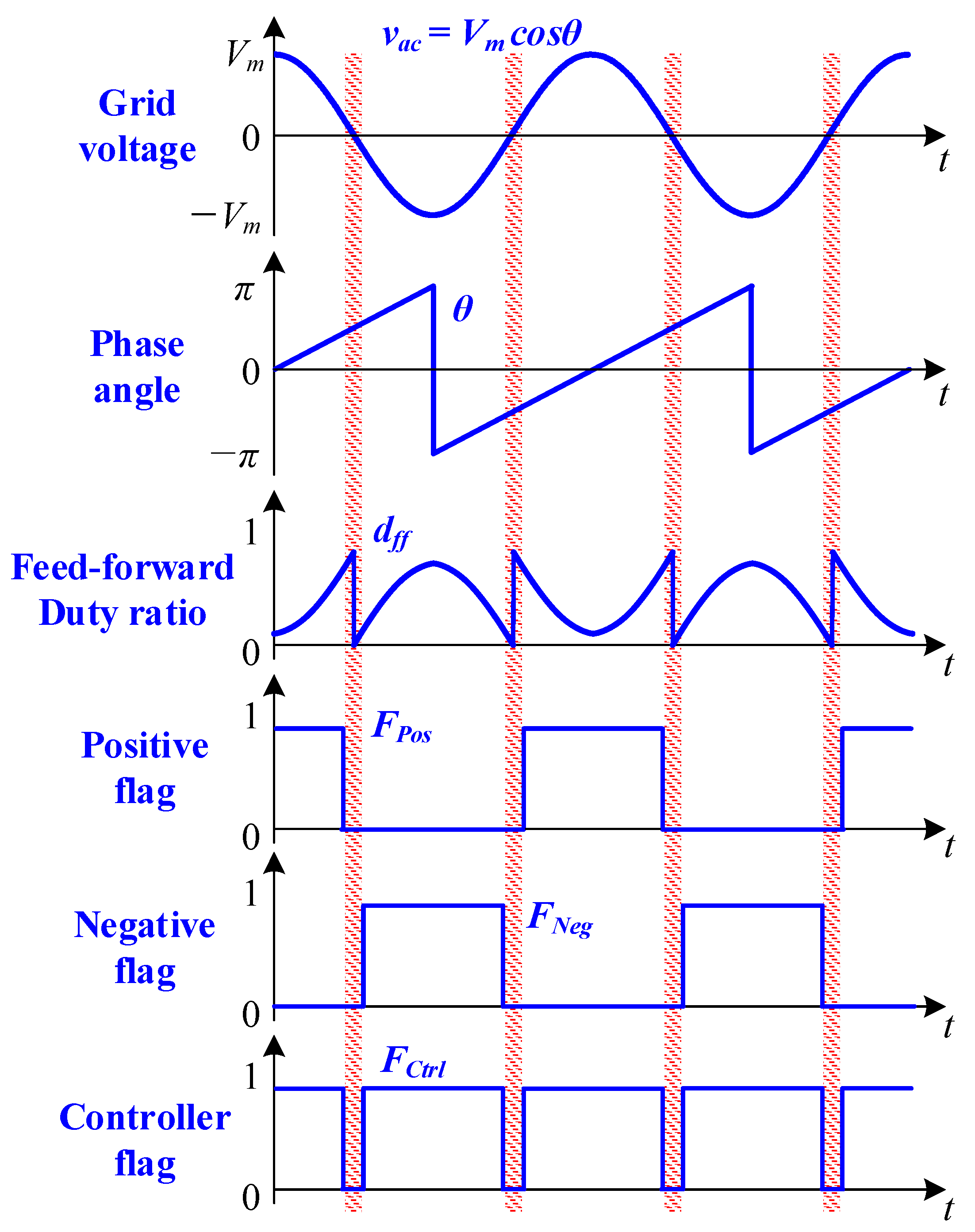

3.3. PLL Rectifying Switch Algorithm

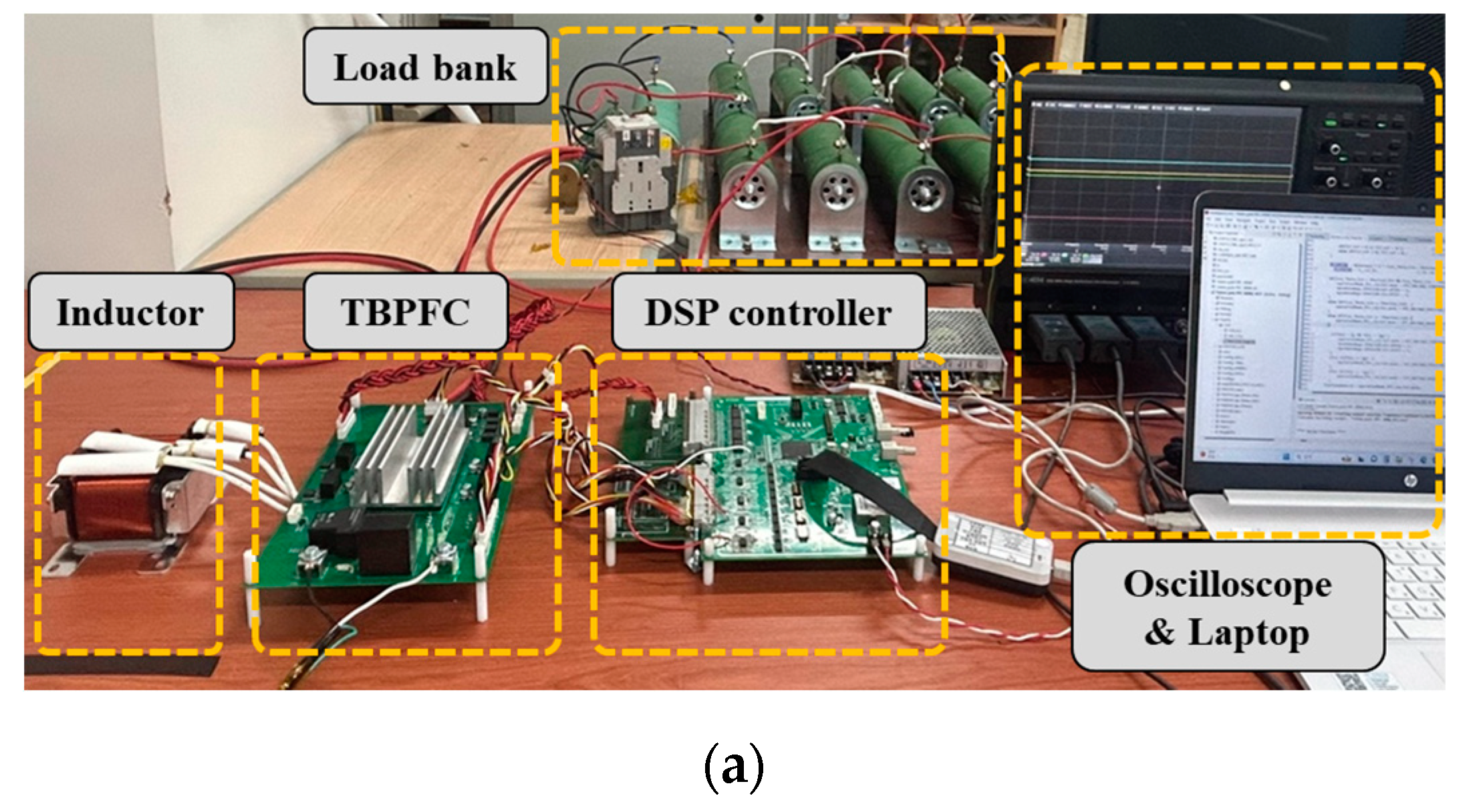

4. Realization and Experimental Results

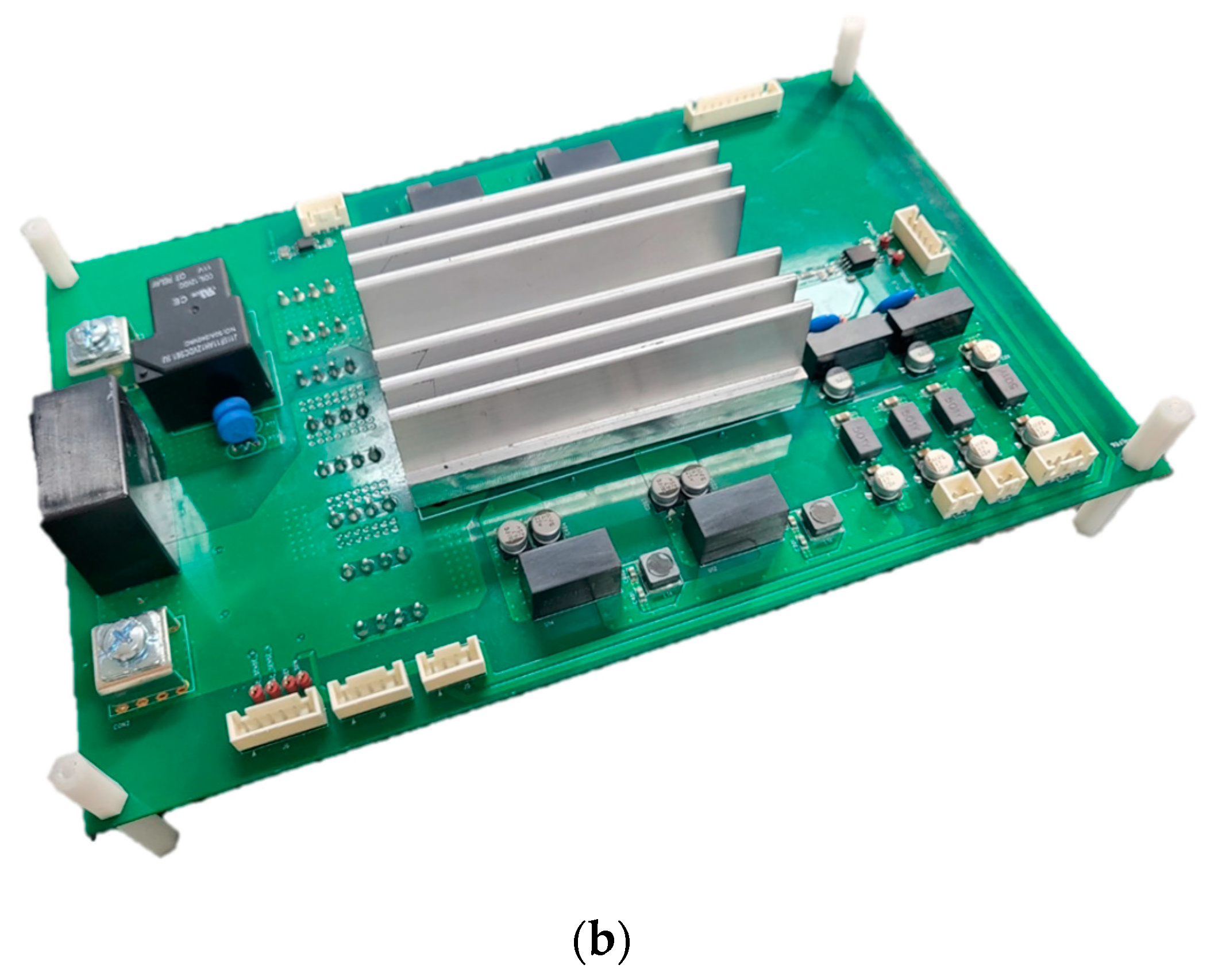

4.1. Hardware Specifications

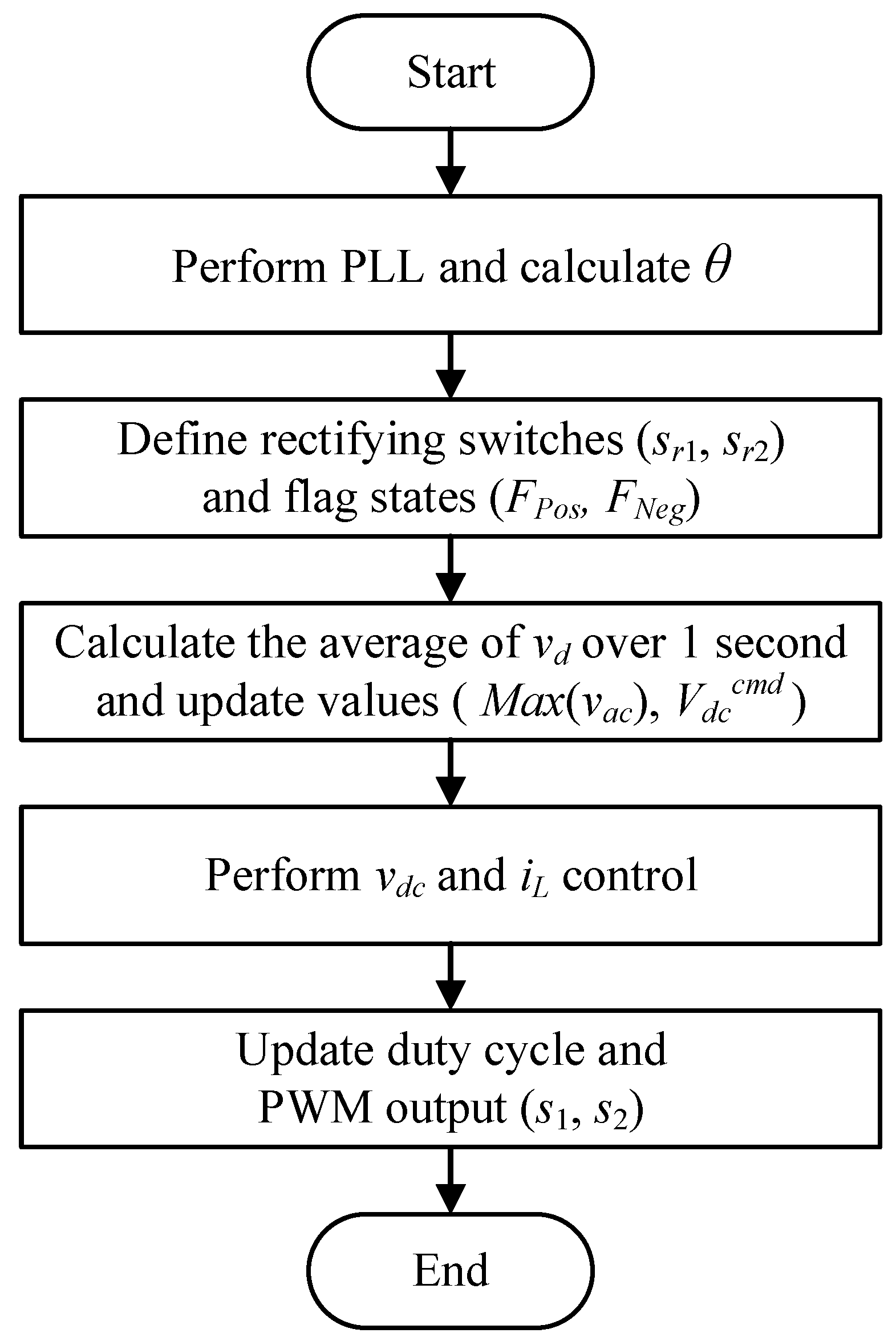

4.2. Algorithm Implementation

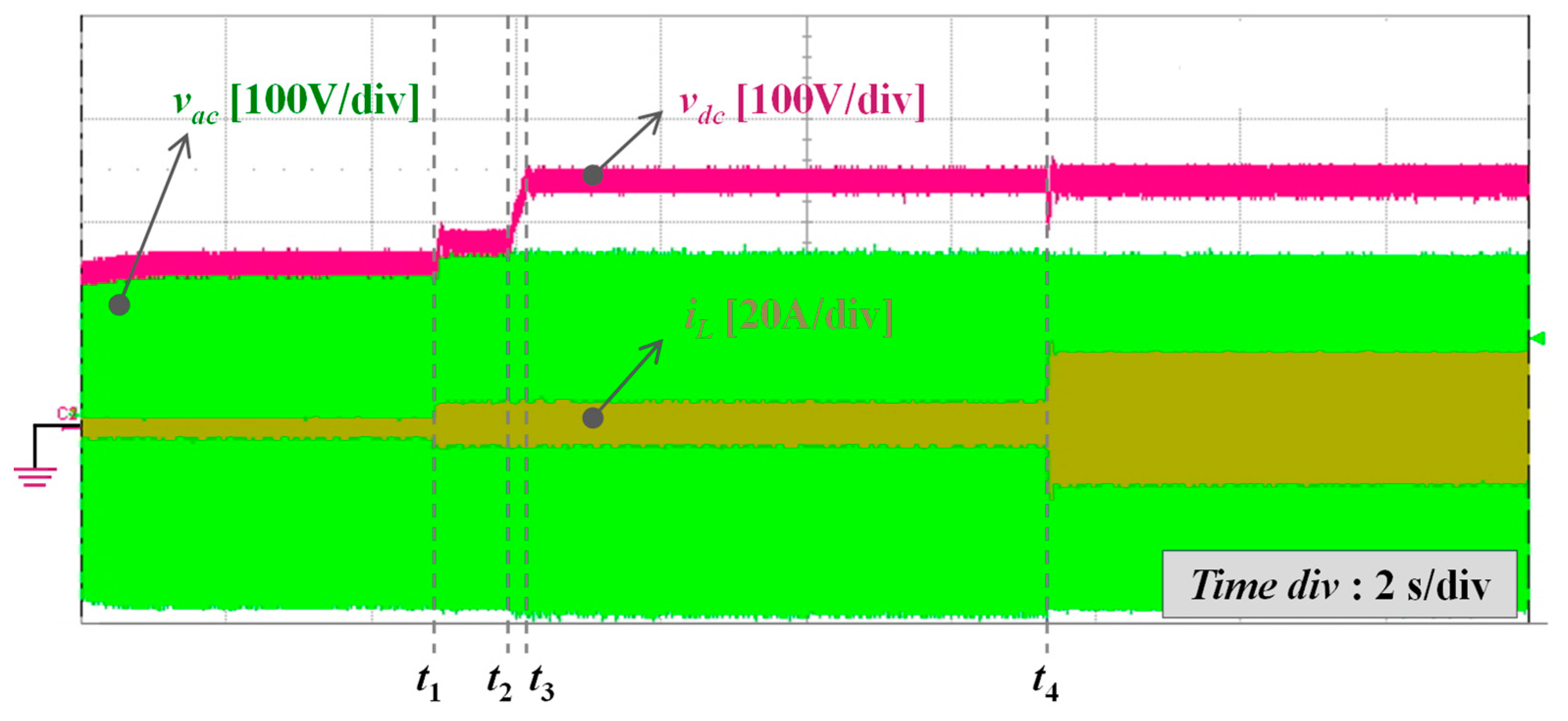

4.3. Experimental Results

5. Future Considerations

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Lee, Y.-D.; Kim, C.-E.; Kim, D.-M.; Choi, S.-H.; Moon, G.-W. A New Bridgeless PFC Converter having Low Common-Mode Noise and High Efficiency for Server Power Application. In Proceedings of the 2019 10th International Conference on Power Electronics and ECCE Asia (ICPE 2019—ECCE Asia), Busan, Republic of Korea, 27–30 May 2019; pp. 1–6. [Google Scholar]

- Baek, J.; Kim, J.-K.; Lee, J.-B.; Park, M.-H.; Moon, G.-W. A New Standby Structure Integrated with Boost PFC Converter for Server Power Supply. IEEE Trans. Power Electron. 2019, 34, 5283–5293. [Google Scholar] [CrossRef]

- Patel, N.; Lopes, L.A.C.; Rathore, A.K. Analysis and Design of Soft-Switching Single-Stage Single-Phase PFC Converter for Bidirectional Plug-in EV Charger. In Proceedings of the 2022 IEEE Energy Conversion Congress and Exposition (ECCE), Detroit, MI, USA, 9–13 October 2022; pp. 1–7. [Google Scholar]

- Pandey, R.; Singh, B. Bridgeless PFC Converter Based EV Charger. In Proceedings of the 2020 IEEE International Conference on Computing, Power and Communication Technologies (GUCON), Greater Noida, India, 2–4 October 2020; pp. 290–295. [Google Scholar]

- Rajasekaran, S.; Suresh, S.; Karthikeyan, K.; Bhuvanesh, A. Implementation of an A-Source DC–DC Boost Combination Phase-Shifting Full-Bridge Converter for Electric Car Rapid Charging Applications. J. Electr. Eng. Technol. 2023, 18, 2871–2884. [Google Scholar] [CrossRef]

- Kumar, K.A.; Veeramallu, V.K.S.; Narasimharaju, B.L. Performance Analysis of Coupled Inductor Based Ripple Free Boost PFC AC-DC LED Driver. In Proceedings of the 2020 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Jaipur, India, 16–19 December 2020; pp. 1–4. [Google Scholar]

- Jha, A.; Singh, B. A bridgeless boost PFC converter fed LED driver for high power factor and low THD. In Proceedings of the 2018 IEEMA Engineer Infinite Conference (eTechNxT), New Delhi, India, 13–14 March 2018; pp. 1–6. [Google Scholar]

- Ponce-Silva, M.; Salazar-Pérez, D.; Rodríguez-Benítez, O.M.; Vela-Valdés, L.G.; Claudio-Sánchez, A.; De León-Aldaco, S.E.; Cortés-García, C.; Saavedra-Benítez, Y.I.; Lozoya-Ponce, R.E.; Aquí-Tapia, J.A. Flyback Converter for Solid-State Lighting Applications with Partial Energy Processing. Electronics 2021, 10, 60. [Google Scholar] [CrossRef]

- IEC 61000-3-2, Part 3–2; Limits for Harmonic Current Emissions (Equipment Input Current ≤16A per Phase). IEC: Geneva, Switzerland, 2005.

- Lee, D.G.; Kim, R.Y. Control of Hybrid Active Power Filter to Reduce Harmonics of 3-Phase Cap-Less Inverter. J. Electr. Eng. Technol. 2023, 18, 261–270. [Google Scholar] [CrossRef]

- Park, J.W.; Le, T.-V.; Kang, F.-S.; Park, S.-J. Novel Current Slope Control in Dual-Active-Bridge Converter Using Periodic Filters and Direct Access Memory in DSP. J. Electr. Eng. Technol. 2023. [Google Scholar] [CrossRef]

- Lee, G.-Y.; Cho, M.-S.; Kim, R.-Y. Lumped Parameter Modeling Based Power Loop Analysis Technique of Power Circuit Board with Wide Conduction Area for WBG Semiconductors. Electronics 2021, 10, 1722. [Google Scholar] [CrossRef]

- Araumi, R.; Yamada, R.; Wada, K. Improvement of Characteristics in CRM-PFC Using a Control Method based on Switching Frequency Limitation. In Proceedings of the 2022 International Power Electronics Conference (IPEC-Himeji 2022-ECCE Asia), Himeji, Japan, 15–19 May 2022; pp. 2213–2218. [Google Scholar]

- Dacol, R.P.; Heerdt, J.A.; Waltrich, G. Non-Isolated High Current Battery Charger with PFC Semi-Bridgeless Rectifier. In Proceedings of the 2019 IEEE 15th Brazilian Power Electronics Conference and 5th IEEE Southern Power Electronics Conference (COBEP/SPEC), Santos, Brazil, 1–4 December 2019; pp. 1–6. [Google Scholar]

- Dong, S.; Yang, X.; Xu, Y.; Wei, J.; Wang, K. GaN-based Interleaved CRM Totem-pole PFC Rectifier with Variable-step Adaptive ZVS Control. In Proceedings of the 2022 IEEE International Power Electronics and Application Conference and Exposition (PEAC), Guangzhou, China, 4–7 November 2022; pp. 247–251. [Google Scholar]

- Fan, C.; Liu, F.; Zhao, S. Research on SiC-based Totem-pole Bridgeless PFC Converter and Control Strategy. In Proceedings of the 2023 6th International Conference on Energy, Electrical and Power Engineering (CEEPE), Guangzhou, China, 21–23 April 2023; pp. 654–659. [Google Scholar] [CrossRef]

- Kwak, B.; Kim, J. Digital Implementation Method for Synchronous PWM Control of GaN Transistor at Zero-Crossing of Totem-Pole PFC in Energy Storage Applications. Electronics 2021, 10, 30. [Google Scholar] [CrossRef]

- Lee, Y.-D.; Baek, J.; Moon, G.-W.; Kim, C.-E. A Reconfigurable Totem-pole PFC Rectifier with Light Load Optimization Control Strategy and Soft-Switching Capability. IEEE Trans. Power Electron. 2021, 36, 4371–4382. [Google Scholar] [CrossRef]

- Naraharisetti, K.; Channegowda, J.; Green, P.B. Design and modeling of CCM average current control PFC AC-DC Boost converter. In Proceedings of the 2021 IEEE Green Technologies Conference (GreenTech), Denver, CO, USA, 7–9 April 2021; pp. 403–408. [Google Scholar]

- Gandhi, B.; Ezhilmaran, M. Achieving high input power factor for DCM boost PFC converters by controlling variable duty cycle. In Proceedings of the 2013 International Conference on Computation of Power, Energy, Information and Communication (ICCPEIC), Chennai, India, 17–18 April 2013; pp. 18–20. [Google Scholar]

- Chen, X.; Son, G.; Jin, F.; Li, Q. A Microcontroller-Based High Efficiency Critical Conduction Mode Control for GaN-Based Totem-Pole PFC. In Proceedings of the 2021 IEEE 22nd Workshop on Control and Modelling of Power Electronics (COMPEL), Cartagena, Colombia, 2–5 November 2021; pp. 1–7. [Google Scholar]

- El Aroudi, A.; Haroun, R.; Cid-Pastor, A.; Martinez-Salamero, L. Suppression of Line Frequency Instabilities in PFC AC-DC Power Supplies by Feedback Notch Filtering the Pre-Regulator Output Voltage. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 796–809. [Google Scholar] [CrossRef]

- Rao, V.M.; Jain, A.K.; Reddy, K.K.; Behal, A. Experimental Comparison of Digital Implementations of Single-Phase PFC Controllers. IEEE Trans. Ind. Electron. 2008, 55, 67–78. [Google Scholar] [CrossRef]

- Cabezas, J.J.; González-Medina, R.; Figueres, E.; Garcerá, G. Comparison and combination of digital controls for single-phase boost PFC converters in avionic power systems. In Proceedings of the 2017 IEEE 26th International Symposium on Industrial Electronics (ISIE), Edinburgh, UK, 19–21 June 2017; pp. 645–650. [Google Scholar]

- Sun, B. How to reduce current spikes at AC zero-crossing for totem-pole PFC. Analog. Appl. J. 2015. Available online: https://www.ti.com/lit/slyt650 (accessed on 1 September 2023).

- Sun, B. Control challenges in a totem-pole PFC. Analog. Appl. J. 2017. Available online: https://www.ti.com/lit/pdf/slyt718 (accessed on 1 June 2023).

- Gong, X.; Wang, G.; Bhardwaj, M. 6.6kW Three-Phase Interleaved Totem Pole PFC Design with 98.9% Peak Efficiency for HEV/EV Onboard Charger. In Proceedings of the 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), Anaheim, CA, USA, 17–21 March 2019; pp. 2029–2034. [Google Scholar]

- Koh, H.-G.; Ko, H.-J.; Choi, Y.-J. A MPCC-Based Variable Sampling Time Interleaving Method for a Two-Phase Totem-Pole Bridgeless Boost PFC Converter. IEEE Access 2023, 11, 104295–104304. [Google Scholar]

- Lee, J.-Y.; Chen, J.-H.; Lo, K.-Y. Design of a GaN Totem-Pole PFC Converter Using DC-Link Voltage Control Strategy for Data Center Applications. IEEE Access 2022, 10, 50278–50287. [Google Scholar]

| Parameters | Symbol | Values |

|---|---|---|

| Rated power | P | 3 kW |

| Input grid voltage | vac | 90~120 Vrms |

| Output voltage | vdc | 190~250 V |

| Inductance | L | 1.3 mH |

| Capacitance | C | 1.05 mF |

| Switching frequency | fsw | 10 kHz |

| Sampling time | Tsamp | 100 μs |

| Parameters | Symbol | Values |

|---|---|---|

| P gain of voltage controller | Kpv | 0.08 |

| I gain of voltage controller | Kiv | 10.0 |

| P gain of current controller | Kpi | 0.02 |

| I gain of current controller | Kii | 5.0 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, G.-Y.; Park, H.-C.; Ji, M.-W.; Kim, R.-Y. Digitalized Control Algorithm of Bridgeless Totem-Pole PFC with a Simple Control Structure Based on the Phase Angle. Electronics 2023, 12, 4449. https://doi.org/10.3390/electronics12214449

Lee G-Y, Park H-C, Ji M-W, Kim R-Y. Digitalized Control Algorithm of Bridgeless Totem-Pole PFC with a Simple Control Structure Based on the Phase Angle. Electronics. 2023; 12(21):4449. https://doi.org/10.3390/electronics12214449

Chicago/Turabian StyleLee, Gi-Young, Hae-Chan Park, Min-Woo Ji, and Rae-Young Kim. 2023. "Digitalized Control Algorithm of Bridgeless Totem-Pole PFC with a Simple Control Structure Based on the Phase Angle" Electronics 12, no. 21: 4449. https://doi.org/10.3390/electronics12214449