SiC Trench MOSFET with Depletion-Mode pMOS for Enhanced Short-Circuit Capability and Switching Performance

Abstract

:1. Introduction

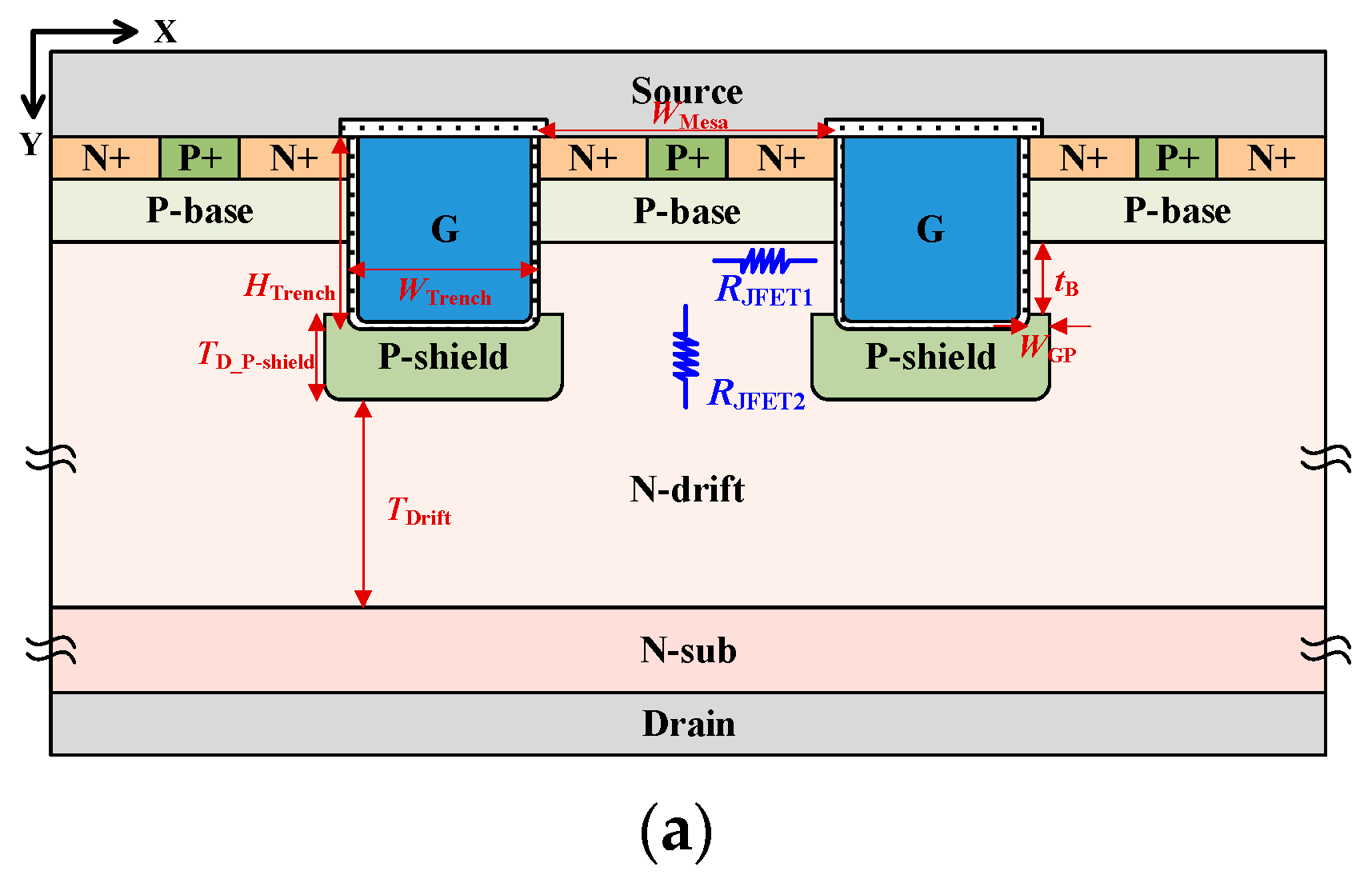

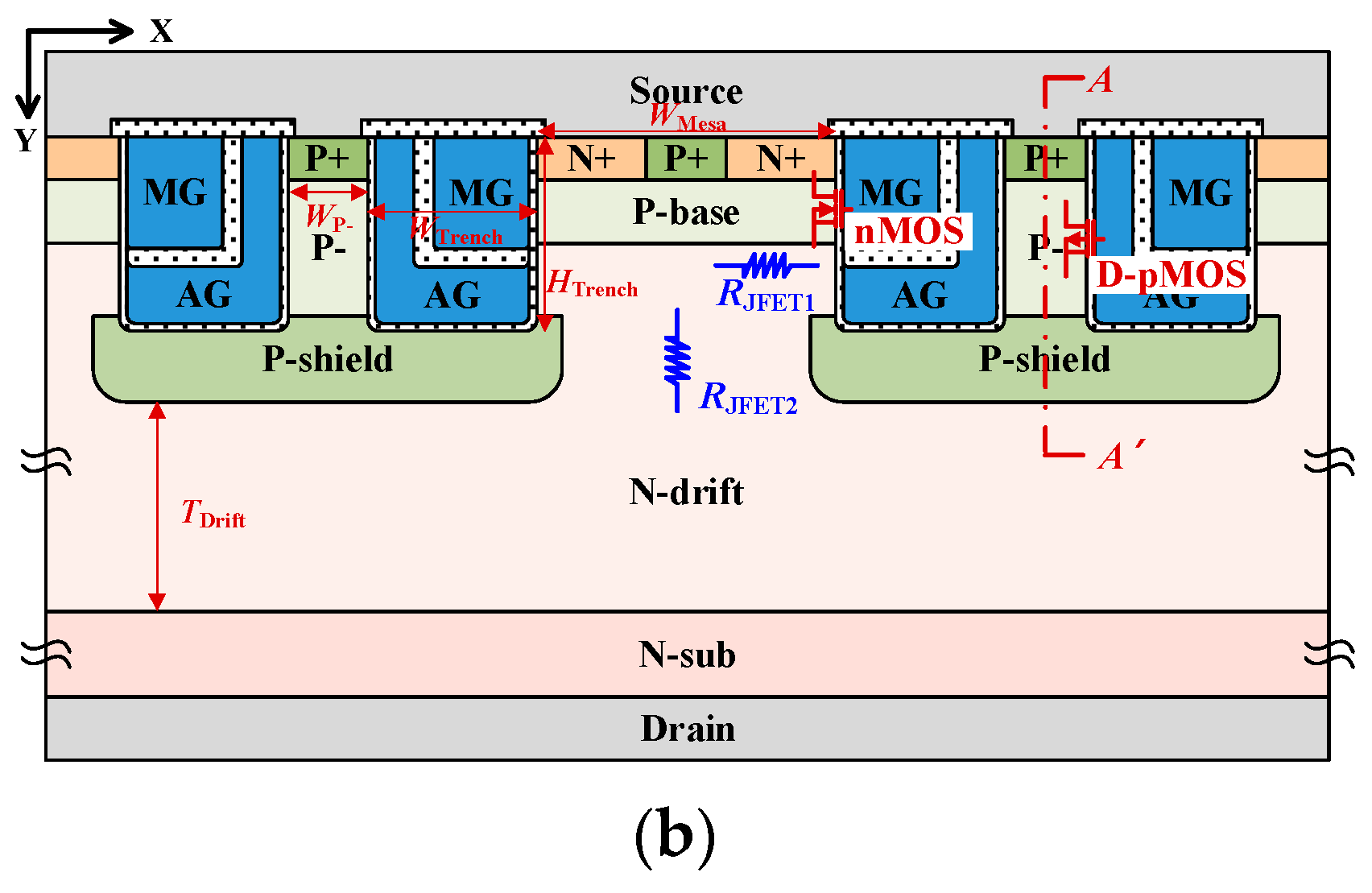

2. Device Structure and Design Concept

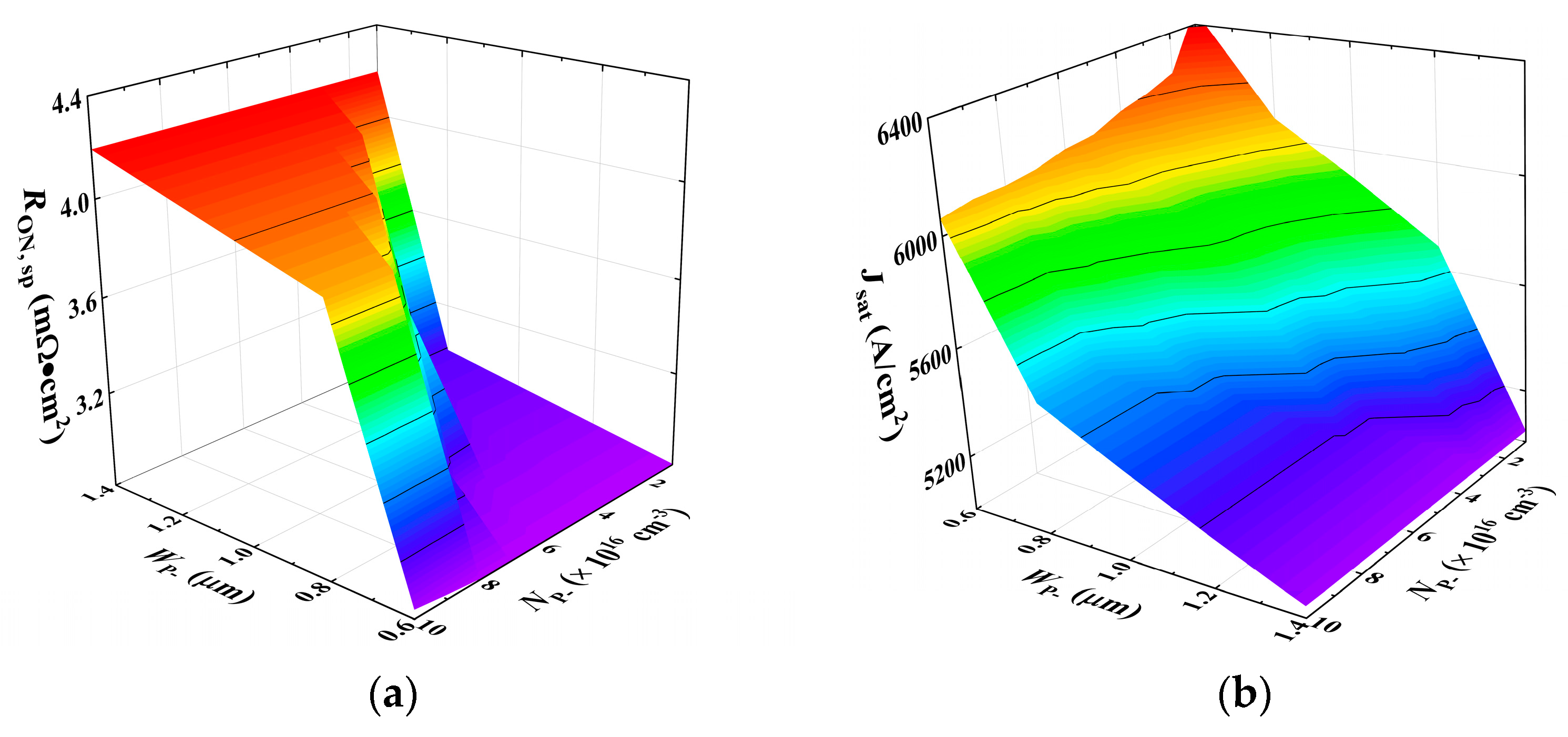

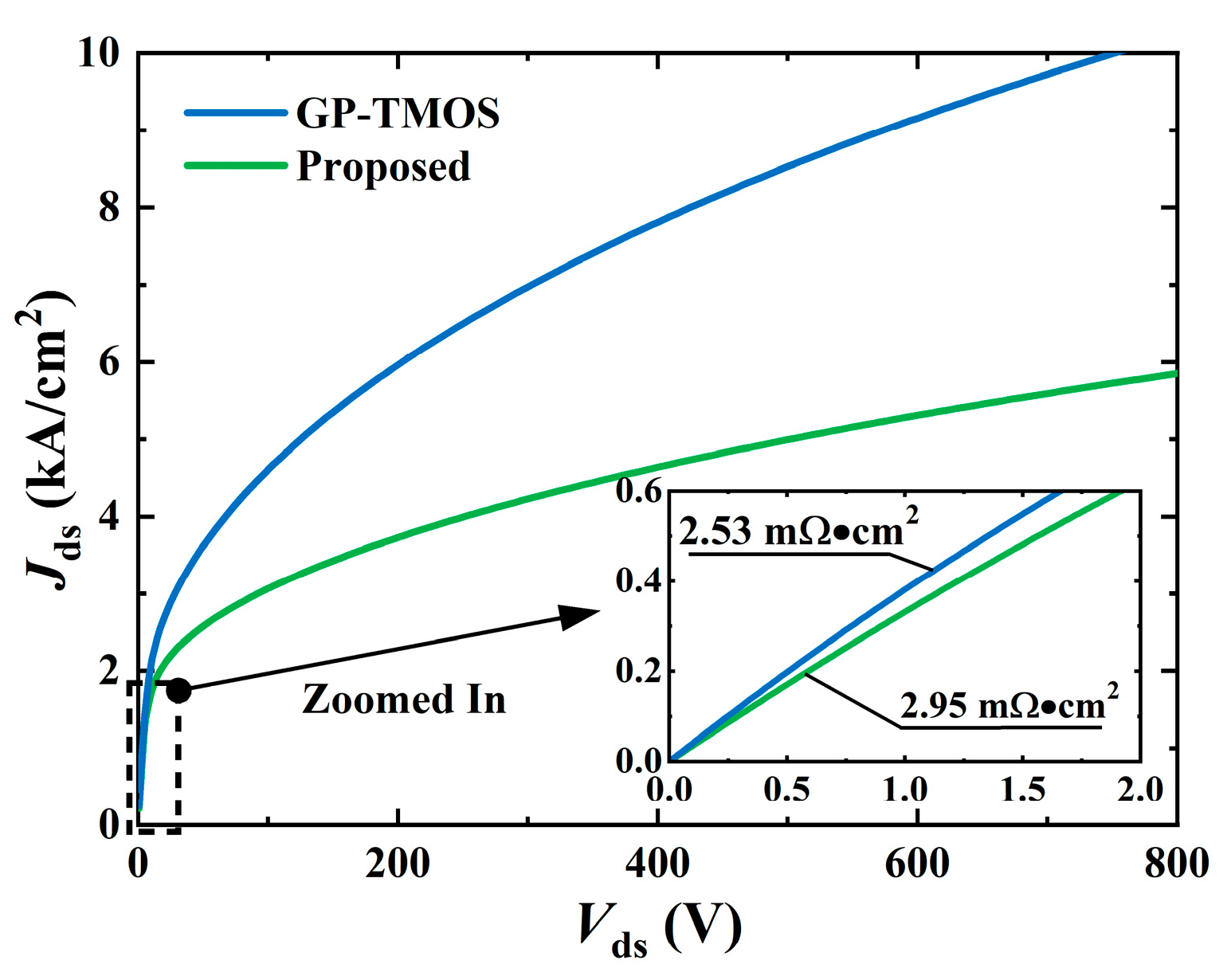

3. Simulation Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Wang, J.; Zhao, T.; Li, J.; Huang, A.Q.; Callanan, R.; Husna, F.; Agarwal, A. Characterization, Modeling, and Application of 10-kV SiC MOSFET. IEEE Trans. Electron Devices 2008, 55, 1798–1806. [Google Scholar] [CrossRef]

- Zishun, P.; Jun, W.; Zeng, L.; Zongjian, L.; Yuxing, D.; Guoqiang, Z.; John, S.Z. A Variable-Frequency Current-Dependent Switching Strategy to Improve Tradeoff Between Efficiency and SiC MOSFET Overcurrent Stress in Si/SiC-Hybrid-Switch-Based Inverters. IEEE Trans. Power Electron. 2021, 36, 4877–4886. [Google Scholar]

- Kimoto, T.; Cooper, J.A. Fundamentals of Silicon Carbide Technology: Growth, Characterization, Devices and Applications; IEEE Press: Piscataway, NJ, USA, 2014; pp. 11–33. [Google Scholar]

- Shinojima, Y. Automotive semiconductors in the CASE era. In Proceedings of the 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Nagoya, Japan, 30 May–3 June 2021; pp. 1–5. [Google Scholar] [CrossRef]

- Zhu, J.; Kim, H.; Chen, H.; Erickson, R.; Maksimovic, D. High efficiency SiC traction inverter for electric vehicle applications. In Proceedings of the 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 4–8 March 2018; pp. 1428–1433. [Google Scholar] [CrossRef]

- Palmour, J.W.; Edmond, J.A.; Kong, H.S.; Carter, C.H., Jr. 6H silicon carbide power devices for aerospace applications. In Proceedings of the 28th Intersociety Energy Conversion Engineering Conference, Atlanta, GA, USA, 8–13 August 1993; pp. 1.249–1.254. [Google Scholar]

- Li, Y.; Cooper, J.; Capano, M. High-voltage (3 kV) UMOSFETs in 4H-SiC. IEEE Trans. Electron Devices 2002, 49, 972–975. [Google Scholar] [CrossRef]

- Sui, Y.; Tsuji, T.; Cooper, J. On-State Characteristics of SiC power UMOSFETs on 115-/spl mu/m drift Layers. IEEE Electron Device Lett. 2005, 26, 255–257. [Google Scholar] [CrossRef]

- Losee, P.A.; Bolotnikov, A.; Yu, L.C.; Dunne, G.; Esler, D.; Erlbaum, J.; Rowden, B.; Gowda, A.; Halverson, A.; Ghandi, R.; et al. SiC MOSFET design considerations for reliable high voltage operation. In Proceedings of the 2017 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 2–6 April 2017; pp. 2A-2.1–2A-2.8. [Google Scholar] [CrossRef]

- Song, Q.; Yang, S.; Tang, G.; Han, C.; Zhang, Y.; Tang, X.; Zhang, Y. 4H-SiC Trench MOSFET with L-Shaped Gate. IEEE Electron Device Lett. 2016, 37, 463–466. [Google Scholar] [CrossRef]

- Harada, S.; Kobayashi, Y.; Ariyoshi, K.; Kojima, T.; Senzaki, J.; Tanaka, Y.; Okumura, H. 3.3-kV-Class 4H-SiC MeV-Implanted UMOSFET With Reduced Gate Oxide Field. IEEE Electron Device Lett. 2016, 37, 314–316. [Google Scholar] [CrossRef]

- Shen, Z.; Zhang, F.; Yan, G.; Wen, Z.; Zhao, W.; Wang, L.; Liu, X.; Sun, G.; Zeng, Y. High-Frequency Switching Properties and Low Oxide Electric Field and Energy Loss in a Reverse-Channel 4H-SiC UMOSFET. IEEE Trans. Electron Devices 2020, 67, 4046–4053. [Google Scholar] [CrossRef]

- Nakamura, R.; Nakano, Y.; Aketa, M.; Noriaki, K.; Ino, K. 1200V 4H-SiC Trench Devices. In Proceedings of the PCIM Europe 2014; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 20–22 May 2014; pp. 1–7. [Google Scholar]

- Peters, D.; Basler, T.; Zippelius, B.; Aichinger, T.; Bergner, W.; Esteve, R.; Kueck, D.; Siemieniec, R. The New CoolSiCTM Trench MOSFET Technology for Low Gate Oxide Stress and High Performance. In Proceedings of the PCIM Europe 2017, International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 20–22 May 2017; pp. 1–7. [Google Scholar]

- Zhou, X.; Yue, R.; Zhang, J.; Dai, G.; Li, J.; Wang, Y. 4H-SiC Trench MOSFET with Floating/Grounded Junction Barrier-controlled Gate Structure. IEEE Trans. Electron Devices 2017, 64, 4568–4574. [Google Scholar] [CrossRef]

- Takaya, H.; Misumi, T.; Fujiwara, H.; Ito, T. 4H-SiC Trench MOSFET with low on-resistance at high temperature. In Proceedings of the 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Vienna, Austria, 13–18 September 2020; pp. 118–121. [Google Scholar] [CrossRef]

- Wang, Y.; Tian, K.; Hao, Y.; Yu, C.-H.; Liu, Y.-J. An Optimized Structure of 4H-SiC U-Shaped Trench Gate MOSFET. IEEE Trans. Electron Devices 2015, 62, 2774–2778. [Google Scholar] [CrossRef]

- Wei, J.; Zhang, M.; Jiang, H.; Cheng, C.-H.; Chen, K.J. Low ON-Resistance SiC Trench/Planar MOSFET With Reduced OFF-State Oxide Field and Low Gate Charges. IEEE Electron Device Lett. 2016, 37, 1458–1461. [Google Scholar] [CrossRef]

- Zhang, M.; Wei, J.; Jiang, H.; Chen, K.J.; Cheng, C. SiC trench MOSFET with self-biased p-shield for low R ON-SP and low OFF-state oxide field. IET Power Electron. 2017, 10, 1208–1213. [Google Scholar] [CrossRef]

- Xing, Y.; Deng, X.; Wu, H.; Xu, X.; Li, X.; Li, X.; Wen, Y. An enhanced high frequency performance SiC MOSFET with self-adjusting P-shield region potential. Semicond. Sci. Technol. 2022, 37, 85019. [Google Scholar] [CrossRef]

- Wang, Z.; Shi, X.; Tolbert, L.M.; Wang, F.; Liang, Z.; Costinett, D.; Blalock, B.J. Temperature-Dependent Short-Circuit Capability of Silicon Carbide Power MOSFETs. IEEE Trans. Power Electron. 2016, 31, 1555–1566. [Google Scholar] [CrossRef]

- Deng, X.; Li, X.; Li, X.; Zhu, H.; Xu, X.; Wen, Y.; Sun, Y.; Chen, W.; Li, Z.; Zhang, B. Short-Circuit Capability Prediction and Failure Mode of Asymmetric and Double Trench SiC MOSFETs. IEEE Trans. Power Electron. 2021, 36, 8300–8307. [Google Scholar] [CrossRef]

- Yang, T.; Wang, Y.; Yue, R. SiC Trench MOSFET with Reduced Switching Loss and Increased Short-Circuit Capability. IEEE Trans. Electron Devices 2020, 67, 3685–3690. [Google Scholar] [CrossRef]

- Ni, W.; Wang, X.; Xu, M.; Wang, Q.; Feng, C.; Xiao, H.; Jiang, L.; Li, W. Study of Asymmetric Cell Structure Tilt Implanted 4H-SiC Trench MOSFET. IEEE Electron Device Lett. 2019, 40, 698–701. [Google Scholar] [CrossRef]

- Baliga, B.J. Fundamentals of Power Semiconductor Devices; Springer: New York, NY, USA, 2008; pp. 363–373. [Google Scholar]

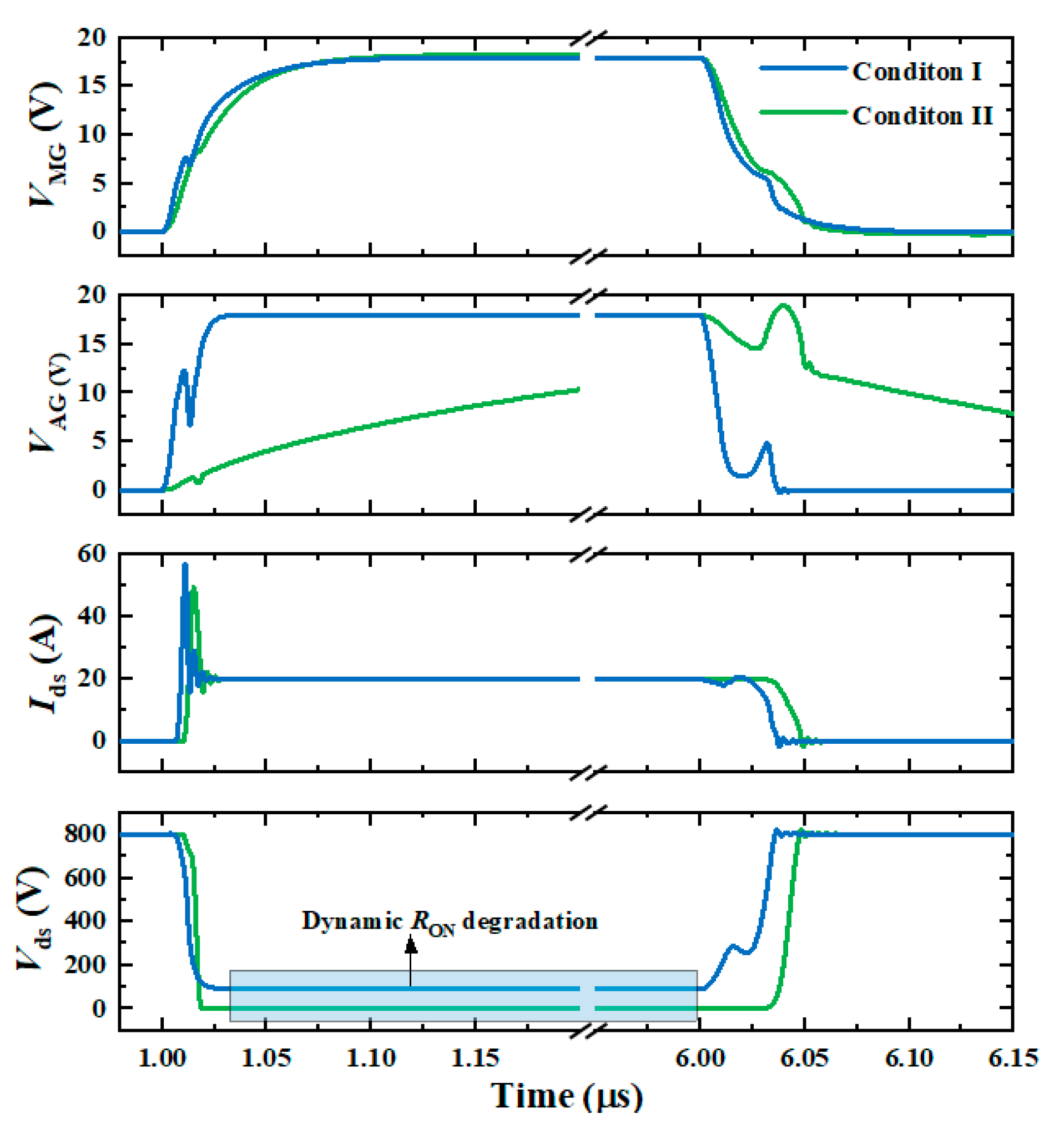

- Wei, J.; Zhang, M.; Jiang, H.; Wang, H.; Chen, K.J. Dynamic Degradation in SiC Trench MOSFET with a Floating p-Shield Revealed with Numerical Simulations. IEEE Trans. Electron Devices 2017, 64, 2592–2598. [Google Scholar] [CrossRef]

- Han, K.; Baliga, B.J.; Sung, W. Split-Gate 1.2-kV 4H-SiC MOSFET: Analysis and Experimental Validation. IEEE Electron Device Lett. 2017, 38, 1437–1440. [Google Scholar] [CrossRef]

- Kim, D.; De Boer, S.; Mancini, S.A.; Isukapati, S.B.; Lynch, J.; Yun, N.; Morgan, A.J.; Jang, S.Y.; Sung, W. Static, Dynamic, and Short-circuit Characteristics of Split-Gate 1.2 kV 4H-SiC MOSFETs. In Proceedings of the 2023 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 26–30 March 2023; pp. 1–4. [Google Scholar] [CrossRef]

| Device Parameters | Proposed | GP-TMOS |

|---|---|---|

| N-drift layer thickness, Tdrift | 12.0 μm | 12.0 μm |

| N-drift layer concentration, Ndrift | 8.0 × 1015 cm−3 | 8.0 × 1015 cm−3 |

| Trench width, WTrench | 1.5 μm | 1.0 μm |

| Trench depth, HTrench | 1.6 μm | 1.6 μm |

| P-shield layer thickness, TP-shield | 0.5 μm | 0.5 μm |

| Distance of P-shield layer beyond the gate trench, WGP | 0.3 μm | 0.3 μm |

| P-layer concentration, NP- | 4.0 × 1016 cm−3 | - |

| P-layer width, WP- | 1.0 μm | - |

| P-base mesa width, Wmesa | 3.0 μm | 3.0 μm |

| Inversion channel length, LCH | 0.5 μm | 0.5 μm |

| Gate oxide thickness, Toxide | 50 nm | 50 nm |

| Cell width, Wcell | 7.0 μm | 4.0 μm |

| Active area | 10.0 mm2 | 10.0 mm2 |

| Proposed | GP-TMOS | |

|---|---|---|

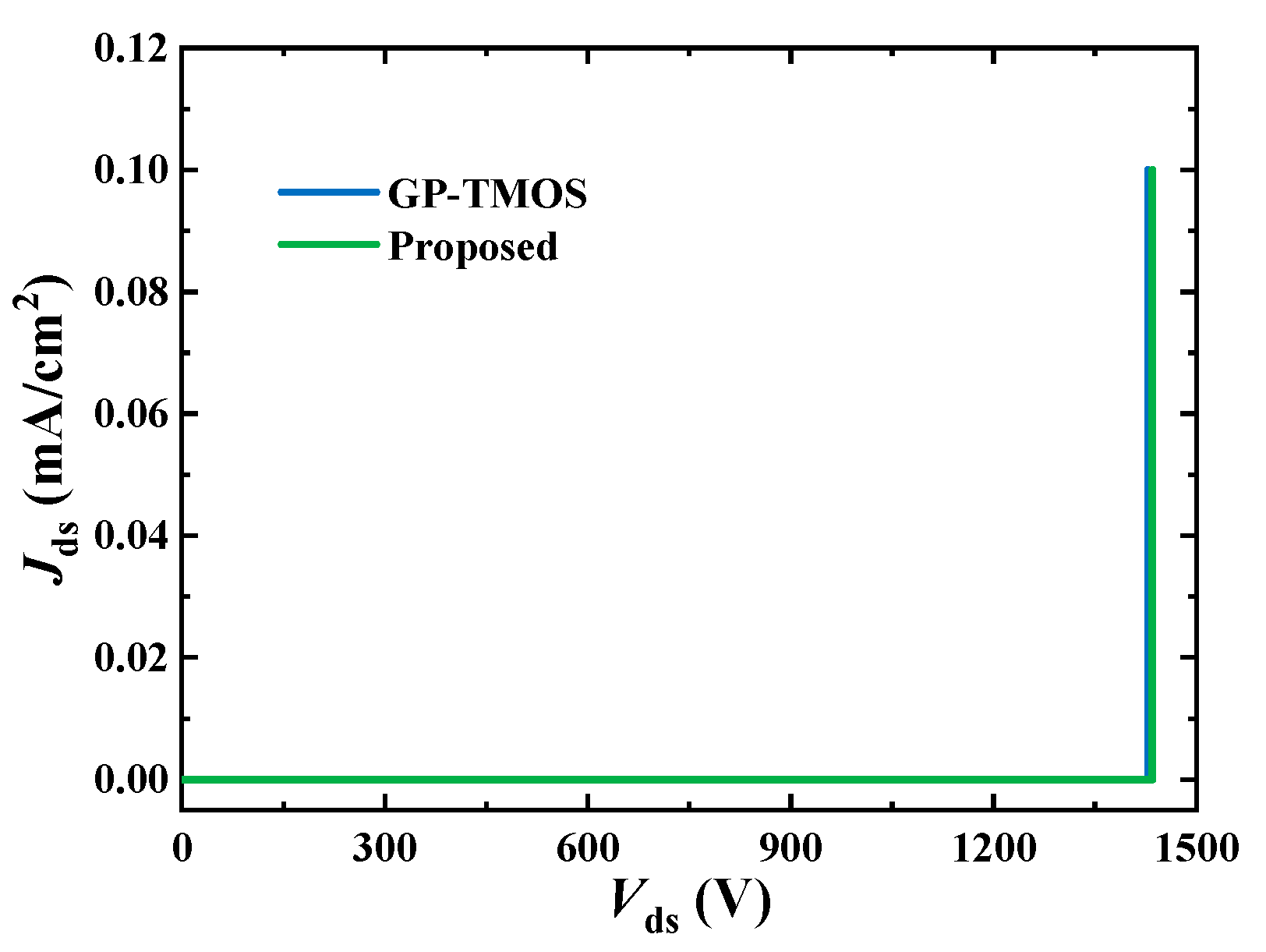

| RON, sp a [mΩ·cm2] | 2.95 | 2.53 |

| BV b [V] | 1434 | 1428 |

| Jsat c [kA/cm2] | 5.85 | 10.22 |

| tSC d [μs] | 10.0 | 5.2 |

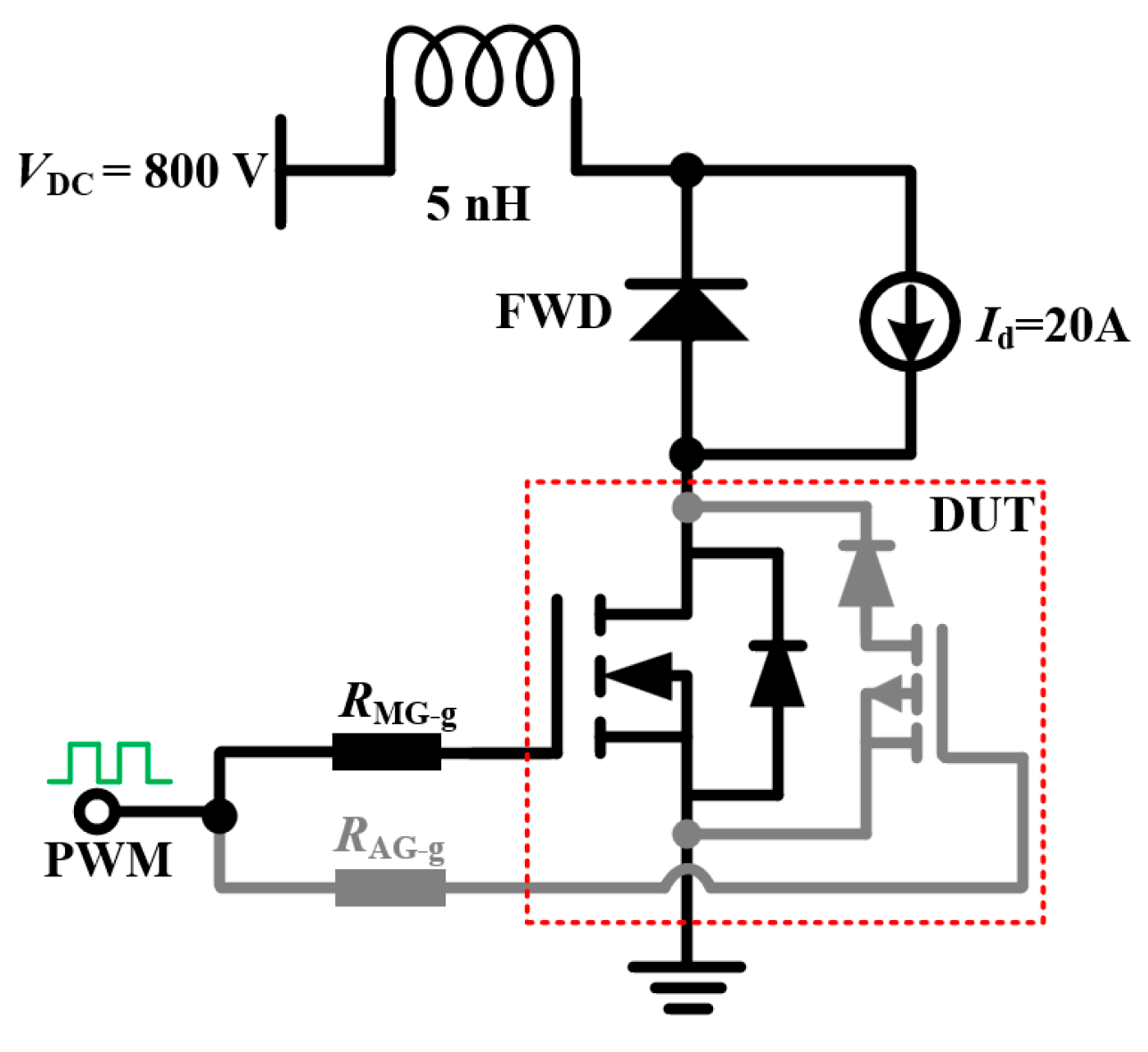

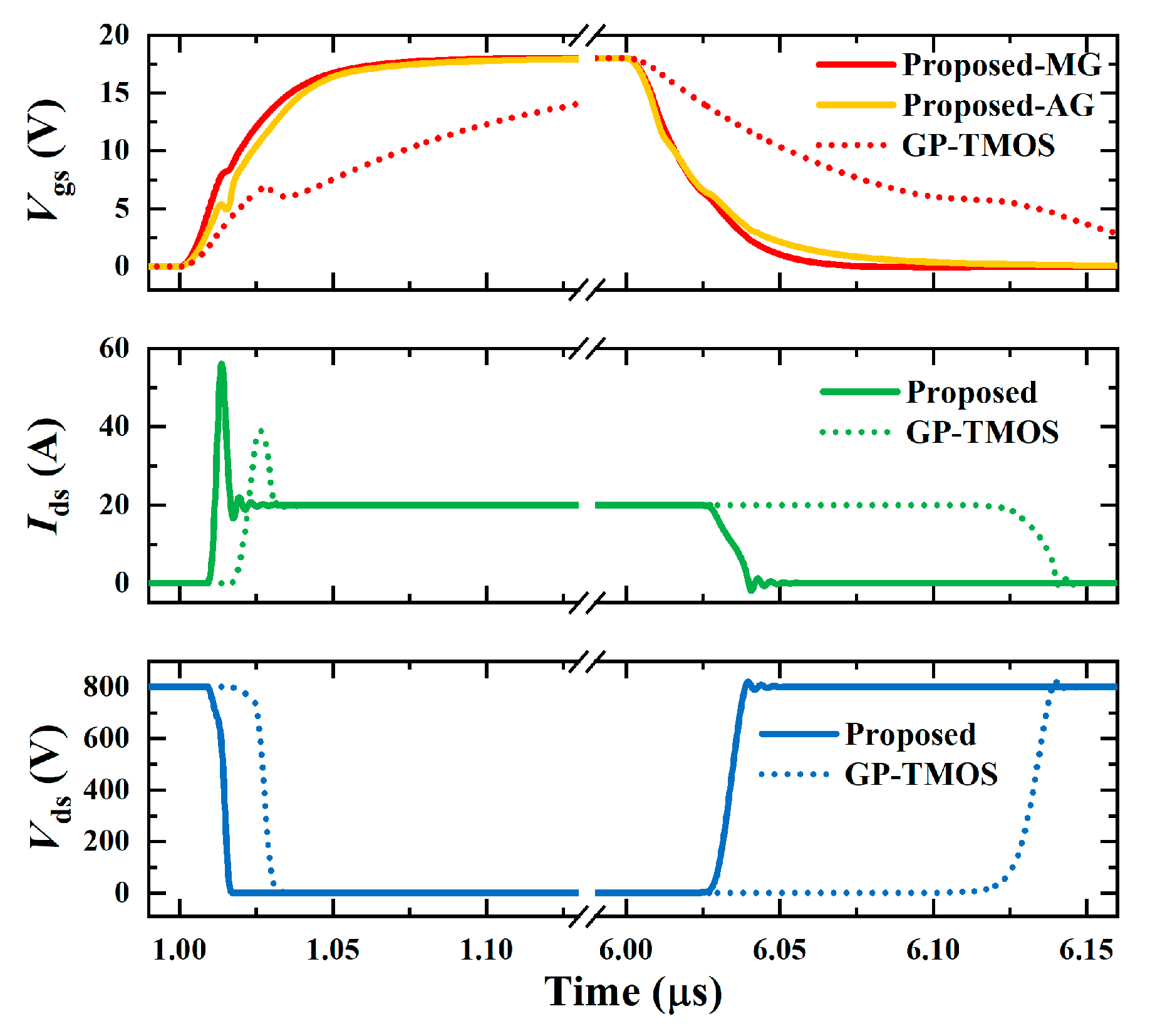

| td (on) e [ns] | 5.8 | 15.4 |

| tr f [ns] | 4.6 | 4.9 |

| td (off) g [ns] | 23.6 | 110 |

| tf h [ns] | 7.8 | 12.4 |

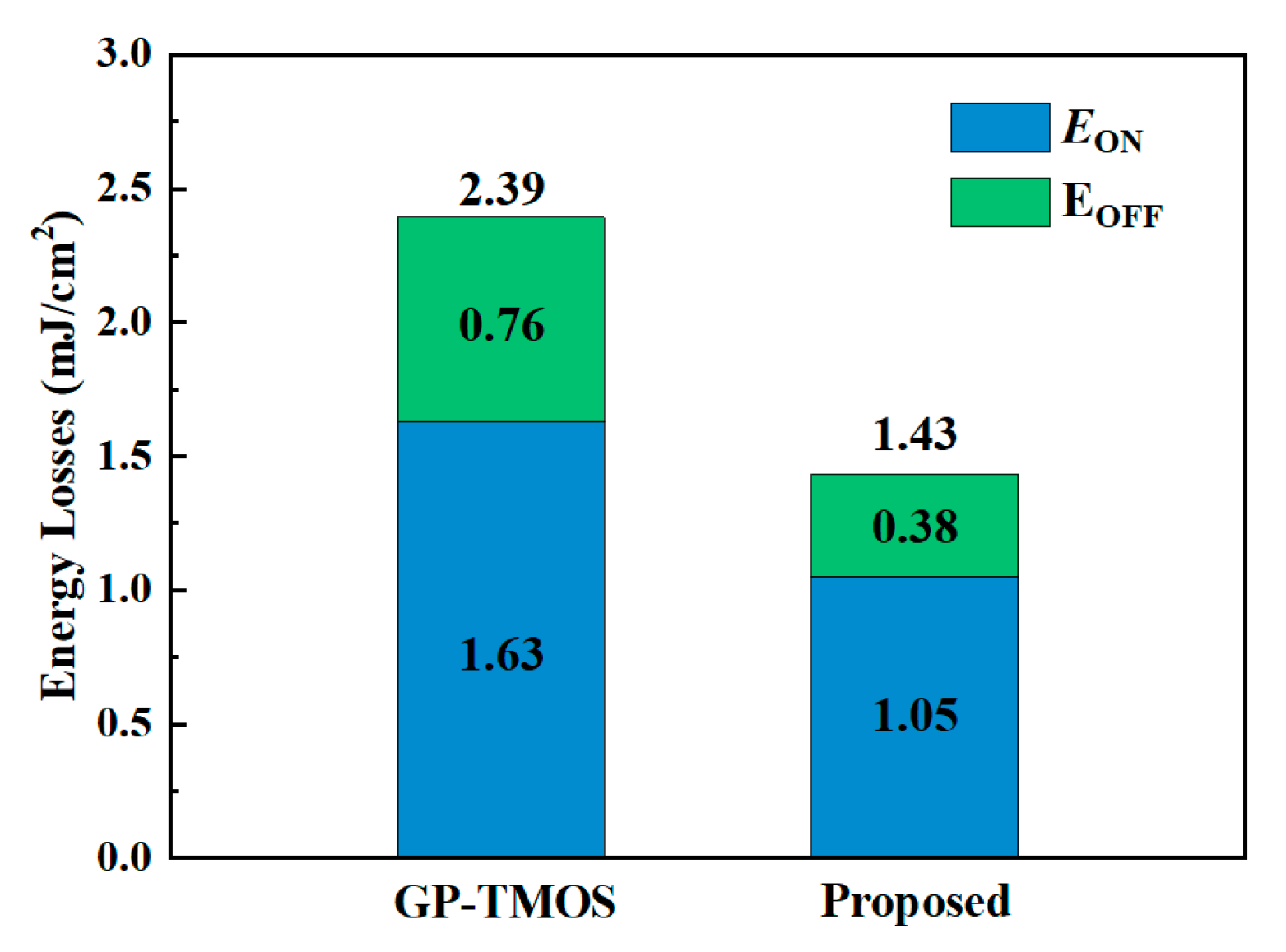

| EON i [mJ/cm2] | 1.05 | 1.63 |

| EOFF j [mJ/cm2] | 0.38 | 0.76 |

| ESW [mJ/cm2] | 1.43 | 2.39 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yu, H.; Shi, L.; Bhattacharya, M.; Jin, M.; Qian, J.; Agarwal, A.K. SiC Trench MOSFET with Depletion-Mode pMOS for Enhanced Short-Circuit Capability and Switching Performance. Electronics 2023, 12, 4764. https://doi.org/10.3390/electronics12234764

Yu H, Shi L, Bhattacharya M, Jin M, Qian J, Agarwal AK. SiC Trench MOSFET with Depletion-Mode pMOS for Enhanced Short-Circuit Capability and Switching Performance. Electronics. 2023; 12(23):4764. https://doi.org/10.3390/electronics12234764

Chicago/Turabian StyleYu, Hengyu, Limeng Shi, Monikuntala Bhattacharya, Michael Jin, Jiashu Qian, and Anant K. Agarwal. 2023. "SiC Trench MOSFET with Depletion-Mode pMOS for Enhanced Short-Circuit Capability and Switching Performance" Electronics 12, no. 23: 4764. https://doi.org/10.3390/electronics12234764

APA StyleYu, H., Shi, L., Bhattacharya, M., Jin, M., Qian, J., & Agarwal, A. K. (2023). SiC Trench MOSFET with Depletion-Mode pMOS for Enhanced Short-Circuit Capability and Switching Performance. Electronics, 12(23), 4764. https://doi.org/10.3390/electronics12234764