Mapping Outputs and States Encoding Bits to Outputs Using Multiplexers in Finite State Machine Implementations

Abstract

1. Introduction

2. Background

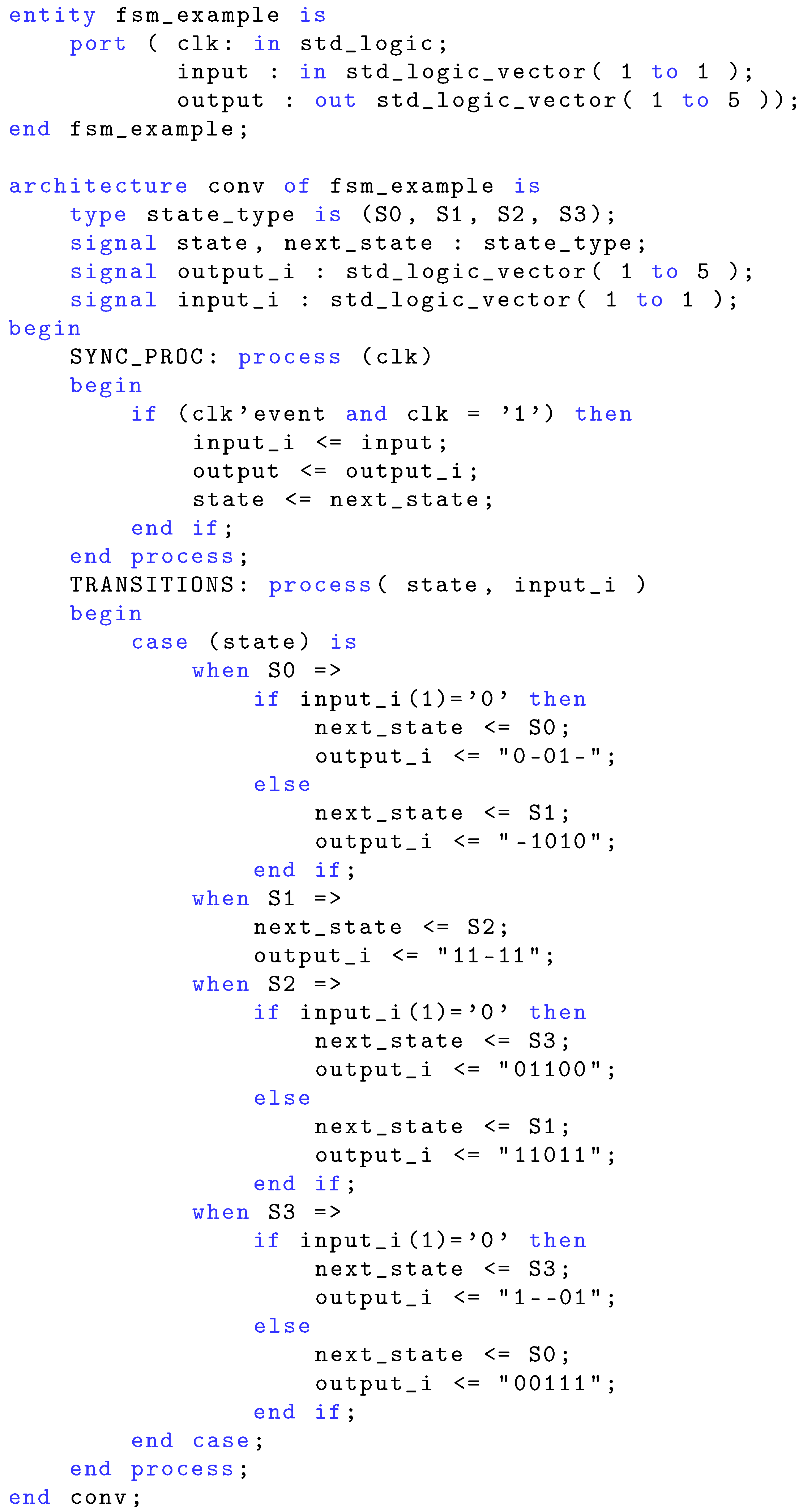

3. Mapping Outputs and States Encoding Bits to Outputs by Means of Multiplexers

4. Integer Linear Programming Formulation

- for all , which is equal to one if and only if can be generated from and via a multiplexer controlled by so that for all transitions in which , and for the remaining ( is therefore mapped to and ).

- for all , which is equal to one if and only if can be generated from and via a multiplexer controlled by so that for all transitions in which , and for the remaining ( is therefore mapped to and ).

- for all , which represents the value of the for the transition corresponding to the i-th row of the STT. Note that must be equal to for all such that (i.e., is not a don’t care); however, the remainder values of will be determined by the solver.

- for all , which represents the j-th bit of the encoding of .

- for all such that , which is equal to one if and only if i-th bit of the encoding of and that of are different.

5. Experimental Results

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Katz, R.H. Contemporary Logic Design; Benjamin/Cummings: Redwood City, CA, USA, 1994. [Google Scholar]

- Barkalov, A.; Titarenko, L. Logic Synthesis for FSM-Based Control Units; Lecture Notes in Electrical Engineering; Springer: Berlin/Heidelberg, Germany, 2009. [Google Scholar]

- Barkalov, A.; Titarenko, L.; Kolopienczyk, M.; Mielcarek, K.; Bazydlo, G. Design of EMB-Based Mealy FSMs. In Logic Synthesis for FPGA-Based Finite State Machines; Springer International Publishing: Berlin/Heidelberg, Germany, 2016; pp. 193–237. [Google Scholar] [CrossRef]

- Baranov, S. Logic and System Design of Digital Systems; TUT Press: Tallin, Estonia, 2008. [Google Scholar]

- Barkalov, A.; Titarenko, L.; Mielcarek, K.; Chmielewski, S. Twofold State Assignment for Mealy FSMs. In Logic Synthesis for FPGA-Based Control Units; Springer: Berlin/Heidelberg, Germany, 2020; pp. 61–90. [Google Scholar]

- Barkalov, A.; Titarenko, L.; Mielcarek, K.; Chmielewski, S. Twofold State Assignment for Moore FSMs. In Logic Synthesis for FPGA-Based Control Units; Springer: Berlin/Heidelberg, Germany, 2020; pp. 91–116. [Google Scholar]

- El-Maleh, A. A Probabilistic Tabu Search State Assignment Algorithm for Area and Power Optimization of Sequential Circuits. Arab. J. Sci. Eng. 2020, 45, 6273–6285. [Google Scholar] [CrossRef]

- da Silva Ribeiro, R.; de Carvalho, R.L.; da Silva Almeida, T. Optimization of state assignment in a finite state machine. Acad. J. Comput. Eng. Appl. Math. 2022, 3, 9–16. [Google Scholar] [CrossRef]

- Solov’ev, V. Minimization of mealy finite-state machines by using the values of the output variables for state assignment. J. Comput. Syst. Sci. Int. 2017, 56, 96–104. [Google Scholar] [CrossRef]

- Salauyou, V.; Ostapczuk, M. State Assignment of Finite-State Machines by Using the Values of Output Variables. In Theory and Applications of Dependable Computer Systems. Advances in Intelligent Systems and Computing; Springer: Berlin/Heidelberg, Germany, 2020; Volume 1173, pp. 91–116. [Google Scholar]

- Das, N.; Priya P, A. Reset: A Reconfigurable state encoding technique for FSM to achieve security and hardware optimality. Microprocess. Microsyst. 2020, 77, 103196. [Google Scholar] [CrossRef]

- Barkalov, A.A.; Titarenko, L.; Mielcarek, K. Reducing LUT Count for Mealy FSMs With Transformation of States. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2022, 41, 1400–1411. [Google Scholar] [CrossRef]

- Aly, W.M. Solving the State Assignment Problem Using Stochastic Search Aided with Simulated Annealing. Am. J. Eng. Appl. Sci. 2009, 2, 703–707. [Google Scholar] [CrossRef][Green Version]

- De Micheli, G.; Brayton, R.; Sangiovanni-Vincentelli, A. Optimal State Assignment for Finite State Machines. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 1985, 4, 269–285. [Google Scholar] [CrossRef]

- Villa, T.; Sangiovanni-Vincentelli, A. NOVA: State assignment of finite state machines for optimal two-level logic implementation. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 1990, 9, 905–924. [Google Scholar] [CrossRef]

- Mengibar, L.; Entrena, L.; Lorenz, M.; Millan, E. Partitioned state encoding for low power in FPGAs. Electron. Lett. 2005, 41, 948–949. [Google Scholar] [CrossRef]

- Chen, D.S.; Sarrafzadeh, M.; Yeap, G. State encoding of finite state machines for low power design. In Proceedings of the 1995 IEEE International Symposium on Circuits and Systems (ISCAS), Seattle, DC, USA, 30 April–3 May 1995; Volume 3, pp. 2309–2312. [Google Scholar] [CrossRef]

- Avedillo, M.; Quintana, J.; Huertas, J. State merging and state splitting via state assignment: A new FSM synthesis algorithm. IEEE Proc. Comput. Digit. Tech. 1994, 141, 229–237. [Google Scholar] [CrossRef]

- Almaini, A.; Miller, J.; Thomson, P.; Billina, S. State assignment of finite state machines using a genetic algorithm. IEEE Proc. Comput. Digit. Tech. 1995, 142, 279–286. [Google Scholar] [CrossRef]

- El-Maleh, A.; Sait, S.; Nawaz Khan, F. Finite state machine state assignment for area and power minimization. In Proceedings of the 2006 IEEE International Symposium on Circuits and Systems, Kos, Greece, 21–24 May 2006; p. 4. [Google Scholar]

- Wei, R.S.; Tseng, C.J. Column compaction and its application to the control path synthesis. In Proceedings of the 1987 IEEE International Conference on Computer-Aided Design Digest of Technical Papers, Santa Clara, CA, USA, 9–12 November 1987; Volume 87, pp. 320–323. [Google Scholar]

- Binger, D.; Knapp, D. Encoding multiple outputs for improved column compaction. In Proceedings of the 1991 IEEE International Conference on Computer-Aided Design Digest of Technical Papers, Santa Clara, CA, USA, 11–14 November 1991; pp. 230–233. [Google Scholar] [CrossRef]

- Mitra, S.; Avra, L.; McCluskey, E. An output encoding problem and a solution technique. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 1999, 18, 761–768. [Google Scholar] [CrossRef][Green Version]

- Le Gal, B.; Ribon, A.; Bossuet, L.; Dallet, D. Area optimization of ROM-based controllers dedicated to digital signal processing applications. In Proceedings of the 2010 18th European Signal Processing Conference, Aalborg, Denmark, 23–27 August 2010; pp. 547–551. [Google Scholar]

- Lee, S.; Choi, K. Critical-Path-Aware High-Level Synthesis with Distributed Controller for Fast Timing Closure. ACM Trans. Des. Autom. Electron. Syst. 2014, 19, 1–29. [Google Scholar] [CrossRef]

- Xilinx. 7 Series FPGAs Configurable Logic Block: User Guide. 2016. Available online: https://docs.xilinx.com/v/u/en-US/ug474_7Series_CLB (accessed on 17 January 2023).

- Yang, S. Logic Synthesis and Optimization Benchmarks User Guide, Version 3.0; Microelectronic Center of North Carolina: Research Triangle, NC, USA, 1991. [Google Scholar]

- Rho, J.K.; Hachtel, G.D.; Somenzi, F.; Jacoby, R.M. Exact and heuristic algorithms for the minimization of incompletely specified state machines. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 1994, 13, 167–177. [Google Scholar] [CrossRef]

- Gurobi Optimization. Gurobi Optimizer Reference Manual. 2020. Available online: http://www.gurobi.com (accessed on 17 January 2023).

| CONV | OMOSEBO | Comparison | ||||

|---|---|---|---|---|---|---|

| FSM | # LUTs | Freq. | # LUTs | Freq. | LUT Red. | Freq. Inc. |

| (MHz) | (MHz) | (%) | (%) | |||

| s1 | 78 | 358 | 32 | 430 | 59 | 20 |

| mark1 | 26 | 443 | 15 | 592 | 42 | 34 |

| s27 | 7 | 649 | 5 | 693 | 29 | 7 |

| planet | 104 | 406 | 85 | 438 | 18 | 8 |

| opus | 17 | 567 | 14 | 665 | 18 | 17 |

| s510 | 58 | 461 | 50 | 440 | 14 | −5 |

| s820 | 77 | 389 | 68 | 396 | 12 | 2 |

| ex1 | 70 | 415 | 63 | 407 | 10 | −2 |

| ex6 | 20 | 643 | 18 | 627 | 10 | −2 |

| styr | 103 | 376 | 95 | 348 | 8 | −7 |

| ex4 | 15 | 742 | 14 | 716 | 7 | −4 |

| cse | 41 | 426 | 41 | 472 | 0 | 11 |

| s832 | 76 | 379 | 85 | 382 | −12 | 1 |

| keyb | 40 | 357 | 46 | 348 | −15 | −3 |

| mc | 3 | 907 | 4 | 851 | −33 | −6 |

| Mean | 49 | 501 | 42 | 520 | 11 | 5 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Senhadji-Navarro, R.; Garcia-Vargas, I. Mapping Outputs and States Encoding Bits to Outputs Using Multiplexers in Finite State Machine Implementations. Electronics 2023, 12, 502. https://doi.org/10.3390/electronics12030502

Senhadji-Navarro R, Garcia-Vargas I. Mapping Outputs and States Encoding Bits to Outputs Using Multiplexers in Finite State Machine Implementations. Electronics. 2023; 12(3):502. https://doi.org/10.3390/electronics12030502

Chicago/Turabian StyleSenhadji-Navarro, Raouf, and Ignacio Garcia-Vargas. 2023. "Mapping Outputs and States Encoding Bits to Outputs Using Multiplexers in Finite State Machine Implementations" Electronics 12, no. 3: 502. https://doi.org/10.3390/electronics12030502

APA StyleSenhadji-Navarro, R., & Garcia-Vargas, I. (2023). Mapping Outputs and States Encoding Bits to Outputs Using Multiplexers in Finite State Machine Implementations. Electronics, 12(3), 502. https://doi.org/10.3390/electronics12030502