Subthreshold Delay Variation Model Considering Transitional Region for Input Slew

Abstract

:1. Introduction

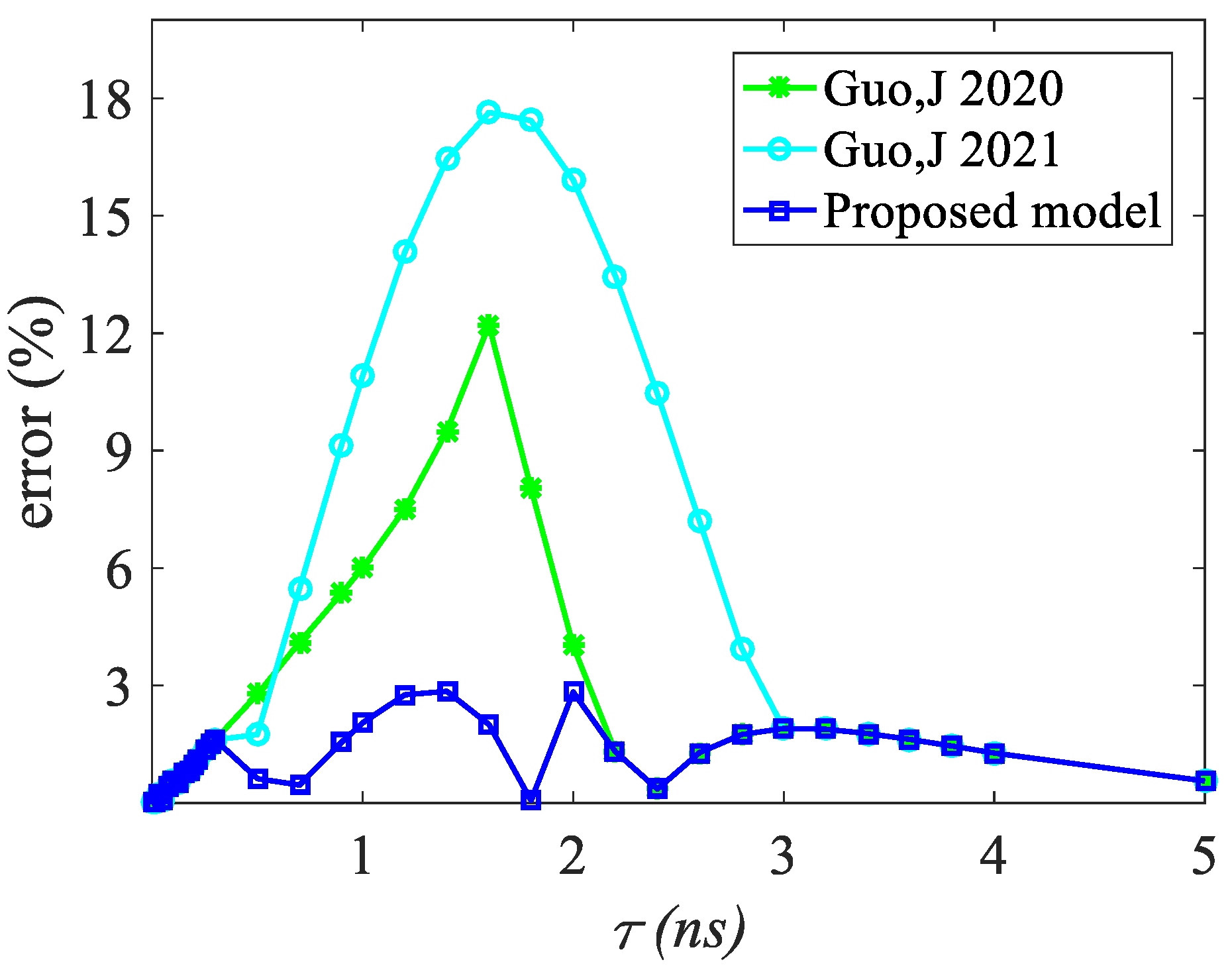

- To increase the model accuracy in the transitional region between fast and slow input slew, the impact of slew time between fast and slow input slew is partitioned efficiently with an adaptive error tolerance method and characterized by linear interpolation.

- The impact of load capacitance is analytically derived to be independent with the sensitivity of the step delay distribution as well as delay with non-step input slew, so that the variance of gate delay with different load capacitances could be efficiently characterized by scaling the mean of delay with a pre-characterized sensitivity for a reference load.

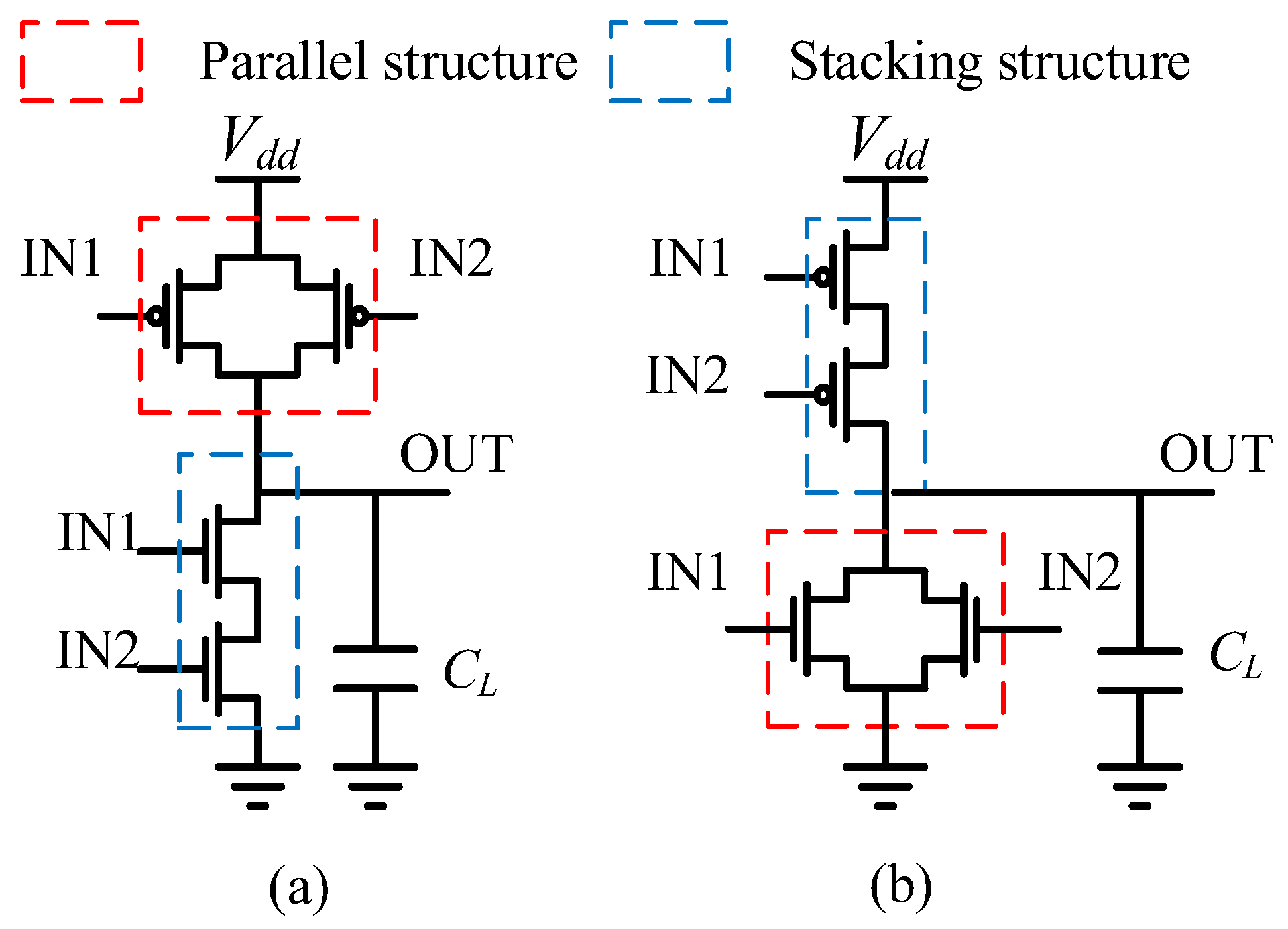

- To extend the timing variation model to complex gates, the dominant threshold voltage fluctuation is derived to be equivalent with those in multiple transistors for both parallel and stacking structures.

2. Proposed Subthreshold Timing Variation Model for Inverter

2.1. Timing Variation Model for Fast and Slow Input Slew

2.2. Timing Variation Model for Input Slew in Transitional Region

2.3. Timing Variation Model for Different Loads

3. Proposed Subthreshold Timing Variation Model for Complex Gates

3.1. Threshold Voltage Equivalence for Parallel Structure

3.2. Threshold Voltage Equivalence for Stacking Structure

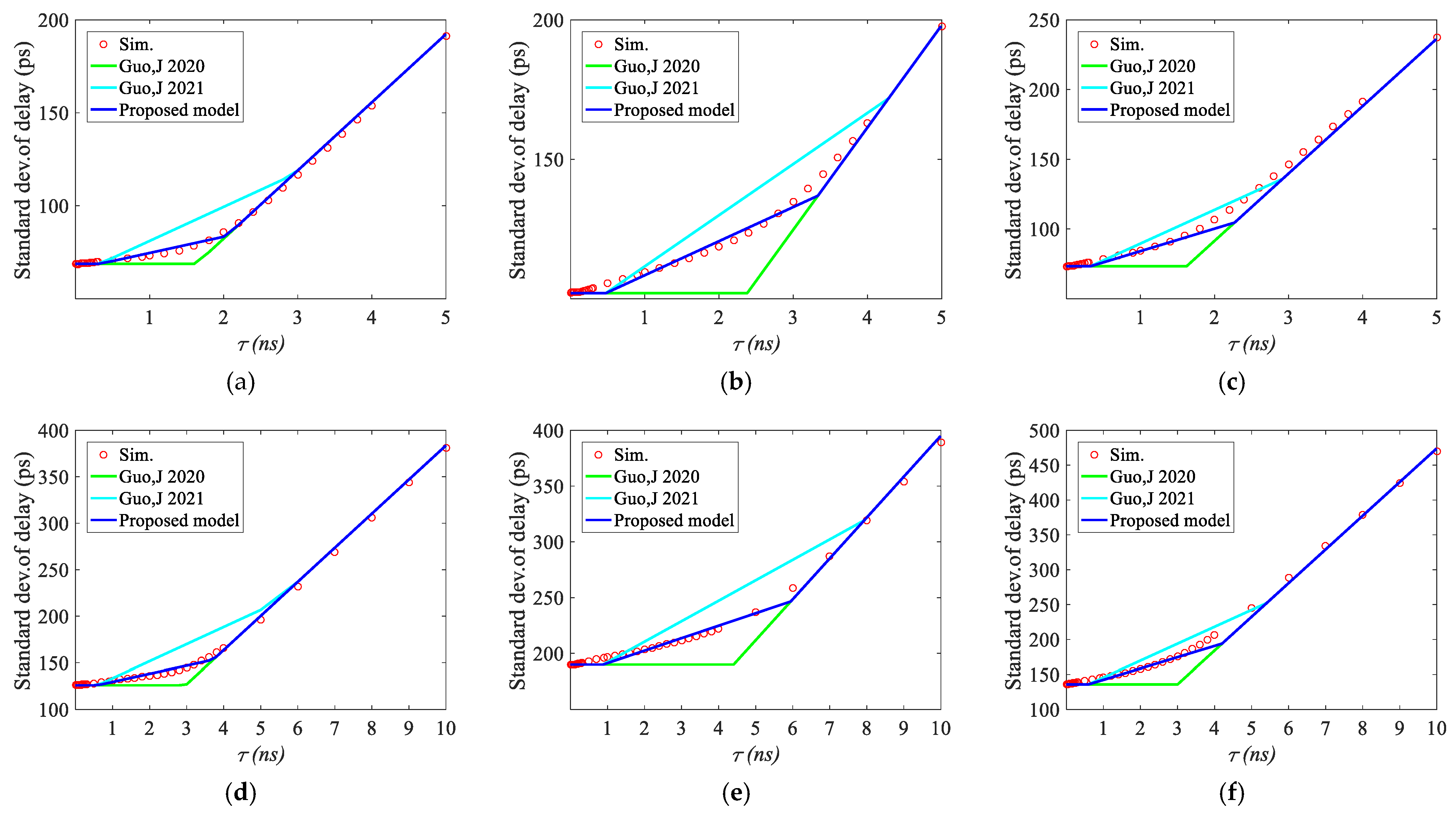

4. Experimental Results and Discussions

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Appendix A

- (1)

- 0 < t ≤ τ

- (2)

- t > τ

References

- Pinckney, N.; Blaauw, D.; Sylvester, D. Low-power near-threshold design: Techniques to improve energy efficiency energy-efficient near-threshold design has been proposed to increase energy efficiency across a wid. IEEE Solid State Circuits Mag. 2015, 7, 49–57. [Google Scholar] [CrossRef]

- Alioto, M. Ultra-Low Power VLSI Circuit Design Demystified and Explained: A Tutorial. IEEE Trans. Circuits Syst. I Regul. Pap. 2012, 59, 3–29. [Google Scholar] [CrossRef]

- Dreslinski, R.G.; Wieckowski, M.; Blaauw, D.; Sylvester, D.; Mudge, T.N. Near-Threshold Computing: Reclaiming Moore’s Law Through Energy Efficient Integrated Circuits. Proc. IEEE 2010, 98, 253–266. [Google Scholar] [CrossRef]

- Alioto, M.; Scotti, G.; Trifiletti, A. A novel framework to estimate the path delay variability on the back of an envelope via the fan-out-of-4 metric. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 64, 2073–2085. [Google Scholar] [CrossRef]

- Corsonello, P.; Frustaci, F.; Lanuzza, M.; Perri, S. Over/undershooting effects in accurate buffer delay model for sub-threshold domain. IEEE Trans. Circuits Syst. I Regul. Pap. 2014, 61, 1456–1464. [Google Scholar] [CrossRef]

- Cao, P.; Liu, Z.; Guo, J.; Wu, J. An Analytical Gate Delay Model in Near/Subthreshold Domain Considering Process Variation. IEEE Access 2019, 7, 171515–171524. [Google Scholar] [CrossRef]

- Guo, J.; Cao, P.; Li, M.; Liu, Z.; Yang, J. Statistical Timing Model for Subthreshold Circuit with Correlated Variation Consideration. In Proceedings of the 2020 IEEE International Symposium on Circuits and Systems (ISCAS), Seville, Spain, 12–14 October 2020; pp. 1–5. [Google Scholar]

- Guo, J.; Cao, P.; Li, M.; Gong, Y.; Liu, Z.; Bai, G.; Yang, J. Semi-Analytical Path Delay Variation Model With Adjacent Gates Decorrelation for Subthreshold Circuits. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2021, 40, 931–944. [Google Scholar] [CrossRef]

- Frustaci, F.; Corsonello, P.; Perri, S. Analytical delay model considering variability effects in subthreshold domain. IEEE Trans. Circuits Syst. II Express Briefs 2012, 59, 168–172. [Google Scholar] [CrossRef]

- Shiomi, J.; Ishihara, T.; Onodera, H. Microarchitectural-level statistical timing models for near-threshold circuit design. In Proceedings of the 20th Asia and South Pacific Design Automation Conference, Tokyo, Japan, 19–22 January 2015; pp. 87–93. [Google Scholar]

- Sharma, A.; Alam, N.; Bulusu, A. Effective Drive Current for Near-Threshold CMOS Circuits’ Performance Evaluation: Modeling to Circuit Design Techniques. IEEE Trans. Electron Devices 2018, 65, 2413–2421. [Google Scholar] [CrossRef]

- Dani, L.M.; Mishra, N.; Sharma, A.; Bulusu, A. Variation-Aware Prediction of Circuit Performance in Near-Threshold Regime Using Supply-Independent Transition Threshold Points. IEEE Trans. Electron Devices 2019, 66, 5065–5071. [Google Scholar] [CrossRef]

- Pidin, S. Influence of Within-Die Transistor Characteristics Variation on FINFET Circuit Delay. IEEE Trans. Electron Devices 2021, 68, 3276–3282. [Google Scholar] [CrossRef]

- Pelgrom, M.J.M.; Duinmaijer, A.C.J.; Welbers, A.P.G. Matching properties of MOS transistors. IEEE J. Solid-State Circuits 1989, 24, 1433–1439. [Google Scholar] [CrossRef]

| Slew | 100 ps | 500 ps | 1 ns | 2 ns | 3 ns | 5 ns | |

|---|---|---|---|---|---|---|---|

| Load | |||||||

| 1 fF | 1.55 | 4.15 | 1.68 | 0.09 | 0.62 | 3.1 | |

| 3 fF | 0.27 | 0.06 | 3.84 | 3.29 | 1.44 | 0.56 | |

| 5 fF | 0.59 | 0.58 | 2.19 | 2.52 | 2.69 | 1.44 | |

| 10 fF | 0.17 | 1.56 | 1.07 | 1.83 | 1.64 | 2.99 | |

| 20 fF | 0.64 | 0.89 | 1.74 | 3.77 | 0.72 | 3.37 | |

| Slew | 100 ps | 500 ps | 1 ns | 2 ns | 3 ns | 5 ns | |

|---|---|---|---|---|---|---|---|

| Load | |||||||

| 1 fF | 1.02 | 1.92 | 0.26 | 1.45 | 0.17 | 0.33 | |

| 3 fF | 0.28 | 4.36 | 2.94 | 0.32 | 4.63 | 2.78 | |

| 5 fF | 0.06 | 2.93 | 4.67 | 1.78 | 0.16 | 5.21 | |

| 10 fF | 0.15 | 1.75 | 3.43 | 4.12 | 2.12 | 2.20 | |

| 20 fF | 0.28 | 1.15 | 1.96 | 3.39 | 4.94 | 2.46 | |

| Slew | 100 ps | 500 ps | 1 ns | 2 ns | 3 ns | 5 ns | |

|---|---|---|---|---|---|---|---|

| Load | |||||||

| 1 fF | 0.35 | 6.49 | 1.00 | 0.65 | 1.29 | 3.26 | |

| 3 fF | 0.29 | 6.26 | 5.55 | 0.71 | 2.25 | 3.12 | |

| 5 fF | 0.36 | 6.30 | 5.02 | 6.01 | 1.35 | 3.19 | |

| 10 fF | 0.44 | 3.43 | 6.41 | 4.15 | 4.90 | 1.08 | |

| 20 fF | 0.53 | 2.01 | 3.39 | 6.40 | 4.72 | 3.47 | |

| Load | Fast Input | Transition Area | Slow Input | |||

|---|---|---|---|---|---|---|

| Max | Ave | Max | Ave | Max | Ave | |

| 5 fF | 4.46 | 3.96 | 4.53 | 3.03 | 2.97 | 2.95 |

| 10 fF | 4.50 | 4.07 | 4.57 | 3.73 | 2.67 | 2.24 |

| 20 fF | 4.15 | 3.55 | 4.63 | 4.28 | 2.86 | 2.08 |

| Load | Fast Input | Transition Area | Slow Input | |||

|---|---|---|---|---|---|---|

| Max | Ave | Max | Ave | Max | Ave | |

| 5 fF | 4.28 | 3.82 | 4.22 | 2.75 | 6.40 | 4.73 |

| 10 fF | 5.78 | 4.59 | 4.40 | 3.27 | 5.76 | 4.86 |

| 20 fF | 4.57 | 3.90 | 4.89 | 4.25 | 3.56 | 2.94 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cao, P.; Xu, W.; Wu, Y.; Liu, W.; Wang, Y. Subthreshold Delay Variation Model Considering Transitional Region for Input Slew. Electronics 2023, 12, 615. https://doi.org/10.3390/electronics12030615

Cao P, Xu W, Wu Y, Liu W, Wang Y. Subthreshold Delay Variation Model Considering Transitional Region for Input Slew. Electronics. 2023; 12(3):615. https://doi.org/10.3390/electronics12030615

Chicago/Turabian StyleCao, Peng, Weixing Xu, Yuanjie Wu, Wanyu Liu, and Yu Wang. 2023. "Subthreshold Delay Variation Model Considering Transitional Region for Input Slew" Electronics 12, no. 3: 615. https://doi.org/10.3390/electronics12030615

APA StyleCao, P., Xu, W., Wu, Y., Liu, W., & Wang, Y. (2023). Subthreshold Delay Variation Model Considering Transitional Region for Input Slew. Electronics, 12(3), 615. https://doi.org/10.3390/electronics12030615