A True Process-Heterogeneous Stacked Embedded DRAM Structure Based on Wafer-Level Hybrid Bonding

Abstract

:1. Introduction

- Data Movement Energy

- Physical Interface

- Protocol Definition

- Density Extensibility

- Process Compatibility

- Hybrid Bonding Connection Fast Test

- We propose a new DRAM architecture, SeDRAM, which provides extremely high energy efficiency and a simplified local data interface.

- We develop the bandwidth extension method based on the 3DIC process, which guarantees maximum bandwidth reach to TBps pre-chip.

- We put forward the fast test method for hybrid bonding (HB) connections.

2. SeDRAM

2.1. SeDRAM Architecture

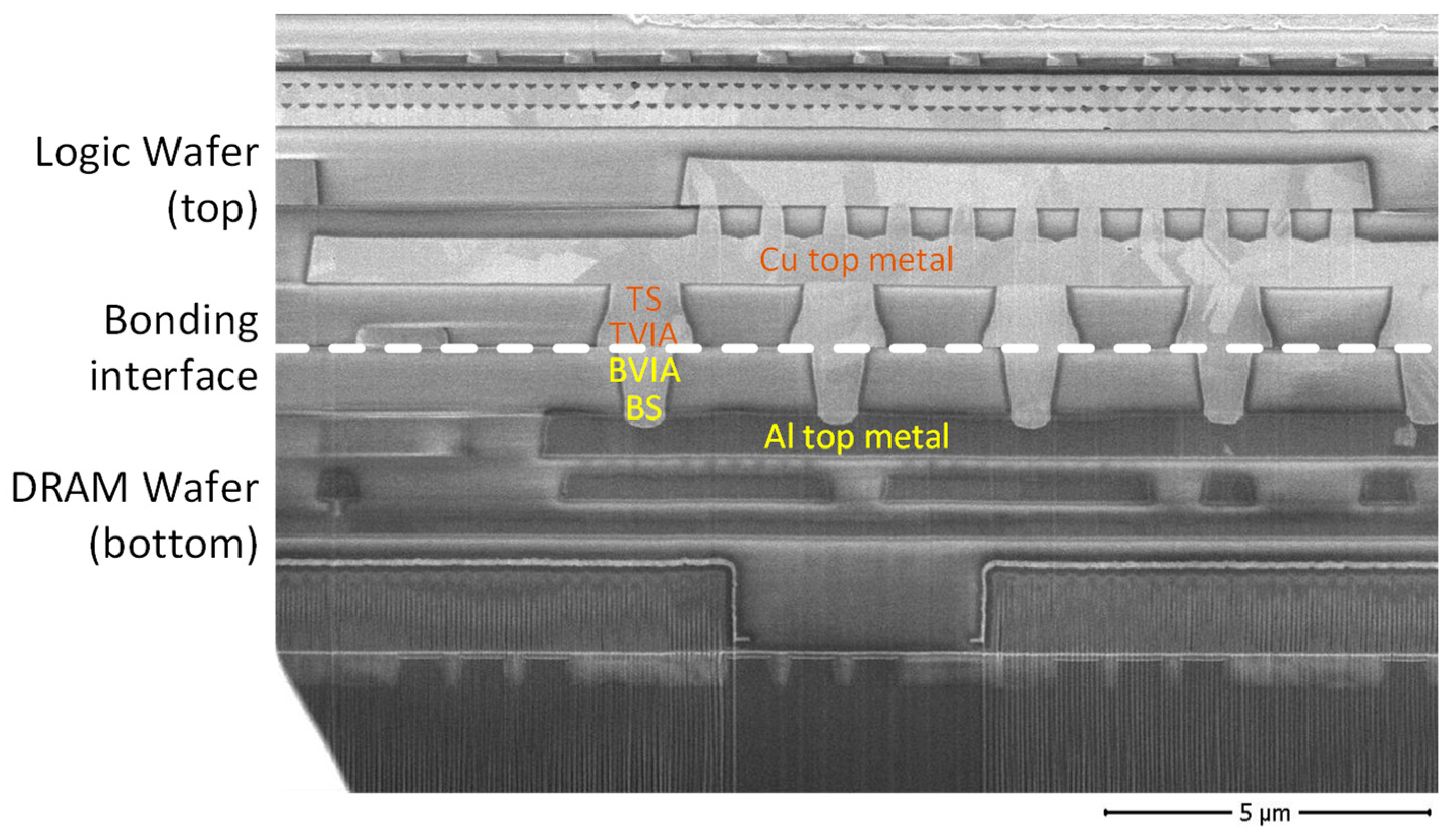

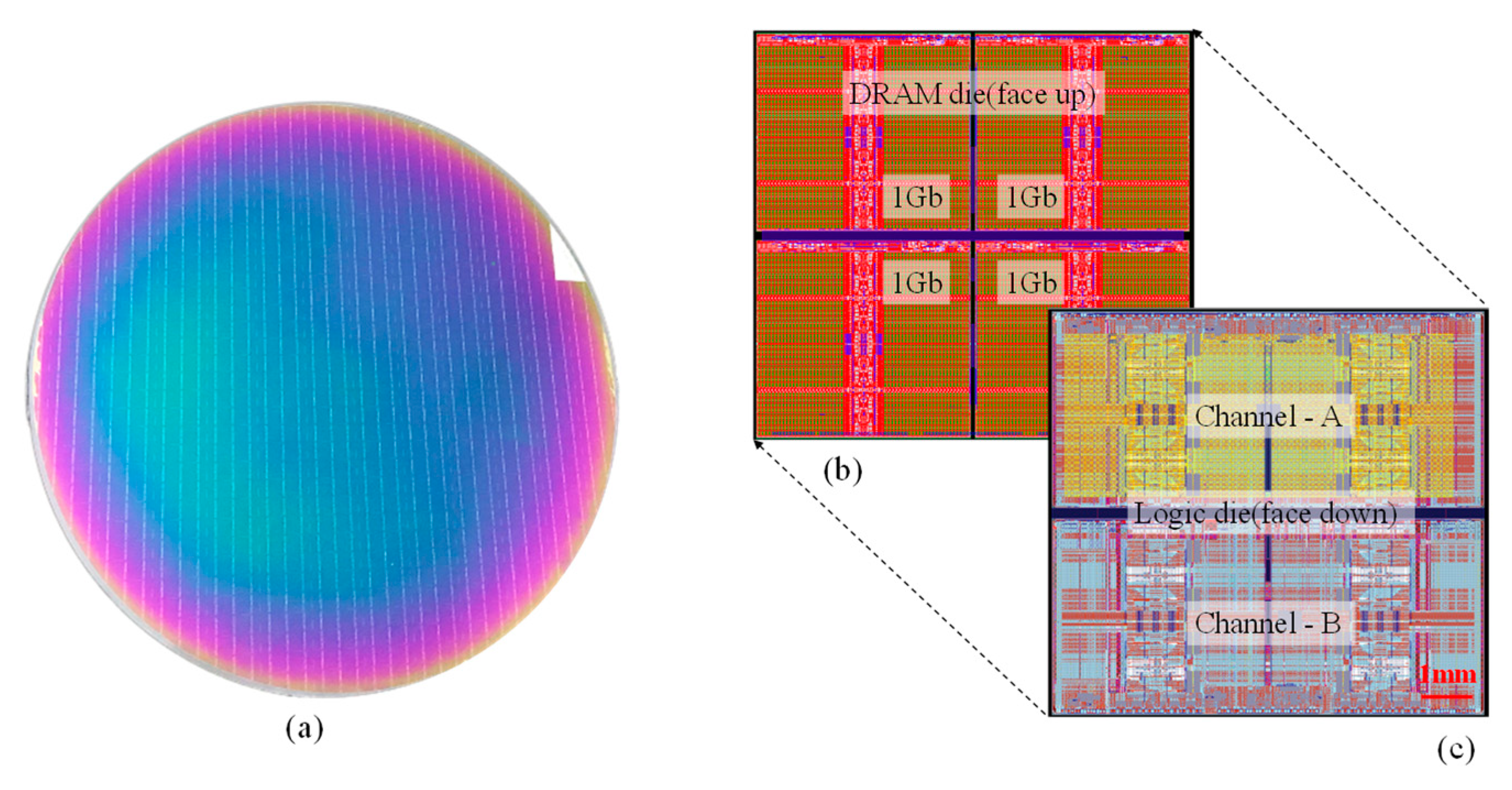

2.2. Hybrid Bonding Technology

2.2.1. Hybrid Bonding Integrity

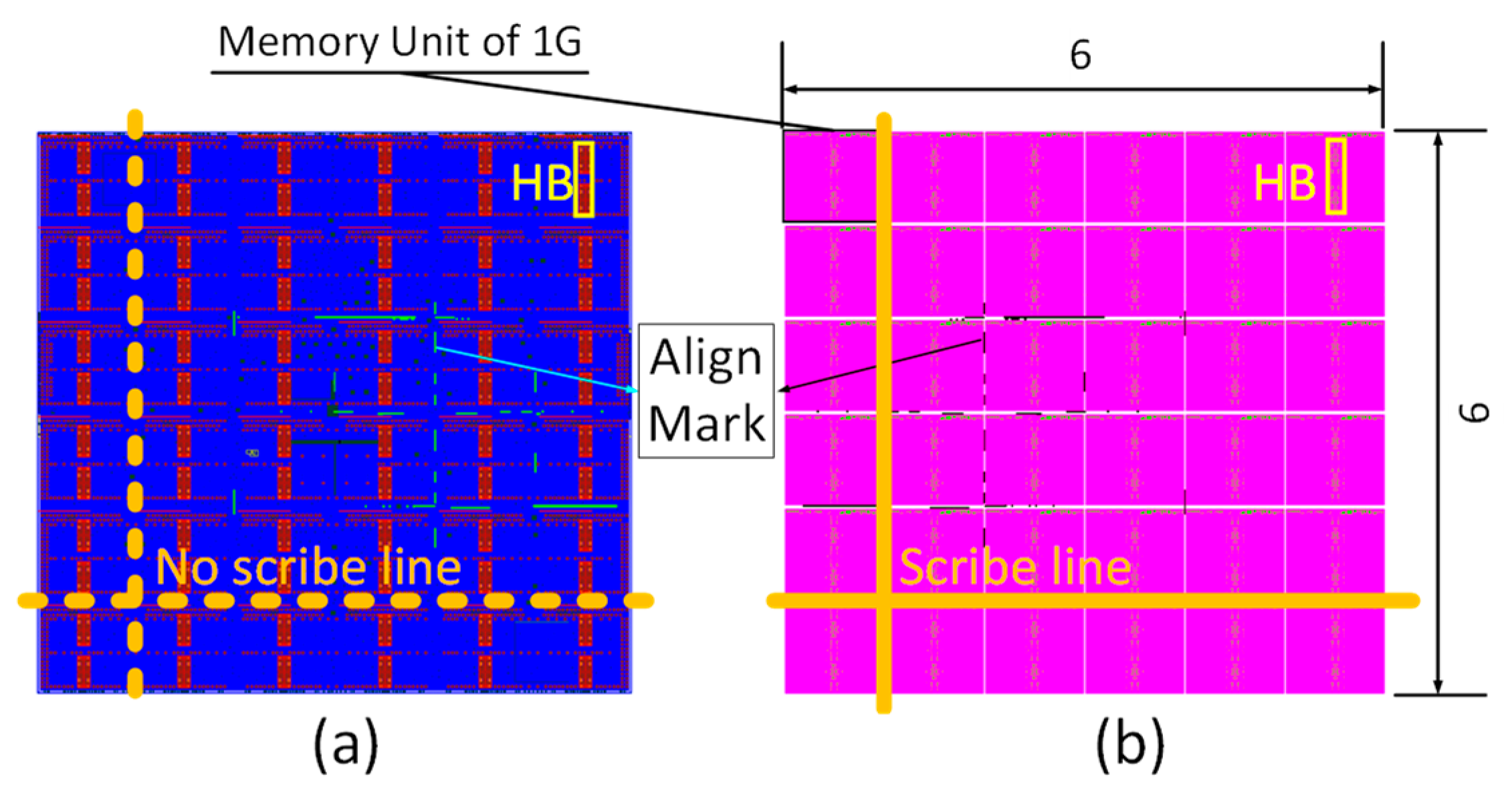

2.2.2. Reticle Design

2.2.3. Logic-to-DRAM Interface

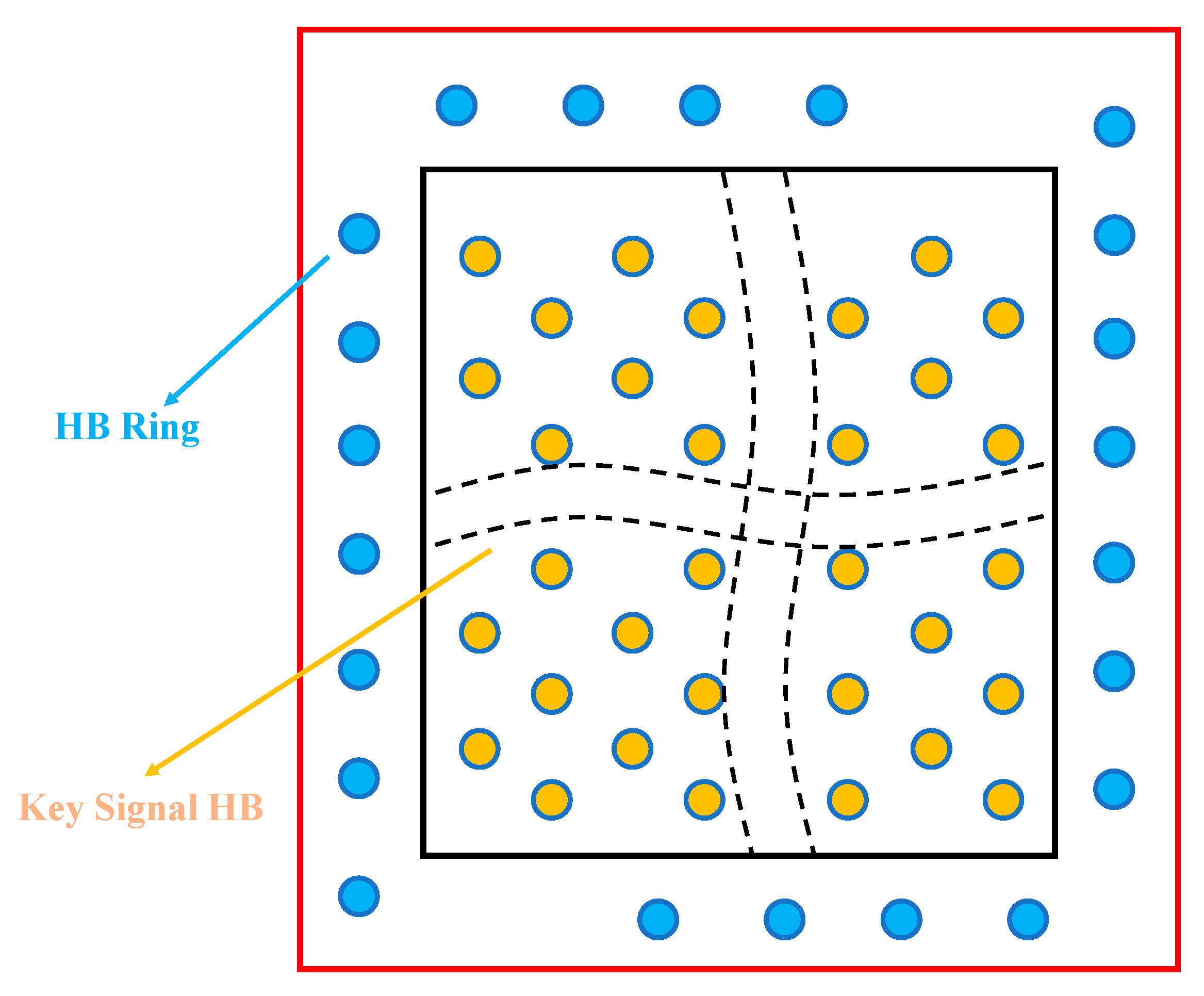

3. Hybrid Bonding Test in SeDRAM

3.1. DFT IP for SeDRAM

3.2. Indirect and Direct Test of Hybrid Bonding

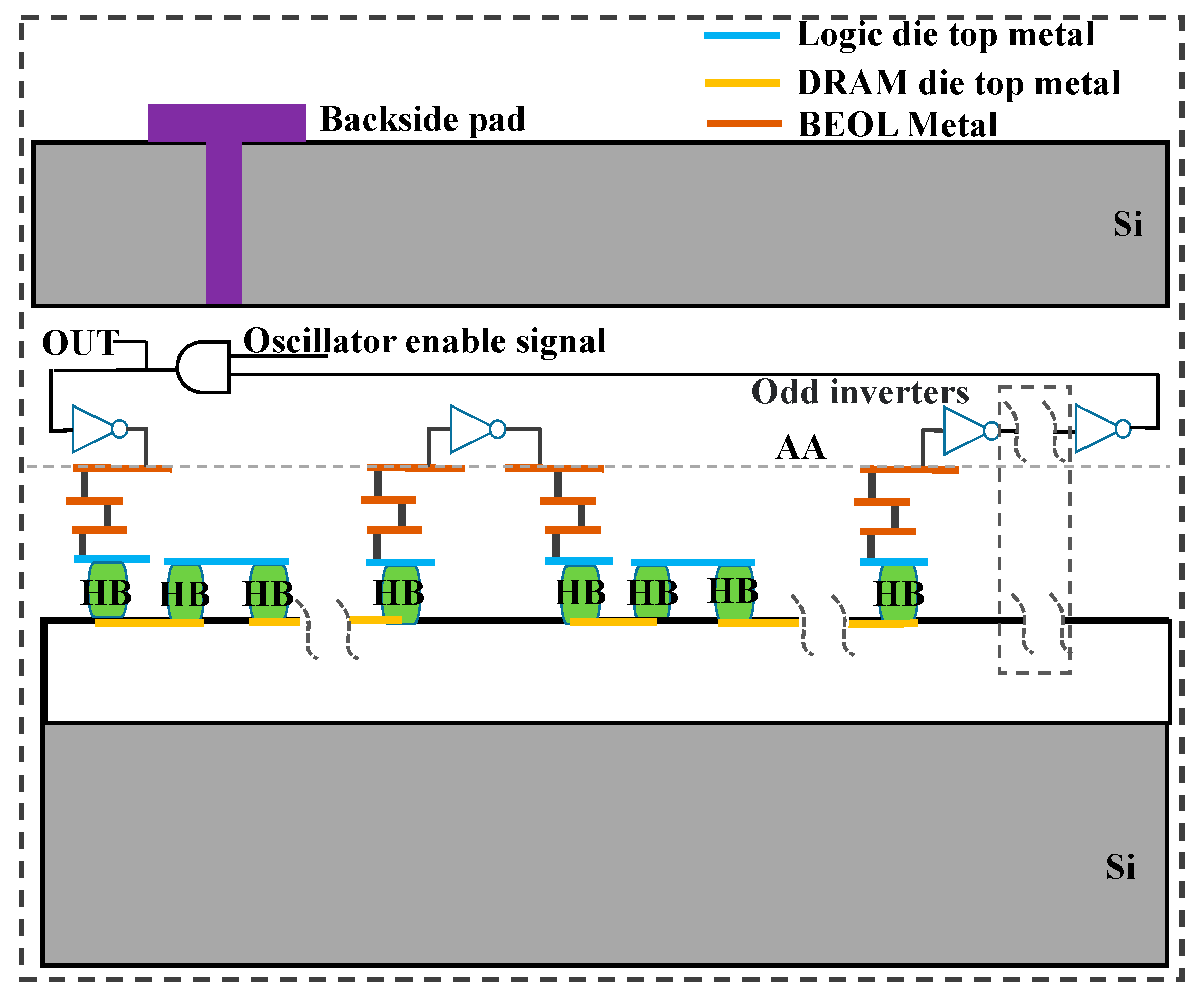

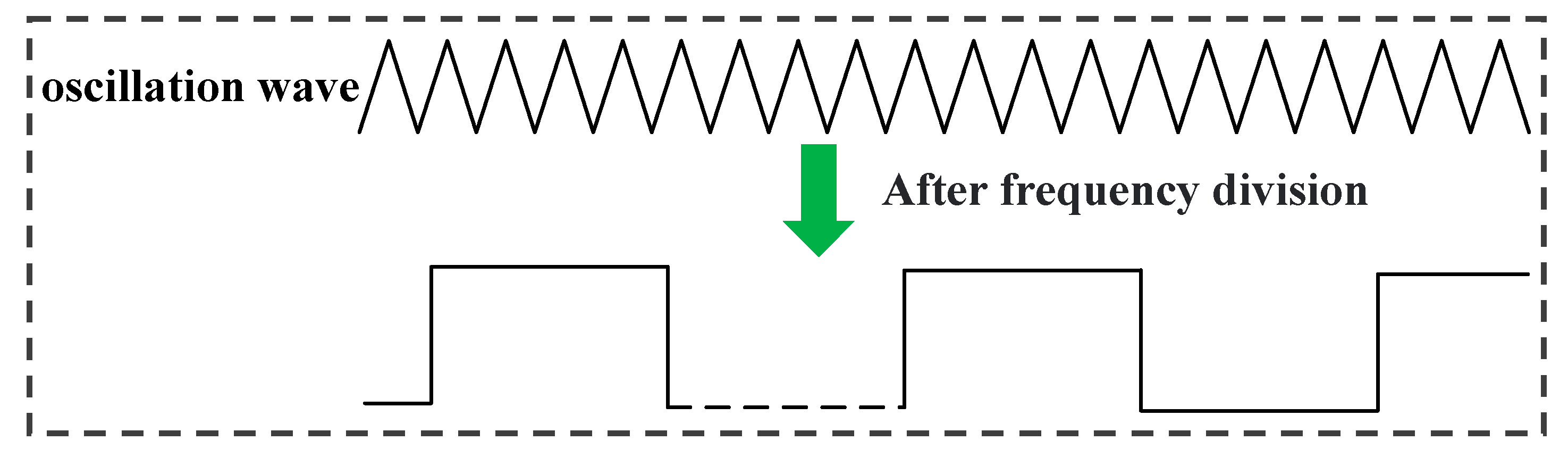

3.3. Fast Test for Hybrid Bonding Connection

4. Results and Discussion

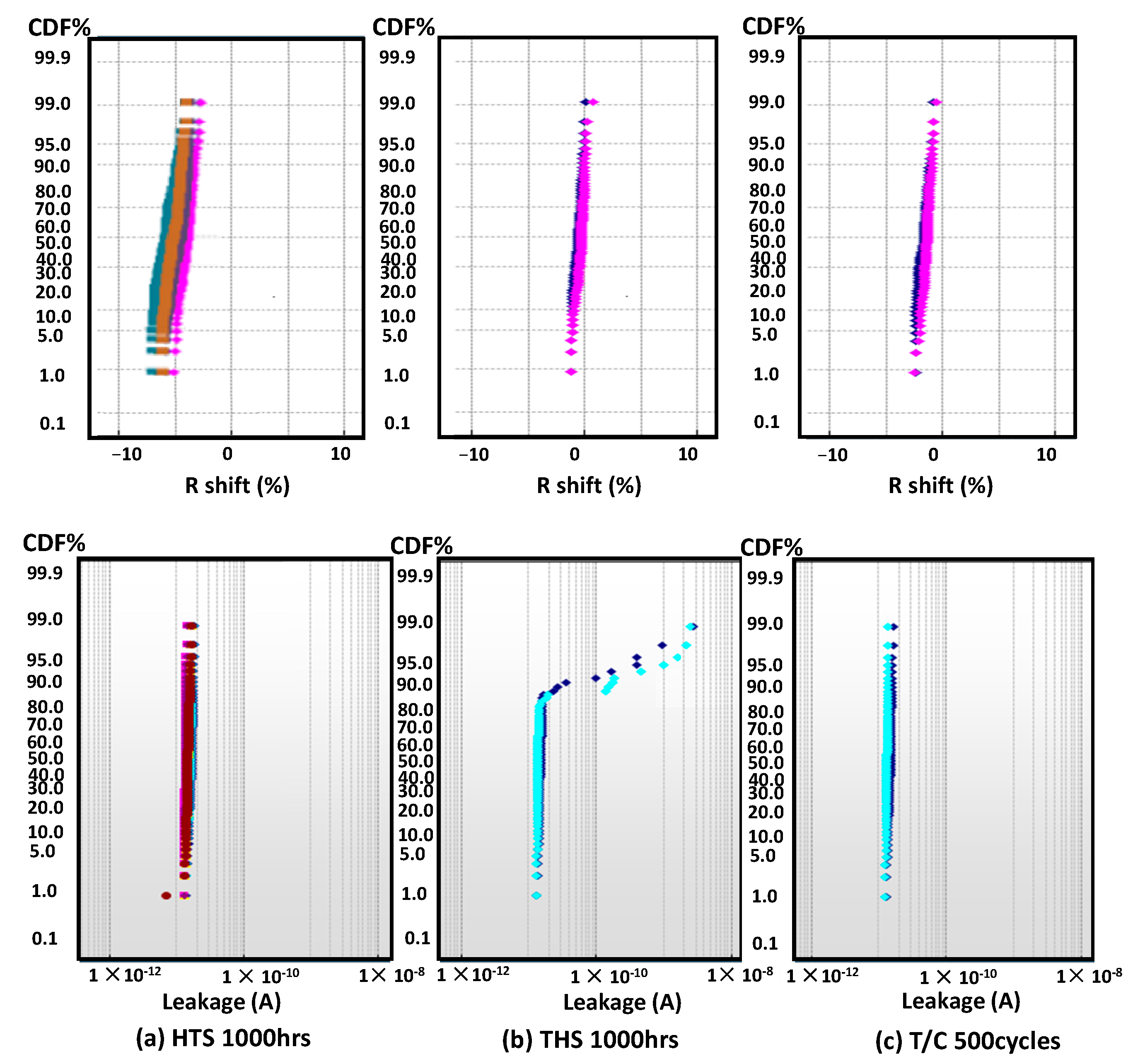

4.1. Hybrid Bonding Test-Key Results

4.2. A 4 Gb LPDDR4/4X by SeDRAM Test Results

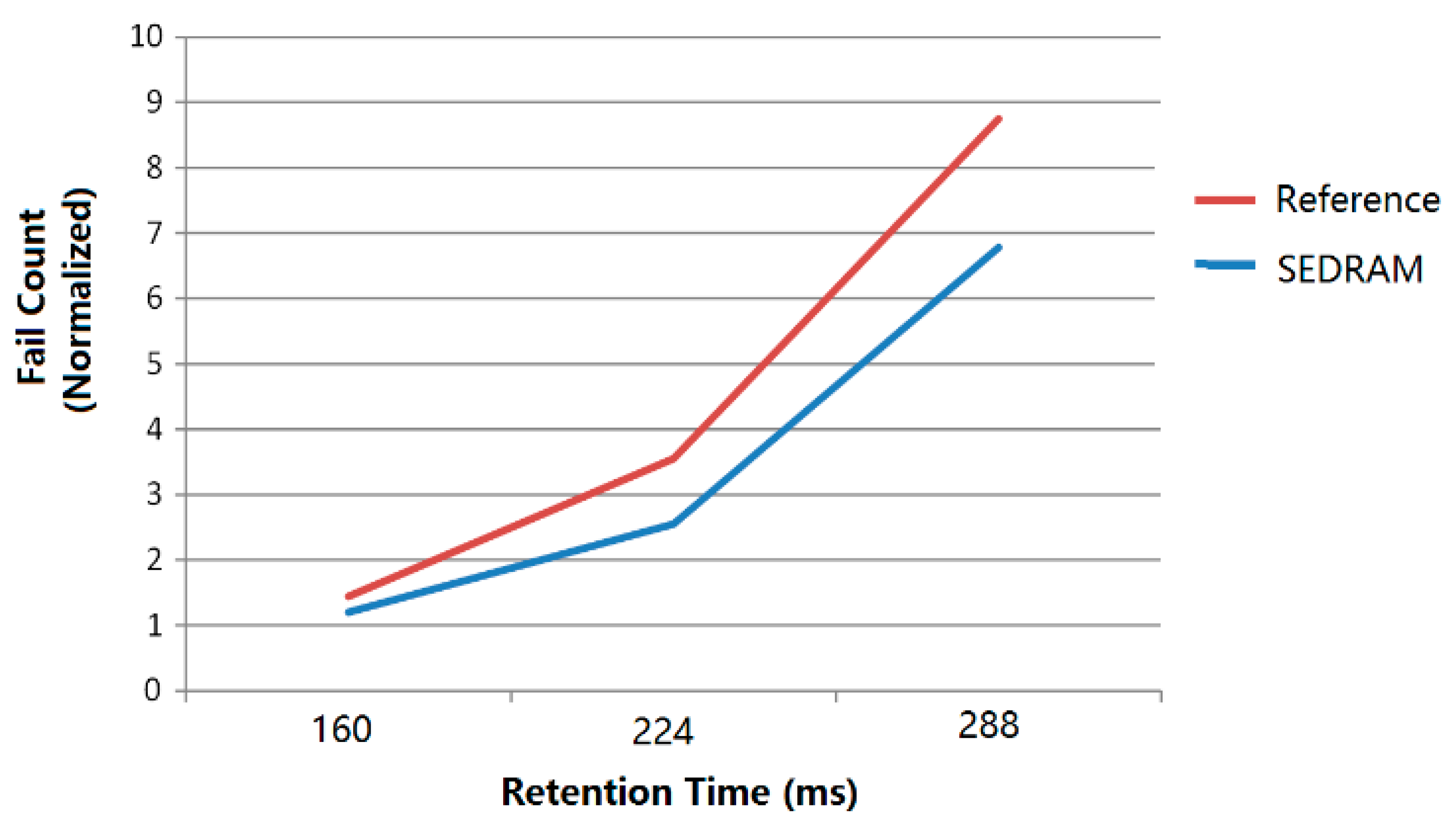

4.3. Hybrid Bonding Connection Test Results

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Bai, F.J.; Jiang, X.P.; Wang, S.; Yu, B.; Tan, J.; Zuo, F.G.; Wang, C.J.; Wang, F.; Long, X.D.; Yu, G.Q.; et al. A stacked embedded DRAM array for LPDDR4/4X using hybrid bonding 3D integration with 34GB/s/1Gb 0.88 pJ/b logic-to-memory interface. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12–18 December 2020; pp. 6.6.1–6.6.4. [Google Scholar]

- Park, S.K. Technology scaling challenge and future prospects of DRAM and NAND flash memory. In Proceedings of the 2015 IEEE International Memory Workshop (IMW), Monterey, CA, USA, 17–20 May 2015; pp. 1–4. [Google Scholar]

- Kwon, Y.C.; Lee, S.H.; Lee, J.; Kwon, S.H.; Ryu, J.M.; Son, J.P.; Seongil, O.; Yu, H.-S.; Lee, H.; Kim, S.Y.; et al. A 20nm 6GB function-in-memory DRAM, based on HBM2 with a 1.2 TFLOPS programmable computing unit using bank-level parallelism, for machine learning applications. In Proceedings of the 2021 IEEE International Solid- State Circuits Conference (ISSCC), San Francisco, CA, USA, 13–22 February 2021; pp. 350–352. [Google Scholar]

- Niu, D.M.; Li, S.C.; Wang, Y.H.; Han, W.; Zhang, Z.; Guan, Y.J.; Guan, T.C.; Sun, F.; Xue, F.; Duan, L.D.; et al. 184QPS/W 64Mb/mm23D logic-to-DRAM hybrid bonding with process-near-memory engine for recommendation system. In Proceedings of the 2022 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 20–26 February 2022; pp. 1–3. [Google Scholar]

- Hwang, K.-D.; Kim, B.; Byeon, S.-Y.; Kim, K.-Y.; Kwon, D.-H.; Lee, H.-B.; Lee, G.-I.; Yoon, S.-S.; Cha, J.-Y.; Jang, S.-Y.; et al. A 16Gb/s/pin 8Gb GDDR6 DRAM with bandwidth extension techniques for high-speed applications. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 210–212. [Google Scholar]

- Hollis, T.M.; Schneider, R.; Brox, M.; Hein, T.; Spirkl, W.; Bach, M.; Balakrishnan, M.; Funfrock, F.; Ivanov, M.; Jovanovic, N.; et al. An 8-Gb GDDR6X DRAM achieving 22 Gb/s/pin With Single-Ended PAM-4 Signaling. IEEE J. Solid-State Circuits 2021, 57, 224–235. [Google Scholar] [CrossRef]

- O’Connor, M.; Chatterjee, N.; Lee, D.; Wilson, J.; Agrawal, A.; Keckler, S.W.; Dally, W.J. Fine-grained DRAM: Energy-efficient DRAM for extreme bandwidth systems. In Proceedings of the 50th Annual IEEE/ACM International Symposium on Microarchitecture, Boston, MA, USA, 14–17 October 2017; pp. 41–54. [Google Scholar]

- Jun, H.; Cho, J.; Lee, K.; Son, H.Y.; Kim, K.; Jin, H.; Kim, K. HBM (high bandwidth memory) DRAM technology and architecture. In Proceedings of the 2017 IEEE International Memory Workshop (IMW), Monterey, CA, USA, 14–17 May 2017; pp. 1–4. [Google Scholar]

- Park, M.-J.; Cho, H.S.; Yun, T.-S.; Byeon, S.; Koo, Y.J.; Yoon, S.; Lee, D.U.; Choi, S.; Park, J.; Lee, J.; et al. A 192-Gb 12-high 896-Gb/s HBM3 DRAM with a TSV auto-calibration scheme and machine-learning-based layout optimization. In Proceedings of the 2022 IEEE International Solid- State Circuits Conference (ISSCC), San Francisco, CA, USA, 20–26 February 2022; pp. 444–446. [Google Scholar]

- Chujo, N.; Sakui, K.; Ryoson, H.; Sugatani, S.; Nakamura, T.; Ohba, T. Bumpless build cube (BBCube): High-parallelism, high-heat-dissipation and low-power stacked memory using wafer-level 3D integration Process. In Proceedings of the 2020 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 16–19 June 2020; pp. 1–2. [Google Scholar]

- Michailos, J.; Coudrain, P.; Farcy, A.; Hotellier, N.; Cheramy, S.; Lhostis, S.; Deloffre, E.; Sanchez, Y.; Jouve, A.; Guyader, F.; et al. New challenges and opportunities for 3D integrations. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 8.5.1–8.5.4. [Google Scholar]

- Tsai, Y.C.; Lee, C.H.; Chang, H.C.; Liu, J.H.; Hu, H.W.; Ito, H.; Kim, Y.S.; Ohba, T.; Chen, K.-N. Electrical characteristics and reliability of wafer-on-wafer (WOW) bumpless through-silicon via. IEEE Trans. Electron Devices 2021, 68, 3520–3525. [Google Scholar] [CrossRef]

- Sakui, K.; Ohba, T. High bandwidth memory (HBM) and high bandwidth NAND (HBN) with the bumpless TSV technology. In Proceedings of the International 3D Systems Integration Conference (3DIC), Sendai, Japan, 8–10 October 2019; pp. 1–4. [Google Scholar]

- Kim, Y.S.; Kodama, S.; Maeda, N.; Fujimoto, K.; Mizushima, Y.; Kawai, A.; Hsu, T.C.; Tzeng, P.; Ku, T.K.; Ohba, T. Electrical characteristics of bumpless interconnects for through silicon via (TSV) and wafer-on-wafer (WOW) integration. In Proceedings of the International Conference on Electronics Packaging (ICEP), Hokkaido, Japan, 20–22 April 2016; pp. 74–78. [Google Scholar]

- Kim, S.H.; Kang, P.; Kim, T.; Lee, K.; Jang, J.; Moon, K.; Na, H.; Hyun, S.; Hwang, K. Cu microstructure of high density Cu hybrid bonding interconnection. In Proceedings of the IEEE 69th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 28–31 May 2019; pp. 636–641. [Google Scholar]

- Lee, D.U.; Kim, K.W.; Kim, K.W.; Kim, H.; Kim, J.Y.; Park, Y.J.; Kim, J.H.; Kim, D.S.; Park, H.B.; Shin, J.W.; et al. A 1.2V 8Gb 8-channel 128GB/s high-bandwidth memory (HBM) stacked DRAM with effective microbump I/O test methods using 29nm process and TSV. In Proceedings of the 2014 IEEE International Solid- State Circuits Conference (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 432–433. [Google Scholar]

- Jiang, X.P.; Zuo, F.G.; Wang, S.; Zhou, X.F.; Wang, Y.B.; Liu, Q.; Ren, Q.W.; Liu, M. A 1596-GB/s 48-Gb stacked embedded DRAM 384-Core SoC with hybrid bonding integration. IEEE Solid-State Circuits Lett. 2022, 5, 110–113. [Google Scholar] [CrossRef]

- Jiang, X.P.; Zuo, F.G.; Wang, S.; Zhou, X.F.; Yu, B.; Wang, Y.B.; Liu, Q.; Liu, M.; Kang, Y.; Ren, Q.W. A 1596GB/s 48Gb embedded DRAM 384-Core SoC with hybrid bonding integration. In Proceedings of the 2021 IEEE Asian Solid-State Circuits Conference (A-SSCC), Busan, Republic of Korea, 7–10 November 2021; pp. 1–3. [Google Scholar]

- Li, Y.; Schneider, H.; Schnabel, F.; Thewes, R.; Schmitt-Landsiedel, D. DRAM yield analysis and optimization by a statistical design approach. IEEE Trans. Circuits Syst. I Regul. Pap. 2011, 58, 2906–2918. [Google Scholar] [CrossRef]

- Van De Goor, A.J.; Schanstra, I. Address and data scrambling: Causes and impact on memory tests. In Proceedings of the First IEEE International Workshop on Electronic Design, Test and Applications, Christchurch, New Zealand, 29–31 January 2002; pp. 1–9. [Google Scholar]

- Park, J.; Lee, B.; Lee, H.; Lim, D.; Kang, J.; Cho, C.; Na, M.; Jin, I. Wafer to wafer hybrid bonding for DRAM applications. In Proceedings of the 2022 IEEE 72nd Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 31 May 2022–3 June 2022; pp. 126–129. [Google Scholar]

- Lee, D.U.; Cho, H.S.; Kim, J.; Ku, Y.J.; Oh, S.; Kim, C.D.; Kim, H.W.; Lee, W.Y.; Kim, T.K.; Yun, T.S.; et al. A 128Gb 8-High 512GB/s HBM2E DRAM with a Pseudo Quarter Bank Structure, Power Dispersion and an Instruction-Based At-Speed PMBIST. In Proceedings of the 2020 IEEE International Solid- State Circuits Conference (ISSCC), San Francisco, CA, USA, 16–20 February 2020; pp. 334–336. [Google Scholar]

| GDDR6 ISSCC2018 [5] | HBM2E ISSCC2020 [22] | HBM3 ISSCC2022 [9] | This Work | |

|---|---|---|---|---|

| Connection | - | ubump | ubump | Hybrid bonding |

| PHY | - | Yes | Yes | No |

| IO | 32 | 1024 | 1024 | 4096 |

| Speed (Mbps) | 16,384 | 4096 | 7168 | 266 |

| Total Bandwidth (GBps) | 64 | 512 | 896 | 136 |

| Density (Gbit) | 8 | 128 | 192 | 4 |

| Energy Efficiency (a. u) | 100% | 80% | 53% | 12% |

| Bandwidth per Gbit (GBps/Gbit) | 8 | 4 | 4.7 | 34 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, S.; Jiang, X.; Bai, F.; Xiao, W.; Long, X.; Ren, Q.; Kang, Y. A True Process-Heterogeneous Stacked Embedded DRAM Structure Based on Wafer-Level Hybrid Bonding. Electronics 2023, 12, 1077. https://doi.org/10.3390/electronics12051077

Wang S, Jiang X, Bai F, Xiao W, Long X, Ren Q, Kang Y. A True Process-Heterogeneous Stacked Embedded DRAM Structure Based on Wafer-Level Hybrid Bonding. Electronics. 2023; 12(5):1077. https://doi.org/10.3390/electronics12051077

Chicago/Turabian StyleWang, Song, Xiping Jiang, Fujun Bai, Wenwu Xiao, Xiaodong Long, Qiwei Ren, and Yi Kang. 2023. "A True Process-Heterogeneous Stacked Embedded DRAM Structure Based on Wafer-Level Hybrid Bonding" Electronics 12, no. 5: 1077. https://doi.org/10.3390/electronics12051077

APA StyleWang, S., Jiang, X., Bai, F., Xiao, W., Long, X., Ren, Q., & Kang, Y. (2023). A True Process-Heterogeneous Stacked Embedded DRAM Structure Based on Wafer-Level Hybrid Bonding. Electronics, 12(5), 1077. https://doi.org/10.3390/electronics12051077