Low-Power Current Integrating Flat-Passband Infinite Impulse Response Filter for Sensor Read-Out Integrated Circuit in 65-nm CMOS Technology

Abstract

:1. Introduction

2. Current Integrating Analog IIR Filter Topology

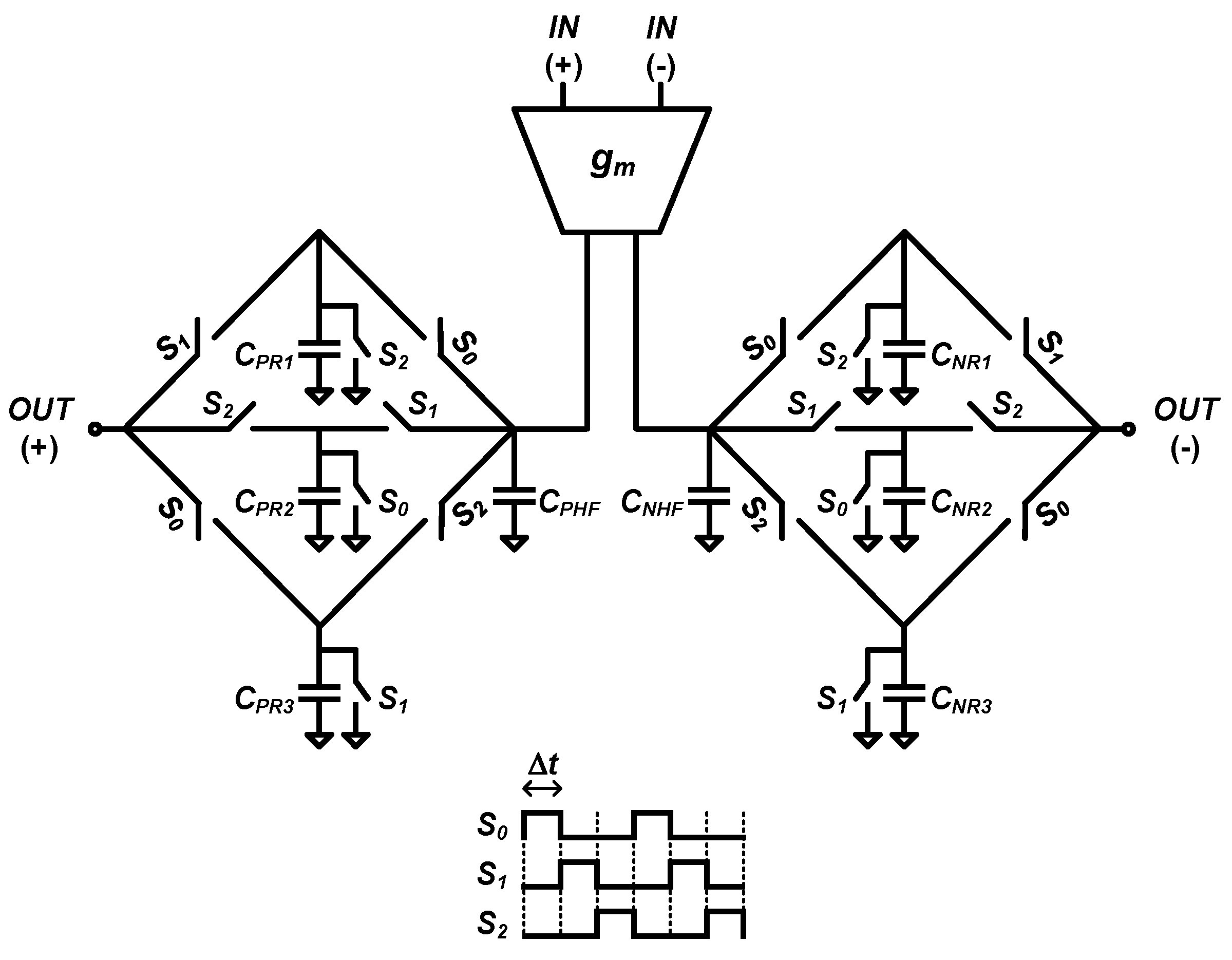

2.1. Conventional Architecture

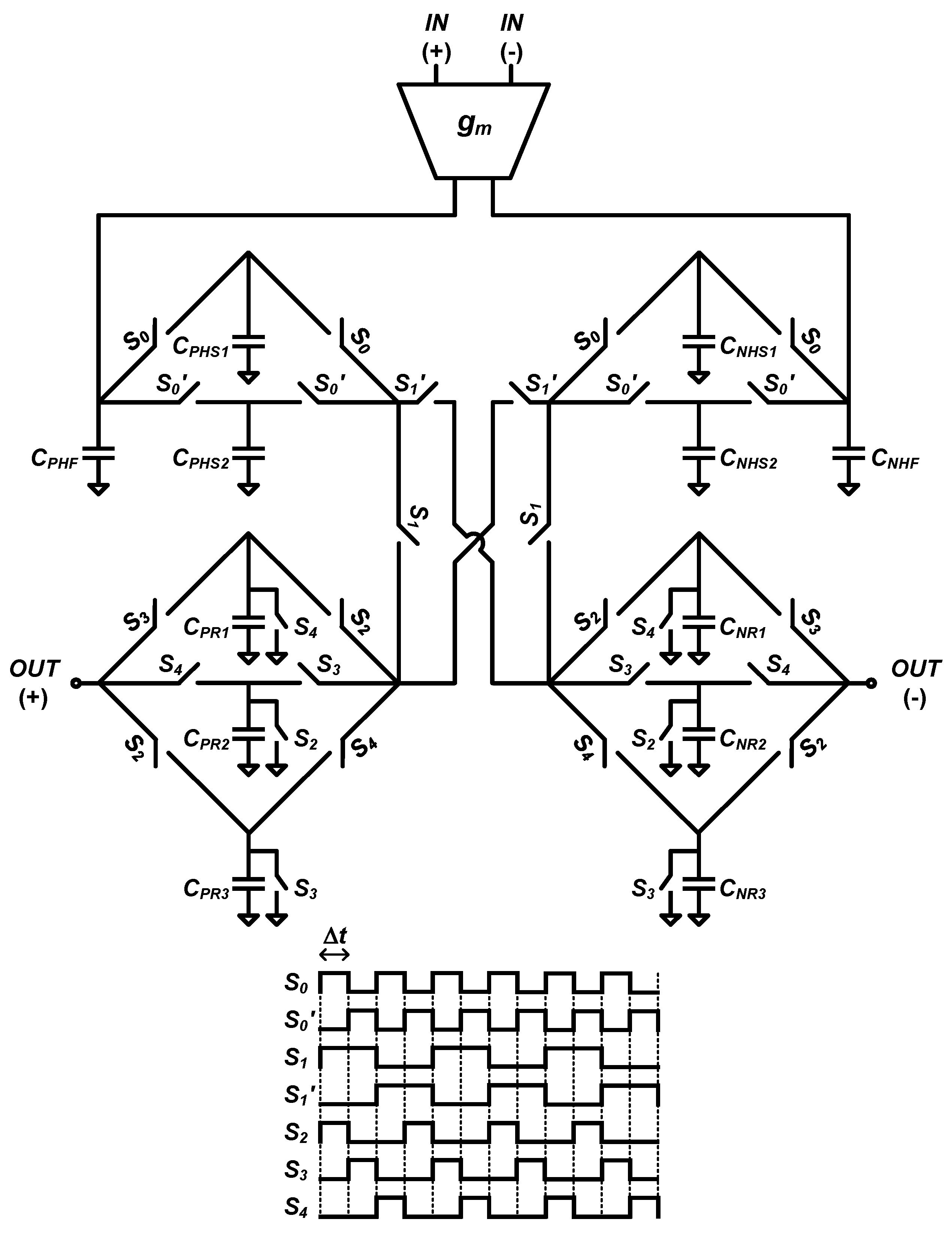

2.2. Proposed Architecture

2.3. Transconductance Amplifier

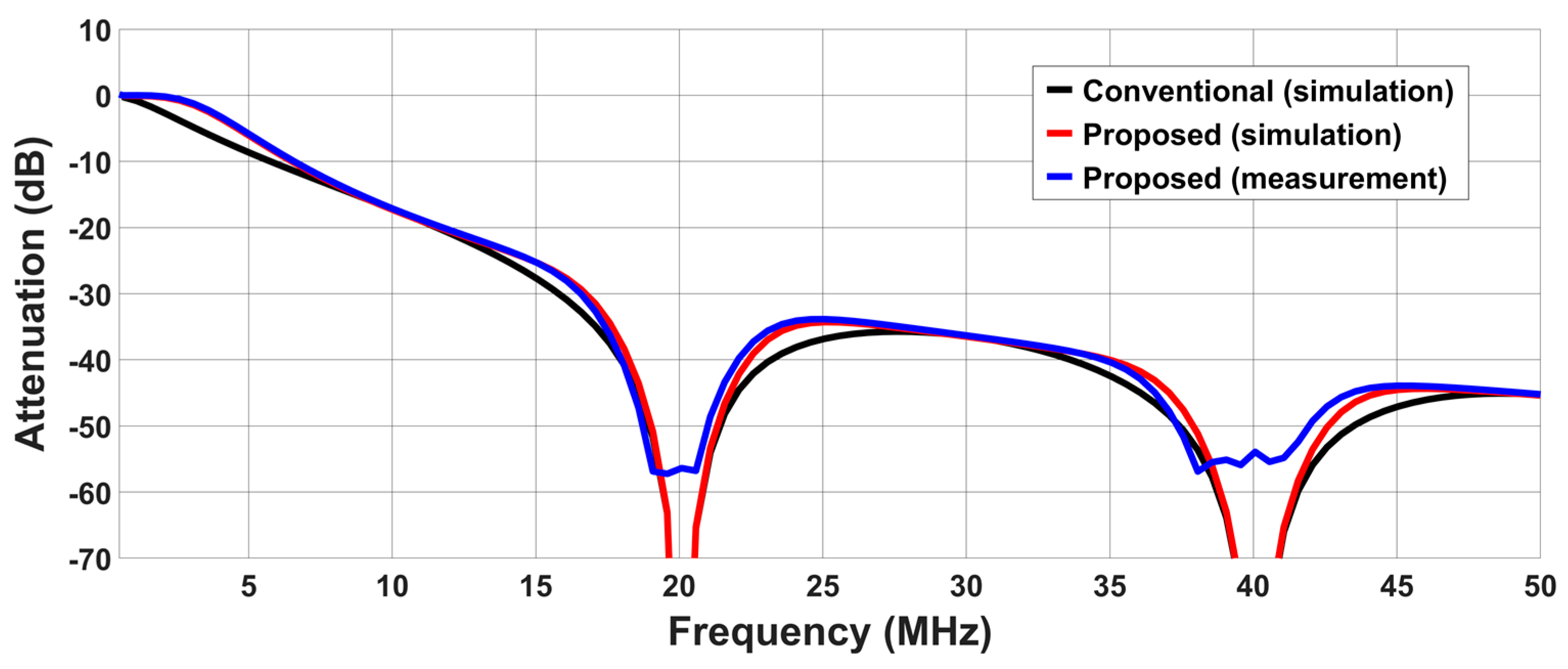

3. Measurement Results

4. Discussion

4.1. Performance Comparison

4.2. Related Application

5. Conclusions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Wang, X.; Boon, C.C.; Yang, K.; Kong, L. A 20–80 MHz Continuously Tunable Gm-C Low-Pass Filter for Ultra-Low Power WBAN Receiver Front-End. IEEE Access 2021, 9, 154136–154142. [Google Scholar] [CrossRef]

- Wang, Y.; Wu, B.; Huang, H. A 3rd/5th Order Active RC Chebyshev Analog Baseband Low-Pass Filter with Reconfigurable Bandwidth and Gain. IEEE Access 2021, 9, 129319–129328. [Google Scholar] [CrossRef]

- Lavalle-Aviles, F.; Sanchez-Sinencio, E. A 0.6-V Power-Efficient Active-RC Analog Low-Pass Filter with Cutoff Frequency Selection. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2020, 28, 1757–1769. [Google Scholar] [CrossRef]

- Zheng, J.; Ki, W.-H.; Tsui, C.-Y. A Fully Integrated Analog Front End for Biopotential Signal Sensing. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 3800–3809. [Google Scholar] [CrossRef]

- Jiang, W.; Zhu, Y.; Chan, C.-H.; Murmann, B.; Martins, R.P. A 7-Bit 2 GS/s Time-Interleaved SAR ADC with Timing Skew Calibration Based on Current Integrating Sampler. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 557–568. [Google Scholar] [CrossRef]

- Liu, C.-C.; Huang, M.-C. 28.1 A 0.46mW 5MHz-BW 79.7dB-SNDR Noise-Shaping SAR ADC with Dynamic-Amplifier-Based FIR-IIR Filter. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–9 February 2017. [Google Scholar]

- Zhou, Y.; Filiol, N.M.; Yuan, F. A Quadrature Charge-Domain Sampling Mixer with Embedded FIR, IIR, and N-Path Filters. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 1431–1440. [Google Scholar] [CrossRef]

- Ge, X.; Theuwissen, A.J.P. A 0.5erms−Temporal Noise CMOS Image Sensor with Gm-Cell-Based Pixel and Period-Controlled Variable Conversion Gain. IEEE Trans. Electron Devices 2017, 64, 5019–5026. [Google Scholar] [CrossRef] [Green Version]

- dos Santos, F.V.; Dogaru, E. Flexible Wideband Radio Transceiver Testing Using Non-Uniform Subsampling Demodulation. In Proceedings of the 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018. [Google Scholar]

- Yoshizawa, A.; Iida, S. Parasitic Discrete-Time-Pole Cancelling Techniques for Ultra-Wideband Discrete-Time Charge-Domain Baseband Filters. In Proceedings of the 2010 IEEE Asian Solid-State Circuits Conference, Beijing, China, 8–10 November 2010. [Google Scholar]

- Huang, M.-F.; Kuo, M.-C.; Yang, T.-Y.; Huang, X.-L. A 58.9-DB ACR, 85.5-DB SBA, 5–26-MHz Configurable-Bandwidth, Charge-Domain Filter in 65-nm CMOS. IEEE J. Solid-State Circuits 2013, 48, 2827–2838. [Google Scholar] [CrossRef]

- Tohidian, M.; Madadi, I.; Staszewski, R.B. A 2 mW 800 MS/s 7th-Order Discrete-Time IIR Filter with 400 kHz-to-30 MHz BW and 100 dB Stop-Band Rejection in 65 nm CMOS. In Proceedings of the 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2013. [Google Scholar]

- Bozorg, A.; Staszewski, R.B. A Charge-Sharing IIR Filter with Linear Interpolation and High Stopband Rejection. IEEE J. Solid-State Circuits 2022, 57, 2090–2101. [Google Scholar] [CrossRef]

- Payandehnia, P.; Maghami, H.; Mirzaie, H.; Kareppagoudr, M.; Dey, S.; Tohidian, M.; Temes, G.C. A 0.49–13.3 MHz Tunable Fourth-Order LPF with Complex Poles Achieving 28.7 DBm OIP3. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 2353–2364. [Google Scholar] [CrossRef]

- Chan, W.P.; Narducci, M.; Gao, Y.; Cheng, M.-Y.; Cheong, J.H.; George, A.K.; Cheam, D.D.; Leong, S.C.; Damalerio, M.R.B.; Lim, R.; et al. A Monolithically Integrated Pressure/Oxygen/Temperature Sensing SoC for Multimodality Intracranial Neuromonitoring. IEEE J. Solid-State Circuits 2014, 49, 2449–2461. [Google Scholar] [CrossRef]

- Fick, L.; Fick, D.; Alioto, M.; Blaauw, D.; Sylvester, D. A 346 um 2 VCO-Based, Reference-Free, Self-Timed Sensor Interface for Cubic-Millimeter Sensor Nodes in 28 nm CMOS. IEEE J. Solid-State Circuits 2014, 49, 2462–2473. [Google Scholar] [CrossRef]

- Tang, Z.; Fang, Y.; Yu, X.-P.; Shi, Z.; Tan, N. A CMOS Temperature Sensor with Versatile Readout Scheme and High Accuracy for Multi-Sensor Systems. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 3821–3829. [Google Scholar] [CrossRef]

- Liu, L.; Gao, D.; Tian, Y.; Yu, Y.; Qin, Z. A Low Mismatch and High Input Impedance Multi-Channel Time-Division Multiplexing Analog Front End for Bio-Sensors. IEEE Sens. J. 2022, 22, 6755–6763. [Google Scholar] [CrossRef]

| Operation Diagram | Clock State | |||

|---|---|---|---|---|

| S0 | S1 | S2 | ||

| Sampling capacitor on positive path | CPHF | S | S | S |

| CPR1 | CS | RO | D | |

| CPR2 | D | CS | RO | |

| CPR3 | RO | D | CS | |

| Sampling capacitor on negative path | CNHF | S | S | S |

| CNR1 | CS | RO | D | |

| CNR2 | D | CS | RO | |

| CNR3 | RO | D | CS | |

| Operation Diagram | Clock State | |||||||

|---|---|---|---|---|---|---|---|---|

| S0 | S0′ | S1 | S1′ | S2 | S3 | S4 | ||

| Sampling capacitor on positive path | CPHF | S | S | - | - | - | - | - |

| CPHS1 | S | - | - | - | - | - | - | |

| CPHS2 | - | S | - | - | - | - | - | |

| CPR1 | - | - | - | - | CS | RO | D | |

| CPR2 | - | - | - | - | D | CS | RO | |

| CPR3 | - | - | - | - | RO | D | CS | |

| Sampling capacitor on negative path | CNHF | S | S | - | - | - | - | - |

| CNHS1 | S | - | - | - | - | - | - | |

| CNHS2 | - | S | - | - | - | - | - | |

| CNR1 | - | - | - | - | CS | RO | D | |

| CNR2 | - | - | - | - | D | CS | RO | |

| CNR3 | - | - | - | - | RO | D | CS | |

| Proposed Architecture | [12] | [13] | [14] | |

|---|---|---|---|---|

| Decimation | None | None | None | None |

| 3 dB bandwidth [MHz] | 3.8 | 0.4 to 30 | 1 to 9.9 | 0.49 to 13.3 |

| Sampling frequency [MHz] | 20 | 800 | 333 | 300 |

| BSR | 0.19 | 0.0005 to 0.0375 | 0.003 to 0.033 | 0.0016 to 0.044 |

| Supply voltage [V] | 1.2 | 1.2 | 0.9 | 1.8 |

| Current consumption of gm-cell [mA] | 0.25 | 0.23 | 0.36 | 1.05 |

| Current consumption of clock generator [mA] | 0.04 | 1.4 | 0.66 | 1.33 |

| Power [mW] | 0.35 | 1.96 | 0.92 | 4.3 |

| Technology | 65-nm CMOS | 65-nm CMOS | 28-nm CMOS | 180-nm CMOS |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jo, S.-H. Low-Power Current Integrating Flat-Passband Infinite Impulse Response Filter for Sensor Read-Out Integrated Circuit in 65-nm CMOS Technology. Electronics 2023, 12, 1191. https://doi.org/10.3390/electronics12051191

Jo S-H. Low-Power Current Integrating Flat-Passband Infinite Impulse Response Filter for Sensor Read-Out Integrated Circuit in 65-nm CMOS Technology. Electronics. 2023; 12(5):1191. https://doi.org/10.3390/electronics12051191

Chicago/Turabian StyleJo, Sung-Hun. 2023. "Low-Power Current Integrating Flat-Passband Infinite Impulse Response Filter for Sensor Read-Out Integrated Circuit in 65-nm CMOS Technology" Electronics 12, no. 5: 1191. https://doi.org/10.3390/electronics12051191