Abstract

A CMOS widely tunable second-order -C bandpass filter (BPF), intended to be used in multi-sine bioimpedance applications, is presented. The filter incorporates a tunable transconductor in which the responses of two linearized voltage-to-current converters are subtracted. As a result, the effective transconductance can be continuously adjusted over nearly three decades, which allows a corresponding programmability of the center frequency of the BPF. The circuit was designed and fabricated in 180 nm CMOS technology to operate with a 1.8 V supply, and the experimental characterization was carried out over eight samples of the silicon prototype. The simulated transconductance of the cell can be tuned from 5.3 nA/V up to 19.60 A/V. The measured range of the experimental transconductance varied, however, between 1.42 A/V and 20.57 A/V. Similarly, the center frequency of the BPF, which in the simulations ranged from 500 Hz to 342 kHz, can be programmed in the silicon prototypes from 22.4 kHz to 290 kHz. Monte Carlo and corner simulations were carried out to ascertain the origin of this deviation. Besides, the extensive simulation and experimental characterization of the standalone transconductor and the complete BPF are provided.

1. Introduction

The electrical bioimpedance (BI) technique allows characterizing a biological medium through its electrical properties [1]. A sinusoidal excitation signal is applied to the impedance under test (), and its composition is determined in terms of the magnitude and phase of the signal response. A current is usually preferred as the stimulation signal, to avoid damages in the sample. In particular, currents in the range of A to a few mA are typically used. In such a case, a voltage has to be acquired across , which is usually achieved by means of an instrumentation amplifier, and subsequently conditioned and processed. The measurement of the biological impedance at a given single frequency is commonly known as bioimpedance analysis (BIA).

Bioimpedance spectroscopy (BIS) is used to determine the impedance over a frequency range, which is known as the dispersion range , typically varying from several hundreds of Hz to a few MHz. One approach to address the BIS was to use a stepped-sine excitation current, , and carry out the measurements sequentially while the frequency of was changed for each analysis. Nevertheless, this solution is only suitable when the physiological phenomenon does not change in time or variations are very slow. In the case of time-variant events, it is recommended to follow a multi-sine bioimpedance analysis, which allows simultaneous bioimpedance measurements at different frequencies. Besides, if the model to adjust the frequency response of the medium under test is known, a very limited number of samples results in being sufficient in most applications [2].

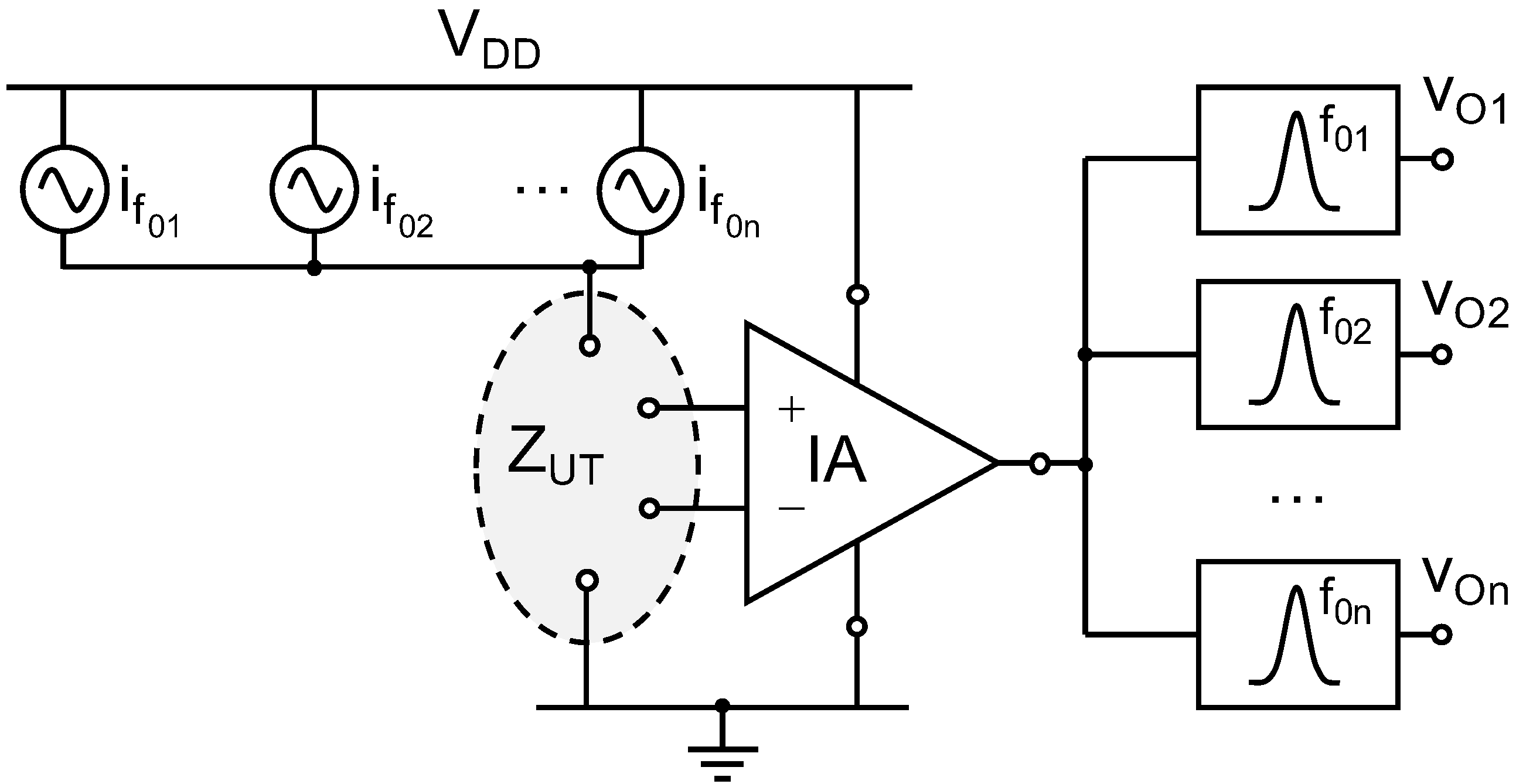

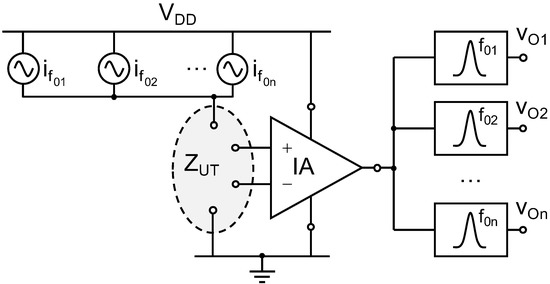

The front-end of a multi-sine BI analyzer, shown in Figure 1, includes the generation and summation of all the excitation signals, from to , which are subsequently applied to . The frequency components in the overall response obtained at must be separated, which can be achieved by using a bandpass filter (BPF) with a certain selectivity degree. A suitable technique to implement a monolithic BPF is the -C approach [3,4,5,6,7,8,9,10], where the characteristic frequencies of the filter are given by the ratio of a transconductance () and a capacitor (C), being an appropriate tuning parameter. Indeed, an electronically programmable transconductor allows a straightforward adjustment of the different characteristics of the BPF, whereas a continuous tuning facilitates the implementation of automatic control loops.

Figure 1.

Bioimpedance spectroscopy by multi-sine analysis.

In this work, the design of a widely tunable transconductor in 180 nm CMOS technology is presented, and its application to the implementation of a fully integrated second-order -C BPF for multi-sine BI analysis is detailed. The proposed transconductor [11] incorporates a mechanism for continuous tuning of , which leads to the programmability of the center frequency of the BPF over nearly three decades. Silicon prototypes of the standalone transconductor and the BPF were fabricated, and the correspondence between simulation and experimental results is discussed. The rest of the paper is organized as follows. A review of the state-of-the-art of widely tunable transconductors able to achieve a very low transconductance is reported in Section 2. The principle of operation of the proposed transconductor is described in Section 3, and the structure of the BPF is detailed in Section 4. The simulation and experimental results are reported, compared, and discussed in Section 5, and finally, conclusions are drawn in Section 6.

2. Widely Tunable Low- Techniques

The programmability of the center frequency of a BPF over a broad frequency range requires the availability of a widely tunable transconductor. Besides, if operation at low frequencies is required, the minimum achievable transconductance should be very low in order to avoid using excessively large integrated capacitors. Different approaches have been previously proposed in order to design a tunable transconductor able to achieve a very small value [12]. As a result, filters with a broad programmability range [13,14] or suitable for operation at very low frequency have been implemented [15,16,17,18].

Multiple solutions have been proposed in the literature to attain a low- transconductor. On the one hand, linearization techniques lead to a reduction of the effective transconductance of a differential stage. Among them, we can mention source degeneration [19,20], bump linearization [21], or triode operation [22]. Furthermore, the current division approach [12] enables increasing the current levels, in order to obtain a good matching, while simultaneously resulting in a very low value. Signal attenuation is another widespread technique used to reduce the effective transconductance of a differential stage. To this end, either passive components [23] or active devices with an inherently attenuating response, such as bulk-driven [24] or floating-gate [25] MOS transistors, can be used. Regarding the tuning of , common approaches are based on modifying the biasing current levels of the input section [5] or the drain-to-source voltage, , of the input devices when they are operated in the triode region [26]. Besides, the use of component banks that can be digitally controlled [27,28] or the inclusion of continuously adjustable current mirrors [29] is an extended practice.

In [30], current division and source degeneration techniques were applied to gate-driven, bulk-driven, and floating-gate MOS transistors to obtain a very low . Nevertheless, the proposed solutions were not provided with programmability. Mourabit et al. [31] proposed the use of multiple-input floating-gate transistors to implement a transconductor in which linearization was achieved by cancellation of the cubic distortion term. The use of MOS transistors operating in the triode region was proposed in [32,33] to attain a low transconductance value. However, the tuning range can be constrained by the relatively narrow region of the drain-to-source voltage in which a MOS transistor operates in ohmic mode. The channel-length modulation effect can also be exploited to obtain a low transconductance value [34], and this approach has also been adapted to operate in a low-voltage environment [35]. The proposal in [36] combined signal attenuation, current division, and resistive source degeneration to reach low values. In this case, signal attenuation led to an increase of the effective input differential mode (DM) voltage range, which constrained the operation of the common mode (CM) feedback (CMFB) section. Besides, current division requires the use of a certain amount of biasing current, which is not subsequently used for the signal processing. Current steering [18,37] is another solution that allows reduction and electronic tuning in a linearized transconductor. In [38], the bootstrapping effect was applied to a passive resistor, with the help of two voltage followers, to achieve transconductance values in the range of tens of nA/V. Nevertheless, the tuning range obtained was very narrow. Finally, it is worth pointing out that, in addition to the use of bulk-driven [39,40,41] and floating-gate [3] MOS transistors, also quasi-floating-gate MOS devices [42] have been proposed in the literature to obtain a widely tunable low- transconductor.

3. Proposed Widely Tunable Transconductor

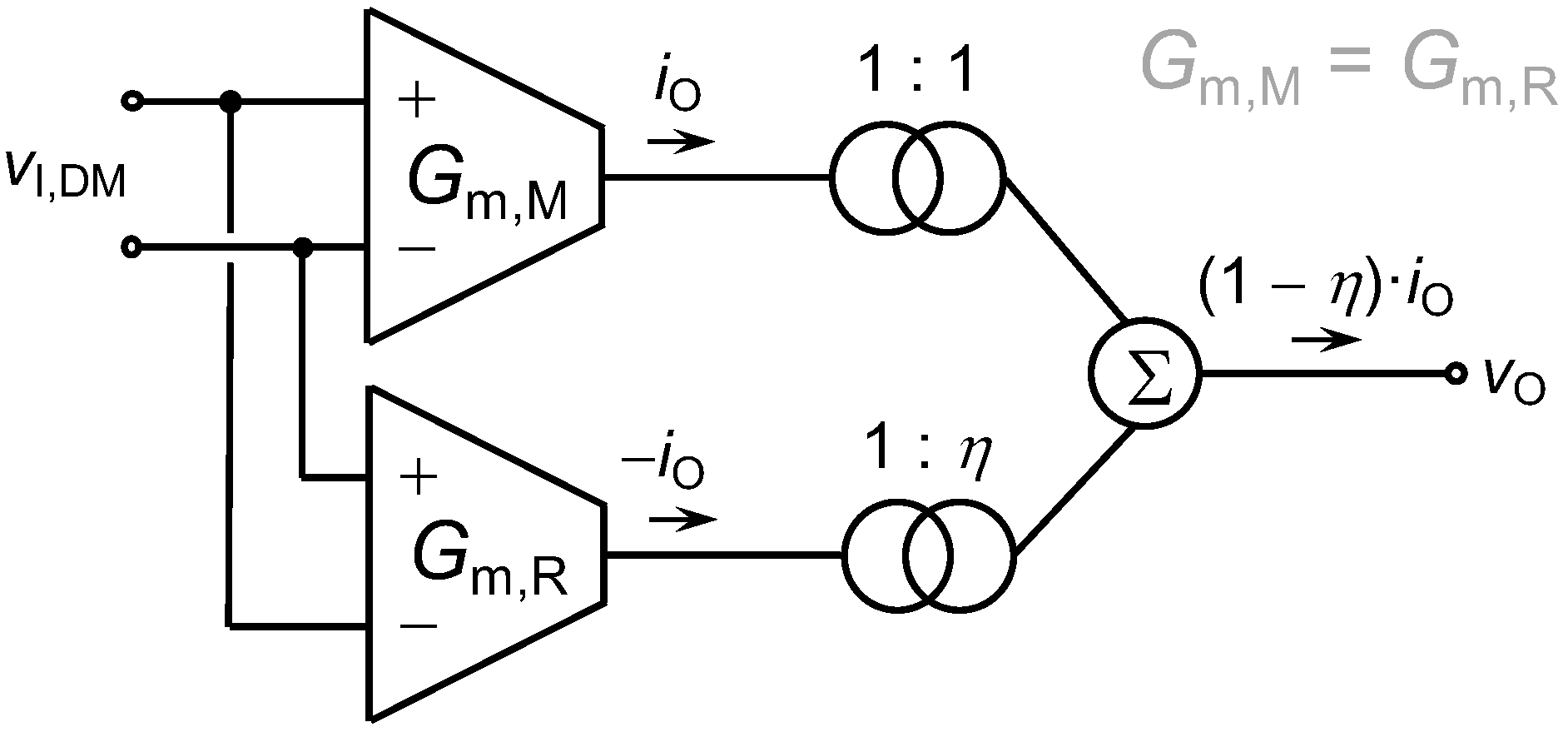

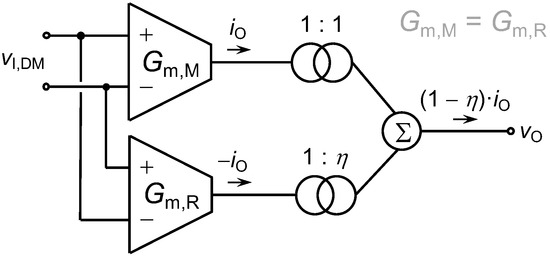

The conceptual block diagram of the proposed transconductor is illustrated in Figure 2. As observed, the output current contributions of two matched voltage-to-current (V-to-I) converters, and from the main and replica, respectively, are subtracted by reversing the polarity of their input voltages. Besides, the output current of is conveyed to the transconductor output by a current mirror with a gain nominally equal to unity, while the current gain for is equal to a parameter, . The resulting effective transconductance is

where . If the value of the gain of the current mirror that processes the signal from is programmed in the range , can be continuously tuned over a very wide range of values, from down to values very close to zero.

Figure 2.

Block diagram of the proposed tunable transconductor.

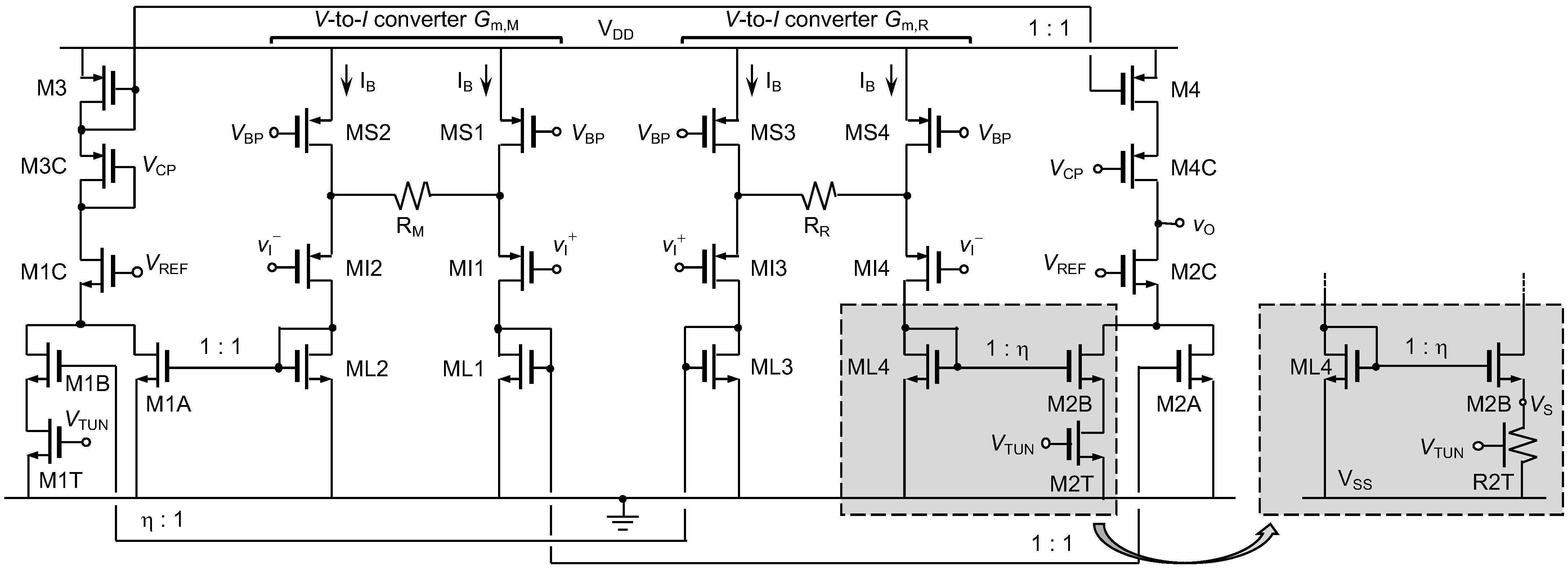

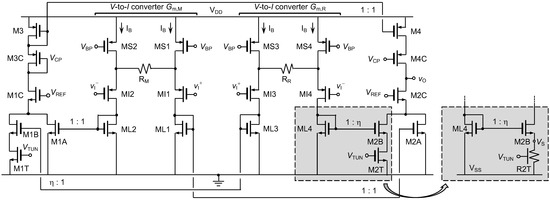

The transistor-level implementation of the proposed transconductor is depicted in Figure 3. The principle of operation of the two V-to-I cells is based on converting a voltage into a current on a resistor, and at and , respectively. Two source followers, transistors MI and MS, isolate the resistor in each cell from the preceding and the subsequent stages, while load transistors ML are used to mirror the current signal to the output node. The transconductance of each V-to-I converter can be expressed as

where and is the transconductance of equally sized transistors MI1 to MI4. The factor of 2 indicates that the current generated is conveyed to the output node through both branches of the V-to-I converter, whereas the second term describes analytically the loading effect of R on the source followers.

Figure 3.

Transistor-level implementation of the proposed tunable transconductor.

The input DM voltage range of the transconductor is constrained by the maximum current, , that can flow through the source degeneration resistors, that is

Besides, the input CM voltage is limited close to ground and by the operation in the saturation of the input transistors, MI1 to MI4, and the current source transistors, MS1 to MS4, respectively. Regarding the output voltage range, it can be extended, if required, by using a fully differential (FD) structure, which is a common practice in low-voltage environments and also provides well-known additional benefits. Besides, in the particular case of the circuit in Figure 3, the use of a FD configuration would allow getting rid of the systematic offset voltage introduced by the PMOS current mirror formed by M3 and M4. Nevertheless, the need for a CMFB network in a differential structure and its design complexity in the case of a tunable circuit led to the choice of a single-ended structure, with which the specifications of the intended application can be met.

The transconductance of the V-to-I converter can be continuously tuned by including transistors M1T and M2T below the output transistors of the NMOS current mirrors, M1B and M2B, as observed in Figure 3. Indeed, when the voltage at the gate of transistors M1T and M2T, , is equal to ground, these devices are turned off, and the effective drain-to-source resistance of the transistor is ideally infinite. Hence, only the contribution of is processed through current mirrors with gain 1:1 in Figure 3. As the value of increases, the drain-to-source resistance of the tuning devices, represented by the equivalent resistance R2T in Figure 3, is reduced and the voltage at the source terminal of transistors M1B and M2B, , is set closer to ground. For the extreme situation in which , ideally and, hence, the gain of the NMOS current mirrors is very close to unity. In such a case, , which theoretically allows obtaining a very low transconductance value. The gain of the programmable current mirrors, , has a nonlinear dependence on the control variable , and its particular expression will depend on the inversion level of the transistors, i.e., weak, moderate, or strong. Nevertheless, the response of the transconductor in terms of total harmonic distortion (THD) is not impacted by this fact as is first adjusted to obtain the required transconductance level and is then kept constant during the normal operation of the circuit.

It becomes apparent from Figure 2 that a tunable transconductor can be implemented by using only the replica transconductor and the programmable current mirror with gain 1:. Indeed, a DM voltage applied to the input of this arrangement produces an output current equal to , which is equivalent to an effective transconductance , which can be adjusted by means of parameter . Nevertheless, the actual implementation of the V-to-I converter in Figure 3 reveals that, for very low values of , the value of the current flowing through the output branch is very small, and hence, the linear operating range of transconductor is significantly reduced as compared to the proposed configuration.

As was already detailed, the principle of operation of the proposed transconductor is based on subtracting the individual transconductance contributions of two ideally equal V-to-I converters. Therefore, the minimum achievable effective transconductance relies on the matching between these basic building blocks. In principle, there are different possible sources of error, highlighting the key role of the source degeneration resistors and the current mirrors. The sensitivity of the proposed transconductor to random variations in the source degeneration resistors, and , was analytically evaluated, and the corresponding results are given next. A similar analysis can be carried out for the mismatch contribution of the current mirrors. Assuming values for the resistors and , the expression of the minimum effective transconductance, reached for the tuning case in which , i.e., , can be approached as

That is, the minimum achievable moves from the ideal value of zero to approximately a level in the range predicted by (4).

The proposed transconductor has a single-stage structure, and hence, the open-loop voltage gain can be written as

where

is the output resistance, is the load capacitor, and only the dominant pole has been taken into account. From (5), the open-loop DC gain, , and the dominant pole, , of the transconductor can be expressed, respectively, as follows:

where V, the effective transconductance takes its maximum value (), the DC current flowing through the output branch is equal to , and the intrinsic gain of the transconductor at low frequencies displays its maximum value, which is relatively high due to the use of cascode transistors. Nevertheless, for the case in which , the value of reaches its minimum level, whereas the DC current at the output branch is equal to 2, that is twice with respect to the other extreme case considered. As a consequence, the open-loop voltage gain of the transconductor will be greatly reduced and its closed-loop response will be correspondingly affected despite the inclusion of cascode transistors. For this reason, a long channel length was set for the transistors determining the open-loop gain of the transconductor, in order to increase its value in the worst-case operating point.

4. Second-Order -C Bandpass Filter

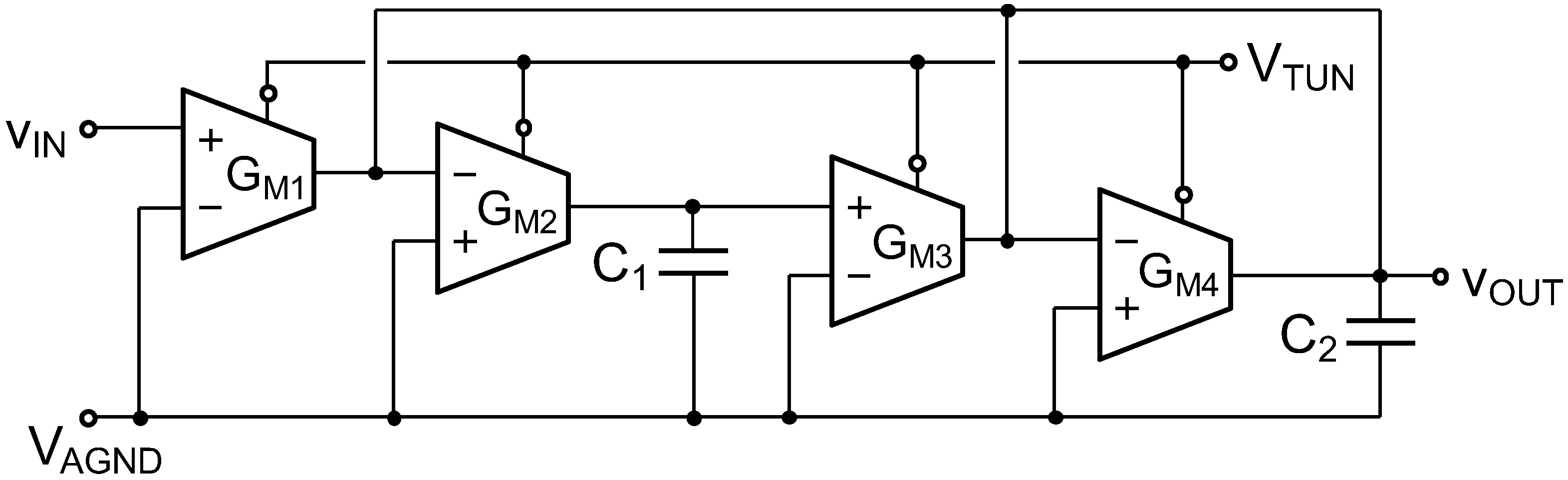

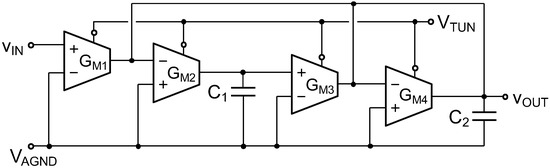

The block diagram of the second-order -C BPF designed and implemented is shown in Figure 4. A routine hand analysis leads to the following expression for its transfer function:

where , with i = 1 to 4, is the effective transconductance of the i-th transconductor and and are on-chip capacitors. The gain at the center frequency, , the center frequency, , and the quality factor, Q, can be obtained from (8) and expressed as

Figure 4.

Circuit schematic of the designed -C BPF.

It is worth pointing out that the inclusion of four transconductors in the BPF implementation allows programming the voltage gain, the center frequency, and the quality factor independently. The BPF illustrated in Figure 4 aims at the separation of signals at different frequencies in multi-sine bioimpedance analysis, which requires a moderate to relatively high quality factor. The Q of the filter can be robustly determined, in view of (9c), as a ratio of transconductances, i.e., , or a ratio of capacitors, that is . In the design described in this work, the second option was selected in order to be able to use the same transconductor to implement to . Therefore, considering all the transconductors equal, i.e., , and by setting , the gain at the center frequency, the center frequency, and the quality factor may be obtained from (9) as

The resulting BPF has constant values of and Q, whereas can be tuned by modifying the value of in (10b). The programmability of was obtained by adjusting the control variable in Figure 3 and Figure 4. Indeed, when = 0 V, the value of reaches its maximum level, , which leads to the highest achievable center frequency. On the other hand, for the case in which , the value of reaches its minimum value, and hence, also in the BPF does. Finally, it is worth noting that the voltage in Figure 4 represents the analog ground, that is the intermediate level between and ground when a single supply is used.

5. Simulation and Experimental Results

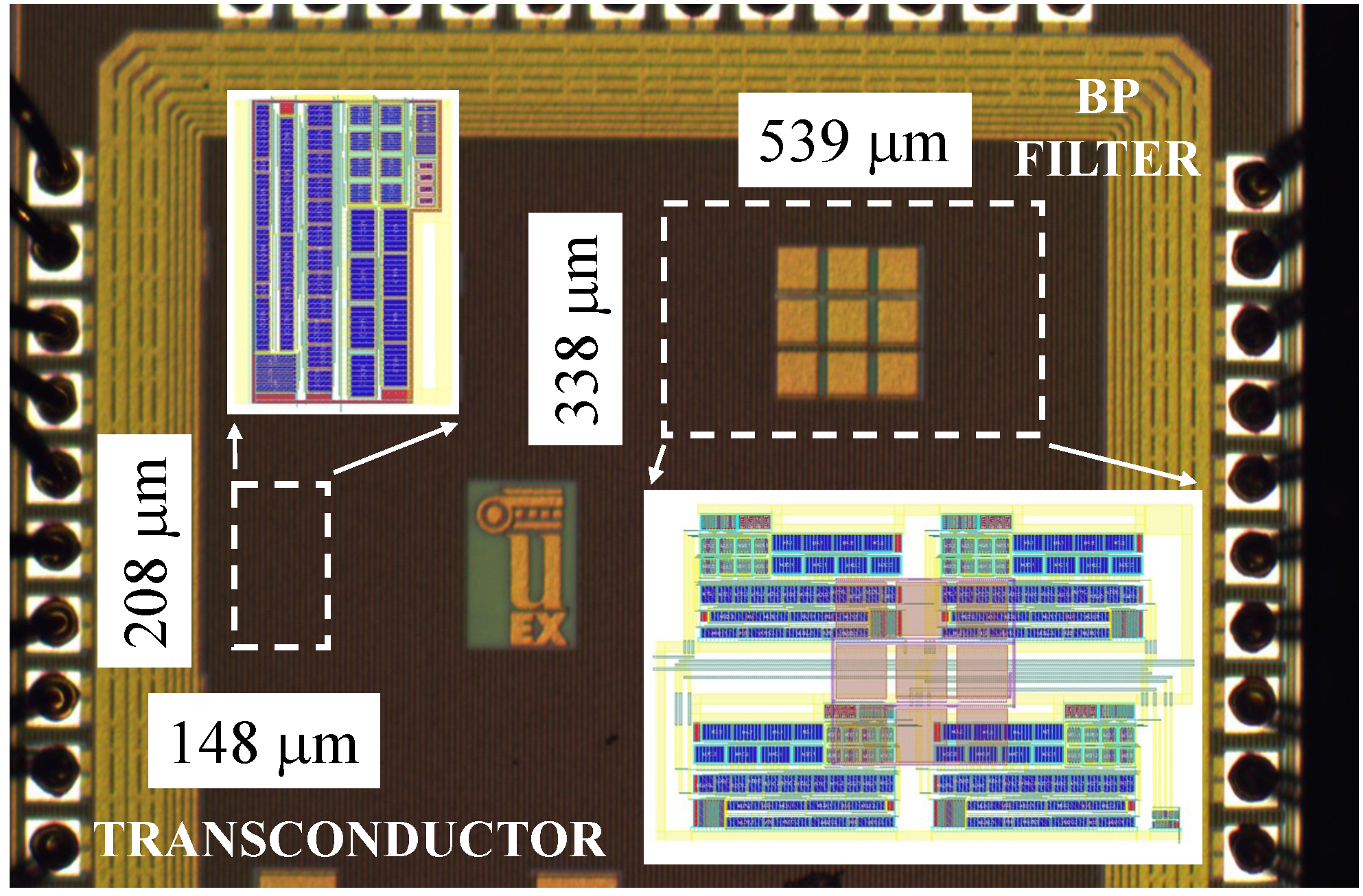

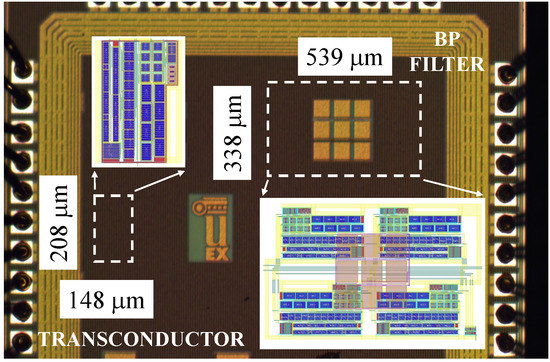

The transconductor illustrated in Figure 3 and the second-order -C BPF depicted in Figure 4 were designed and fabricated in 180 nm CMOS technology to operate with a single supply voltage of 1.8 V. The transistors’ aspect ratios, source degeneration resistors’ values, and biasing currents levels were estimated by taking into account the expressions of the transconductance in (1) and (2), so that the filter response can span the intended frequency range and the input DM voltage range in (3), in order to be able to process the typical input signals level, in the order of tenths of mV in our application. Subsequently, these values were refined by means of simulations with a twofold objective: achieving the proposed specifications and ensuring the operation in saturation of all the active devices, thus resulting in the sizes provided in Table 1. A microphotograph of the chip is provided in Figure 5, where the layout of the transconductor and the BPF are detailed. A total of eight samples of the silicon prototypes were experimentally characterized.

Table 1.

Transistor aspect ratios of the transconductor in Figure 3.

Figure 5.

Chip microphotograph.

In the case of the transconductor in Figure 3, the biasing current, , was set to 20 A and the source degeneration resistors, and , were implemented with high-resistivity non-salicided polysilicon with a nominal value of 5 kΩ. The reference voltage used to bias the NMOS cascode transistors was set to 0.9 V, whereas the PMOS cascode transistor M4C was biased by the diode-connected transistor M3C. Besides, it is worth pointing out that the current mirrors connected to the main and replica V-to-I converters were sized to have an additional attenuation of 10:1 in order to further reduce the minimum achievable transconductance value. The output terminal of the transconductor was directly connected to the bonding pad, avoiding any internal buffering, with the goal of carrying out a thorough experimental characterization of the standalone block.

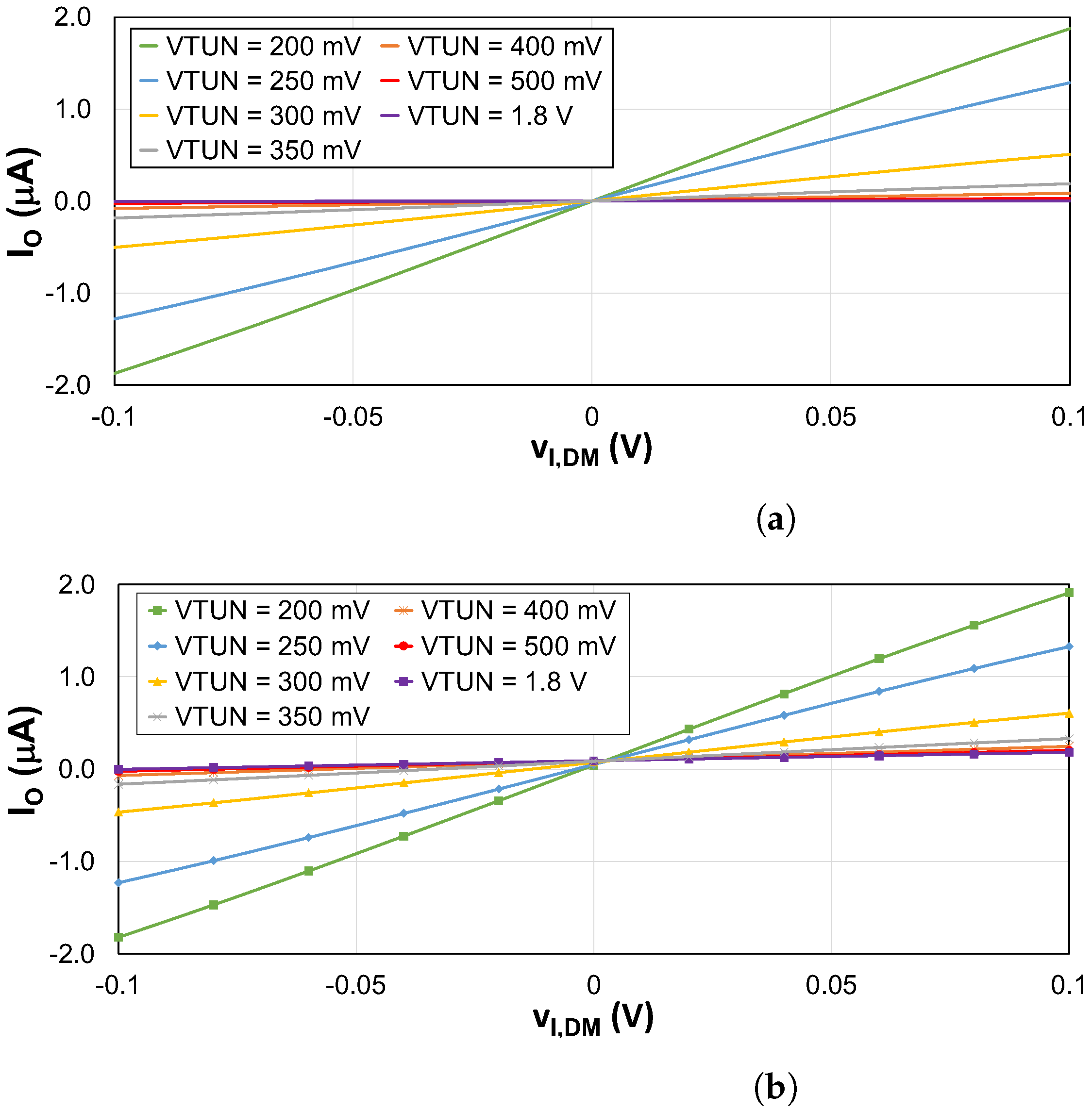

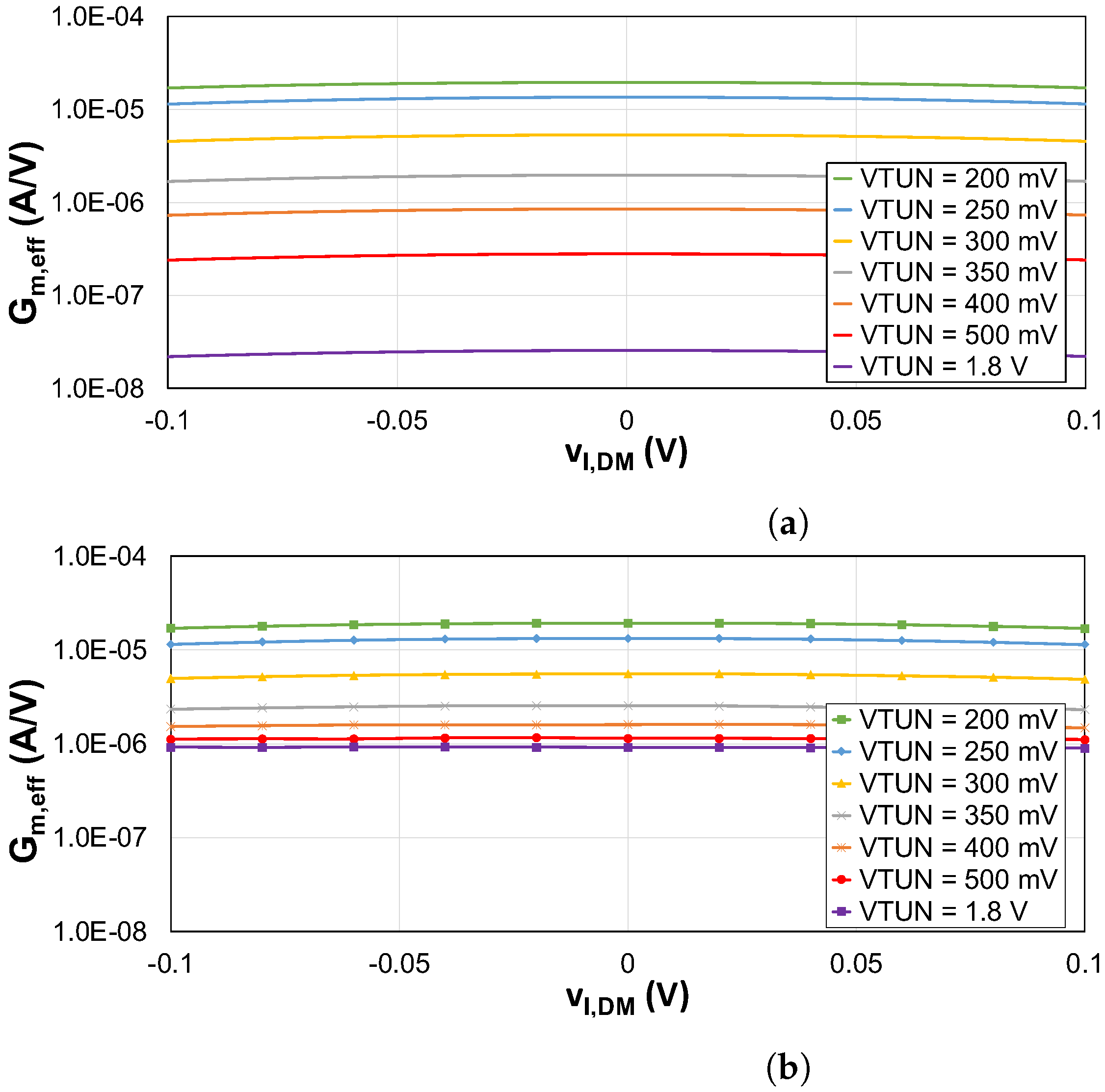

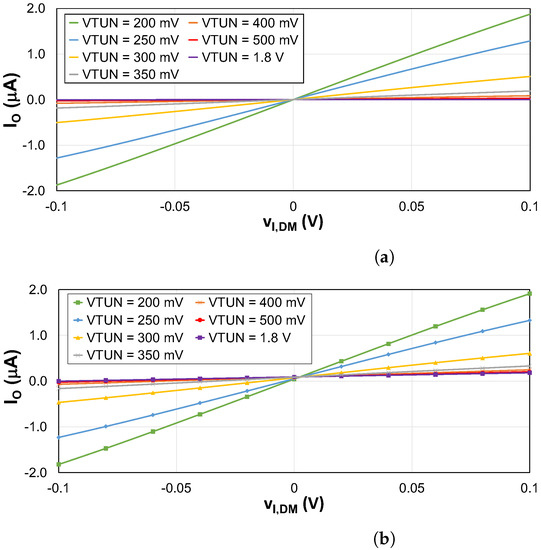

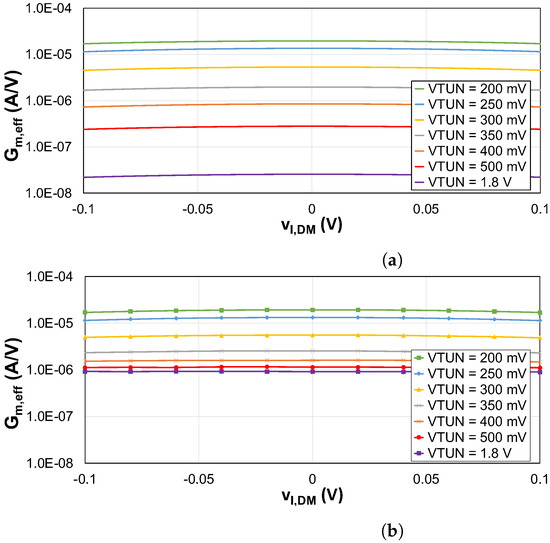

The effective of the transconductor was determined by applying an input DM signal superimposed on a CM voltage of 0.9 V, while shorting the output terminal also to 0.9 V, i.e., the mid-supply. First, the output current, , was obtained as a function of the input DM voltage, , as illustrated in Figure 6, where the simulated and experimental responses are provided. A highly linear behavior of the output current can be observed during a substantial range of the input DM voltage. Then, the derivative of with respect to led to , which is represented in Figure 7. A logarithmic scale was selected for the ordinate axis, due to the broad range achieved for the simulated transconductance (Figure 7a), which spans over nearly three decades. Indeed, when = 0 V, being disabled, a maximum value for the transconductance of 19.92 A/V was obtained in typical mean conditions (tt), whereas for = 1.8 V, being fully enabled, the transconductance was reduced to only 25.7 nA/V. On the other hand, the measured transconductance (Figure 7b) showed a maximum value of 20.57 A/V, in close agreement with the simulated result, whereas the minimum value, 1.42 A/V, was noticeably higher than in the simulations. The measurements were repeated by using a different methodology. A commercial transimpedance amplifier (TIA) was connected to the output of the transconductor, in order to convert the output current into a voltage. The value of was determined by deriving the output voltage with respect to the input DM voltage and taking into account the gain of the TIA. The experimental results obtained in this case confirmed the responses illustrated in Figure 7b.

Figure 6.

Transconductor output current as a function of the input DM voltage: (a) simulated and (b) measured responses.

Figure 7.

Effective transconductance vs. : (a) simulated and (b) measured responses.

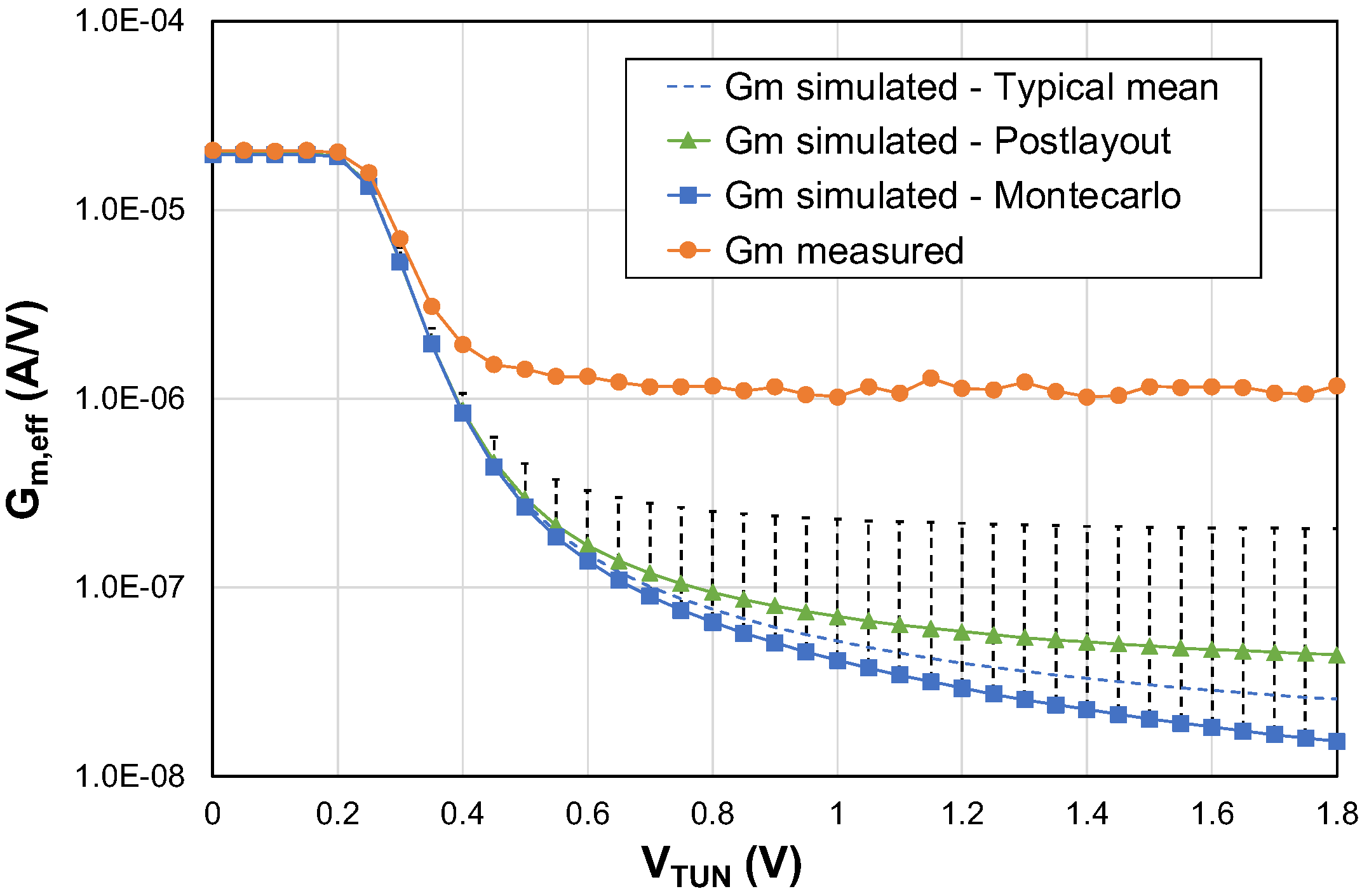

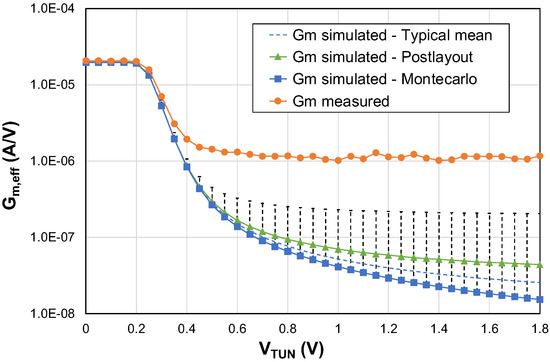

The impact of mismatches and process variations on was assessed. Very similar results were obtained at the corners (ff, ss, fnsp, and snfp) as compared to the tt case, that is there was not an important change in when the process parameters were equally varied in the same type of transistors. Besides, a 1000-run Monte Carlo analysis, including mismatch and process variations in a 3- distribution, were carried out for a large variety of values of the control variable . The corresponding results are provided in Figure 8, where the upper error bars, indicating the standard deviation of the effective transconductance, are included for this case. The transconductance simulated in typical mean and post-layout conditions are also included in Figure 8, for comparison purposes and to illustrate the influence of parasitics, respectively. As observed, the experimental results were in general out of the error margin of the Monte Carlo response when the standard deviation was considered to define this range. It is worth pointing out that, even though the statistical simulations showed possible negative values for the transconductance, this fact can be counteracted by the tuning scheme, which grants the possibility of achieving a positive value in every case.

Figure 8.

Effective transconductance as a function of .

Different sources of error, including systematic and random mismatches, could explain the divergence between the simulated and the experimental response of the effective transconductance, which becomes evident from Figure 7 and Figure 8. Nevertheless, the analysis of the experimental results obtained in the eight available samples of the transconductor showed that, in all the cases, the measured presented a maximum level very close to the simulated value and a minimum bound always higher than the value expected from the simulations. This fact suggests that the limitation preventing achieving a very low transconductance could have a systematic origin. Besides, the Monte Carlo analysis reported previously showed that the experimental error of the transconductance was larger than the standard deviation of the simulated results, which was mainly caused by random variations. For these reasons, the inclusion of transistors M1T and M2T in the overall structure, along with a possible underestimation of their on-resistance in the transistors models, was considered as the main factor causing the divergence of the experimental transconductance from the expected response when the transconductor was programmed to generate low values.

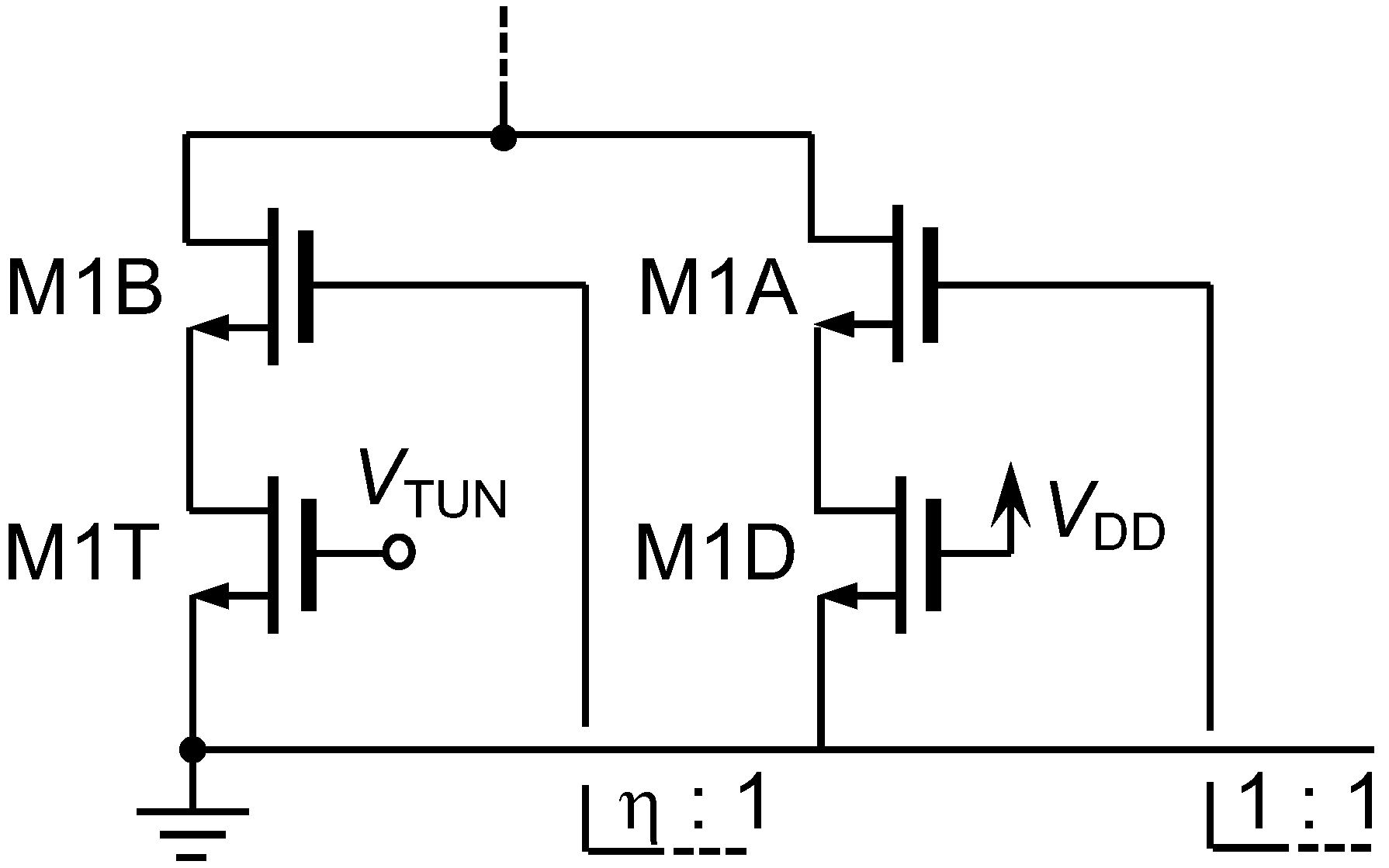

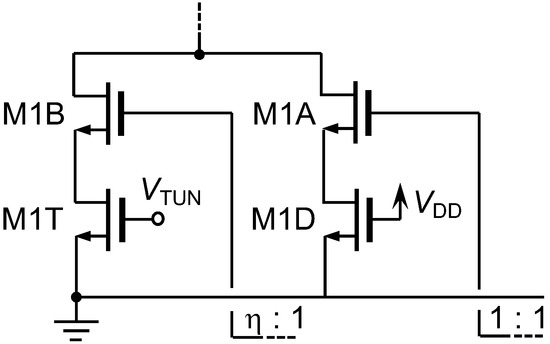

The effect of transistors M1T and M2T on is difficult to fully eliminate, even though it can be counteracted by inducing a similar behavior in the current mirrors that are not tuned, that is on those processing the signal of the V-to-I converter . The scheme proposed in Figure 9 includes a dummy device, M1D, in the current mirrors with a fixed gain in order to reduce their gain in the same proportion as was performed in the programmable current mirrors when . Indeed, in this particular case, the presence of transistors M1D and M2D ideally canceled out the impact of transistors M1T and M2T on when the minimum value of the transconductance was intended to be achieved. As a consequence, the subtraction of and was more effective, as it was demonstrated by means of a 1000-run Monte Carlo analysis including 3- mismatch and process variations, which led to an average value for the effective transconductance of only 1.2 ± 197.4 nA/V. Furthermore, the inclusion of transistors M1D and M2D had a negligible effect when the transconductor was programmed to obtain a higher value. The effectiveness of the solution illustrated in Figure 9 has to be proven experimentally.

Figure 9.

Scheme to further reduce the value of .

The overall performance of the widely tunable transconductor presented is summarized in Table 2 for = 0 V and = 1.8 V. In general, there was good agreement between the simulation and experimental results for high transconductance values ( = 0 V). The gap arising when the transconductor was programmed for a low ( = 1.8 V) was due to the disparity between the simulated and measured transconductances. The data expressed in Table 2 as the mean value plus/minus the standard deviation were obtained through a 1000-run Monte Carlo analysis with mismatch and process variations in a 3- distribution in the case of simulations and from the measurements conducted on eight different samples in the case of the experimental results. Besides, the closed-loop configuration was established by shorting the output terminal to the inverting input terminal, that is by connecting the transconductor in a non-inverting unity-gain feedback configuration. Additionally, a load capacitor was connected to the output terminal in order to obtain a dominant-pole response and, hence, ensure appropriate frequency and time responses. The total output capacitance was estimated to be 64 pF, including the load capacitor, as well as the capacitive effects of the PCB used for test purposes and the test probe. The relatively high value of the load capacitor reduced the bandwidth of the transconductor, thus leading to a decrease of the noise integrated from the low-frequency range (100 Hz) up to the bandwidth (∼50 kHz). As a result, a high value of the dynamic range (DR) was obtained.

Table 2.

Comparison of the simulated and experimental performance of the proposed low- widely tunable transconductor.

The performance of the proposed transconductor is compared in Table 3 to other solutions previously reported to simultaneously achieve a low value and a broad programmability range. As observed, the solution presented provided a wide simulated transconductance tuning range at the cost of the highest supply current. Nevertheless, as was pointed out before, this power consumption is a well-known design trade-off to achieve a determined input DM voltage range for a given value of the source degeneration resistor R.

Table 3.

Performance comparison of the proposed transconductor with other solutions reported in the literature.

The second-order -C BPF in Figure 4 was implemented by using four identical replicas of the transconductor shown in Figure 3, to , and two integrated metal–insulator–metal capacitors with nominal values of = 2.5 pF and = 20 pF, resulting in a quality factor of Q = 2.83. The supply voltage used was equal to 1.8 V, and the analog ground voltage was set to mid-supply, i.e., = 0.9 V, whereas all the transconductors were biased with a current equal to 20 A. An on-chip buffer was connected to the output of the filter for testing purposes.

The DC current consumption of the proposed BPF slightly varied with the value of . Indeed, for levels of the tuning variable close to ground, the signal of the replica V-to-I converter in each transconductor was not mirrored to the output terminal, thus resulting in a total current of 413.3 A. When the tuning transistors were completely switched on, for approximately equal to 0.4 V and higher, the corresponding current mirrors were fully enabled, and hence, the current consumption increased up to 429.1 A. The total difference between the different operating points was reduced by the use of the 10:1 attenuation factor introduced in order to systematically reduce the value of . The simulated and experimental DC offset voltages of the BPF were extracted, respectively, from a Monte Carlo analysis (1000 runs with mismatch and process variations) and from measurements on the eight silicon samples of the prototype. The on-chip test buffer used to isolate the filter during the measurements was based on a PMOS source follower, which caused a level shift of the output voltage with respect to the ideal value of 0.9 V (mid-supply). For this reason, only the standard deviation of the output voltage was taken into account, obtaining simulated and measured values of 1.3/428.6 mV and 9.0/83.1 mV, respectively, for equal to 0/1.8 V. It can be observed that the output voltage deviation was larger for = 1.8 V, a case in which the transconductance achieved its minimum value and led to the lowest value of the intrinsic gain of the transconductors involved in the implementation. Indeed, the simulated offset voltage showed a larger deviation because the effective transconductance took a significantly lower value.

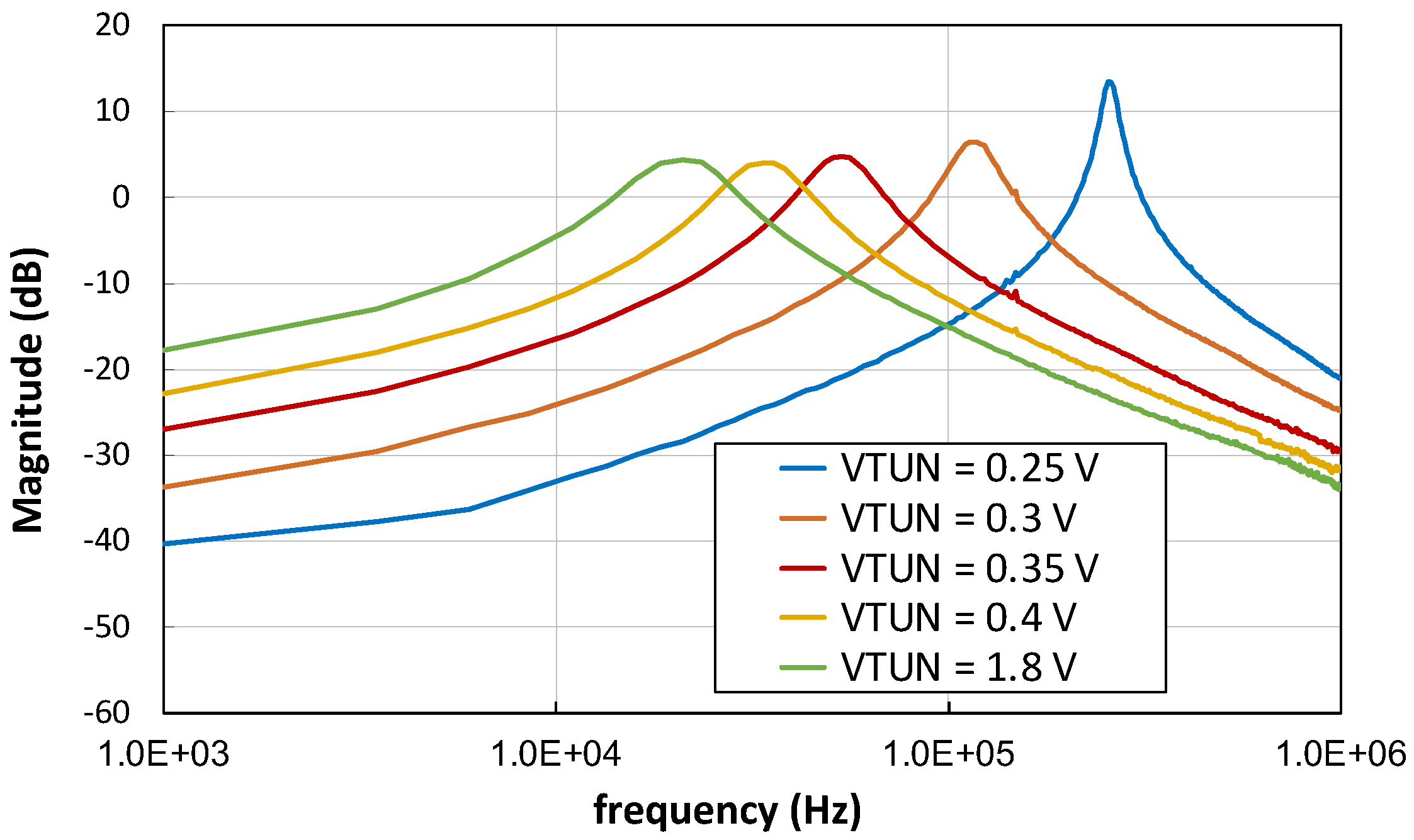

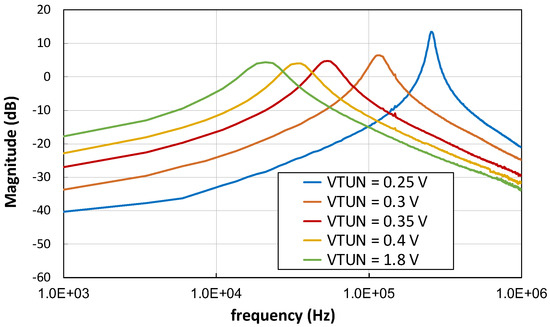

The frequency response of the magnitude of the -C BPF is illustrated in Figure 10, measured for different values of the tuning variable . The center frequency varied from 258 kHz down to 22.4 kHz as the tuning variable, , was increased from 0.25 V to 1.8 V. The overdamping observed in the plot corresponding to = 0.25 V was due to the proximity of the center frequency of the filter to the secondary poles of the transconductors and was boosted by the effect of the value of Q selected. As the level of was made higher, the filter center frequency was separated from the secondary poles and the overdamping was reduced.

Figure 10.

Experimental frequency response of the BPF magnitude for different values of .

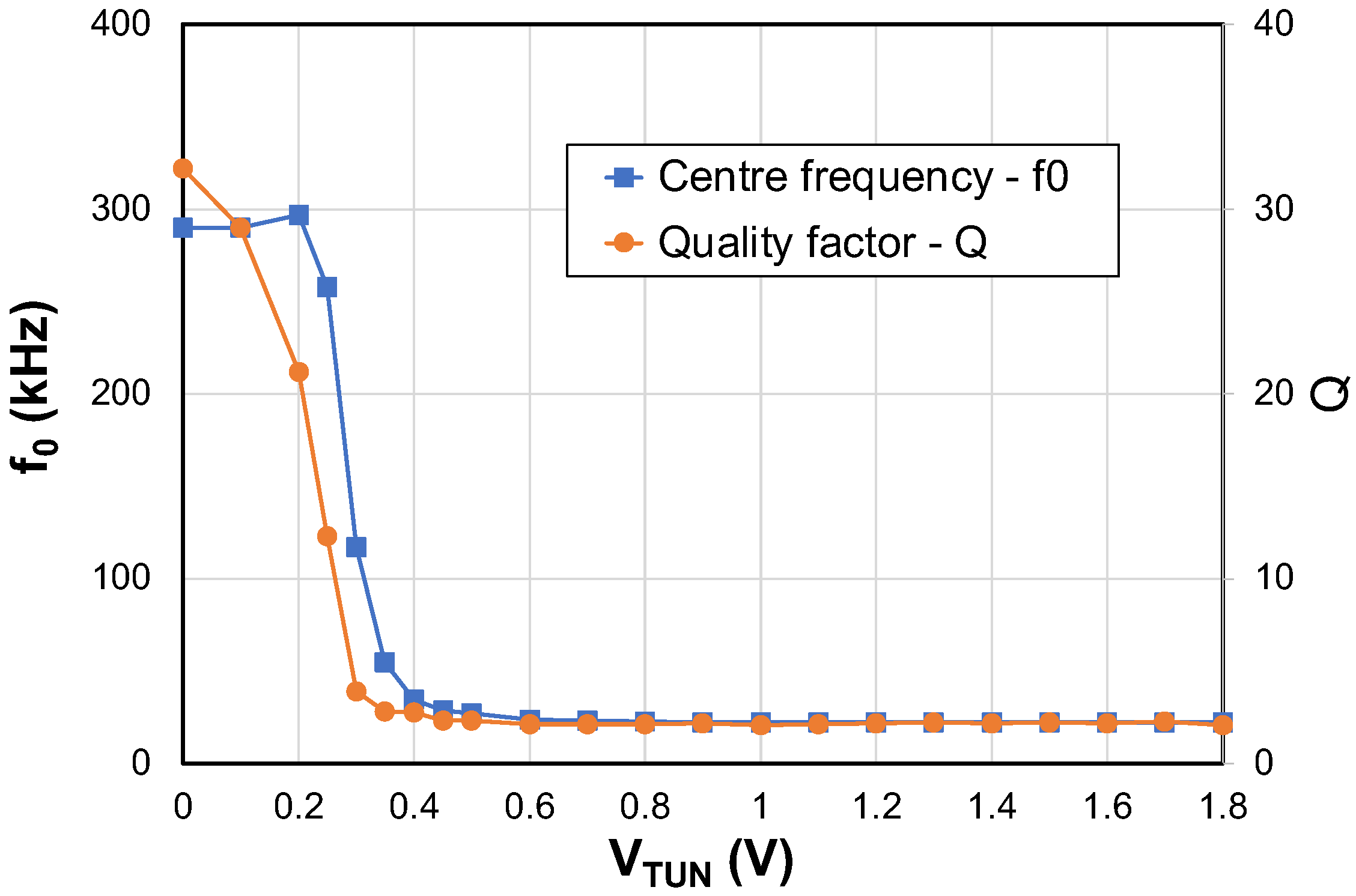

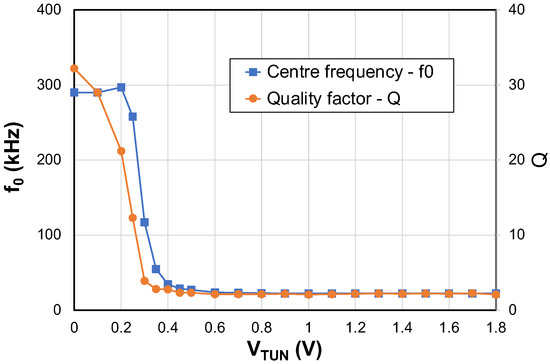

The response of the filter center frequency, , was measured over the entire range of the tuning magnitude, , that is from 0 V to 1.8 V, and is depicted in Figure 11. As observed, the center frequency of the BPF behaved exactly equal to in Figure 8 when was swept. Therefore, the BPF center frequency presented similar limitations in the tuning range as the effective transconductance of the proposed transconductor. Indeed, the simulated frequency response of the BPF led to minimum and maximum values of equal to 500 Hz and 342 kHz, respectively, while the experimental characterization of the filter provided an operating frequency range between 22.4 kHz and 290 kHz. The quality factor as a function of is also represented in Figure 11. Each value of Q was estimated taking into account the measurements of the center frequency and the 3 dB bandwidth of the BPF. For around ground, the high effective transconductance pushed the filter center frequency to high values. Thus, the proximity of the secondary poles of the transconductors to resulted in an increase of the effective value of Q. As was increased, the value of was reduced, and hence, the influence of the secondary poles was alleviated, thus decreasing the quality factor to a level close to the nominal design value.

Figure 11.

Measured values of and Q vs. .

The performance of the proposed second-order -C BPF is summarized in Table 4, where it is also compared to other works previously reported. The following figure-of-merit (FoM) [5], which is very widespread, was used to establish an objective comparison:

where P is the power consumption, the supply voltage, n the filter order, the center frequency, and DR the dynamic range. It is worth pointing out two important aspects. On the one hand, a filter implementation of a given order can make use of a different number of transconductors, depending on the degrees of freedom desired to program individually the gain, the center frequency, and the quality factor. Besides, designing a filter to operate at a given frequency allows optimizing the power consumption more efficiently than in the case in which programmability over a broad frequency range is required. For this reason, the FoM in (11) was modified as follows in order to normalize the total power consumption by the number of transconductors incorporated (FoM) or by the achievable frequency range (FoM):

where in (12) is the number of transconductors involved in the filter and is the ratio of the maximum and minimum achievable center frequencies. As observed in Table 4, even though the proposed solution provided a relatively high value for the initially proposed FoM, it became competitive in terms of the modified comparison parameters, that is FoM and FoM, when the number of transconductors and the achievable frequency range (in the simulated case) were taken into account.

Table 4.

Experimental performance of the proposed -C filter and comparison with similar solutions.

6. Conclusions

Multi-sine bioimpedance analysis requires the use of bandpass filters for signals separation. The use of a BPF with a broad programmability range of the center frequency and able to operate at low frequencies allows using the same filtering section in all the signal conditioning channels. The -C approach is a suitable candidate to adjust the characteristics of the BPF in a straightforward manner. A transconductor with widely tunable transconductance and capable of achieving a very low value, thus being suitable to be instantiated in a programmable -C BPF, was presented. The principle of operation was based on subtracting the responses of two V-to-I converters, linearized by means of resistive source degeneration. The proposed transconductor and a second-order -C BPF were designed and fabricated in 180 nm CMOS technology to operate with a 1.8 V supply. Measurements from eight samples of the silicon prototype were provided. Deviations between the simulated and experimental results for the ratio of the transconductor (from 1281.0× to 14.5×) and the center frequency range of the filter (from 684× to 13×) were found. Corner and Monte Carlo simulations were used to determine the origin of this disagreement, and a mechanism to further reduce the minimum achievable effective transconductance was proposed.

Author Contributions

Conceptualization, I.C., J.M.C., J.L.A. and J.F.D.-C.; methodology, I.C., J.M.C. and J.L.A.; software, I.C. and J.M.C.; formal analysis, J.M.C. and R.P.-A.; investigation, I.C., J.M.C. and J.L.A.; resources, I.C., J.M.C. and M.Á.D.; data curation, I.C., J.M.C., M.Á.D. and R.P.-A.; writing—original draft preparation, I.C., J.M.C., J.L.A. and J.F.D.-C.; writing—review and editing, I.C., J.M.C., J.L.A., M.Á.D., R.P.-A. and J.F.D.-C.; visualization, I.C. and J.M.C.; supervision, J.M.C., J.L.A. and J.F.D.-C.; project administration, J.F.D.-C.; funding acquisition, J.L.A. and J.F.D.-C. All authors have read and agreed to the published version of the manuscript.

Funding

This work was supported by MCIN/AEI/10.13039/501100011033 under Project RTI2018-095994-B-I00 and by Fondo Europeo de Desarrollo Regional (FEDER) “Una manera de hacer Europa”. Silicon samples granted by EUROPRACTICE MPW and design tool support.

Data Availability Statement

Data not subject to confidentiality are available upon request to the corresponding author.

Conflicts of Interest

The authors declare no conflict of interests.

References

- Kassanos, P. Bioimpedance sensors: A tutorial. IEEE Sens. J. 2021, 21, 22190–22219. [Google Scholar] [CrossRef]

- Sanchez, B.; Vandersteen, G.; Bragos, R.; Schoukens, J. Optimal multisine excitation design for broadband electrical impedance spectroscopy. Meas. Sci. Technol. 2011, 22, 115601. [Google Scholar] [CrossRef]

- Rodriguez-Villegas, E.; Yufera, A.; Rueda, A. A 1.25-V micropower Gm-C filter based on FGMOS transistors operating in weak inversion. IEEE J.-Solid-State Circuits 2004, 39, 100–111. [Google Scholar] [CrossRef]

- Graham, D.W.; Hasler, P.E.; Chawla, R.; Smith, P.D. A low-power programmable bandpass filter section for higher order filter applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2007, 54, 1165–1176. [Google Scholar] [CrossRef]

- Corbishley, P.; Rodriguez-Villegas, E. A nanopower bandpass filter for detection of an acoustic signal in a wearable breathing detector. IEEE Trans. Biomed. Circuits Syst. 2007, 1, 163–171. [Google Scholar] [CrossRef] [PubMed]

- Rumberg, B.; Graham, D.W. A low-power and high-precision programmable analog filter bank. IEEE Trans. Circuits Syst. II Express Briefs 2012, 59, 234–238. [Google Scholar] [CrossRef]

- Kulej, T.; Khateb, F. 0.4-V bulk-driven differential-difference amplifier. Microelectron. J. 2015, 46, 362–369. [Google Scholar] [CrossRef]

- Long, G.B.; Ericson, M.N.; Britton, C.L.; Roehrs, B.D.; Farquhar, E.D.; Frank, S.S.; Yen, A.; Blalock, B.J. A sub-threshold low-power integrated bandpass filter for highly integrated spectrum analyzers. In Proceedings of the IEEE International Conference on Electronics, Circuits and Systems (ICECS), Glasgow, UK, 23–25 November 2020; pp. 1–4. [Google Scholar]

- Corbacho, I.; Carrillo, J.M.; Ausín, J.L.; Domínguez, M.Á.; Duque-Carrillo, J.F. 0.8-V CMOS Gm-C bandpass filter for electrical bioimpedance spectroscopy. In Proceedings of the 2021 IEEE International Conference on Electronics, Circuits, and Systems (ICECS) Circuits, Dubai, United Arab Emirates, 28 November–1 December 2021; pp. 1–4. [Google Scholar]

- Carrillo, J.M.; de la Cruz-Blas, C.A. 0.6-V 1.65-μW second-order Gm-C bandpass filter for multi-frequency bioimpedance analysis based on a bootstrapped bulk-driven voltage buffer. J. Low Power Electron. Appl. 2022, 12, 62. [Google Scholar] [CrossRef]

- Corbacho, I.; Carrillo, J.M.; Ausín, J.L.; Domínguez, M.A.; Pérez-Aloe, R.; Duque-Carrillo, J.F. Impact of process variations on the performance of a widely tunable CMOS transconductor. In Proceedings of the 2022 18th International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD), Villasimius, Italy, 12–15 June 2022; pp. 1–4. [Google Scholar]

- Arnaud, A.; Fiorelli, R.; Galup-Montoro, C. Nanowatt, sub-nS OTAs, with sub-10-mV input offset, using series-parallel current mirrors. IEEE J.-Solid-State Circuits 2006, 41, 2009–2018. [Google Scholar] [CrossRef]

- Lo, T.Y.; Hung, C.C. A wide tuning range Gm –C continuous-time analog filter. IEEE Trans. Circuits Syst. I Regul. Pap. 2007, 54, 713–722. [Google Scholar] [CrossRef]

- Veerendranath, P.; Vasantha, M.; Kumar, Y.N.; Bonizzoni, E. A novel low power Gm-C continuous-time analog filter with wide tuning range. In Proceedings of the 2018 31st International Conference on VLSI Design and 2018 17th International Conference on Embedded Systems (VLSID), Pune, India, 6–10 January 2018; pp. 214–219. [Google Scholar]

- Solis-Bustos, S.; Silva-Martinez, J.; Maloberti, F.; Sanchez-Sinencio, E. A 60-dB dynamic-range CMOS sixth-order 2.4-Hz low-pass filter for medical applications. IEEE Trans. Circuits Syst. II Analog. Digit. Signal Process. 2000, 47, 1391–1398. [Google Scholar] [CrossRef]

- Sun, C.Y.; Lee, S.Y. A fifth-order Butterworth OTA-C LPF with multiple-output differential-input OTA for ECG applications. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 421–425. [Google Scholar] [CrossRef]

- Lee, S.Y.; Wang, C.P.; Chu, Y.S. Low-voltage OTA–C filter with an area- and power-efficient OTA for biosignal sensor applications. IEEE Trans. Biomed. Circuits Syst. 2019, 13, 56–67. [Google Scholar] [CrossRef]

- Pérez-Bailón, J.; Calvo, B.; Medrano, N. A CMOS low pass filter for SoC lock-in-based measurement devices. Sensors 2019, 19, 5173. [Google Scholar] [CrossRef] [PubMed]

- Krummenacher, F.; Joehl, N. A 4-MHz CMOS continuous-time filter with on-chip automatic tuning. IEEE J.-Solid-State Circuits 1988, 23, 750–758. [Google Scholar] [CrossRef]

- Steyaert, M.; Crols, J.; Gogaert, S.; Sansen, W. Low-voltage analog CMOS filter design. In Proceedings of the 1993 IEEE International Symposium on Circuits and Systems, Chicago, IL, USA, 3–6 May 1993; Volume 2, pp. 1447–1450. [Google Scholar]

- Sarpeshkar, R.; Lyon, R.F.; Mead, C. A low-power wide-linear-range transconductance amplifier. Analog. Integr. Circuits Signal Process. 1997, 13, 123–151. [Google Scholar] [CrossRef]

- Nauta, B.; Klumperink, E.; Kruiskamp, W. A CMOS triode transconductor. In Proceedings of the 1991 IEEE International Symposium on Circuits and Systems (ISCAS), Singapore, 11–14 June 1991; Volume 4, pp. 2232–2235. [Google Scholar]

- Salthouse, C.; Sarpeshkar, R. A practical micropower programmable bandpass filter for use in bionic ears. IEEE J.-Solid-State Circuits 2003, 38, 63–70. [Google Scholar] [CrossRef]

- Blalock, B.; Allen, P.; Rincon-Mora, G. Designing 1-V op amps using standard digital CMOS technology. IEEE Trans. Circuits Syst. II Analog. Digit. Signal Process. 1998, 45, 769–780. [Google Scholar] [CrossRef]

- Munoz, F.; Torralba, A.; Carvajal, R.; Tombs, J.; Ramirez-Angulo, J. Floating-gate-based tunable CMOS low-voltage linear transconductor and its application to HF g/sub m/-C filter design. IEEE Trans. Circuits Syst. II Analog. Digit. Signal Process. 2001, 48, 106–110. [Google Scholar] [CrossRef]

- Hori, S.; Maeda, T.; Matsuno, N.; Hida, H. Low-power widely tunable Gm-C filter with an adaptive DC-blocking, triode-biased MOSFET transconductor. In Proceedings of the 30th European Solid-State Circuits Conference, Leuven, Belgium, 21–23 September 2004; pp. 99–102. [Google Scholar]

- Calvo, B.; Sanz, M.; Celma, S.; Martinez, P. A CMOS digitally tunable transconductor for video frequency operation [programmable filter applications]. In Proceedings of the 2003 International Symposium on Circuits and Systems ISCAS ’03, Bangkok, Thailand, 25–28 May 2003; Volume 1, p. I. [Google Scholar]

- Sanchez-Rodriguez, T.; Lujan-Martinez, C.; Carvajal, R.; Ramirez-Angulo, J.; Lopez-Martin, A. A CMOS linear tunable transconductor for continuous-time tunable Gm-C filters. In Proceedings of the 2008 IEEE International Symposium on Circuits and Systems (ISCAS), Seattle, WA, USA, 18–21 May 2008; pp. 912–915. [Google Scholar]

- Carrillo, J.M.; Duque-Carrillo, J.F.; Torelli, G. 1-V continuously tunable CMOS bulk-driven transconductor for Gm-C filters. In Proceedings of the 2008 IEEE International Symposium on Circuits and Systems, Seattle, WA, USA, 18–21 May 2008; pp. 896–899. [Google Scholar]

- Veeravalli, A.; Sanchez-Sinencio, E.; Silva-Martinez, J. Transconductance amplifier structures with very small transconductances: A comparative design approach. IEEE J.-Solid-State Circuits 2002, 37, 770–775. [Google Scholar] [CrossRef]

- Mourabit, A.; Lu, G.N.; Pittet, P. Wide-linear-range subthreshold OTA for low-power, low-Voltage, and low-frequency applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2005, 52, 1481–1488. [Google Scholar] [CrossRef]

- Agostinho, P.R.; Haddad, S.A.P.; De Lima, J.A.; Serdijn, W.A. An ultra low power CMOS pA/V transconductor and its application to wavelet filters. Analog. Integr. Circuits Signal Process. 2008, 57, 19–27. [Google Scholar] [CrossRef]

- Jendernalik, J.; Szczepanski, S.; Koziel, S. Highly linear CMOS triode transconductor for VHF applications. IET Circuits Devices Syst. 2012, 6, 9–18. [Google Scholar] [CrossRef]

- Huang, Y.; Drakakis, E.M.; Toumazou, C. A 30pA/V–25μA/V linear CMOS channel-length-modulation OTA. Microelectron. J. 2009, 40, 1458–1465. [Google Scholar] [CrossRef]

- Jakusz, J.; Jendernalik, W.; Blakiewicz, G.; Kłosowski, M.; Szczepański, S. A 1-nS 1-V sub-1-μW linear CMOS OTA with rail-to-rail input for Hz-band sensory interfaces. Sensors 2020, 20, 3303. [Google Scholar] [CrossRef]

- Soares, C.F.; de Moraes, G.S.; Petraglia, A. A low-transconductance OTA with improved linearity suitable for low-frequency Gm-C filters. Microelectron. J. 2014, 45, 1499–1507. [Google Scholar] [CrossRef]

- Wong, A.; Pun, K.P.; Zhang, Y.T.; Hung, K. A near-infrared heart rate measurement IC with very low cutoff frequency using current steering technique. IEEE Trans. Circuits Syst. I Regul. Pap. 2005, 52, 2642–2647. [Google Scholar] [CrossRef]

- Cinco-Izquierdo, O.J.; de la Cruz-Blas, C.A.; Sanz-Pascual, M.T. High-linearity tunable low-Gm transconductor based on bootstrapping. IEEE Trans. Circuits Syst. II Express Briefs 2022, 69, 259–263. [Google Scholar]

- Cotrim, E.D.C.; Ferreira, L.H.d.C. An ultra-low-power CMOS symmetrical OTA for low-frequency Gm-C applications. Analog. Integr. Circuits Signal Process. 2012, 71, 275–282. [Google Scholar] [CrossRef]

- Colletta, G.D.; Ferreira, L.H.C.; Pimenta, T.C. A 0.25-V 22-nS symmetrical bulk-driven OTA for low-frequency Gm-C applications in 130-nm digital CMOS process. Analog. Integr. Circuits Signal Process. 2014, 81, 377–383. [Google Scholar] [CrossRef]

- Khateb, F.; Kulej, T.; Akbari, M.; Steffan, P. 0.3-V bulk-driven nanopower OTA-C integrator in 0.18 μm CMOS. Circuits Syst. Signal Process. 2019, 38, 1333–1341. [Google Scholar] [CrossRef]

- Khateb, F.; Kulej, T.; Veldandi, H.; Jaikla, W. Multiple-input bulk-driven quasi-floating-gate MOS transistor for low-voltage low-power integrated circuits. AEU—Int. J. Electron. Commun. 2019, 100, 32–38. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).