Design of a Sigma-Delta Analog-to-Digital Converter Cascade Decimation Filter

Abstract

1. Introduction

2. Digital Decimation Filter Architecture

2.1. CIC Decimation Filter

- (1)

- The decimation factor of the former stage should be higher than that of the latter stage to reduce the resource and power consumption of the IZ filter, which has a more complex structure.

- (2)

- Increasing the CIC order can improve the anti-aliasing characteristics of the CIC filter.

- (3)

- According to Formula (9), the obtained decimation multiple of the latter stage CIC should be more than three.

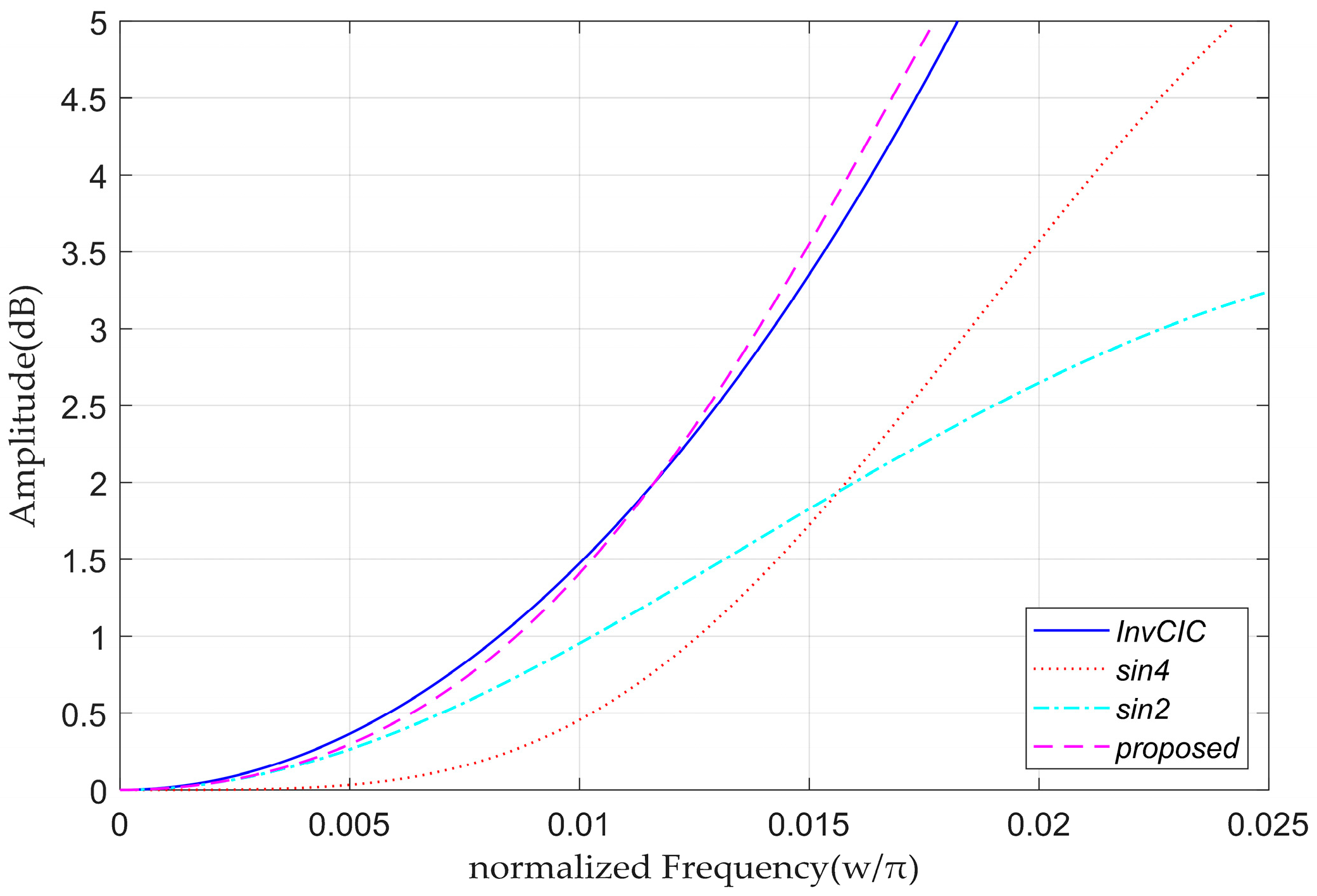

2.2. Compensation Filter

2.3. Coefficient Optimization of CIC and Compensation Filter

- (1)

- Specify the scope and objective function of the algorithm. The initial particle is created in the range and given the initial particle size, position (solution of the objective function), and initial velocity (iteration step size). In order to better simulate the natural environment, the position and initial velocity are assigned randomly. Among these, the maximum that can be achieved by the initial velocity is the difference between the upper and lower boundary values of the position.

- (2)

- Calculate the objective function value of each particle at the initial position and store it as the individual historical optimal value. At the same time, the initial position of the particle is stored as the individual historical optimal solution.

- (3)

- Each particle shares the individual historical optimal value and the individual historical optimal solution to the entire particle swarm. The speed and position of each particle after receiving this information are updated.

- (4)

- Calculate the objective function value of each particle in the updated position, compare it with the previous position, and update the individual history optimal value and individual history optimal solution.

- (5)

- Update the group’s historical optimal value and the group’s historical optimal solution.

- (6)

- Continue to iterate until the end condition of the algorithm is met, and the optimal solution is output.

2.4. Half-Band Filter

3. Simulation, FPGA Verification, and ASIC Design

3.1. Simulation

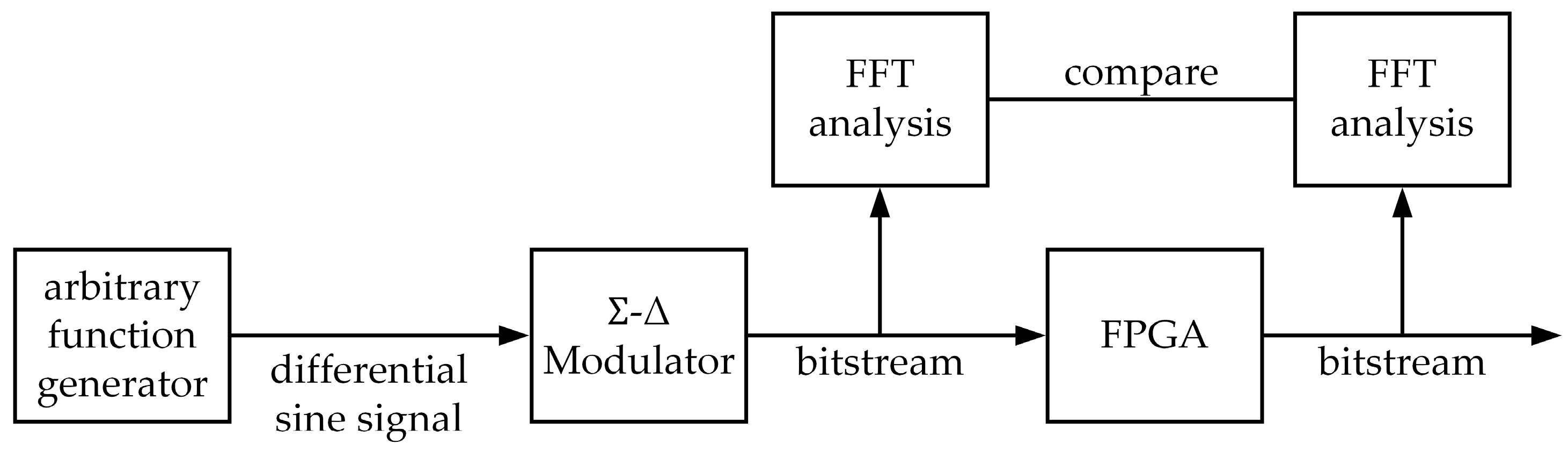

3.2. FPGA Verification

3.3. ASIC Design

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Liu, L.; Li, D.; Ye, Y.; Chen, L.; Wang, Z. A 95dB SNDR audio ΔΣ modulator in 65 nm CMOS. In Proceedings of the 2011 IEEE Custom Integrated Circuits Conference (CICC), San Jose, CA, USA, 19–21 September 2011; pp. 1–4. [Google Scholar]

- Zhu, L.; Tong, X. A 1-V 92.28-dB DR Sigma-Delta Modulator for Sensing Applications. In Proceedings of the 2022 7th International Conference on Integrated Circuits and Microsystems (ICICM), Xi’an, China, 28–31 October 2022; pp. 657–661. [Google Scholar]

- Qian, Z.B.; Yan, W. Low Resource Consumption Design of Digital Decimation Filter. Acta Sci. Nat. Univ. Pekin. 2018, 54, 315–319. [Google Scholar]

- Luo, L.; Li, X.Y.; Zeng, J.Q.; Xu, Z.X. Design of 24-bit Delta-Sigma A/D digital decimation filter. J. Beijing Jiaotong Univ. 2016, 40, 45–49. [Google Scholar]

- Li, D.; Chen, Z.; Liu, X.; Shen, Z.; Xing, Y.; Wan, P. Digital Decimation Filter Design for a 3rd-Order Sigma-Delta Modulator with Achieving 129 dB SNR. In Proceedings of the 2021 IEEE 15th International Conference on Anti-counterfeiting, Security, and Identification (ASID), Xiamen, China, 29–31 October 2021; pp. 187–190. [Google Scholar]

- Fernandez-Vazquez, A.; Dolecek, G.J. Passband and stopband CIC improvement based on efficient IIR filter structure. In Proceedings of the 2010 53rd IEEE International Midwest Symposium on Circuits and Systems, Seattle, WA, USA, 1–4 August 2010; pp. 765–768. [Google Scholar]

- Molnar, G.; Dudarin, A.; Vucic, M. Minimax design of multiplierless sharpened CIC filters based on interval analysis. In Proceedings of the 2016 39th International Convention on Information and Communication Technology, Electronics and Microelectronics (MIPRO), Opatija, Croatia, 30 May–3 June 2016; pp. 94–98. [Google Scholar]

- Molnar, G.; Dudarin, A.; Vucic, M. Design and multiplierless realization of maximally flat sharpened-CIC compensators. IEEE Trans. Circuits Syst. II Express Briefs 2017, 65, 51–55. [Google Scholar] [CrossRef]

- Gautam, D.; Khare, K.; Shrivastava, B.P. A novel approach for optimal design of sample rate conversion filter using linear optimization technique. IEEE Access 2021, 9, 44436–44441. [Google Scholar] [CrossRef]

- Dolecek, G.J.; Dolecek, L. Exploiting features of symmetric polynomials for improved comb filter design. In Proceedings of the 2016 Signal Processing: Algorithms, Architectures, Arrangements, and Applications (SPA), Poznan, Poland, 21–23 September 2016; pp. 26–29. [Google Scholar]

- Dolecek, G.J. Design of comb decimation filter with improved aliasing rejection and compensated passband. In Proceedings of the 2021 IEEE 32nd International Conference on Microelectronics (MIEL), Nis, Serbia, 12–14 September 2021; pp. 255–258. [Google Scholar]

- Jovanovic Dolecek, G.; Baez, R.G.; Molina Salgado, G.; De La Rosa, J.M. Novel multiplierless wideband comb compensator with high compensation capability. Circuits Syst. Signal Process. 2017, 36, 2031–2049. [Google Scholar] [CrossRef]

- Xu, L.; Yang, W.; Tian, H. Design of wideband CIC compensator based on particle swarm optimization. Circuits Syst. Signal Process. 2019, 38, 1833–1846. [Google Scholar] [CrossRef]

- Neeraja, P.; Bindiya, T.; Raghu, C. Low Power Implementation of Compensated and Sharpened CIC Decimation Filter. In Proceedings of the 2022 IEEE 9th Uttar Pradesh Section International Conference on Electrical, Electronics and Computer Engineering (UPCON), Prayagraj, India, 2–4 December 2022; pp. 1–6. [Google Scholar]

- Cao, J.; Liu, Y.; Jiang, B.; Liu, X. The design and implementation of sigma delta ADC digital decimation filter. In Proceedings of the 2013 International Conference on Information Science and Cloud Computing Companion, Guangzhou, China, 7–8 December 2013; pp. 335–338. [Google Scholar]

- Konvalina, J.; Matache, V. Palindrome-polynomials with roots on the unit circle. Comptes Rendus Math. 2004, 26, 39. [Google Scholar]

- Botta, V. Some results on zeros of palindromic and perturbed polynomials of even degree. Proceeding Ser. Braz. Soc. Comput. Appl. Math. 2015, 3. [Google Scholar] [CrossRef]

- Nadar, N.; Mehta, M.; Bhat, K.; Mendes, J.; Chaudhari, R. Hardware implementation of pipelined FFT using polyphase decomposition. In Proceedings of the 2021 International Conference on Recent Trends on Electronics, Information, Communication & Technology (RTEICT), Bangalore, India, 27–28 August 2021; pp. 339–343. [Google Scholar]

- Dolecek, G.J. Improving comb alias rejection by exploiting certain class of palindromic polynomials. In Proceedings of the 2017 European Conference on Circuit Theory and Design (ECCTD), Catania, Italy, 4–6 September 2017; pp. 1–4. [Google Scholar]

- Kennedy, J.; Eberhart, R. Particle swarm optimization. In Proceedings of the Proceedings of ICNN’95-international conference on neural networks, Perth, WA, Australia, 27 November–1 December 1995; pp. 1942–1948. [Google Scholar]

- Mezura-Montes, E.; Coello, C.A.C. Constraint-handling in nature-inspired numerical optimization: Past, present and future. Swarm Evol. Comput. 2011, 1, 173–194. [Google Scholar] [CrossRef]

- Gad, A.G. Particle swarm optimization algorithm and its applications: A systematic review. Arch. Comput. Methods Eng. 2022, 29, 2531–2561. [Google Scholar] [CrossRef]

- Dudarin, A.; Molnar, G.; Vucic, M. Optimum multiplierless sharpened cascaded-integrator-comb filters. Digit. Signal Process. 2022, 127, 103564. [Google Scholar] [CrossRef]

- Zahradnik, P.; Vlcek, M. Equiripple approximation of half-band FIR filters. IEEE Trans. Circuits Syst. II Express Briefs 2009, 56, 941–945. [Google Scholar] [CrossRef]

- Ifeachor, E.C.; Jervis, B.W. Digital Signal Processing: A Practical Approach; Pearson Education: London, UK, 2002. [Google Scholar]

- IEEE Std 1241-2023; IEEE Standard for Terminology and Test Methods for Analog-to-Digital Converters. Available online: https://ieeexplore.ieee.org/document/10269815 (accessed on 6 October 2023).

- Zhong, Y.Q.; Tian, Y.; Li, J.X.; Liu, M.; Zhang, X.; Meng, Z.; Chen, H.; Yan, Y. Design of Low cost ∑△ ADC digital decimation filter. Microelectron. Comput. 2021, 38, 59–65. [Google Scholar]

| Raw Coefficients | SPT Solution | SPT Coefficients |

|---|---|---|

| A1 = 1.5265 | 1 + 2−1 + 2−6 + 2−7 + 2−8 | A1s = 1.52734375 |

| A2 = 1.1252 | 1 + 2−3 | A2s = 1.125 |

| Ref. | [12] | [8] | [14] | This Work |

|---|---|---|---|---|

| Decimation factor | 32 | 32 | 32 | 32 |

| Minimum attenuation in dB | 41.8 | 82.5 | 79 | 93.4 |

| Maximum passband ripple in dB | 0.067 | 0.09 | - | 0.0469 |

| Modules after Vivado Synthesis | Slice LUTs | Slice Registers |

|---|---|---|

| Top | 3749 out of 20,800 | 2497 out of 41,600 |

| Clock module | 6 out of 20,800 | 7 out of 41,600 |

| CIC module | 1660 out of 20,800 | 968 out of 41,600 |

| 4th-order compensation module | 540 out of 20,800 | 120 out of 41,600 |

| 2nd-order compensation module | 128 out of 20,800 | 63 out of 41,600 |

| Half-band module | 1415 out of 20,800 | 1339 out of 41,600 |

| Input signal frequency in Hz 1 | 114 | 781 | 1068 | 2298 | 4730 | 10,223 |

| Modulator output SNR in dB | 91.67 | 91.70 | 91.44 | 91.45 | 91.21 | 90.68 |

| FPGA output SNR in dB | 91.64 | 91.66 | 91.41 | 91.43 | 91.19 | 90.65 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ye, M.; Liu, Z.; Zhao, Y. Design of a Sigma-Delta Analog-to-Digital Converter Cascade Decimation Filter. Electronics 2024, 13, 2090. https://doi.org/10.3390/electronics13112090

Ye M, Liu Z, Zhao Y. Design of a Sigma-Delta Analog-to-Digital Converter Cascade Decimation Filter. Electronics. 2024; 13(11):2090. https://doi.org/10.3390/electronics13112090

Chicago/Turabian StyleYe, Mao, Zitong Liu, and Yiqiang Zhao. 2024. "Design of a Sigma-Delta Analog-to-Digital Converter Cascade Decimation Filter" Electronics 13, no. 11: 2090. https://doi.org/10.3390/electronics13112090

APA StyleYe, M., Liu, Z., & Zhao, Y. (2024). Design of a Sigma-Delta Analog-to-Digital Converter Cascade Decimation Filter. Electronics, 13(11), 2090. https://doi.org/10.3390/electronics13112090