Electron-Induced Single-Event Effect in 28 nm SRAM-Based FPGA

Abstract

1. Introduction

2. Experimental Details

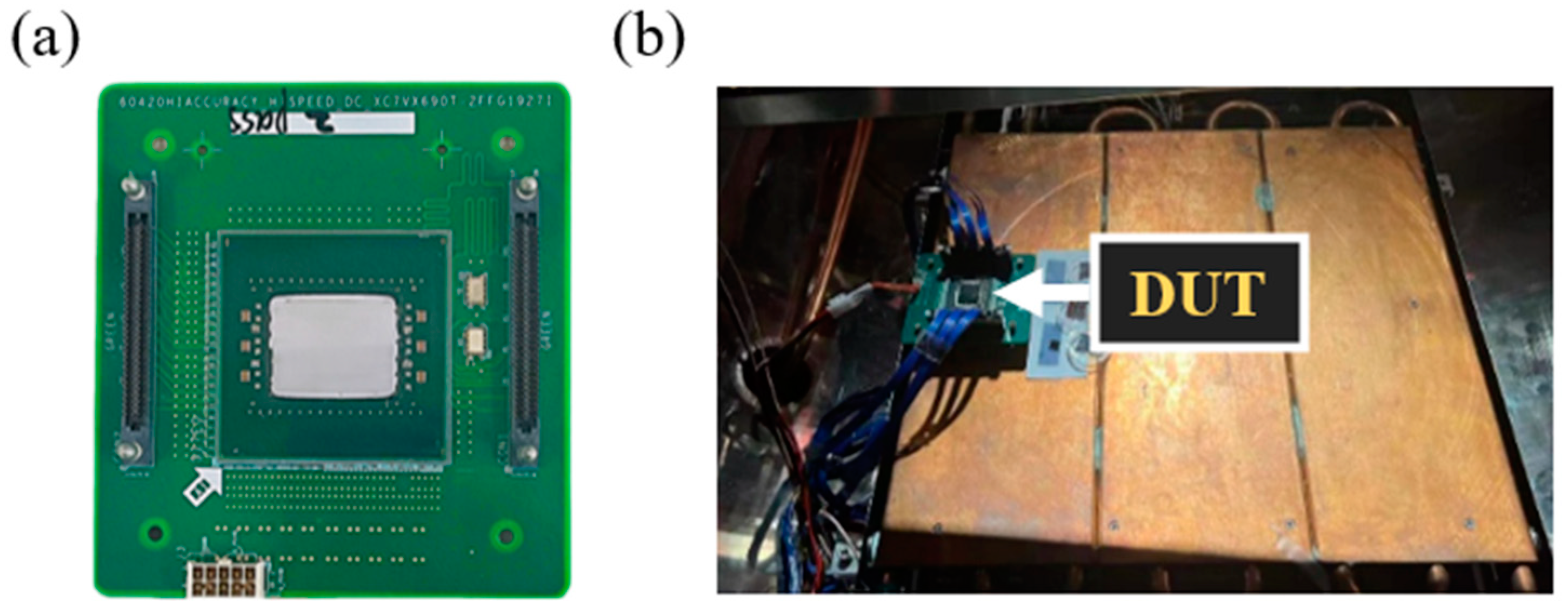

2.1. Device under Test

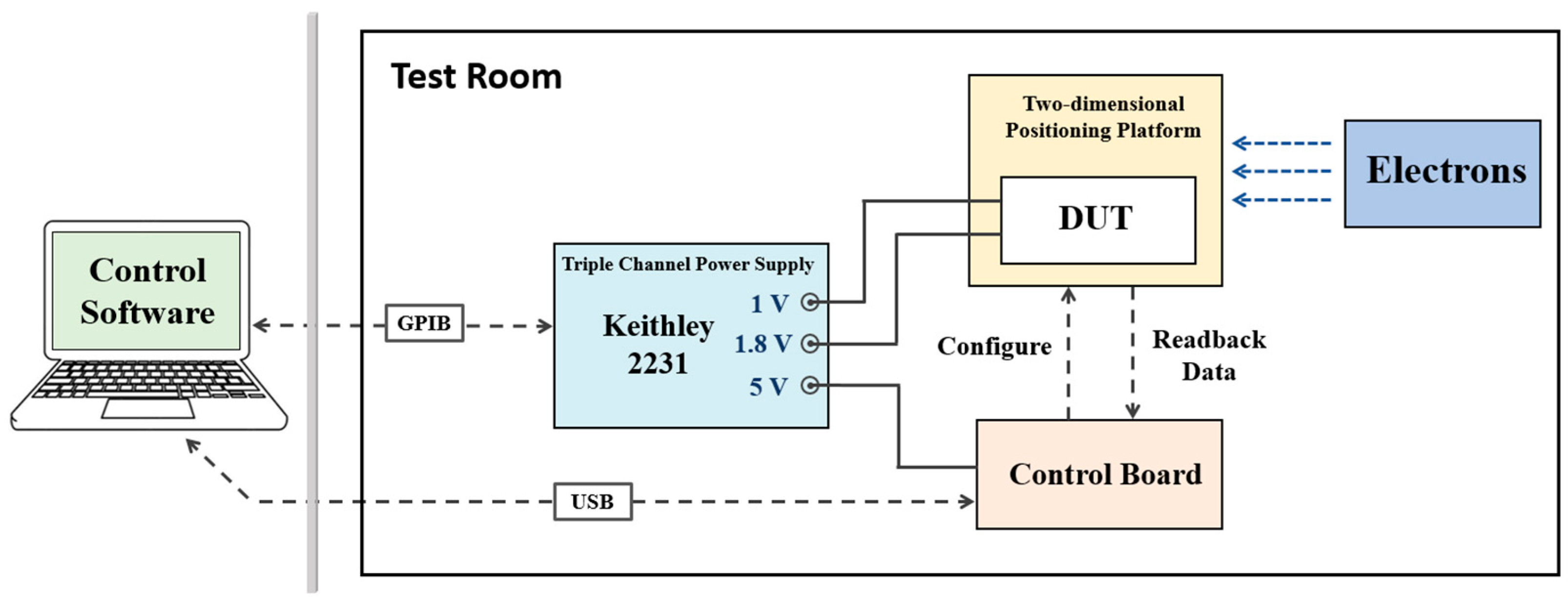

2.2. Experimental Setup

3. Experimental Results

4. Simulation and Discussion

4.1. Monte Carlo Simulations

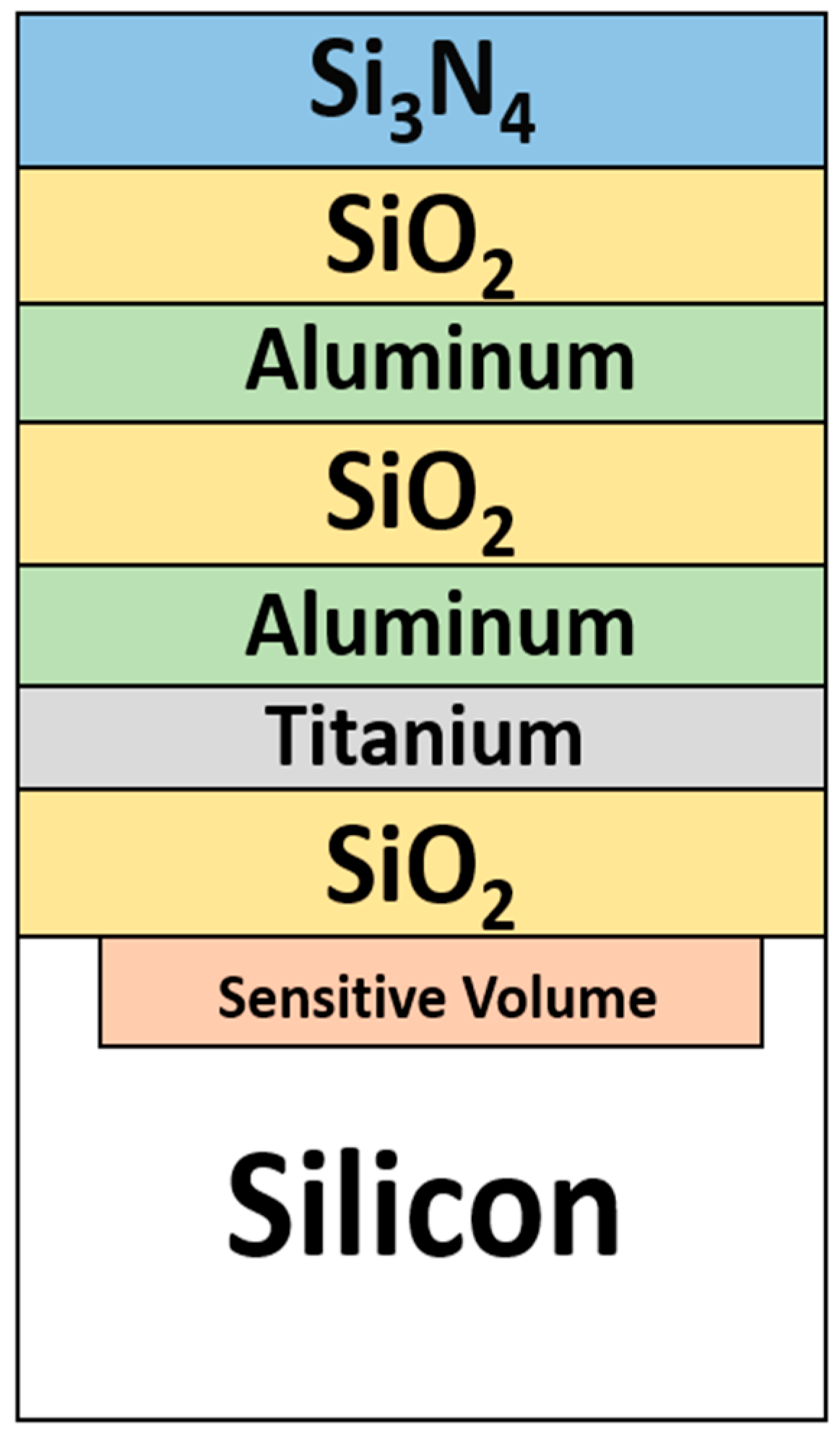

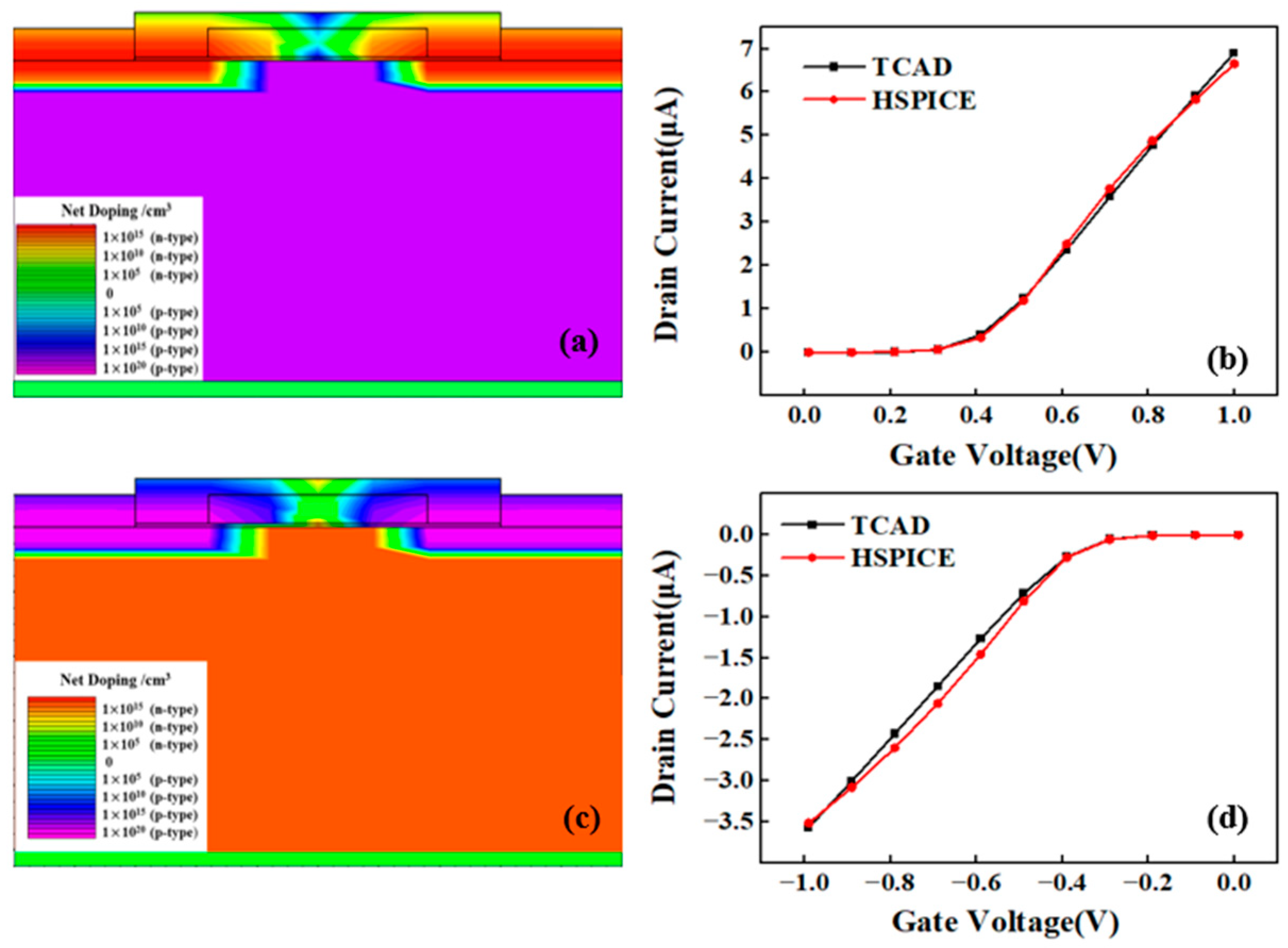

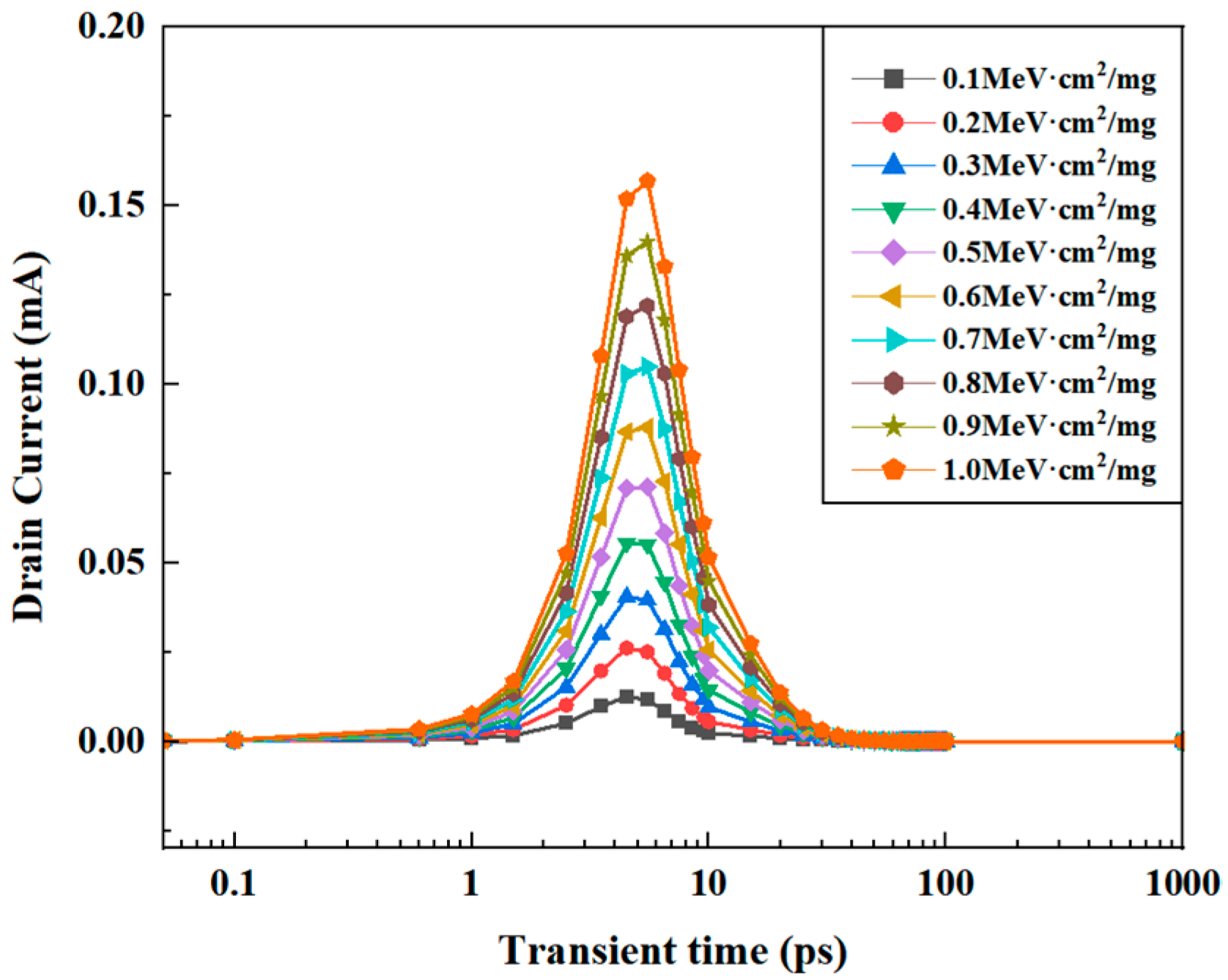

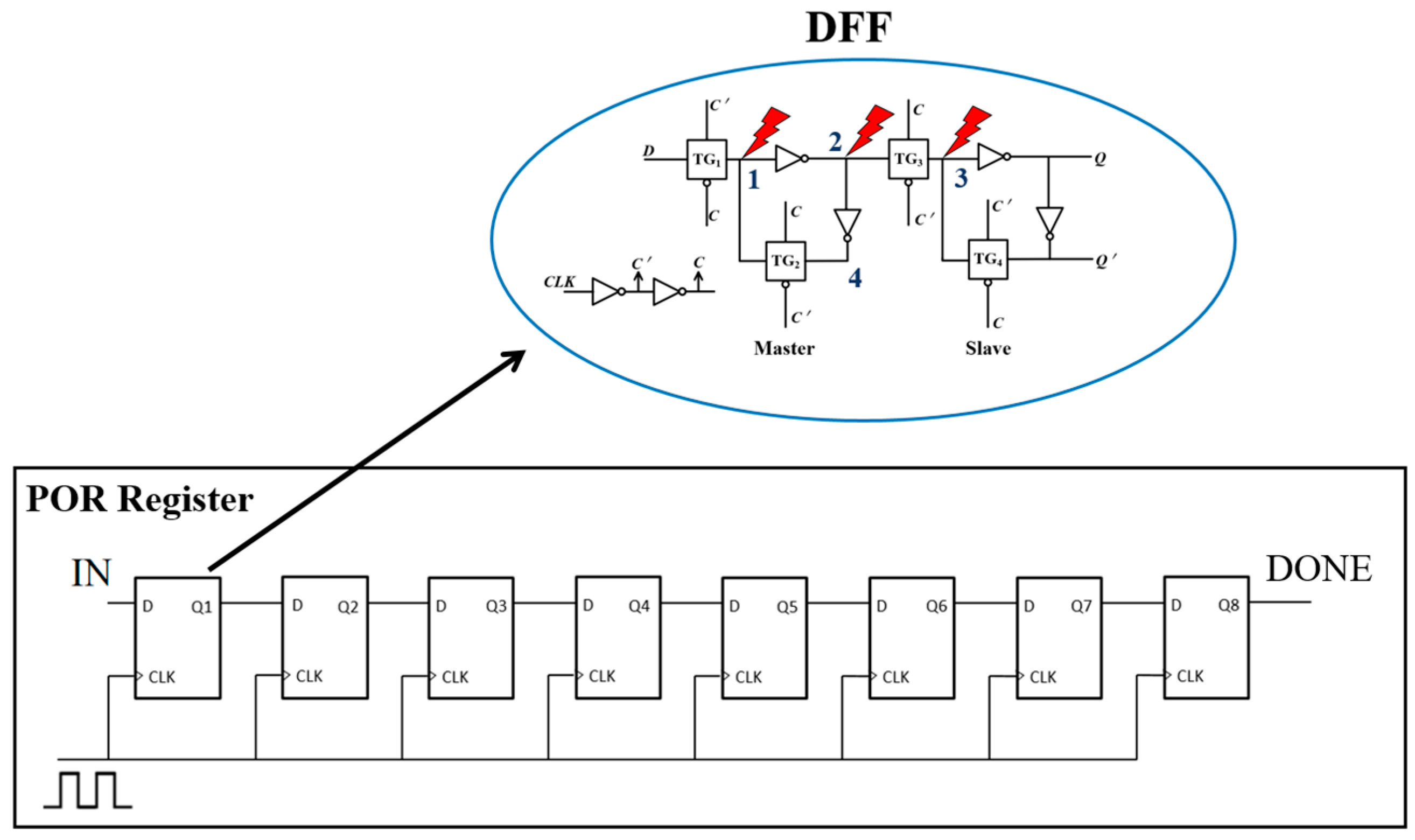

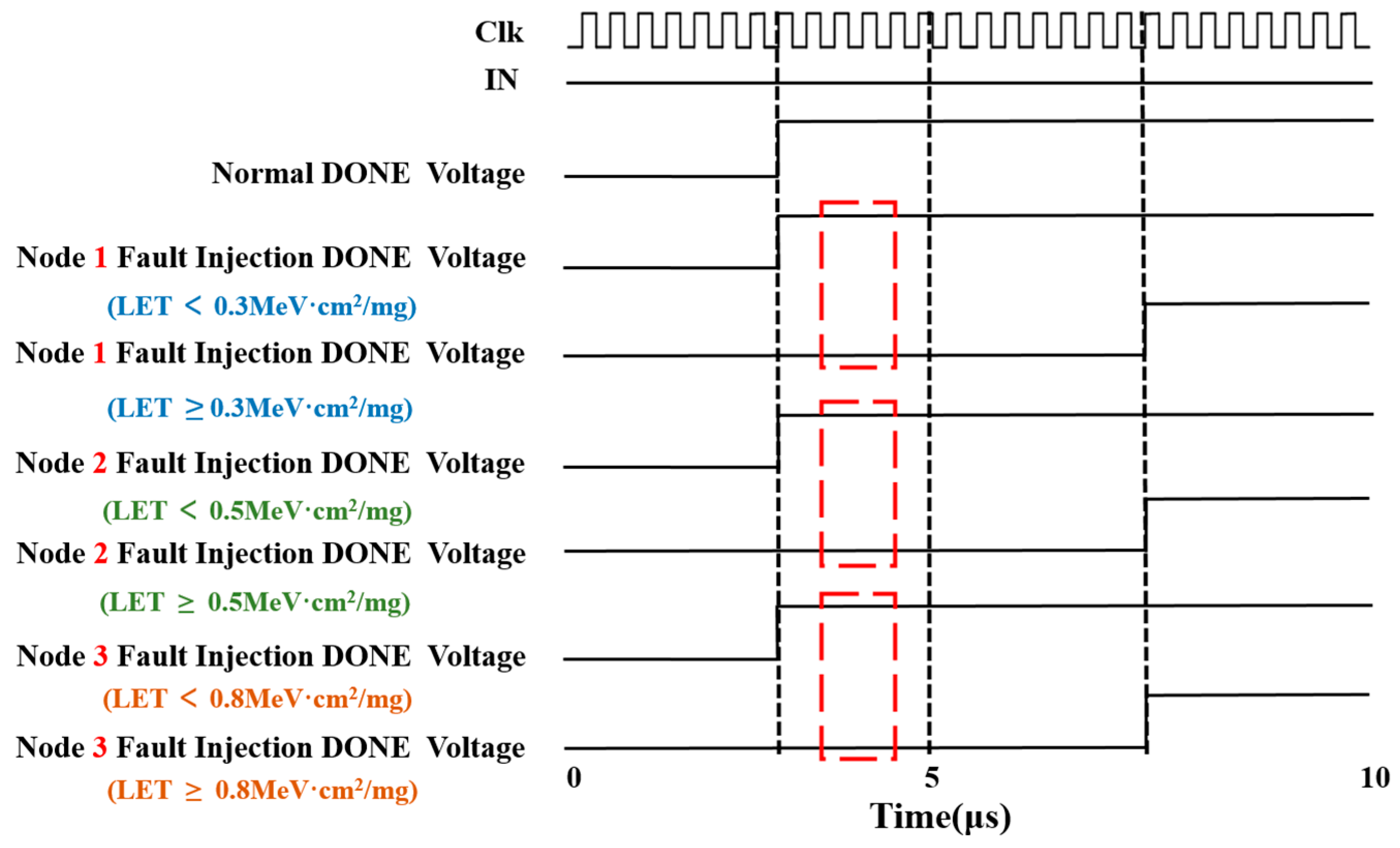

4.2. TCAD and Spice Simulations

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Biswas, S.; Jang, H.; Lee, Y.; Choi, H.; Kim, Y.; Kim, H.; Zhu, Y. Recent advancements in implantable neural links based on organic synaptic transistors. Exploration 2014, 4, 20220150. [Google Scholar] [CrossRef]

- Dodd, P.E.; Sexton, F.W. Critical Charge Concepts for CMOS SRAMs. IEEE Trans. Nucl. Sci. 1995, 42, 1764–1771. [Google Scholar] [CrossRef]

- Barak, J.; Murat, M.; Akkerman, A. SEU due to electrons in silicon devices with nanometric sensitive volumes and small critical charge. Nucl. Instrum. Methods Phys. Res. B 2012, 287, 113–119. [Google Scholar] [CrossRef]

- Koga, R.; Penzin, S.H.; Crawford, K.B.; Crain, W.R. Single Event Functional Interrupt (SEFI) Sensitivity in Microcircuits. In Proceedings of the 1997 European Conference on Radiation and Its Effects on Components and Systems (RADECS), Cannes, France, 15–19 September 1997; pp. 311–318. [Google Scholar]

- Hiemstra, D.M.; Kirischian, V. Single Event Upset Characterization of the Virtex-6 Field Programmable Gate Array Using Proton Irradiation. In Proceedings of the 2012 IEEE Radiation Effects Data Workshop (REDW), Miami, FL, USA, 16–20 July 2012; pp. 1–4. [Google Scholar]

- Tonfat, J.; Lima Kastensmidt, F.; Artola, L.; Hubert, G.; Medina, N.H.; Added, N.; Aguiar, V.A.P.; Aguirre, F.; Macchione, E.L.A.; Silveira, M.A.G. Analyzing the Influence of the Angles of Incidence and Rotation on MBU Events Induced by Low LET Heavy Ions in a 28-nm SRAM-Based FPGA. IEEE Trans. Nucl. Sci. 2017, 64, 2161–2168. [Google Scholar] [CrossRef]

- Maillard, P.; Hart, M.; Barton, J.; Jain, P.; Karp, J. Neutron, 64 MeV Proton, Thermal Neutron and Alpha Single-Event Upset Characterization of Xilinx 20 nm UltraScale Kintex FPGA. In Proceedings of the 2015 IEEE Radiation Effects Data Workshop (REDW), Boston, MA, USA, 13–17 July 2015; pp. 1–5. [Google Scholar]

- Lee, D.S.; Wirthlin, M.; Swift, G.; Le, A.C. Single-Event Characterization of the 28 nm Xilinx Kintex-7 Field-Programmable Gate Array under Heavy Ion Irradiation. In Proceedings of the 2014 IEEE Radiation Effects Data Workshop (REDW), Paris, France, 14–18 July 2014; pp. 1–5. [Google Scholar]

- Wang, Z.; Chen, W.; Yao, Z.; Zhang, F.; Luo, Y.; Tang, X.; Guo, X.; Ding, L.; Peng, C. Proton-Induced Single-Event Effects on 28 nm Kintex-7 FPGA. Microelectron. Reliab. 2020, 107, 113594. [Google Scholar] [CrossRef]

- Quinn, H.; Graham, P.; Krone, J.; Caffrey, M.; Rezgui, S. Radiation-Induced Multi-Bit Upsets in SRAM-Based FPGAs. IEEE Trans. Nucl. Sci. 2005, 52, 2455–2461. [Google Scholar] [CrossRef]

- Garrett, H.B.; Katz, I.; Jun, I.; Kim, W.; Whittlesey, A.C.; Evans, R.W. The Jovian Charging Environment and Its Effects—A Review. IEEE Trans. Plasma Sci. 2012, 40, 144–154. [Google Scholar] [CrossRef]

- King, M.P.; Reed, R.A.; Weller, R.A.; Mendenhall, M.H.; Schrimpf, R.D.; Sierawski, B.D.; Sternberg, A.L.; Narasimham, B.; Wang, J.K.; Pitta, E.; et al. Electron-Induced Single-Event Upsets in Static Random Access Memory. IEEE Trans. Nucl. Sci. 2013, 60, 4122–4129. [Google Scholar] [CrossRef]

- Samaras, A.; Pourrouquet, P.; Sukhaseum, N.; Gouyet, L.; Vandevelde, B.; Chatry, N.; Ecoffet, R.; Bezerra, F.; Lorfevre, E. Experimental Characterization and Simulation of Electron-Induced SEU in 45-nm CMOS Technology. IEEE Trans. Nucl. Sci. 2014, 61, 3055–3060. [Google Scholar] [CrossRef]

- Trippe, J.M.; Reed, R.A.; Austin, R.A.; Sierawski, B.D.; Weller, R.A.; Funkhouser, E.D.; King, M.P.; Narasimham, B.; Bartz, B.; Baumann, R.; et al. Electron-Induced Single Event Upsets in 28 nm and 45 nm Bulk SRAMs. IEEE Trans. Nucl. Sci. 2015, 62, 2709–2716. [Google Scholar] [CrossRef]

- Gadlage, M.J.; Roach, A.H.; Duncan, A.R.; Savage, M.W.; Kay, M.J. Electron-Induced Single-Event Upsets in 45-nm and 28-nm Bulk CMOS SRAM-Based FPGAs Operating at Nominal Voltage. IEEE Trans. Nucl. Sci. 2015, 62, 2717–2724. [Google Scholar] [CrossRef]

- Gadlage, M.J.; Roach, A.H.; Duncan, A.R.; Williams, A.M.; Bossev, D.P.; Kay, M.J. Soft Errors Induced by High-Energy Electrons. IEEE Trans. Device Mater. Reliab. 2017, 17, 157–162. [Google Scholar] [CrossRef]

- Weller, R.A.; Mendenhall, M.H.; Reed, R.A.; Schrimpf, R.D.; Warren, K.M.; Sierawski, B.D.; Massengill, L.W. Monte Carlo Simulation of Single Event Effects. IEEE Trans. Nucl. Sci. 2010, 57, 1726–1746. [Google Scholar] [CrossRef]

- Caron, P.; Inguimbert, C.; Artola, L.; Bezerra, F.; Ecoffet, R. Role of Electron-Induced Coulomb Interactions to the Total SEU Rate during Earth and JUICE Missions. IEEE Trans. Nucl. Sci. 2021, 68, 1607–1612. [Google Scholar] [CrossRef]

- 7Series FPGAs Overview (v2.6.1). Available online: https://docs.amd.com/v/u/en-US/ds180_7Series_Overview.pdf (accessed on 8 September 2020).

- Lv, H.; Zhang, H.; Mei, B.; Li, P.; Mo, R.; Sun, Y. Research of the upset effect on nanodevices caused by high energy electron irradiation. Spacecr. Environ. Eng. 2021, 38, 358–363. [Google Scholar] [CrossRef]

- Caron, P.; Inguimbert, C.; Artola, L.; Chatry, N.; Sukhaseum, N.; Ecoffet, R.; Bezerra, F. Physical Mechanisms Inducing Electron Single-Event Upset. IEEE Trans. Nucl. Sci. 2018, 65, 1759–1767. [Google Scholar] [CrossRef]

- Inguimbert, C.; Ecoffet, R.; Falguere, D. Electron Induced SEUs: Microdosimetry in Nanometric Volumes. IEEE Trans. Nucl. Sci. 2015, 62, 2846–2852. [Google Scholar] [CrossRef]

- Zhang, L.; Cao, Y.; Ren, C.; Ma, M.; Lv, H.; Lv, L.; Zheng, X.; Ma, X. Single Event Effect of 28 nm MOSFET Device. Mod. Appl. Phys. 2022, 13, 10606. [Google Scholar] [CrossRef]

- 7Series FPGAs Configuration (v1.17). Available online: https://docs.amd.com/v/u/en-US/ug470_7Series_Config.pdf (accessed on 5 December 2023).

- Artola, L.; Hubert, G.; Ducret, S.; Mekki, J.; Al Youssef, A.; Ricard, N. Impact of D-Flip-Flop Architectures and Designs on Single-Event Upset Induced by Heavy Ions. IEEE Trans. Nucl. Sci. 2018, 65, 1776–1782. [Google Scholar] [CrossRef]

- Vlagkoulis, V.; Sari, A.; Vrachnis, J.; Antonopoulos, G.; Segkos, N.; Psarakis, M.; Tavoularis, A.; Furano, G.; Boatella Polo, C.; Poivey, C.; et al. Single Event Effects Characterization of the Programmable Logic of Xilinx Zynq-7000 FPGA Using Very/Ultra High-Energy Heavy Ions. IEEE Trans. Nucl. Sci. 2021, 68, 36–45. [Google Scholar] [CrossRef]

| Electron Energy (MeV) | Fluence (cm−2) | Recorded SELs | Recorded SEFIs | Recorded SEUs | ||

|---|---|---|---|---|---|---|

| POR | SMAP | CLB | BRAM | |||

| 1 | NONE | PASS | PASS | 0 | 0 | |

| 2 | NONE | PASS | PASS | 0 | 0 | |

| 3 | NONE | FAIL | PASS | 28,671,373 | 1,760,000 | |

| 4 | NONE | PASS | PASS | 0 | 0 | |

| 5 | NONE | PASS | PASS | 0 | 0 | |

| Parameters | Value |

|---|---|

| Channel length/nm | 28 |

| Thickness of gate oxide (SiO2)/nm | 2 |

| Channel doping/cm−3 | 1 × 1016 |

| Source/drain doping/cm−3 | 4 × 1020 |

| Substrate doping/cm−3 | 3 × 1018 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tian, J.; Cao, R.; Liu, Y.; Cai, Y.; Mei, B.; Zhao, L.; Cui, S.; Lv, H.; Xue, Y. Electron-Induced Single-Event Effect in 28 nm SRAM-Based FPGA. Electronics 2024, 13, 2233. https://doi.org/10.3390/electronics13122233

Tian J, Cao R, Liu Y, Cai Y, Mei B, Zhao L, Cui S, Lv H, Xue Y. Electron-Induced Single-Event Effect in 28 nm SRAM-Based FPGA. Electronics. 2024; 13(12):2233. https://doi.org/10.3390/electronics13122233

Chicago/Turabian StyleTian, Jiayu, Rongxing Cao, Yan Liu, Yulong Cai, Bo Mei, Lin Zhao, Shuai Cui, He Lv, and Yuxiong Xue. 2024. "Electron-Induced Single-Event Effect in 28 nm SRAM-Based FPGA" Electronics 13, no. 12: 2233. https://doi.org/10.3390/electronics13122233

APA StyleTian, J., Cao, R., Liu, Y., Cai, Y., Mei, B., Zhao, L., Cui, S., Lv, H., & Xue, Y. (2024). Electron-Induced Single-Event Effect in 28 nm SRAM-Based FPGA. Electronics, 13(12), 2233. https://doi.org/10.3390/electronics13122233