A Wideband Hybrid Envelope Tracking Supply Modulator with Slew-Rate-Enhanced Linear Amplifier

Abstract

:1. Introduction

2. Circuit Design

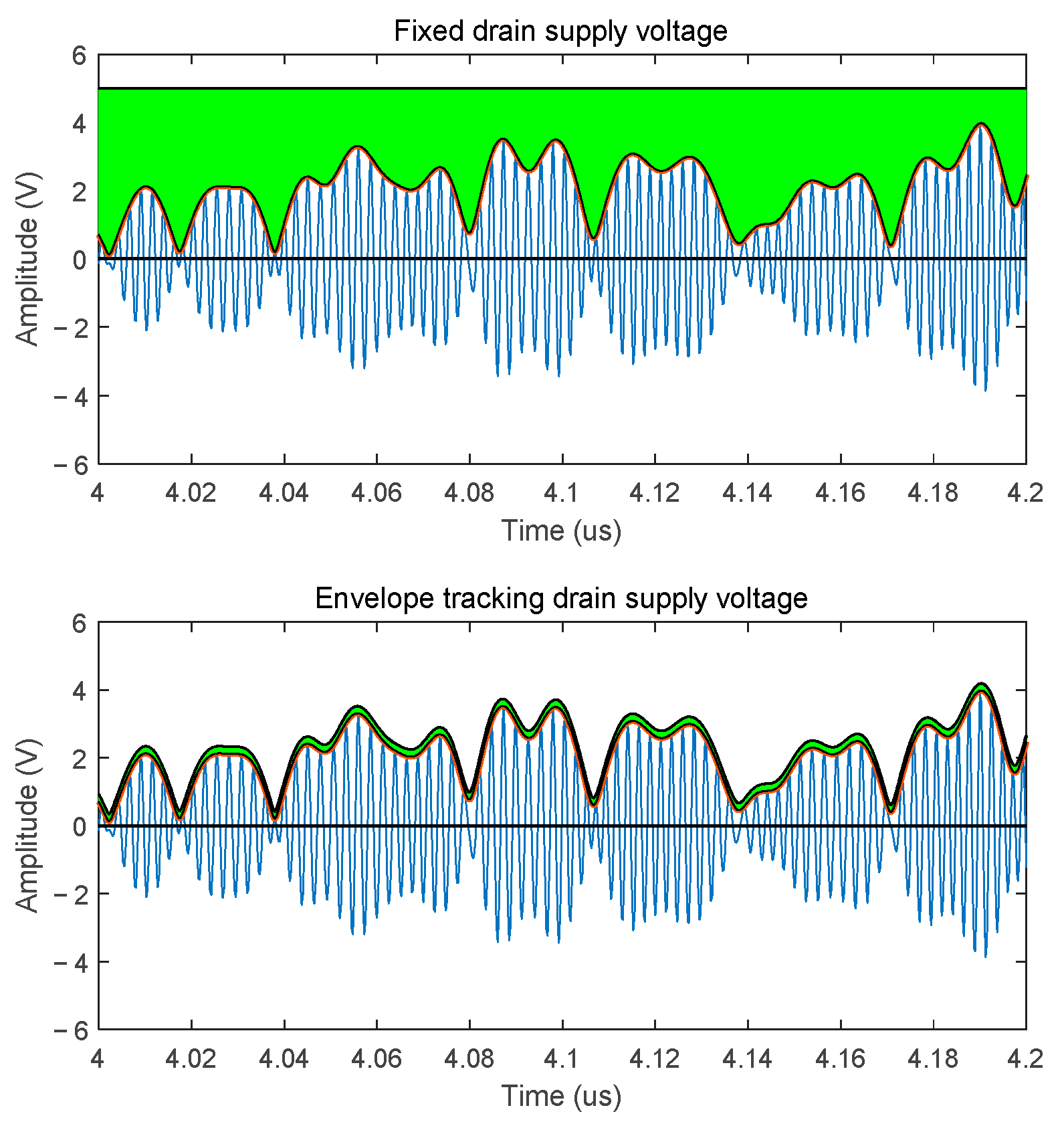

2.1. Principle of the HETSM System

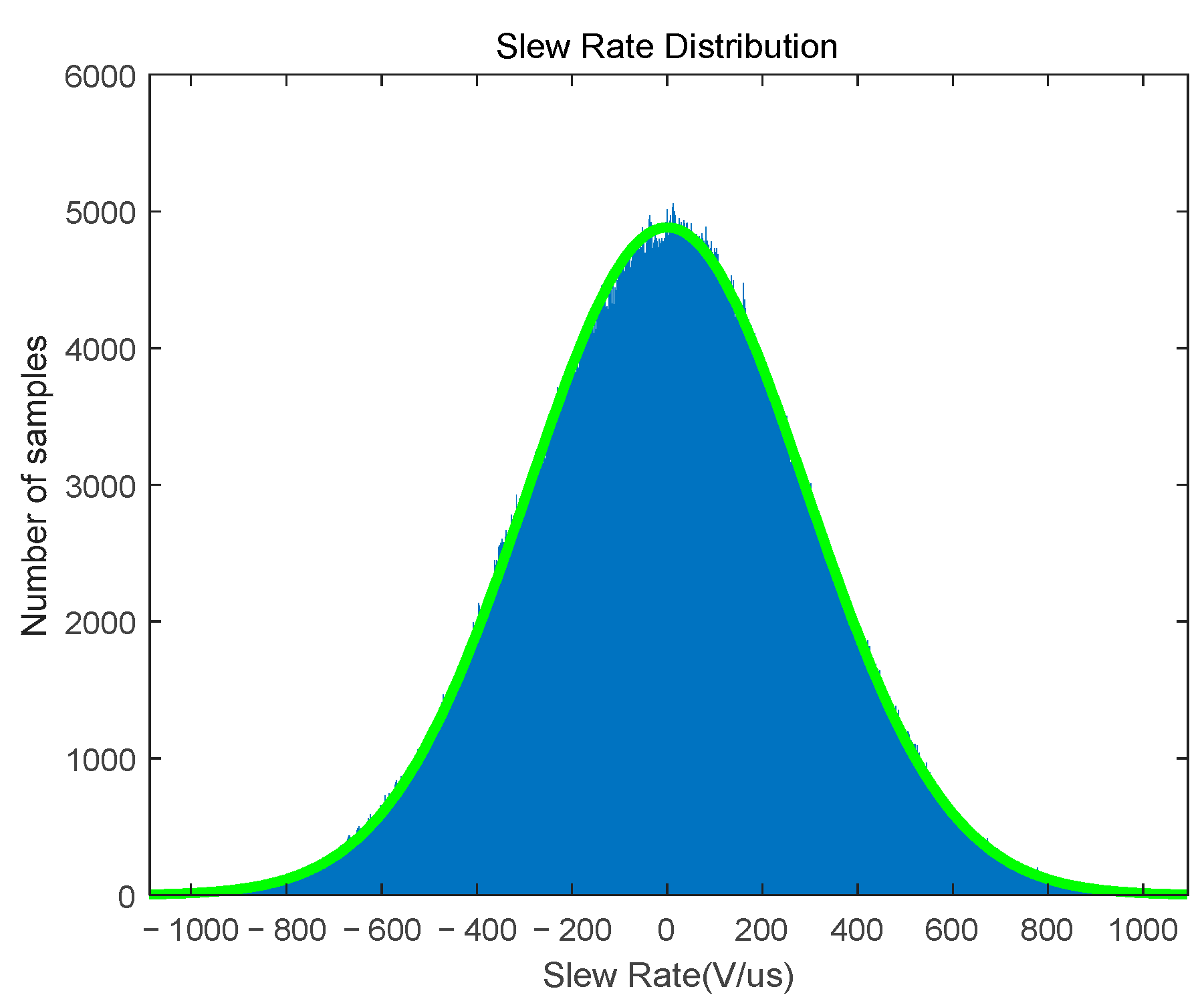

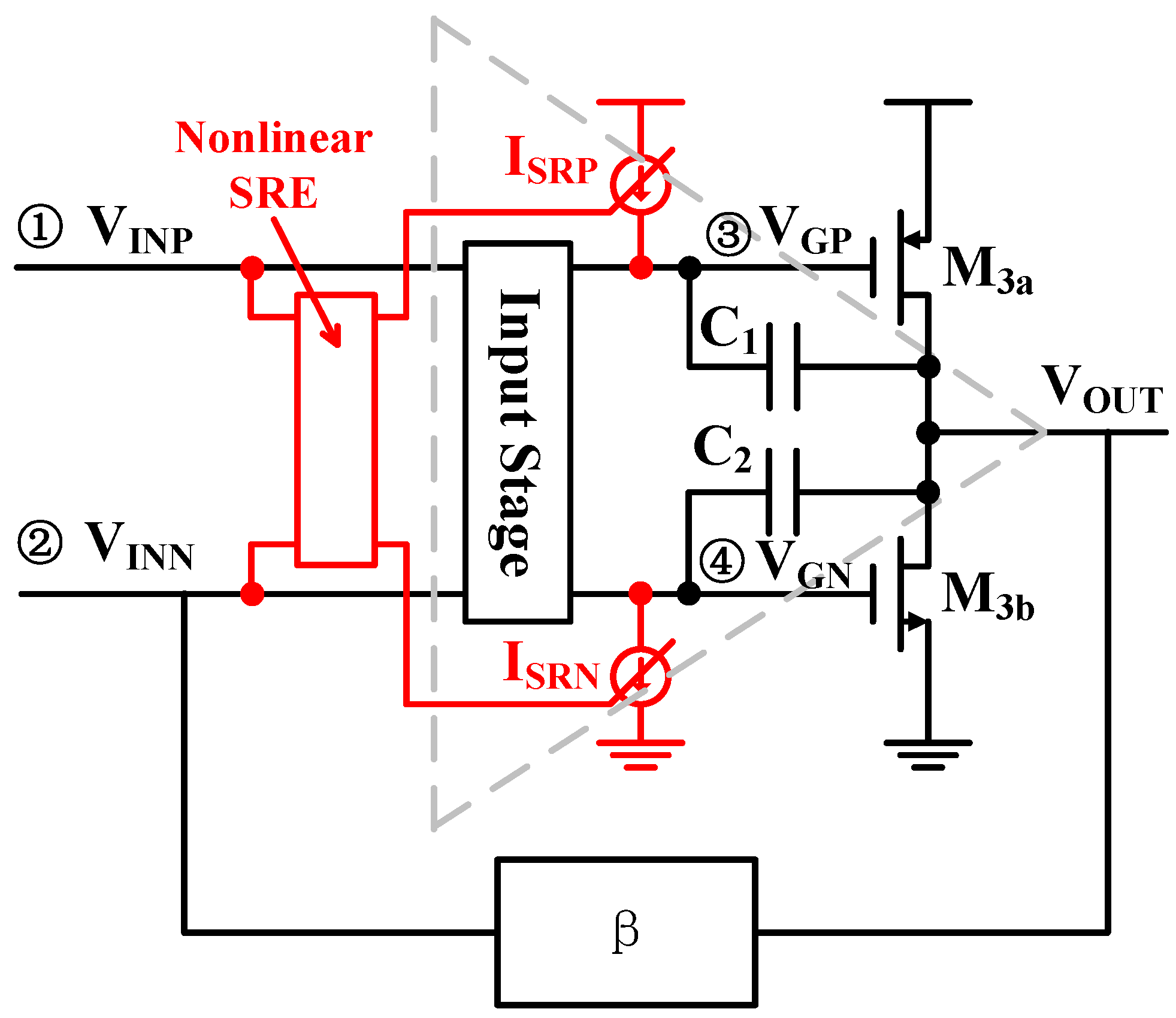

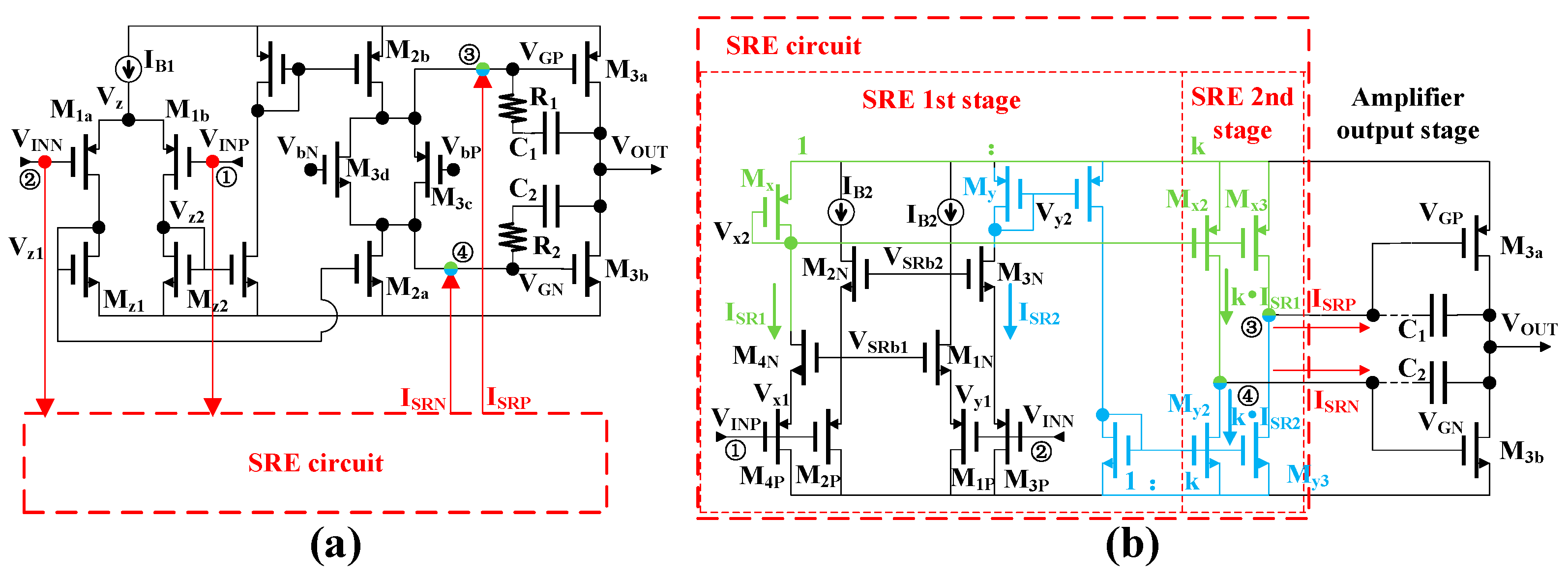

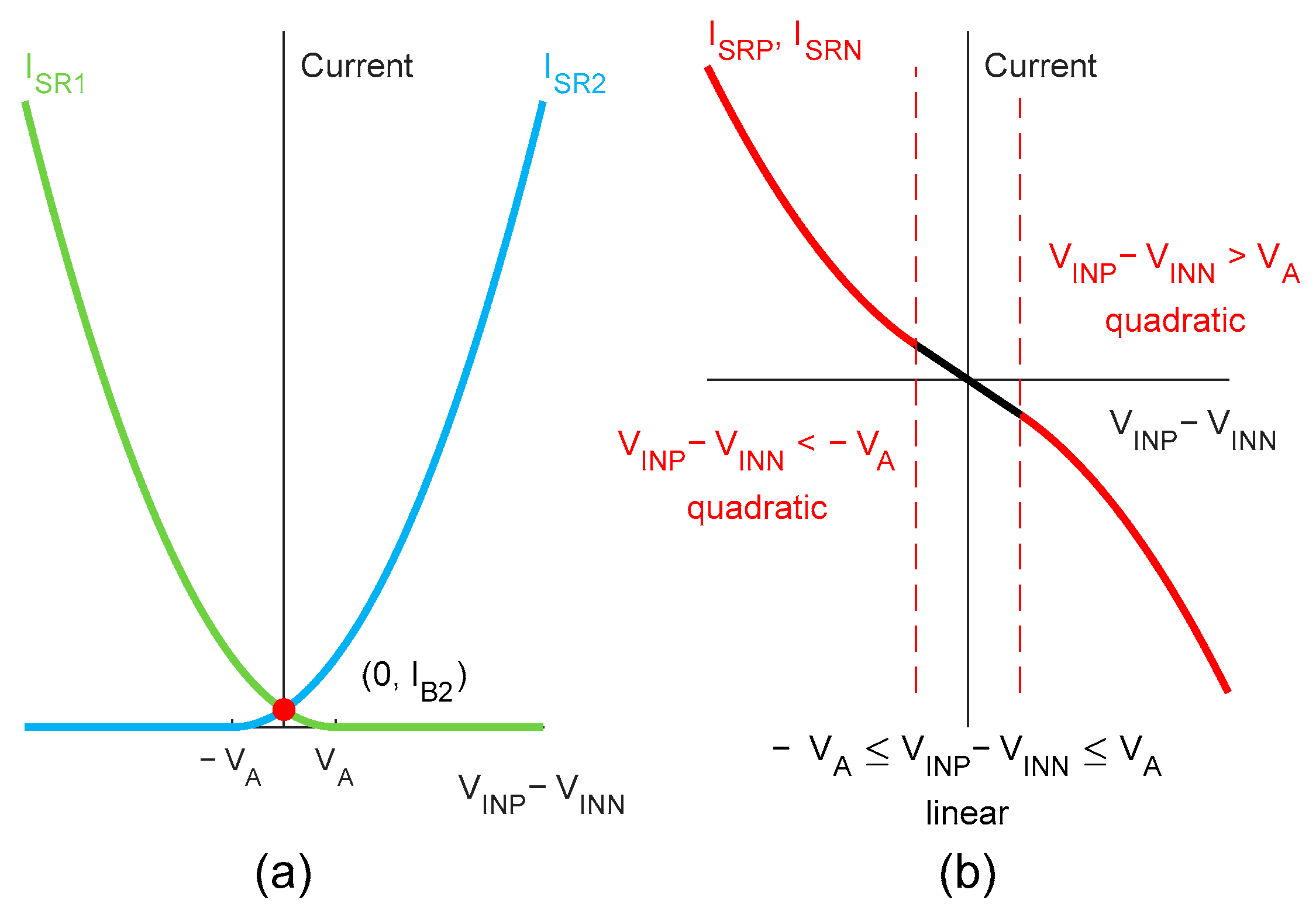

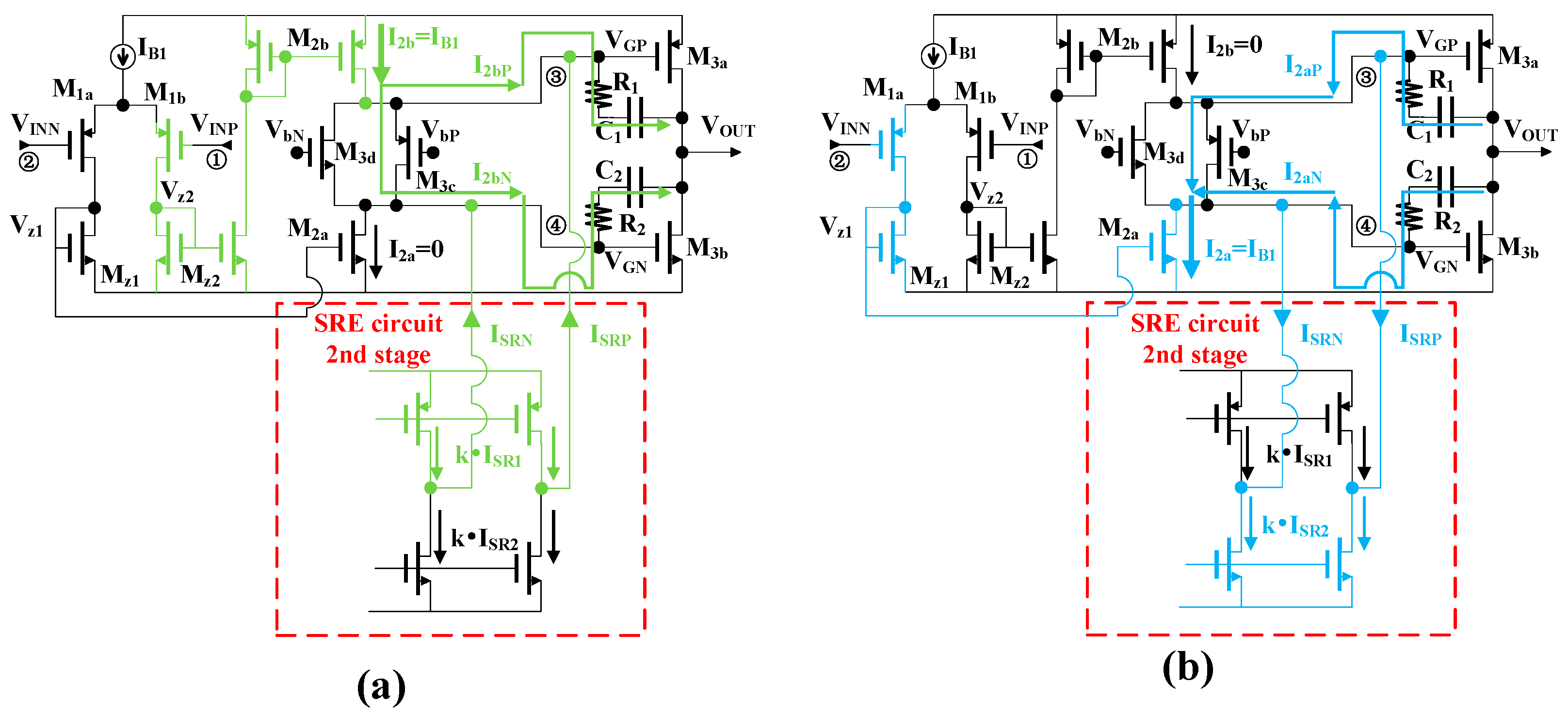

2.2. LA Design with an SRE Structure

2.2.1. The Proposed SRE Circuit

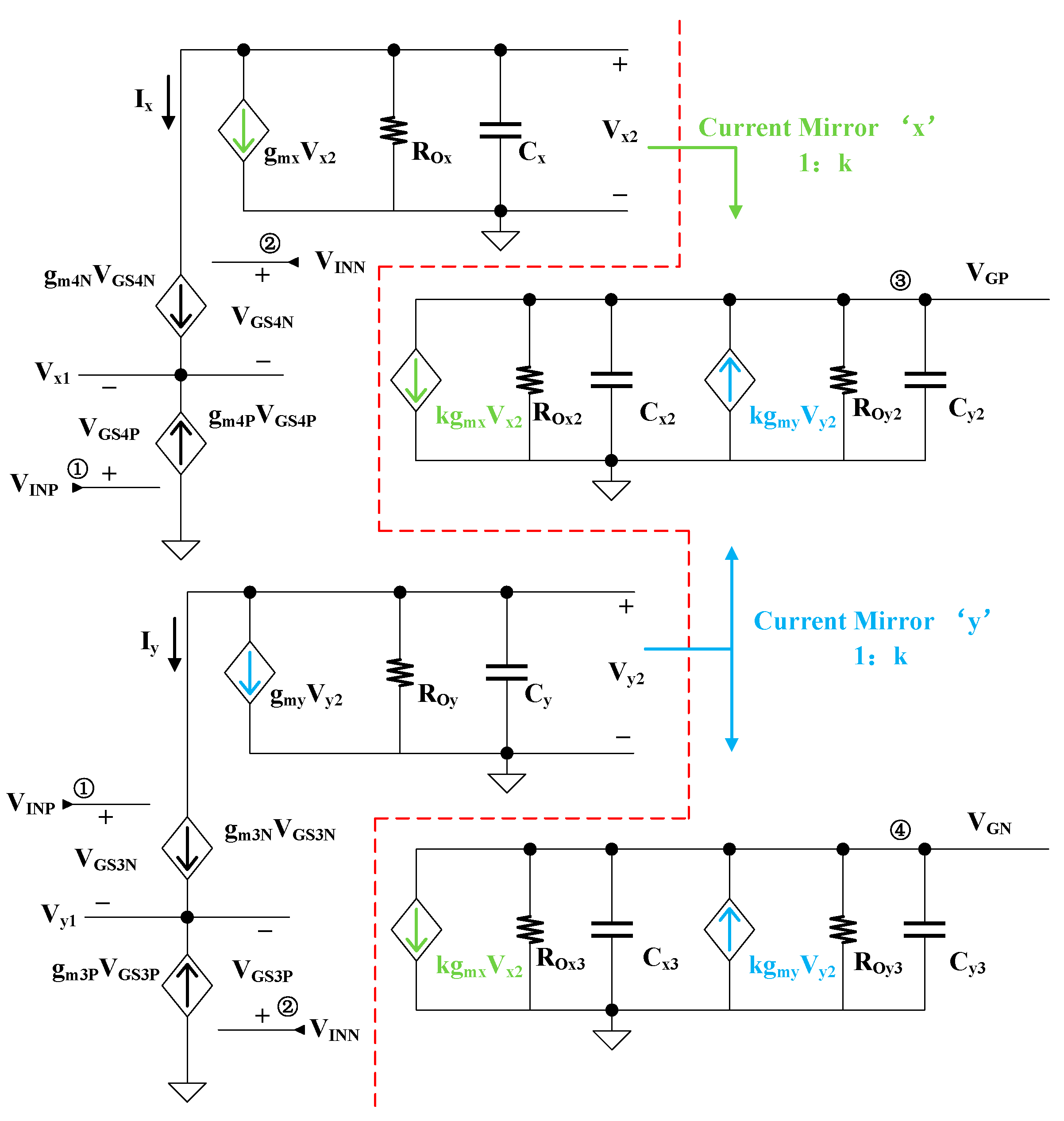

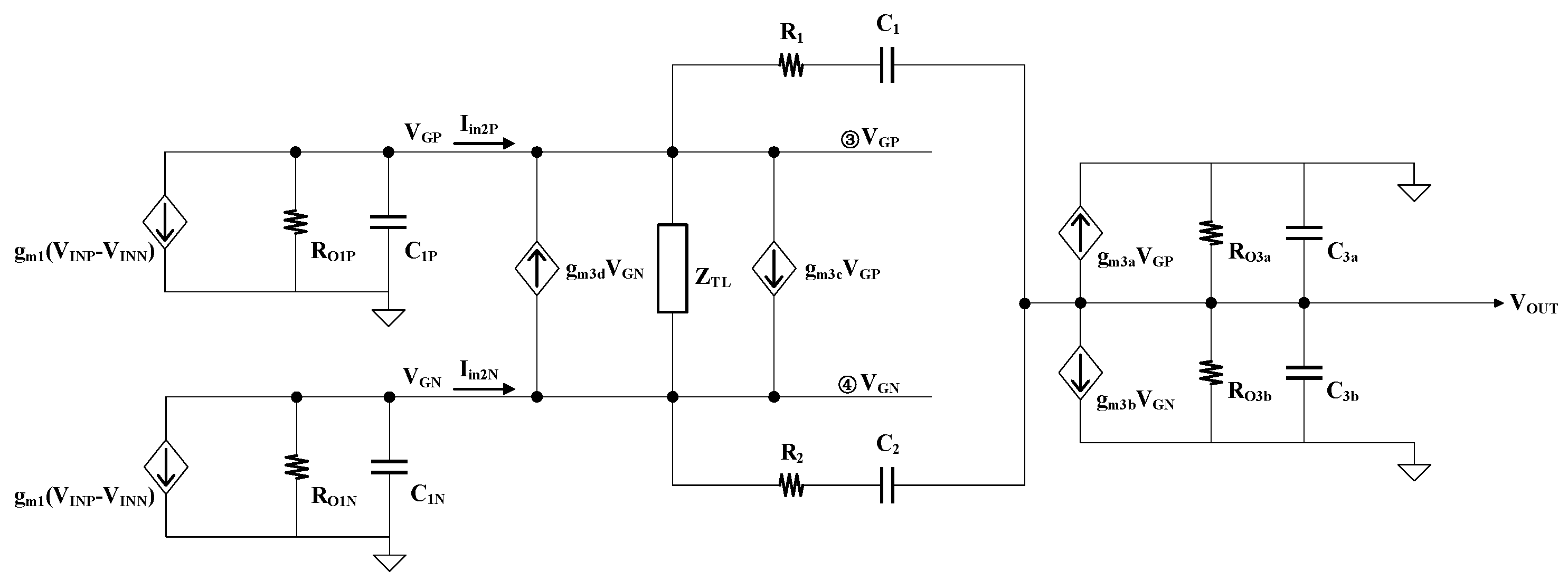

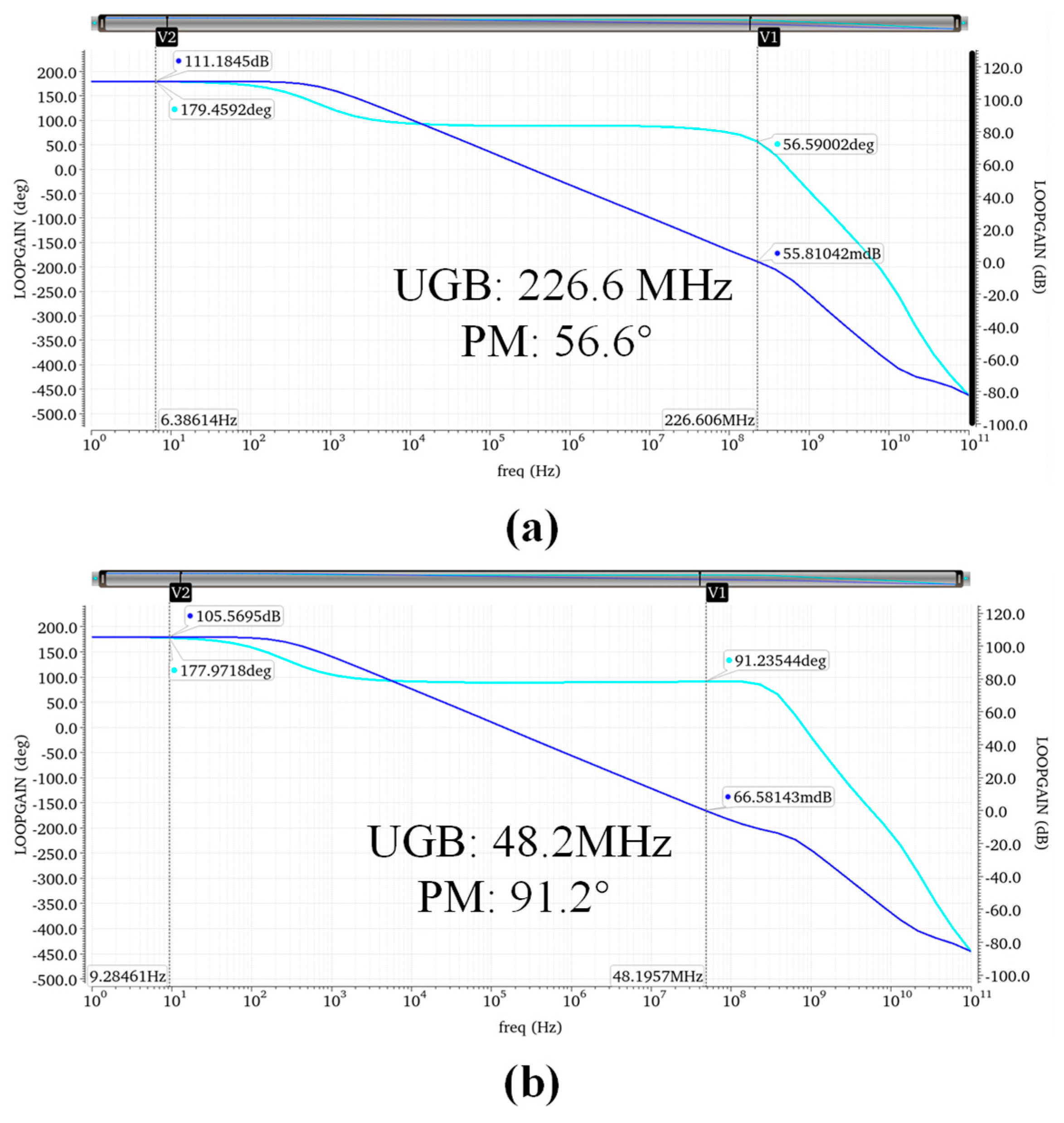

2.2.2. AC Analysis of the LA with the Proposed SRE Circuit

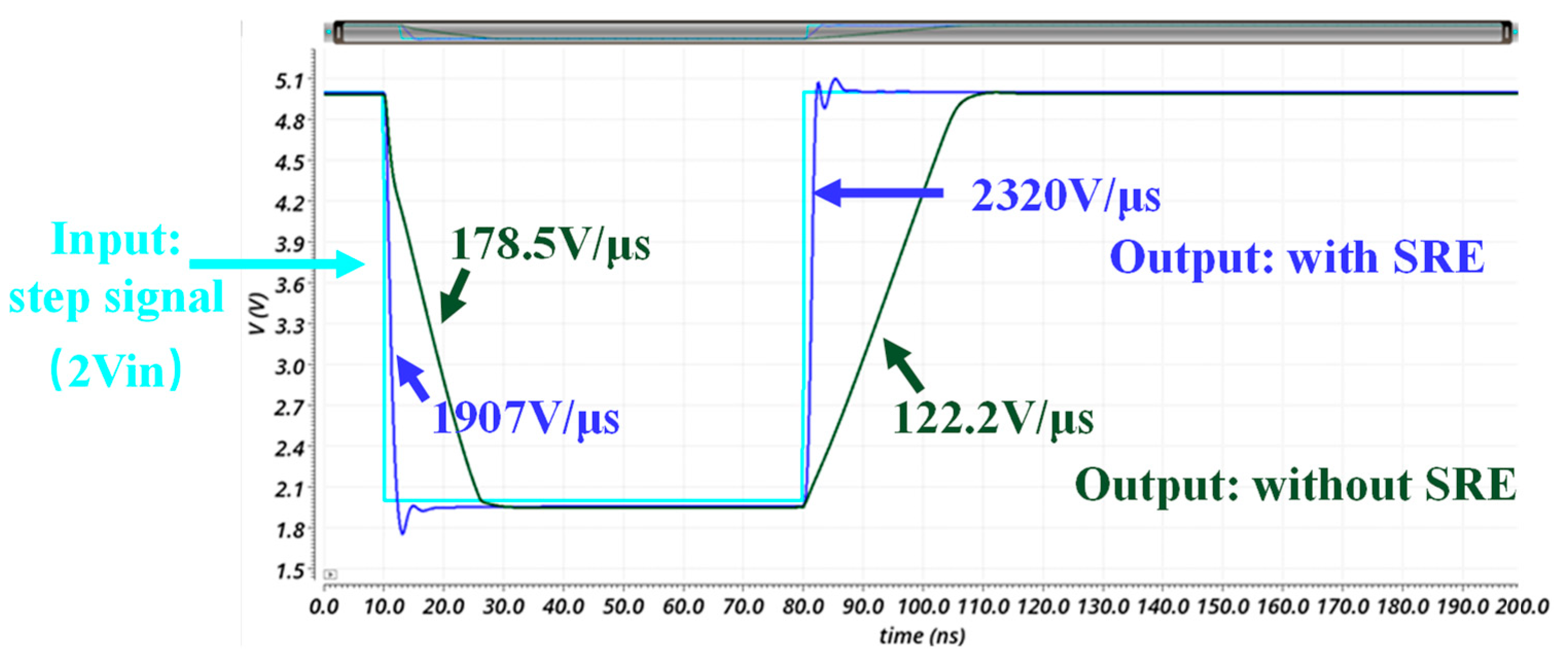

2.2.3. Simulation Results

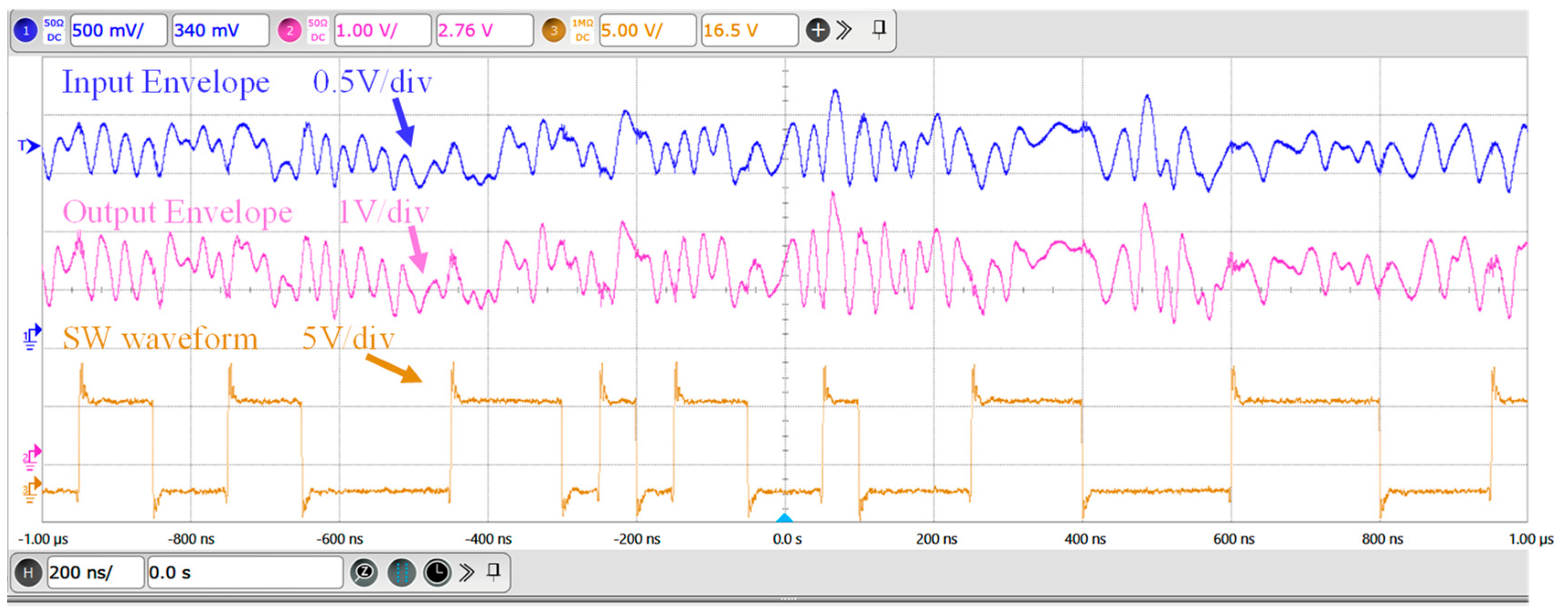

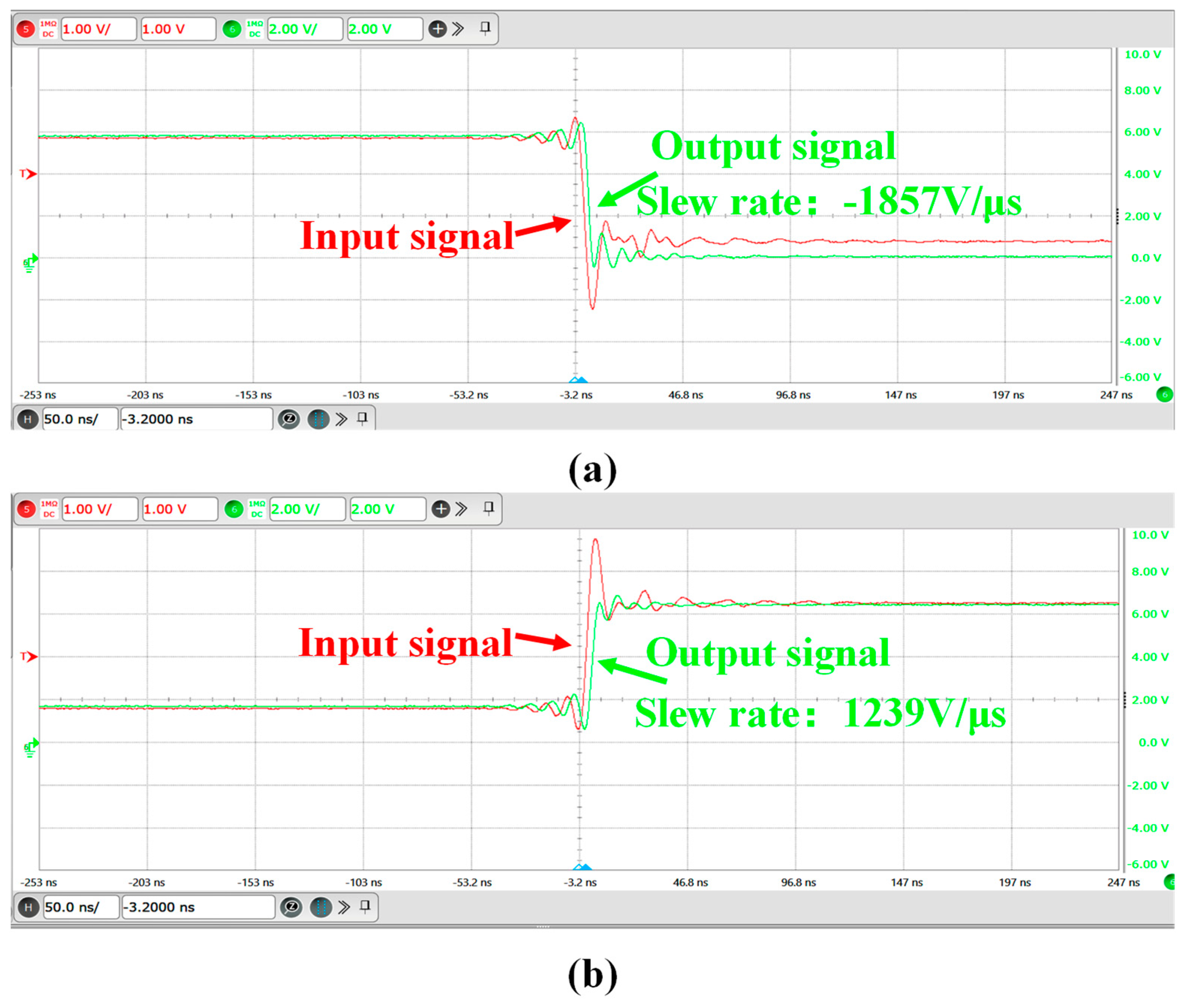

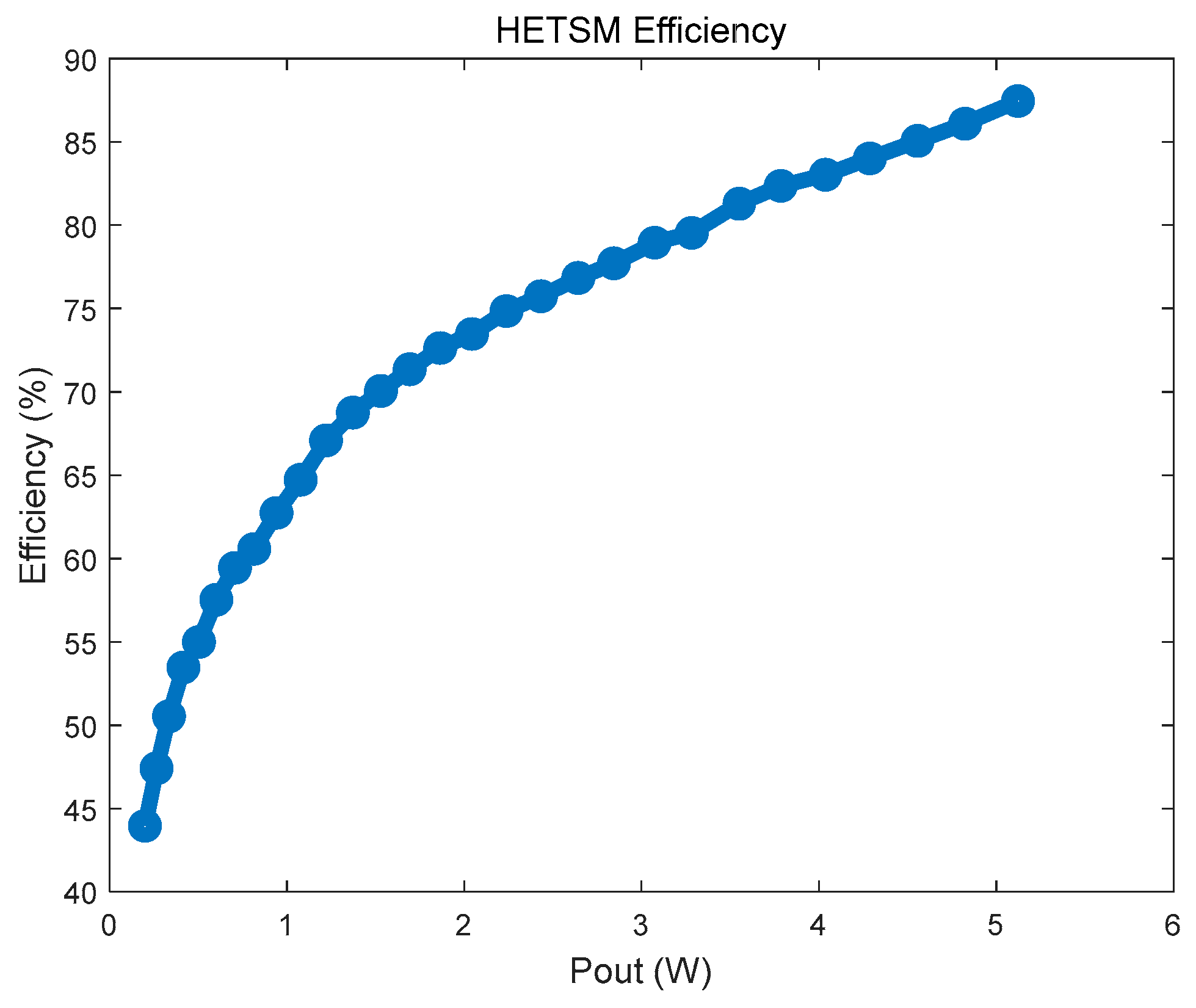

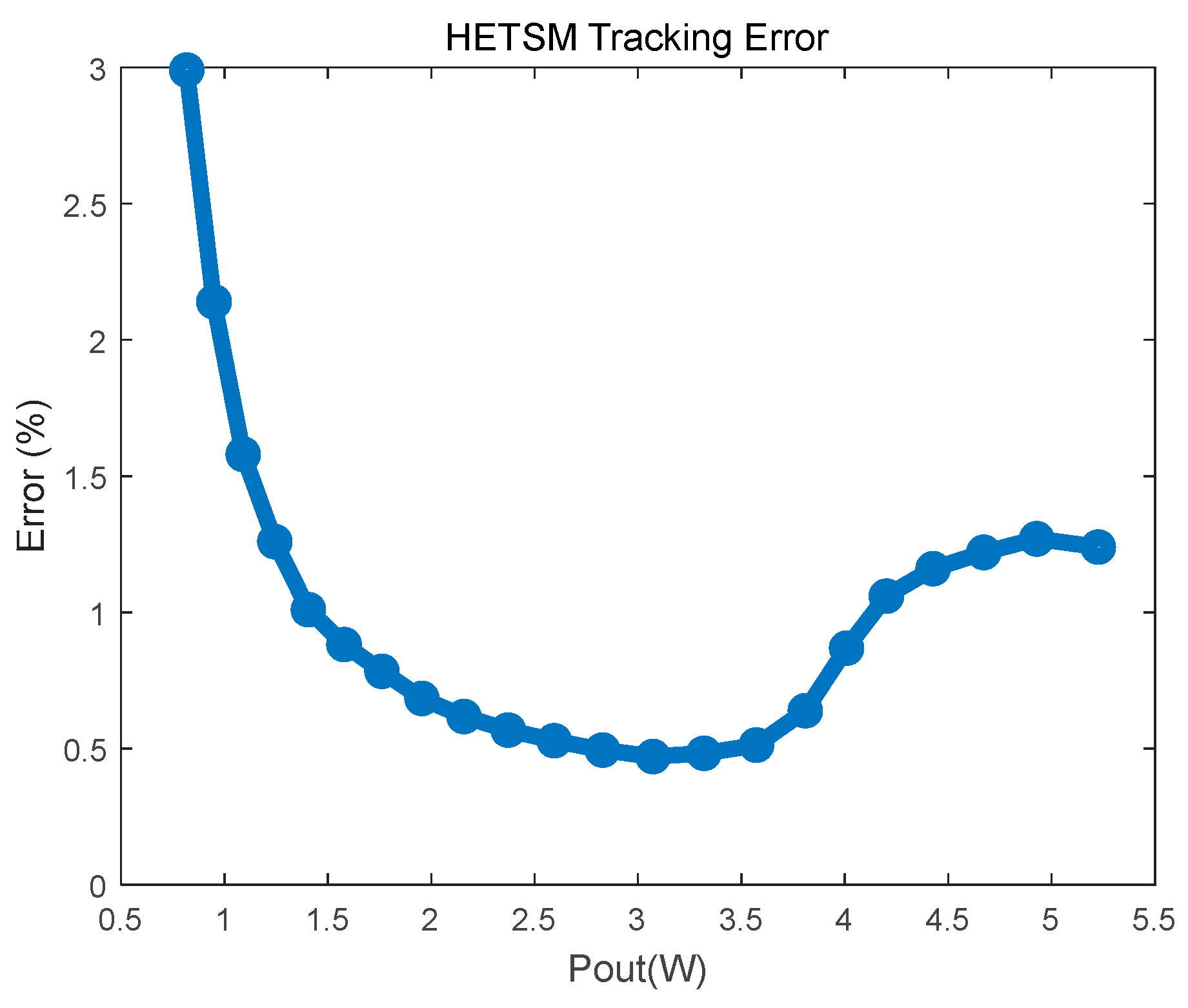

3. Experimental Results

4. Conclusions

Supplementary Materials

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Wang, Z. Envelope Tracking Power Amplifiers for Wireless Communications; Artech House: Boston, MA, USA, 2014; pp. 4–7. ISBN 978-1-60807-784-7. [Google Scholar]

- Ruan, X.; Wang, Y.; Jin, Q. A Review of Envelope Tracking Power Supply for Mobile Communication Systems. CPSS Trans. Power Electron. Appl. 2017, 2, 277–291. [Google Scholar] [CrossRef]

- Asbeck, P.; Popovic, Z. ET Comes of Age: Envelope Tracking for Higher-Efficiency Power Amplifiers. IEEE Microw. Mag. 2016, 17, 16–25. [Google Scholar] [CrossRef]

- Watkins, G.T.; Mimis, K. How Not to Rely on Moore’s Law Alone: Low-Complexity Envelope-Tracking Amplifiers. IEEE Microw. Mag. 2018, 19, 84–94. [Google Scholar] [CrossRef]

- Paek, J.-S.; Kim, D.; Choo, Y.; Youn, Y.-S.; Lee, J.; Cho, T.B.-H. Design of Boosted Supply Modulator With Reverse Current Protection for Wide Battery Range in Envelope Tracking Operation. IEEE Trans. Microw. Theory Tech. 2019, 67, 183–194. [Google Scholar] [CrossRef]

- Leng, Y.; Ruan, X.; Jin, Q.; Wang, Y. High-Efficiency High-Bandwidth Switch-Linear Hybrid Envelope-Tracking Power Supply with Slew Rate Split-Band Method. In Proceedings of the 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 1–5 October 2017; pp. 2246–2252. [Google Scholar] [CrossRef]

- Komatsuzaki, Y.; Lanfranco, S.; Kolmonen, T.; Piirainen, O.; Tanskanen, J.K.; Sakata, S.; Ma, R.; Shinjo, S.; Yamanaka, K.; Asbeck, P. A High Efficiency 3.6–4.0 GHz Envelope-Tracking Power Amplifier Using GaN Soft-Switching Buck-Converter. In Proceedings of the 2018 IEEE/MTT-S International Microwave Symposium—IMS, Philadelphia, PA, USA, 10–15 June 2018; pp. 465–468. [Google Scholar] [CrossRef]

- He, H.; Ge, T.; Chang, J. A Review on Supply Modulators for Envelope-Tracking Power Amplifiers. In Proceedings of the 2016 International Symposium on Integrated Circuits (ISIC), Singapore, 12–14 December 2016; pp. 1–4. [Google Scholar] [CrossRef]

- Mahmoudidaryan, P.; Mandal, D.; Bakkaloglu, B.; Kiaei, S. Wideband Hybrid Envelope Tracking Modulator With Hysteretic-Controlled Three-Level Switching Converter and Slew-Rate Enhanced Linear Amplifier. IEEE J. Solid-State Circuits 2019, 54, 3336–3347. [Google Scholar] [CrossRef]

- Chen, Z.; Xia, Q.; Dong, L.; Fan, S.; Han, K.; Guo, Z.; Xue, Z.; Geng, L. An Open Loop Digitally Controlled Hybrid Supply Modulator Achieving High Efficiency for Envelope Tracking With Baseband up to 200-MHz. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 4142–4153. [Google Scholar] [CrossRef]

- Hsu, Y.-T.; Lin, Z.-Y.; Lee, J.-J.; Chen, K.-H. An Envelope Tracking Supply Modulator Utilizing a GaN-Based Integrated Four-Phase Switching Converter and Average Power Tracking-Based Switch Sizing With 85.7% Efficiency for 5G NR Power Amplifier. IEEE J. Solid-State Circuits 2021, 56, 3167–3176. [Google Scholar] [CrossRef]

- Chen, D.; Zhao, C.; Xiong, Y.; Wu, Y.; Ban, Y.; Liu, Y.; Liu, H.; Kang, K. An Asynchronous Dual Switch Envelope Tracking Supply Modulator with 86% Efficiency. IEICE Electron. Express 2018, 15, 20180206. [Google Scholar] [CrossRef]

- Kwak, M.; Jeong, J.; Hassan, M.; Yan, J.J.; Kimball, D.F.; Asbeck, P.M.; Larson, L.E. High Efficiency Wideband Envelope Tracking Power Amplifier with Direct Current Sensing for LTE Applications. In Proceedings of the 2012 IEEE Topical Conference on Power Amplifiers for Wireless and Radio Applications, Santa Clara, CA, USA, 15–18 January 2012; pp. 41–44. [Google Scholar] [CrossRef]

- He, H.; Ge, T.; Kang, Y.; Guo, L.; Chang, J.S. A 40 MHz Bandwidth, 91% Peak Efficiency, 2.5 W Output Power Supply Modulator With Dual-Mode Sigma–Delta Control and Adaptive Biasing Amplifier for Multistandard Communications. IEEE Trans. Power Electron. 2020, 35, 9430–9442. [Google Scholar] [CrossRef]

- Leng, Y.; Ruan, X.; Jin, Q.; Wang, Y. Current Control Strategies for Parallel-Form Switch-Linear Hybrid Envelope Tracking Power Supply With Two Switched-Mode Converters to Achieve Optimal Power Allocation. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 2356–2368. [Google Scholar] [CrossRef]

- Choi, J.; Kim, D.; Kang, D.; Kim, B. A New Power Management IC Architecture for Envelope Tracking Power Amplifier. IEEE Trans. Microw. Theory Tech. 2011, 59, 1796–1802. [Google Scholar] [CrossRef]

- Cao, T.; Huang, F.; Zhang, Q.; Liu, Y. High Efficiency and Wideband Hybrid Envelope Amplifier for Envelope Tracking Operation of Wireless Transmitter. In Proceedings of the 2018 IEEE MTT-S International Wireless Symposium (IWS), Chengdu, China, 6–10 May 2018; pp. 1–4. [Google Scholar] [CrossRef]

- Xu, P.; Zhang, X.; Cao, P.; Wei, T.; Tong, Z.; Zeng, X.; Xu, J.; Hong, Z. A 2.7 W AC-Coupled Hybrid Supply Modulator Achieving 200 MHz Envelope-Tracking Bandwidth for 5G New Radio Power Amplifier. IEEE Trans. Power Electron. 2023, 38, 7416–7427. [Google Scholar] [CrossRef]

- Leng, W.; Abidi, A.A.; Mundlapudi, S.R.; Darabi, H.; Chowdhury, D.; Afsahi, A.; Li, S. Envelope Tracking Supply Modulator with Trellis-Search-Based Switching and 160-MHz Capability. IEEE J. Solid-State Circuits 2022, 57, 719–733. [Google Scholar] [CrossRef]

- Jing, Y.; Bakkaloglu, B. A High Slew-Rate Adaptive Biasing Hybrid Envelope Tracking Supply Modulator for LTE Applications. IEEE Trans. Microw. Theory Tech. 2017, 65, 3245–3256. [Google Scholar] [CrossRef]

- Li, S.; Yu, K.; Ou, L.; Zhou, P.; Zhang, G. A Compact Hybrid Envelope Tracking Supply Modulator with Wide-Band High-Slew-Rate Linear Amplifier. IEICE Electron. Express 2020, 17, 20200121. [Google Scholar] [CrossRef]

- Li, W.; Bartzoudis, N.; Rubio Fernández, J.; López-Bueno, D.; Montoro, G.; Gilabert, P.L. FPGA Implementation of a Linearization System for Wideband Envelope Tracking Power Amplifiers. IEEE Trans. Microw. Theory Tech. 2023, 71, 1781–1792. [Google Scholar] [CrossRef]

- Montoro, G.; Gilabert, P.L.; Vizarreta, P.; Bertran, E. Slew-Rate Limited Envelopes for Driving Envelope Tracking Amplifiers. In Proceedings of the 2011 IEEE Topical Conference on Power Amplifiers for Wireless and Radio Applications, Phoenix, AZ, USA, 16–19 January 2011; pp. 17–20. [Google Scholar] [CrossRef]

- Yen, A.; Blalock, B.J. A High Slew Rate, Low Power, Compact Operational Amplifier Based on the Super-Class AB Recycling Folded Cascode. In Proceedings of the 2020 IEEE 63rd International Midwest Symposium on Circuits and Systems (MWSCAS), Springfield, MA, USA, 9–12 August 2020; pp. 9–12. [Google Scholar] [CrossRef]

- Kwong, K.Y.; Leung, K.N. Slew-Rate Enhancement Circuit of CMOS Current-Mirror Amplifier by Edge-Detecting Technique. In Proceedings of the 2010 IEEE International Conference of Electron Devices and Solid-State Circuits (EDSSC), Hong Kong, China, 15–17 December 2010; pp. 1–4. [Google Scholar] [CrossRef]

- Panda, B.; Dash, S.K.; Mishra, S.N. High Slew Rate Op-Amp Design for Low Power Applications. In Proceedings of the 2014 International Conference on Control, Instrumentation, Communication and Computational Technologies (ICCICCT), Kanyakumari, India, 10–11 July 2014; pp. 1096–1100. [Google Scholar] [CrossRef]

- Li, P.; Wei, Q.; Luo, L. Slew-Rate Enhancement Circuit of CLASS AB Operational Transconductance Amplifier (OTA) by Auxiliary Circuit. In Proceedings of the 2022 IEEE 4th International Conference on Circuits and Systems (ICCS), Chengdu, China, 23–26 September 2022; pp. 1–5. [Google Scholar] [CrossRef]

- Zhang, M.; Wang, X.; Liu, H.; Qi, X.; Li, X.; Wang, S. Class-AB Operational Amplifier with Current Domain Slew-Rate Enhancement. In Proceedings of the 2022 IEEE 5th International Conference on Electronics Technology (ICET), Chengdu, China, 13–16 May 2022; pp. 142–146. [Google Scholar] [CrossRef]

| Design | Conventional LA (Without SRE) | The Proposed LA (With SRE) |

|---|---|---|

| UGB (MHz) | 48.2 | 226.6 |

| Phase Margin (°) | 91.2 | 56.6 |

| DC Gain (dB) | 105.6 | 111.2 |

| ) | −178.5/+122.2 | −1907/+2320 |

| Quiescent Current (mA) | 16.2 | 24 |

| Process | Temperature (°C) | DC Gain (dB) | Phase Margin (°) | UGB (MHz) | Quiescent Current (mA) | Positive Slew Rate (V/us) | Negative Slew Rate (V/us) |

|---|---|---|---|---|---|---|---|

| ff lib | −40 | 117 | 62 | 209.7 | 20.1 | 4311 | −3246 |

| 25 | 108.8 | 61.3 | 216.9 | 26.2 | 3513 | −3738 | |

| 85 | 96.9 | 60.7 | 213.3 | 32.3 | 1908 | −1920 | |

| tt lib | −40 | 118.3 | 65.3 | 212.6 | 19.5 | 3268 | −2454 |

| 25 | 111.4 | 58.9 | 228.6 | 26.0 | 2583 | −1926 | |

| 85 | 101.8 | 54.3 | 227.4 | 32.3 | 2034 | −1378 | |

| ss lib | −40 | 116.6 | 62.4 | 200.5 | 21.3 | 2222 | −1775 |

| 25 | 108.5 | 54.1 | 202 | 29.5 | 1747 | −1345 | |

| 85 | 93.8 | 67.9 | 153.5 | 37.4 | 1325 | −983 |

| Design | Process (nm) | Signal Bandwidth(MHz) | PAPR (dB) | Die Area (mm2) | LA Architecture | Max ET Voltage (V) | Load Conditions | ) | Max Tracking Error | of LA (mA) | Max Efficiency of ET System |

|---|---|---|---|---|---|---|---|---|---|---|---|

| JSSC2019 [9] | 65 | LTE 40/80 | 7.84@40 MHz 8.06@80 MHz | total: 2 × 2 = 4 core: 1.6 × 2.4 = 2.72 | parallel current–mirror SRE path | 2.4 | 4.7 Ω | −307/+325 | 2.3%@40 MHz 3.2%@80 MHz | NA | 93%@40 MHz 91%@80 MHz |

| MTT2017 [20] | 180 | LTE 10 | 7.24 | core: 1.05 × 1.05 = 1.1 | adaptive biasing using the FVF structure | 3.4 | 6 Ω||150 pF | −152.5/+93.4 | NA | 14 | 83% |

| IEICE2020 [21] | 180 | LTE 10 | 6 | total: 1.55 × 0.8 = 1.24 core: 0.78 | enhanced current–mirror structure | 3 | 5–20 Ω | −160/+220 | 1.5% | 12 | 83% |

| this work | 180 | 100 (16QAM) | 8.49 | total: 1.98 × 0.9 = 1.79 core: 1.55 × 0.6 = 0.93 | parallel nonlinear current–SRE path | 6 | 5 Ω||100 pF | −1857/+1239 | 3% | 24 | 87.4% |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, K.; Wu, J.; Zhuang, H.; Shi, Z.; Lyu, X.; Wang, Z.; Chen, H.; Yu, F. A Wideband Hybrid Envelope Tracking Supply Modulator with Slew-Rate-Enhanced Linear Amplifier. Electronics 2024, 13, 2701. https://doi.org/10.3390/electronics13142701

Zhang K, Wu J, Zhuang H, Shi Z, Lyu X, Wang Z, Chen H, Yu F. A Wideband Hybrid Envelope Tracking Supply Modulator with Slew-Rate-Enhanced Linear Amplifier. Electronics. 2024; 13(14):2701. https://doi.org/10.3390/electronics13142701

Chicago/Turabian StyleZhang, Kaida, Jianhui Wu, Huabao Zhuang, Zhening Shi, Xiaofeng Lyu, Zhiyu Wang, Hua Chen, and Faxin Yu. 2024. "A Wideband Hybrid Envelope Tracking Supply Modulator with Slew-Rate-Enhanced Linear Amplifier" Electronics 13, no. 14: 2701. https://doi.org/10.3390/electronics13142701